A VCII-Based Stray Insensitive Analog Interface for Differential Capacitance Sensors

Abstract

:1. Introduction

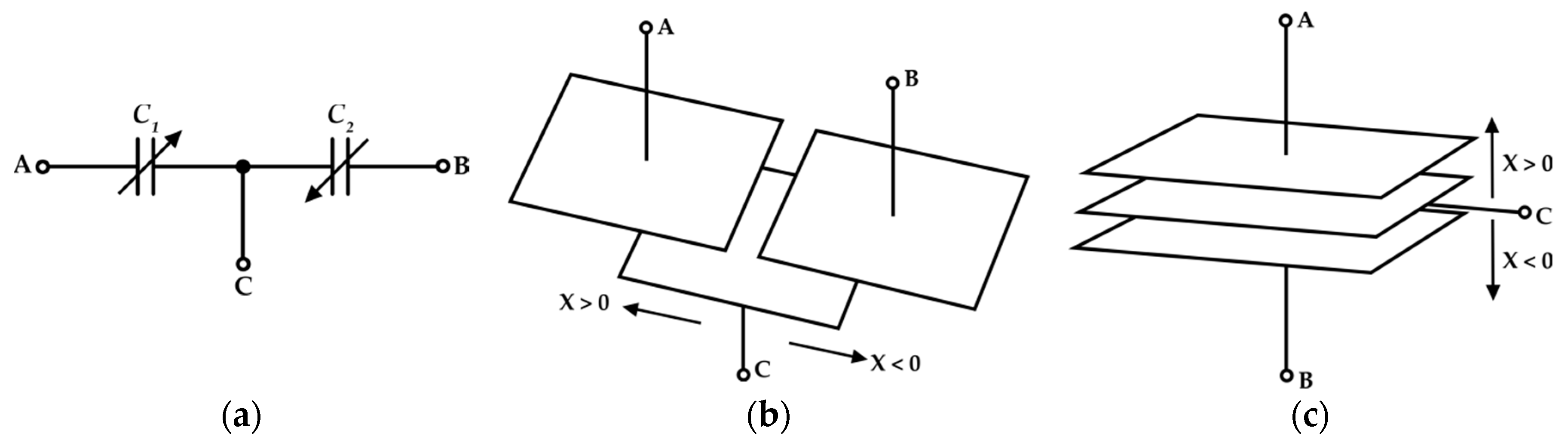

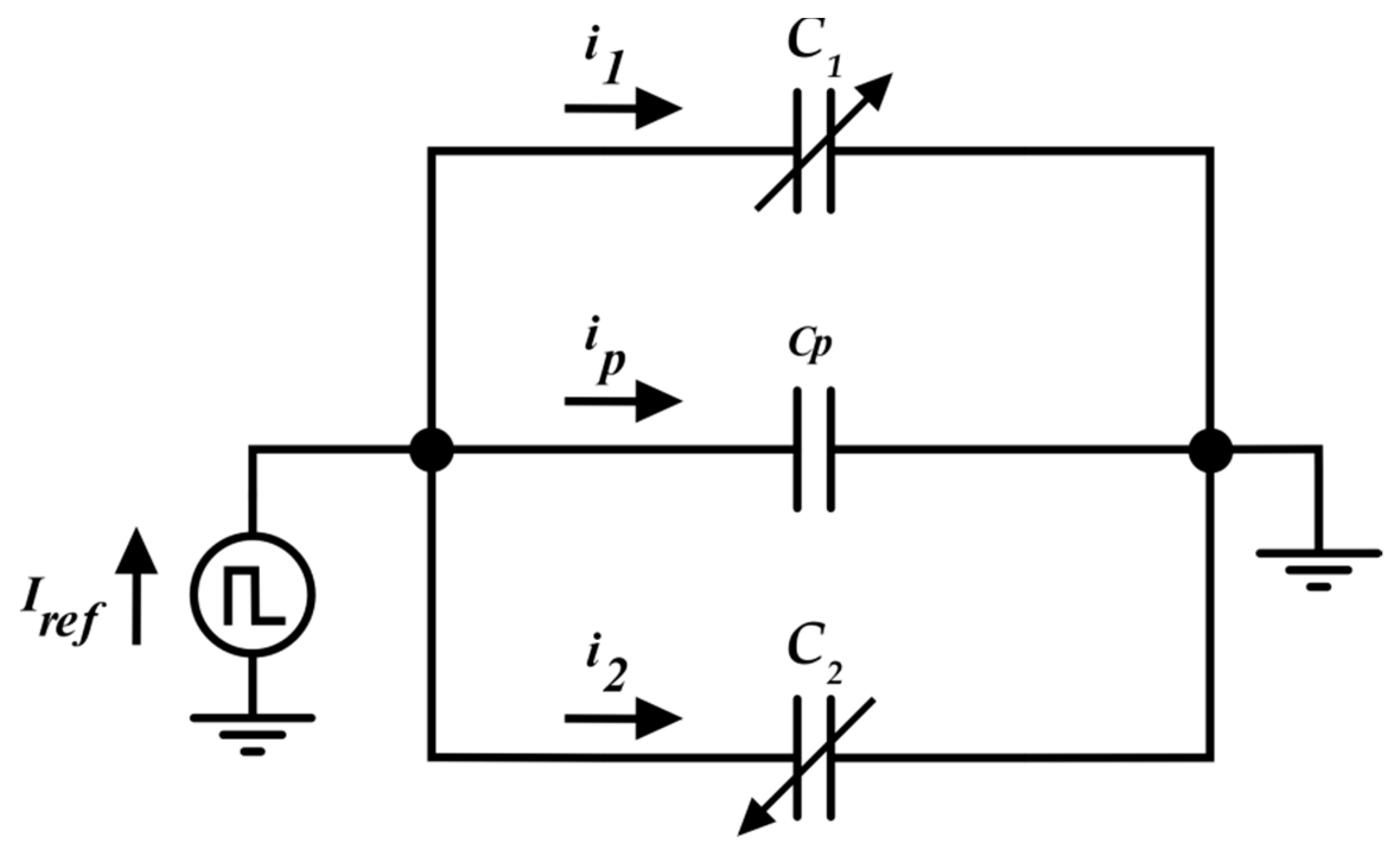

2. Basic Theory

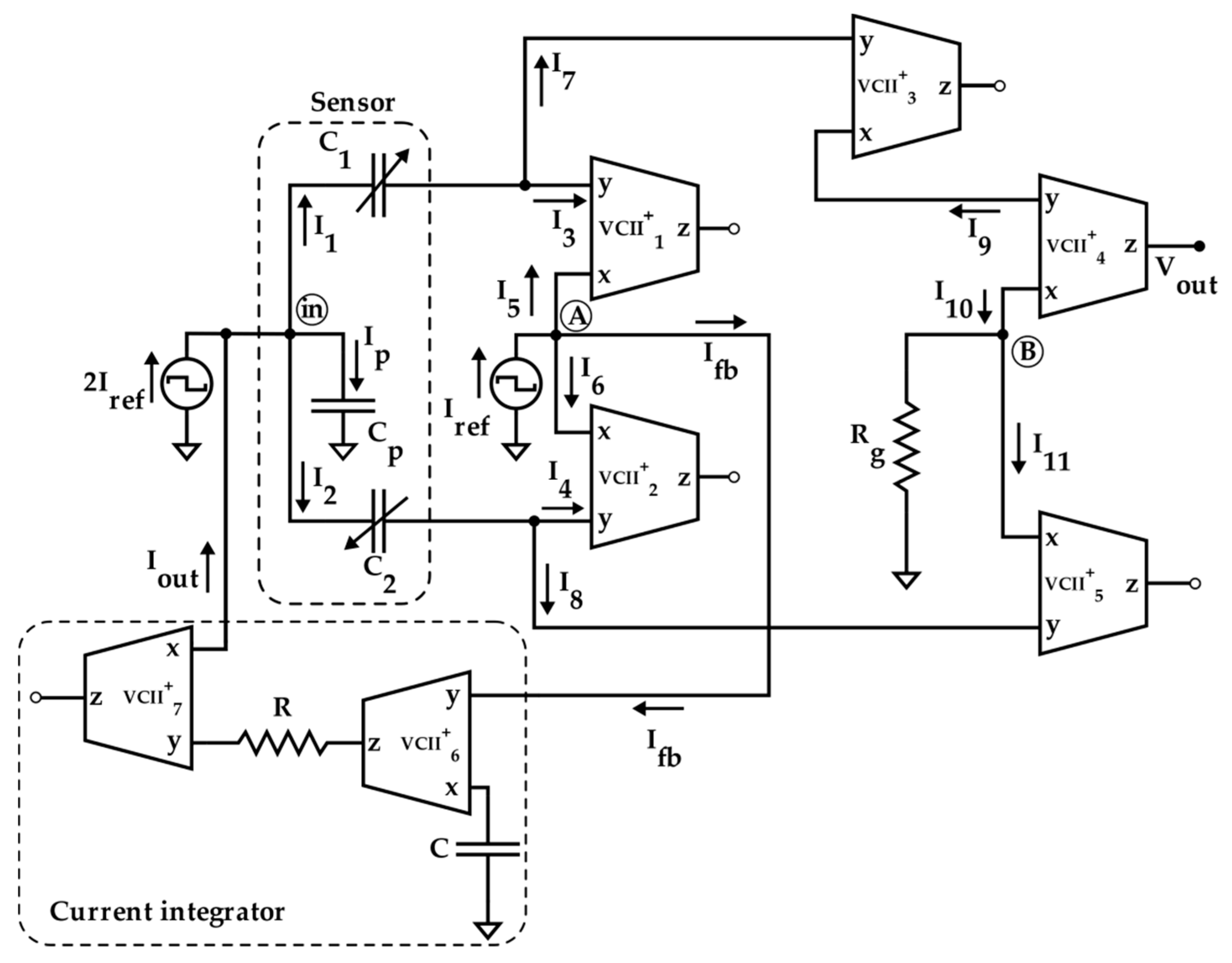

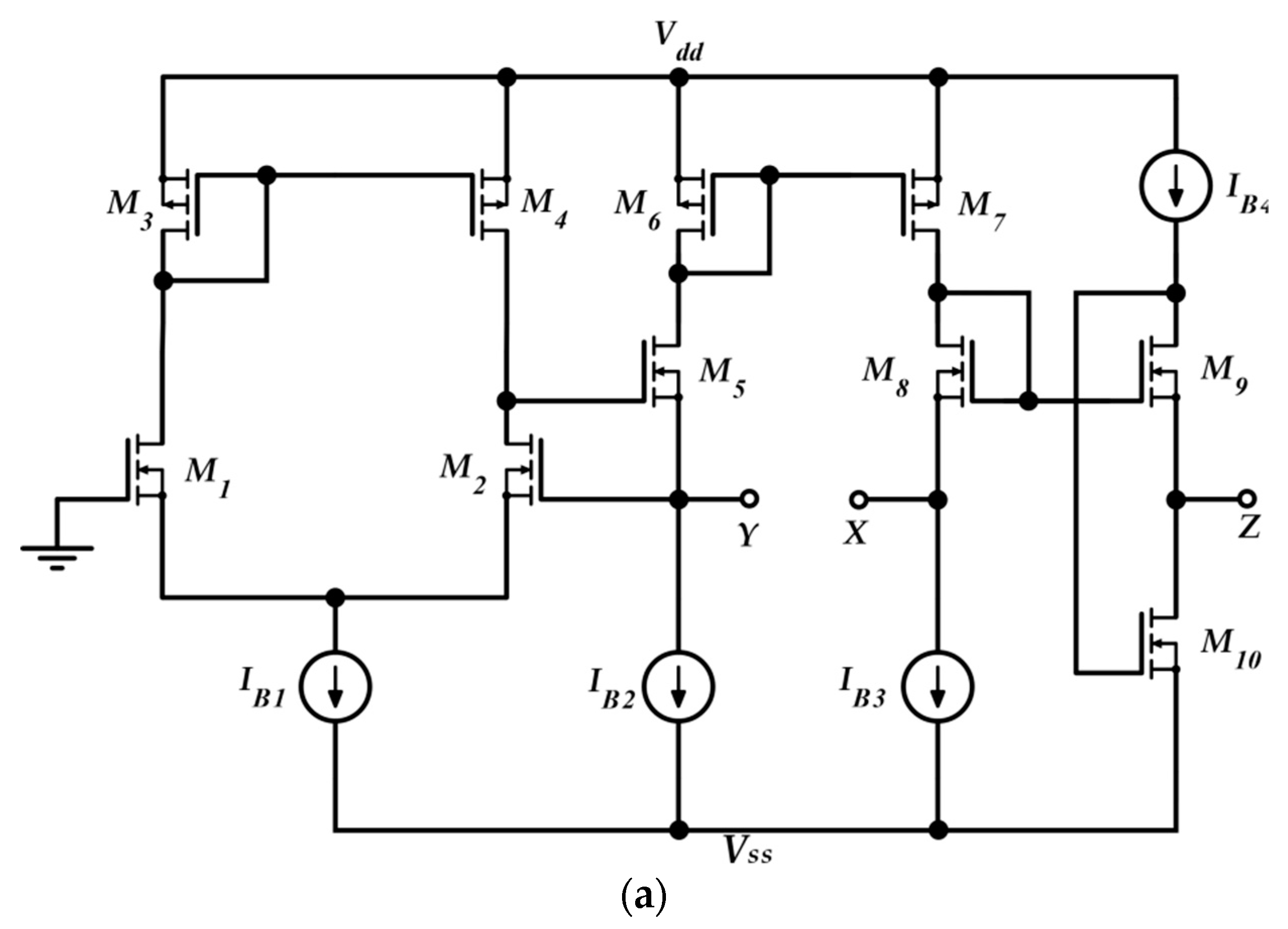

3. The Proposed Interface

- The first part is a VCII-based current summing/subtracting block composed of VCII1–VCII2 and a current source equal to Iref. The sensor input is excited by a current source equal to 2Iref. The virtual ground and low impedance at Y terminal of VCII keeps the sensor second terminal to ground. In this section, according to Equation (5), the sum of I1 and I2 is produced and the result is subtracted from Iref to obtain Ifb, which, suitably integrated, generates the current taken by Cp (Iout tends to −Ip).

- The second part is the control section, which feeds Ifb to the sensor input. As it is shown in Figure 3, it is a VCII-based current-input—current-output integrator composed of the two VCII blocks, a resistor, and a grounded capacitor.

- In the third part (output section), the difference between I1 and I2 is produced and converted to a proportional voltage signal. This operation is performed by three VCII blocks (VCII3–VCII5) and resistor Rg.

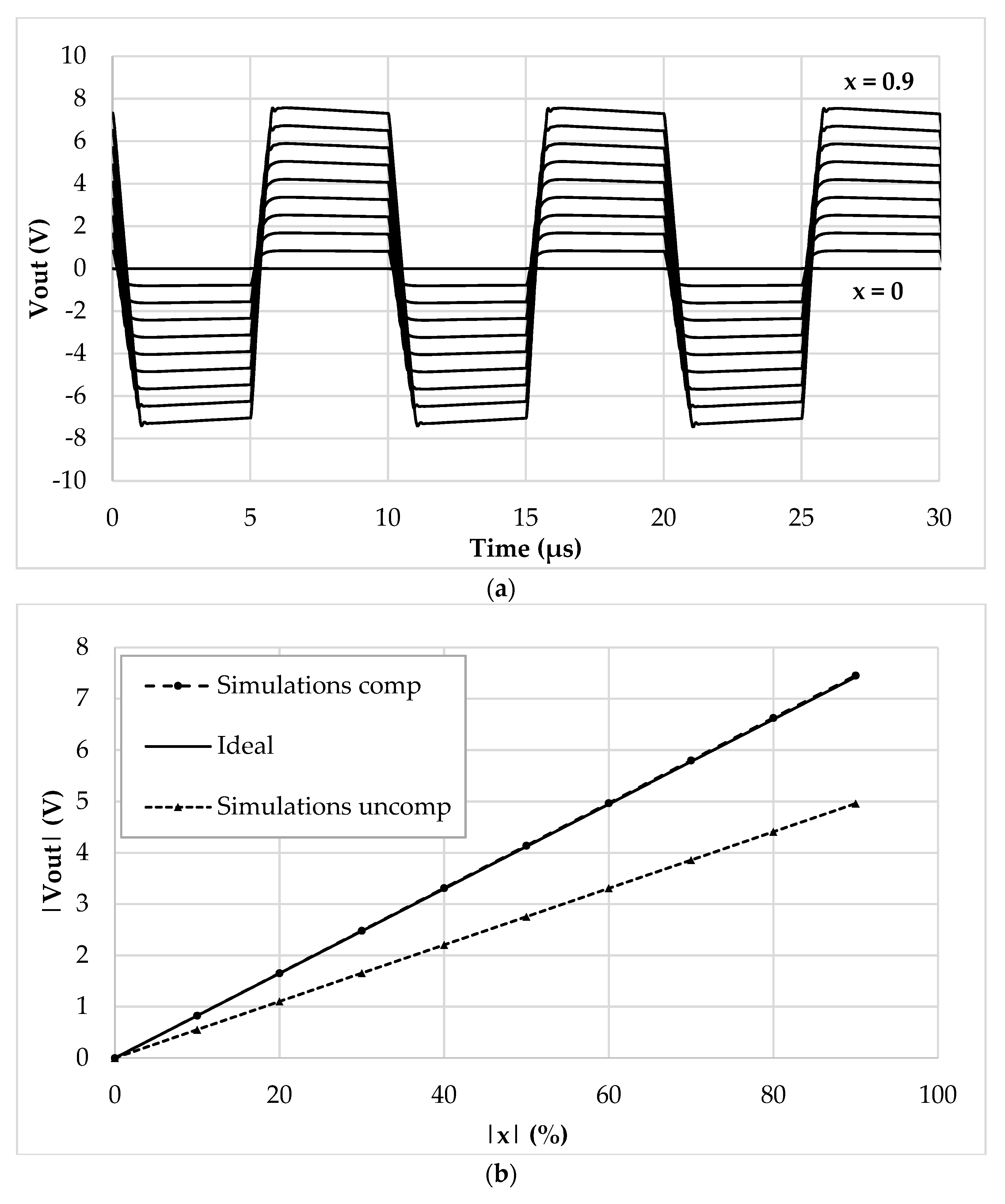

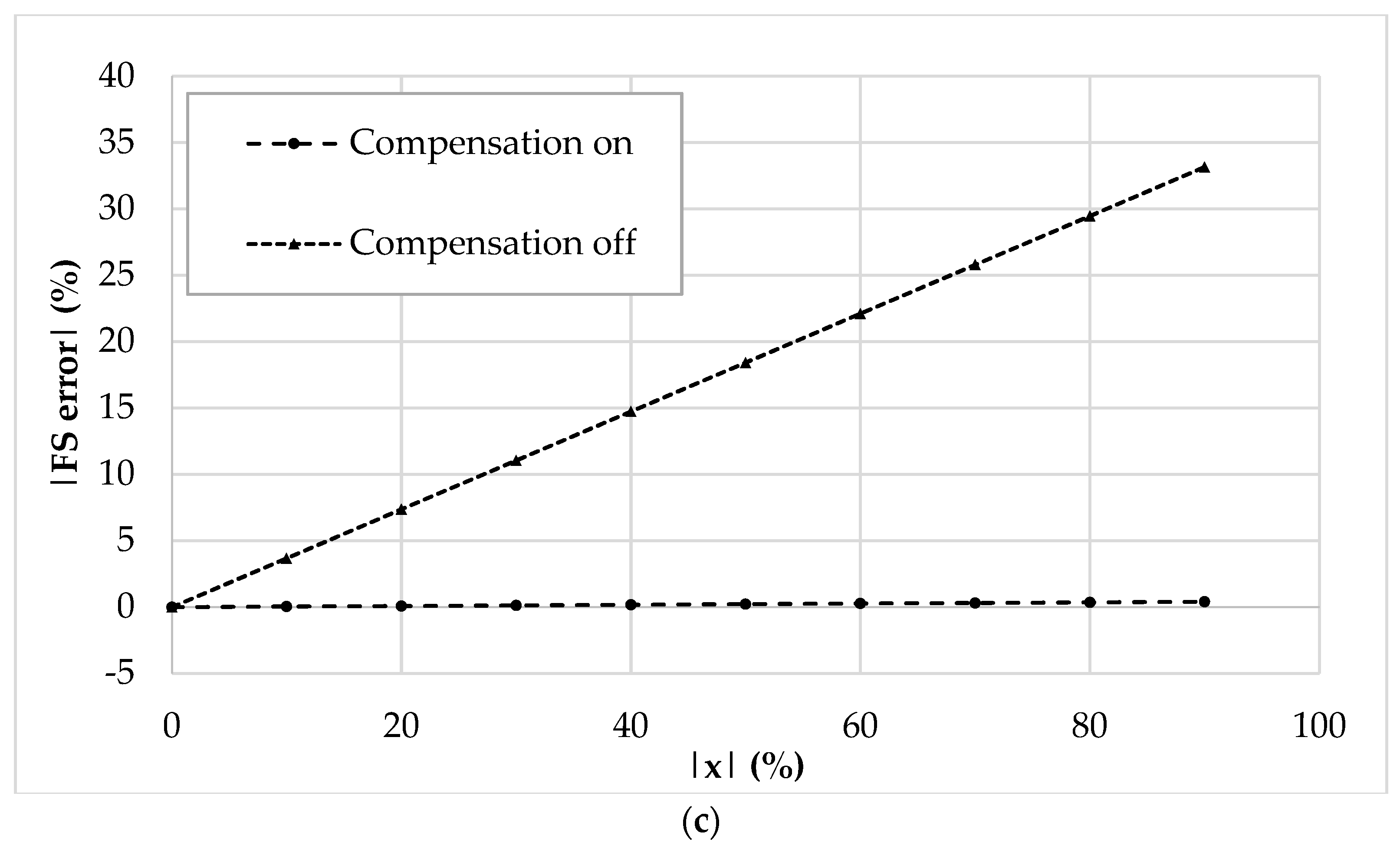

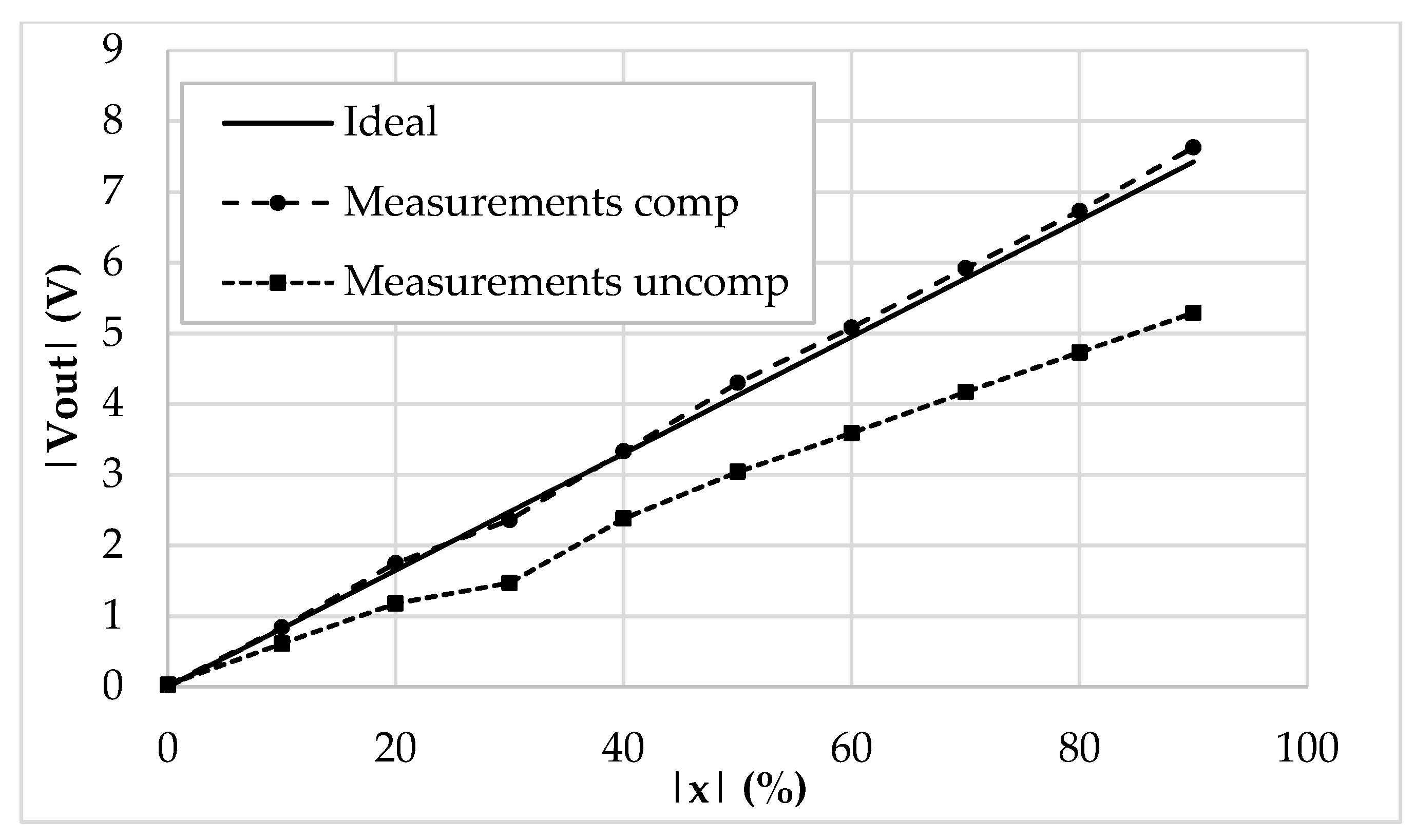

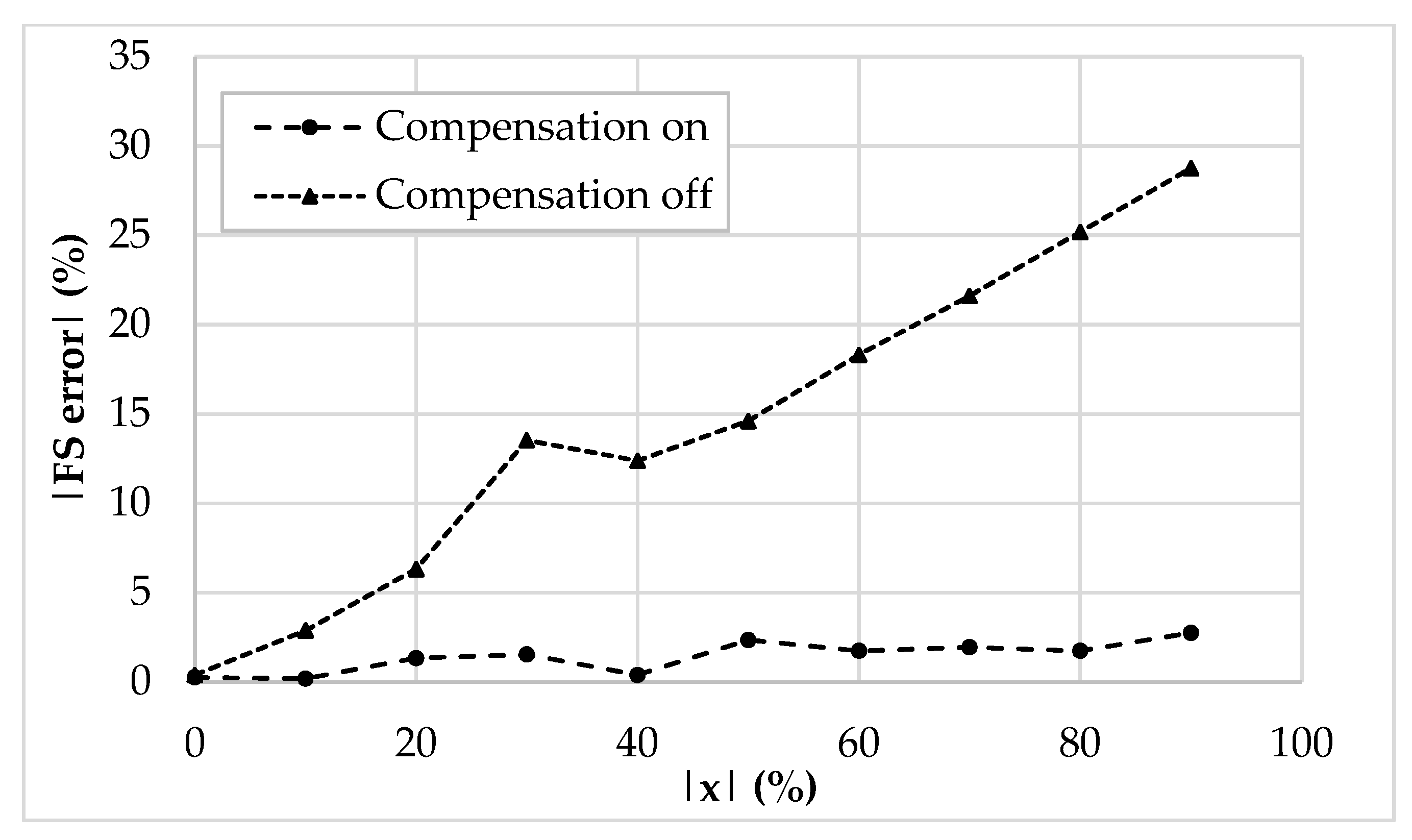

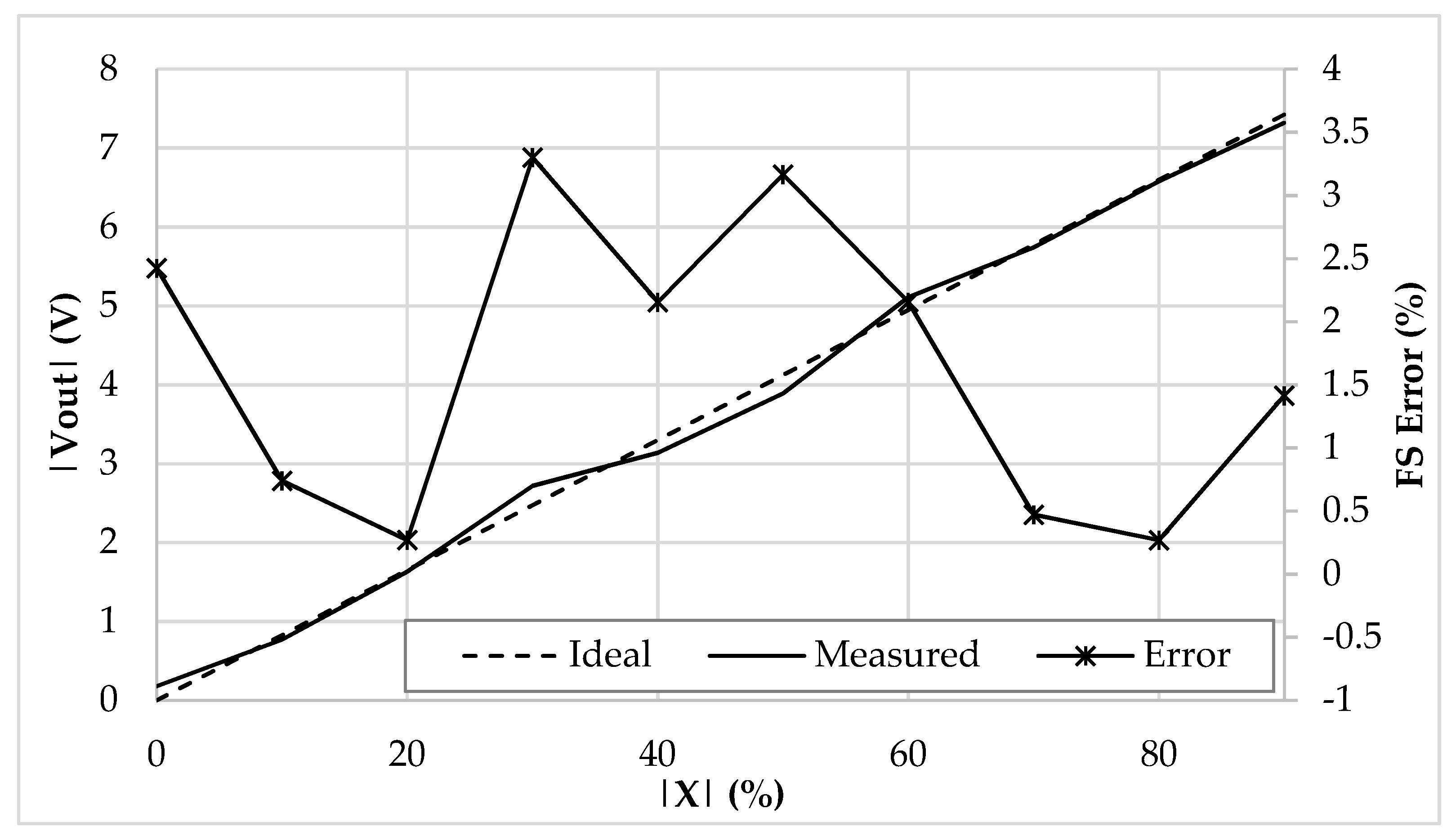

4. Simulation Results and Measurements

5. Conclusions

Author Contributions

Funding

Conflicts of Interest

References

- Polak, L.; Sotner, R.; Petrzela, J.; Jerabek, J. CMOS Current Feedback Operational Amplifier-Based Relaxation Generator for Capacity to Voltage Sensor Interface. Sensors 2018, 18, 4488. [Google Scholar] [CrossRef] [PubMed]

- Brookhuis, R.; Lammerink, T.; Wiegerink, R. Differential capacitive sensing circuit for a multi-electrode capacitive force sensor. Sens. Actuators A Phys. 2015, 234, 168–179. [Google Scholar] [CrossRef]

- Royo, G.; Sánchez-Azqueta, C.; Gimeno, C.; Aldea, C.; Celma, S. Programmable Low-Power Low-Noise Capacitance to Voltage Converter for MEMS Accelerometers. Sensors 2016, 17, 67. [Google Scholar] [CrossRef] [PubMed]

- Chen, W.; Zhao, Z.; Liu, X.; Zhang, Z.; Suo, C. A Capacitive Humidity Sensor Based on Multi-Wall Carbon Nanotubes (MWCNTs). Sensors 2009, 9, 7431–7444. [Google Scholar] [CrossRef] [PubMed]

- Wang, Y.; Chodavarapu, V. Differential Wide Temperature Range CMOS Interface Circuit for Capacitive MEMS Pressure Sensors. Sensors 2015, 15, 4253–4263. [Google Scholar] [CrossRef] [Green Version]

- Hu, H.; Xu, T.; Hui, S. A high-accuracy, high-speed interface circuit for differential-capacitance transducer. Sens. Actuators A Phys. 2006, 125, 329–334. [Google Scholar] [CrossRef]

- Pennisi, S. High-performance and simple CMOS interface circuit for differential capacitive sensors. IEEE Trans. Circuits Syst. II Express Briefs 2005, 52, 327–330. [Google Scholar] [CrossRef]

- Depari, A.; Sisinni, E.; Flammini, A.; Ferri, G.; Stornelli, V.; Barile, G.; Parente, F. Autobalancing Analog Front End for Full-Range Differential Capacitive Sensing. IEEE Trans. Instrum. Meas. 2018, 67, 885–893. [Google Scholar] [CrossRef]

- Barile, G.; Ferri, G.; Parente, F.; Stornelli, V.; Depari, A.; Flammini, A.; Sisinni, E. A standard CMOS bridge-based analog interface for differential capacitive sensors. In Proceedings of the 13th Conference on Ph.D. Research in Microelectronics and Electronics (PRIME), Giardini Naxos, Italy, 12–15 June 2017. [Google Scholar]

- Scotti, G.; Pennisi, S.; Monsurrò, P.; Trifiletti, A. 88-uA 1-MHz Stray-Insensitive CMOS Current-Mode Interface IC for Differential Capacitive Sensors. IEEE Trans. Circuits Syst. I Regul. Pap. 2014, 61, 1905–1916. [Google Scholar] [CrossRef]

- George, B.; Madhu Mohan, N.; Jagadeesh Kumar, V. A Linear Variable Differential Capacitive Transducer for Sensing Planar Angles. IEEE Trans. Instrum. Meas. 2008, 57, 736–742. [Google Scholar] [CrossRef]

- Mochizuki, K.; Watanabe, K.; Masuda, T. A high-accuracy high-speed signal processing circuit of differential-capacitance transducers. IEEE Trans. Instrum. Meas. 1998, 47, 1244–1247. [Google Scholar] [CrossRef] [Green Version]

- Dimitropoulos, P.; Karampatzakis, D.; Panagopoulos, G.; Stamoulis, G. A low-power/low-noise readout circuit for integrated capacitive sensors. IEEE Sens. J. 2006, 6, 755–769. [Google Scholar] [CrossRef]

- Shiah, J.; Rashtian, H.; Mirabbasi, S. A low-noise high-sensitivity readout circuit for MEMS capacitive sensors. In Proceedings of the IEEE International Symposium on Circuits and Systems, Paris, France, 30 May–2 June 2010. [Google Scholar]

- Bracke, W.; Merken, P.; Puers, R.; Van Hoof, C. Ultra-Low-Power Interface Chip for Autonomous Capacitive Sensor Systems. IEEE Trans. Circuits Syst. I Regul. Pap. 2007, 54, 130–140. [Google Scholar] [CrossRef]

- George, B.; Kumar, V. Switched Capacitor Signal Conditioning for Differential Capacitive Sensors. IEEE Trans. Instrum. Meas. 2007, 56, 913–917. [Google Scholar] [CrossRef]

- Mohan, N.M.; Shet, A.R.; Kedarnath, S.; Kumar, V.J. Digital converter for differential capacitive sensors. IEEE Trans. Instrum. Meas. 2008, 57, 2576–2581. [Google Scholar] [CrossRef]

- Barile, G.; Ferri, G.; Parente, F.; Stornelli, V.; Sisinni, E.; Depari, A.; Flammini, A. A CMOS full-range linear integrated interface for differential capacitive sensor readout. Sens. Actuators A Phys. 2018, 281, 130–140. [Google Scholar] [CrossRef]

- Kim, H.; Lee, B.; Mun, Y.; Kim, J.; Han, K.; Roh, Y.; Song, D.; Huh, S.; Ko, H. Reconfigurable Sensor Analog Front-End Using Low-Noise Chopper-Stabilized Delta-Sigma Capacitance-to-Digital Converter. Micromachines 2018, 9, 347. [Google Scholar] [CrossRef]

- Ferri, G.; Parente, F.; Stornelli, V.; Barile, G.; Pantoli, L. Automatic Bridge-based Interface for Differential Capacitive Full Sensing. Procedia Eng. 2016, 168, 1585–1588. [Google Scholar] [CrossRef]

- Ferri, G.; Stornelli, V.; Parente, F.; Barile, G. Full range analog Wheatstone bridge-based automatic circuit for differential capacitance sensor evaluation. Int. J. Circuit Theory Appl. 2016, 45, 2149–2156. [Google Scholar] [CrossRef]

- Ferri, G.; Parente, F.; Stornelli, V. Current conveyor-based differential capacitance analog interface for displacement sensing application. AEU Int. J. Electron. Commun. 2017, 81, 83–91. [Google Scholar] [CrossRef]

- Filanovsky, I.M. Current Conveyor, Voltage Conveyor, Gyrator. In Proceedings of the 44th IEEE 2001 Midwest Symposium on Circuits and Systems, Dayton, OH, USA, 14–17 August 2001; Volume 1, pp. 314–317. [Google Scholar]

- Cajka, J.; Vrba, K. The Voltage Conveyor May Have in Fact Found its Way into Circuit Theory. Int. J. Electron. Commun. 2004, 58, 244–248. [Google Scholar] [CrossRef]

- Safari, L.; Barile, G.; Stornelli, V.; Ferri, G. An Overview on the Second Generation Voltage Conveyor: Features, Design and Applications. IEEE Trans. Circuits Syst. II Express Briefs 2019, 66, 547–551. [Google Scholar] [CrossRef]

- Barile, G.; Ferri, G.; Safari, L.; Stornelli, V. A New High Drive Class-AB FVF Based Second Generation Voltage Conveyor. IEEE Trans. Circuits Syst. II Express Briefs 2019. [Google Scholar] [CrossRef]

- Safari, L.; Barile, G.; Stornelli, V.; Ferri, G.; Leoni, A. New Current Mode Wheatstone Bridge Topologies with Intrinsic Linearity. In Proceedings of the 2018 14th Conference on Ph.D. Research in Microelectronics and Electronics (PRIME), Prague, Czech Republic, 2–5 July 2018. [Google Scholar]

- Safari, L.; Barile, G.; Ferri, G.; Stornelli, V. High performance voltage output filter realizations using second generation voltage conveyor. Int. J. Rf Microw. Comput. Aided Eng. 2018, 28, e21534. [Google Scholar] [CrossRef]

- Barile, G.; Leoni, A.; Pantoli, L.; Safari, L.; Stornelli, V. A New VCII Based Low-Power Low-Voltage Front-end for Silicon Photomultipliers. In Proceedings of the 2018 3rd International Conference on Smart and Sustainable Technologies (SpliTech), Split, Croatia, 26–29 June 2018. [Google Scholar]

- A New VCII Based Low-Power Low-Voltage Front-End for Silicon Photomultipliers. Available online: http://ieeexplore.ieee.org/stamp/stamp.jsp?tp=&arnumber=8448384&isnumber=8448303 (accessed on 13 August 2019).

- Pantoli, L.; Barile, G.; Leoni, A.; Muttillo, M.; Stornelli, V. A Novel Electronic Interface for Micromachined Si-Based Photomultipliers. Micromachines 2018, 9, 507. [Google Scholar] [CrossRef]

- Kaewpoonsuk, A.; Riewruja, V.; Rerkratn, A.; Kamsri, T. An accurate CCII-based voltage controlled current source. In Proceedings of the International Conference on Control, Automation and Systems (ICCAS), Seoul, Korea, 14–17 October 2008. [Google Scholar]

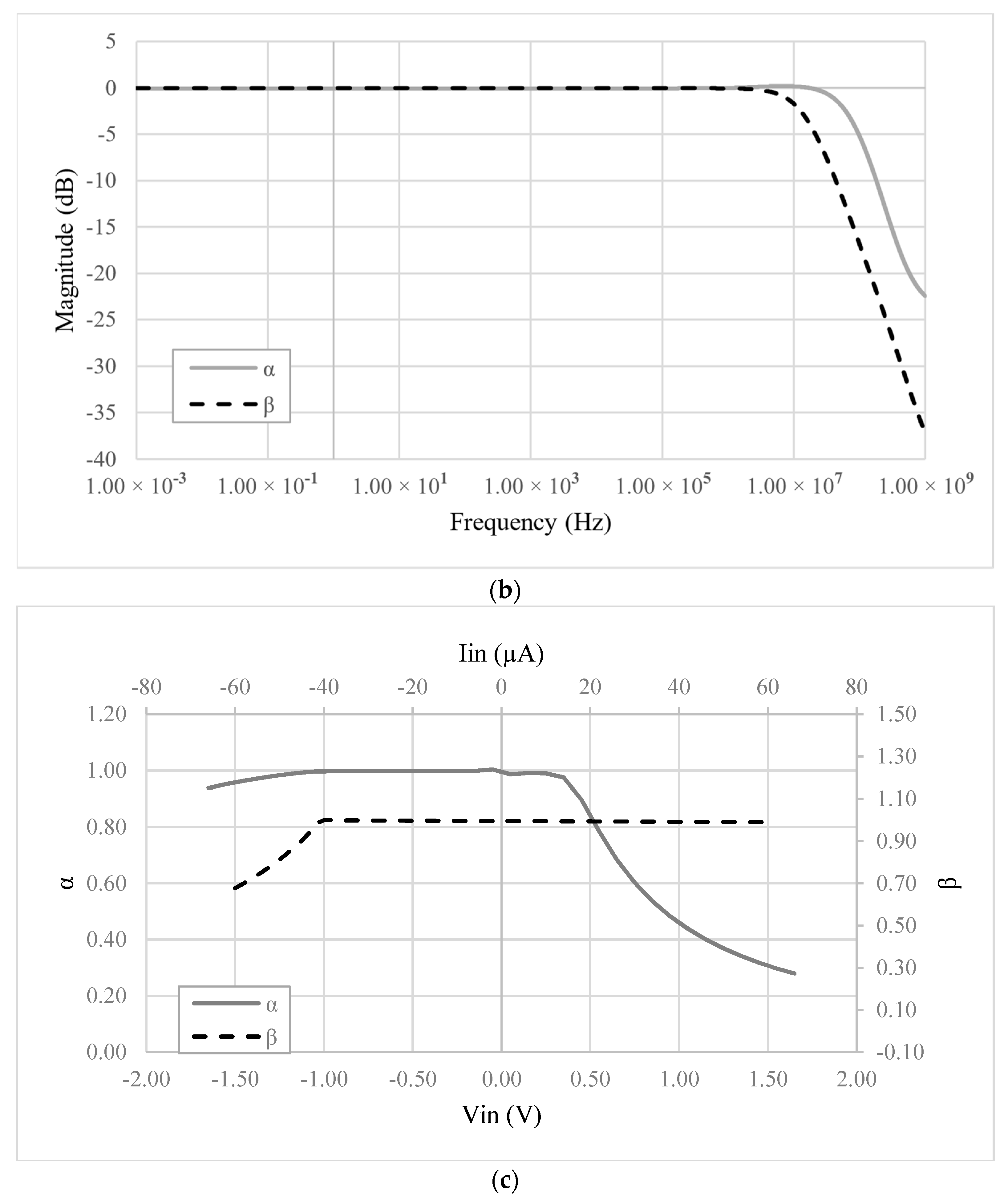

| Parameter | Value | |

|---|---|---|

| rx | 800 kΩ | |

| ry | 50 Ω | |

| rz | 80 Ω | |

| α | −43 mdB | |

| β | −45 mdB | |

| Voltage noise density at | x | 342 nV/√Hz |

| y | 420 nV/√Hz | |

| z | 118 nV/√Hz | |

| Power dissipation | 0.7 mW | |

| Ref. | This Work | [8] | [10] | [12] | [16] | [17] | [21] |

|---|---|---|---|---|---|---|---|

| Approach | Mixed | C to V | C to I | C to V | C to V | C to Digital | C to V |

| Variation Range | ±100% | ±100% | ±100% | ±60% | ±50% | ±50% | −30%; +100% |

| Cbl | 10 pF/200 pF | 140 pF ÷ 14 nF | 1 pF | 20 pF | 500 pF | 400 pF | 400 pF |

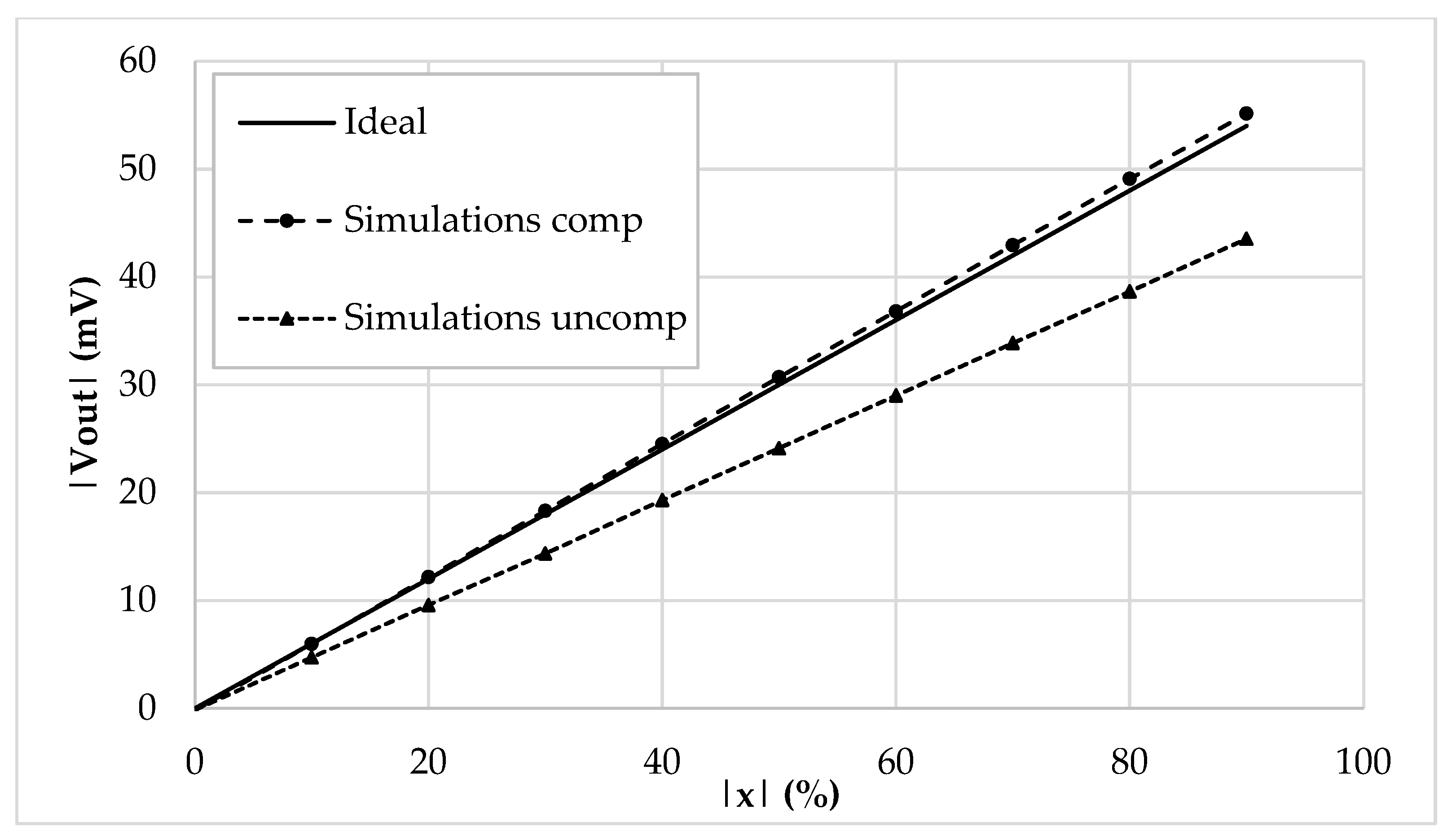

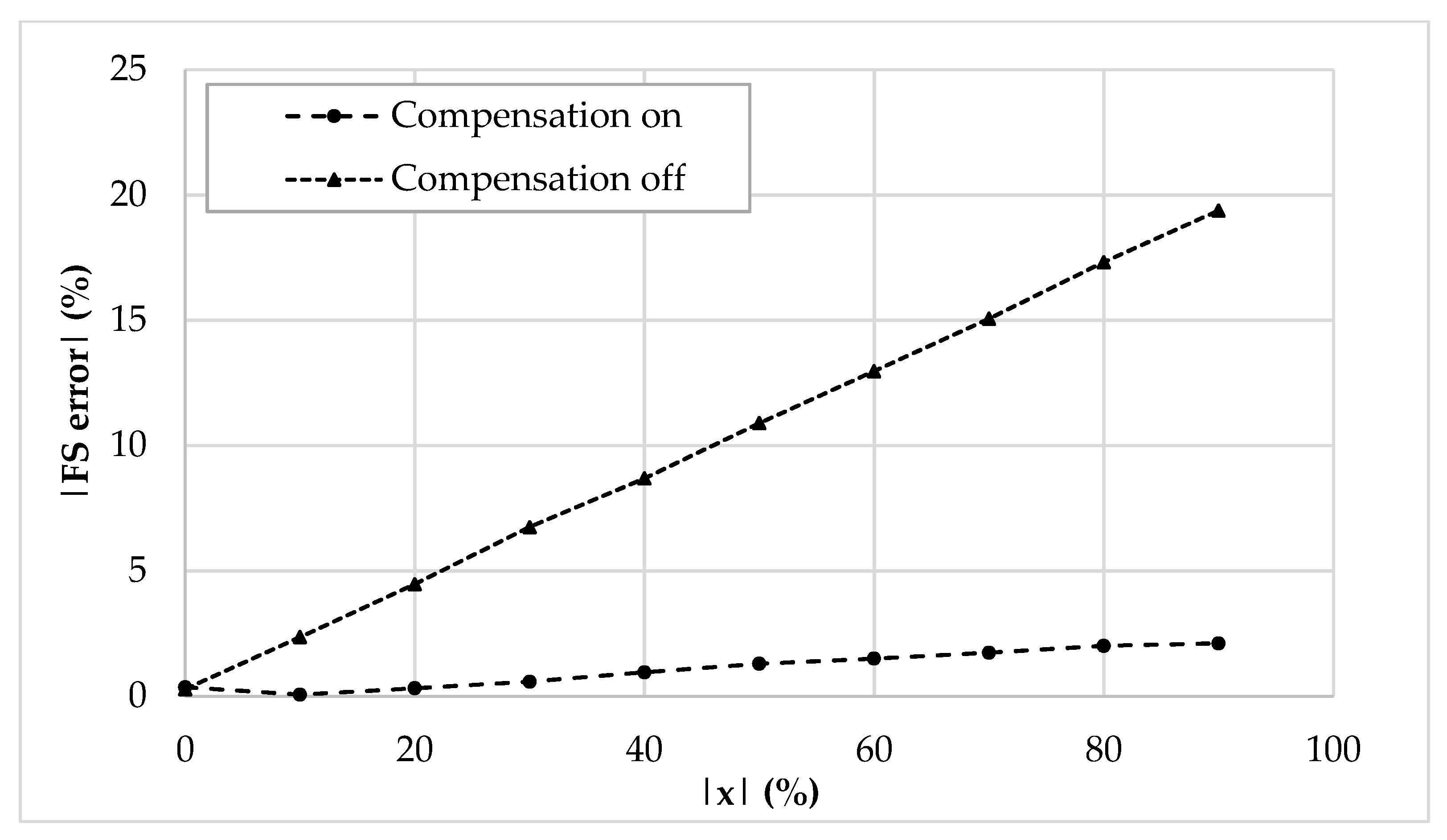

| Linearity Error FS | <1.9%/<0.9% | 0.5 ÷ 0.8% | ±1.5% | <0.1% | <0.03% | <0.2% | <0.45% |

| Sensitivity | 412 mV/pF/21 mV/pF | 71 mV/pF | 50 nA/fF | 833 mV/pf | 5 mV/pF | 4 counts/pF | Nonlinear |

| Typology | Discrete | Discrete | Integrated | Discrete | Discrete | Discrete | Discrete |

© 2019 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).

Share and Cite

Barile, G.; Safari, L.; Ferri, G.; Stornelli, V. A VCII-Based Stray Insensitive Analog Interface for Differential Capacitance Sensors. Sensors 2019, 19, 3545. https://doi.org/10.3390/s19163545

Barile G, Safari L, Ferri G, Stornelli V. A VCII-Based Stray Insensitive Analog Interface for Differential Capacitance Sensors. Sensors. 2019; 19(16):3545. https://doi.org/10.3390/s19163545

Chicago/Turabian StyleBarile, Gianluca, Leila Safari, Giuseppe Ferri, and Vincenzo Stornelli. 2019. "A VCII-Based Stray Insensitive Analog Interface for Differential Capacitance Sensors" Sensors 19, no. 16: 3545. https://doi.org/10.3390/s19163545