An Ultra-Low-Power RFID/NFC Frontend IC Using 0.18 μm CMOS Technology for Passive Tag Applications

Abstract

:1. Introduction

- First and foremost, priority is given to low power consumption and smaller IC area which are the two key parameters for low-power, low-cost electronics.

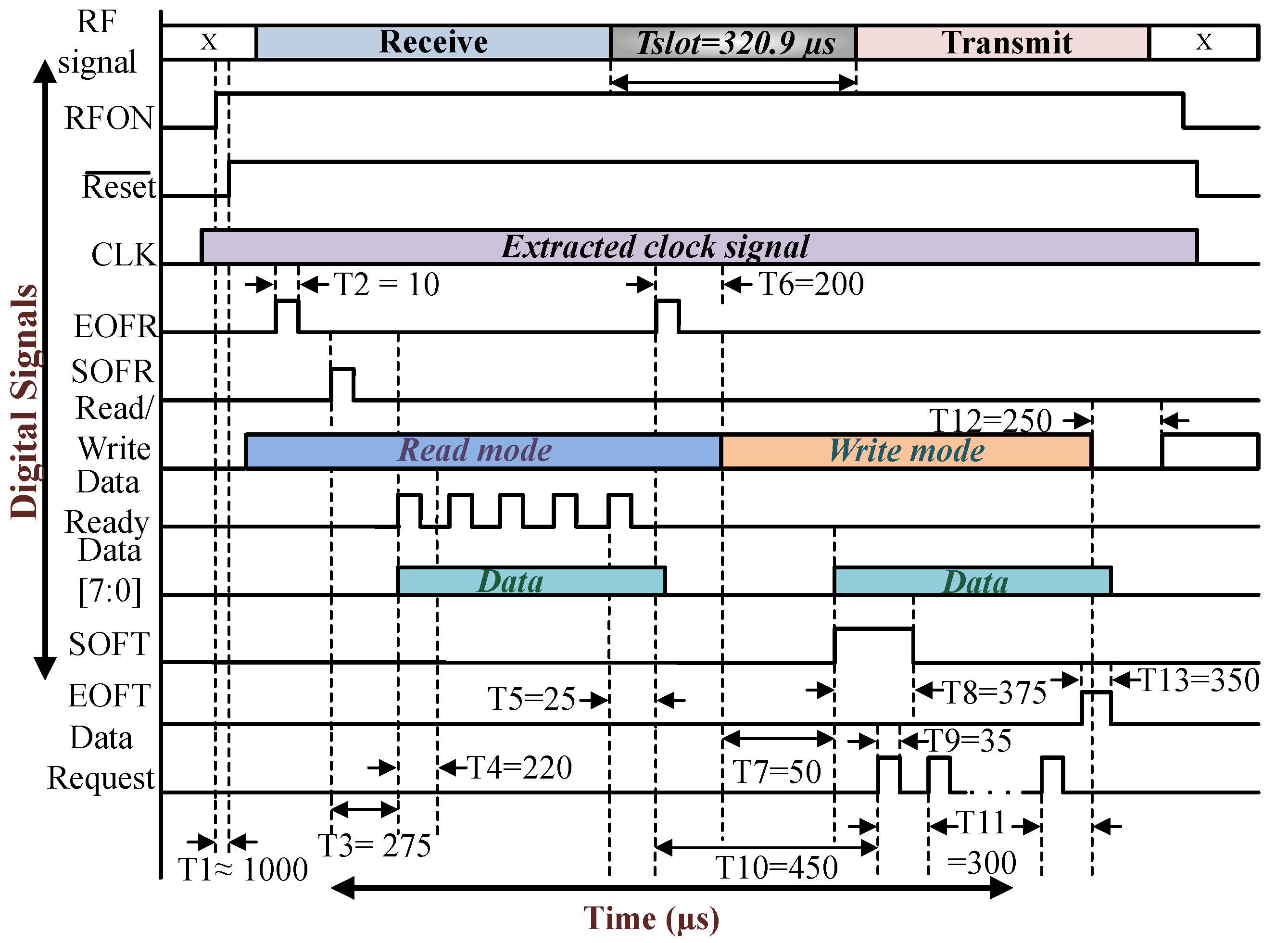

- The digital interface and the RF transceiver are designed in accordance with the ISO/IEC 15693/NFC5 standard.

- As already discussed, the demodulation of the 10% ASK signal is challenging. An innovative and inexpensive method of ASK demodulation, comprising a comparator with a preset offset, is used for the design. The theoretical analysis of the comparator offset voltage depending on the operating region is discussed in detail in the paper. The primary advantage of this method is its simplicity, as it involves no complex circuitry.

- For the envelope detection of the ASK modulated signal, most of the designs use a resistor as a load, whereas for this design the power consumption of the bandgap reference circuit is used as the load. For this, it is essential that the bandgap reference circuit is stable and can operate with the substantial power supply noise. This approach helps to avoid an extra component like a resistor to be used exclusively by the envelope detector circuit, hence reducing the IC area and the power consumption.

- At the architectural level, multiple power supplies and sub-threshold region operations are used wherever possible to keep the power consumption low.

- A figure-of-merit (FOM) proposed in this paper is used for the comparison with other related works.

Organization of the Paper

2. System Model and Architecture

3. Low Power Design Techniques Used for the Analog Design

- Weak inversion or sub-threshold operation is used wherever possible to keep the power consumption low. The sub-threshold drain current can be given as:

- Another method to reduce the overall power consumption is to use multiple power supply. Some of the analog circuits are driven by fixed supply voltage of = , which is discussed later in Section 4.

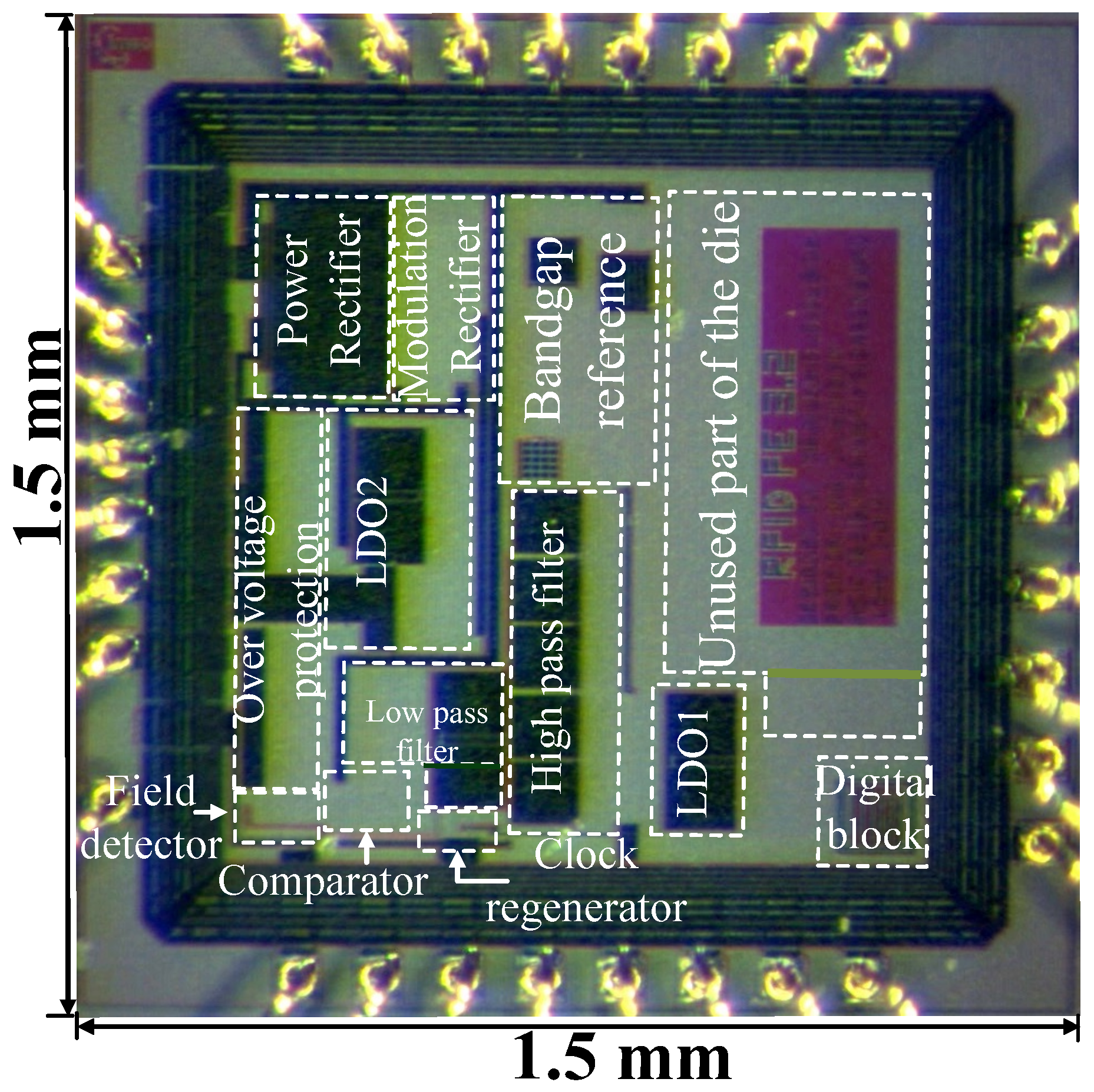

4. Analog Block

- Power supply and management unit

- Communication unit

- Field detector unit

- Clock regenerator.

4.1. Power Supply and Management

4.1.1. Over-Voltage Protection

4.1.2. Power Rectifier Circuit

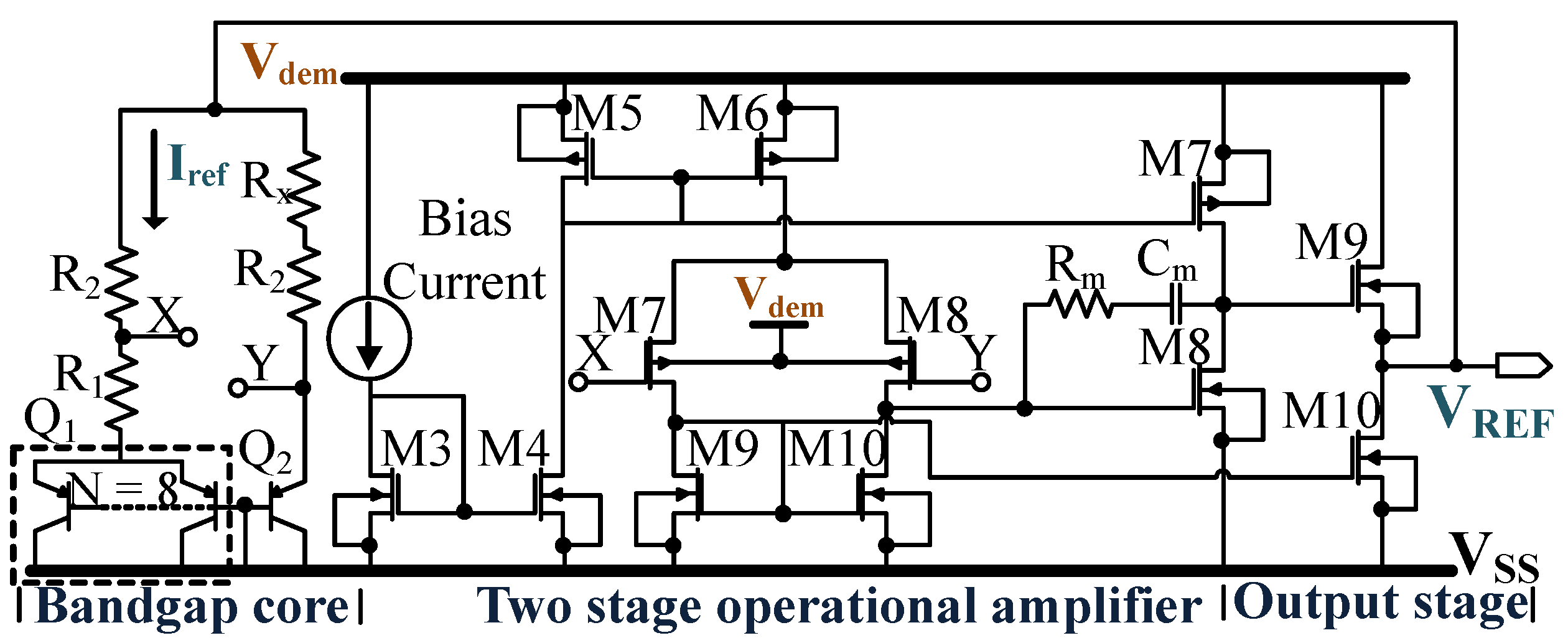

4.1.3. Bandgap Reference

4.1.4. Low Drop out Regulator Circuit (LDO2 & LDO1)

4.2. Communication unit

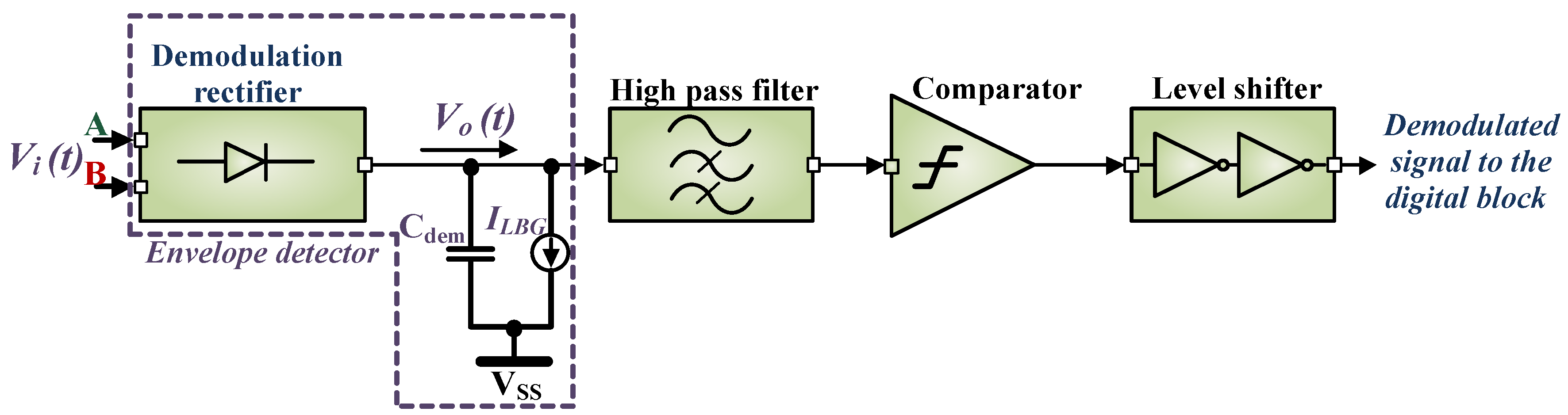

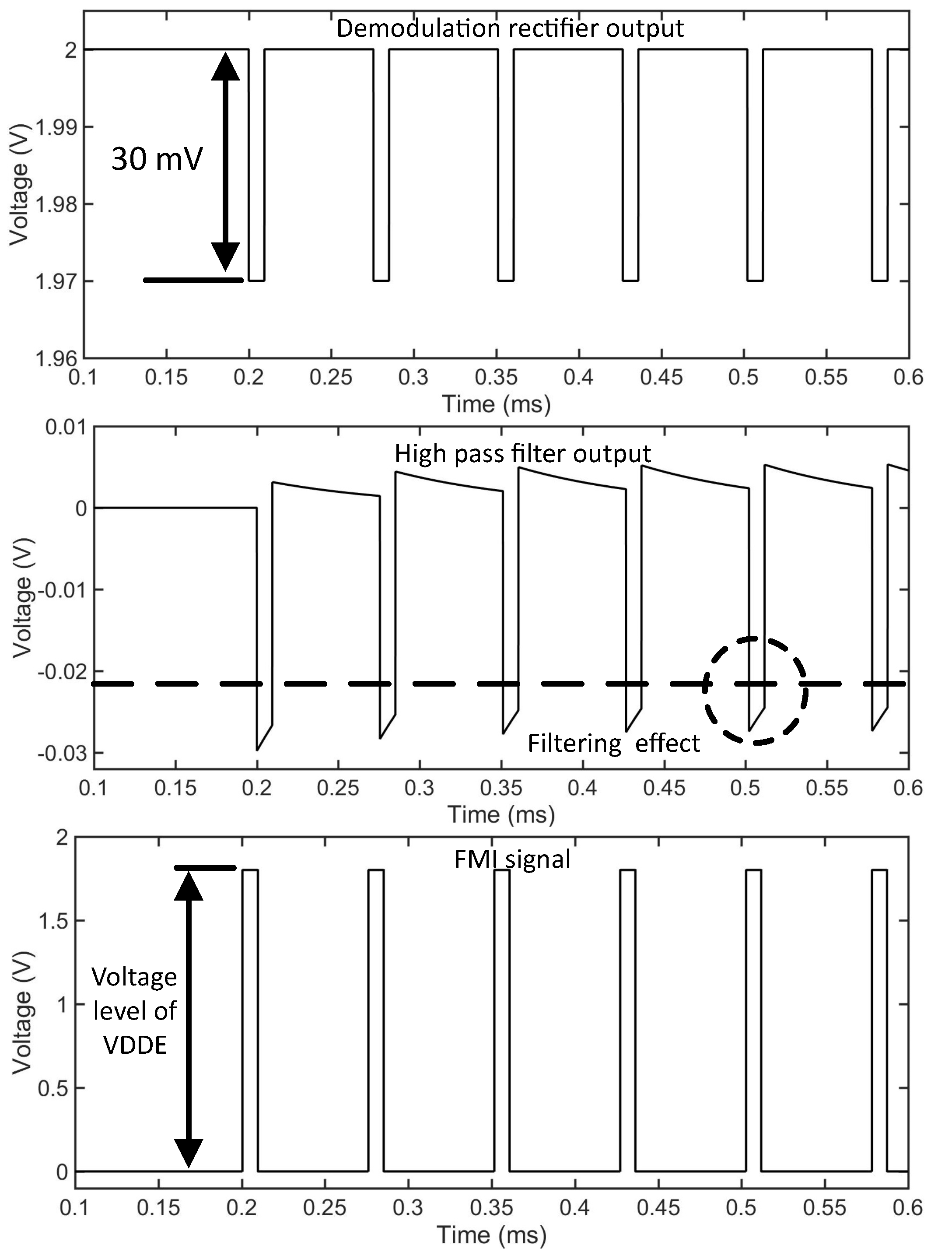

4.2.1. Demodulation and Envelope Detector Circuit

4.2.2. Comparator with High Pass Filter and Level Shifter

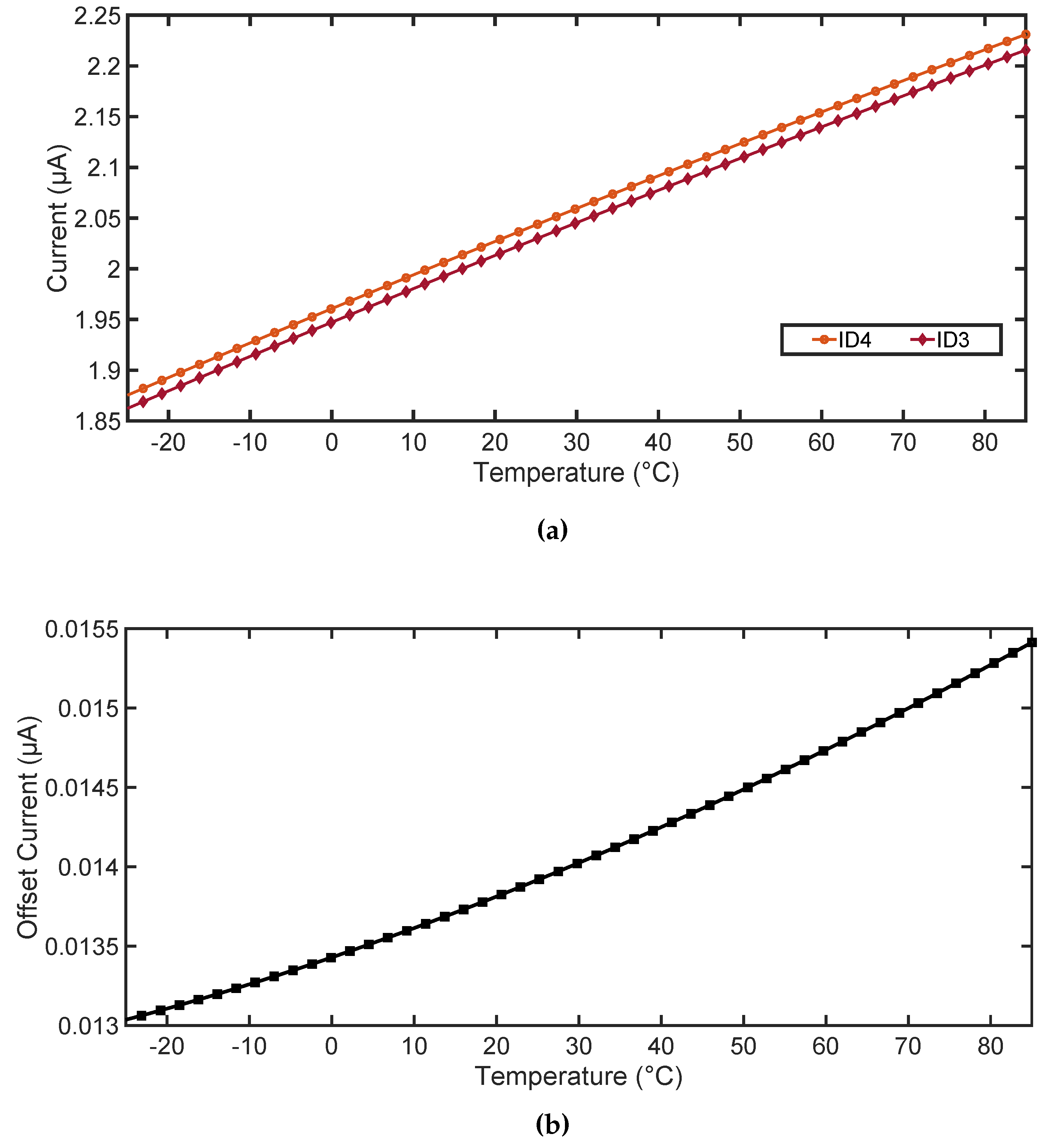

- In weak inversion region, the variation in the drain current is the major contributor to the mismatches in absence of any .

- The tolerances or spreading in the process factor and the device dimensions are the principal reason behind the offset voltage in the strong inversion region.

- The overall offset voltage is much smaller in the weak inversion region in comparison to the strong inversion one.

- In the weak inversion region, the offset voltage will largely depend on the variation created in the tail current of the differential pair due to , which can be achieved by using a relatively small value of .

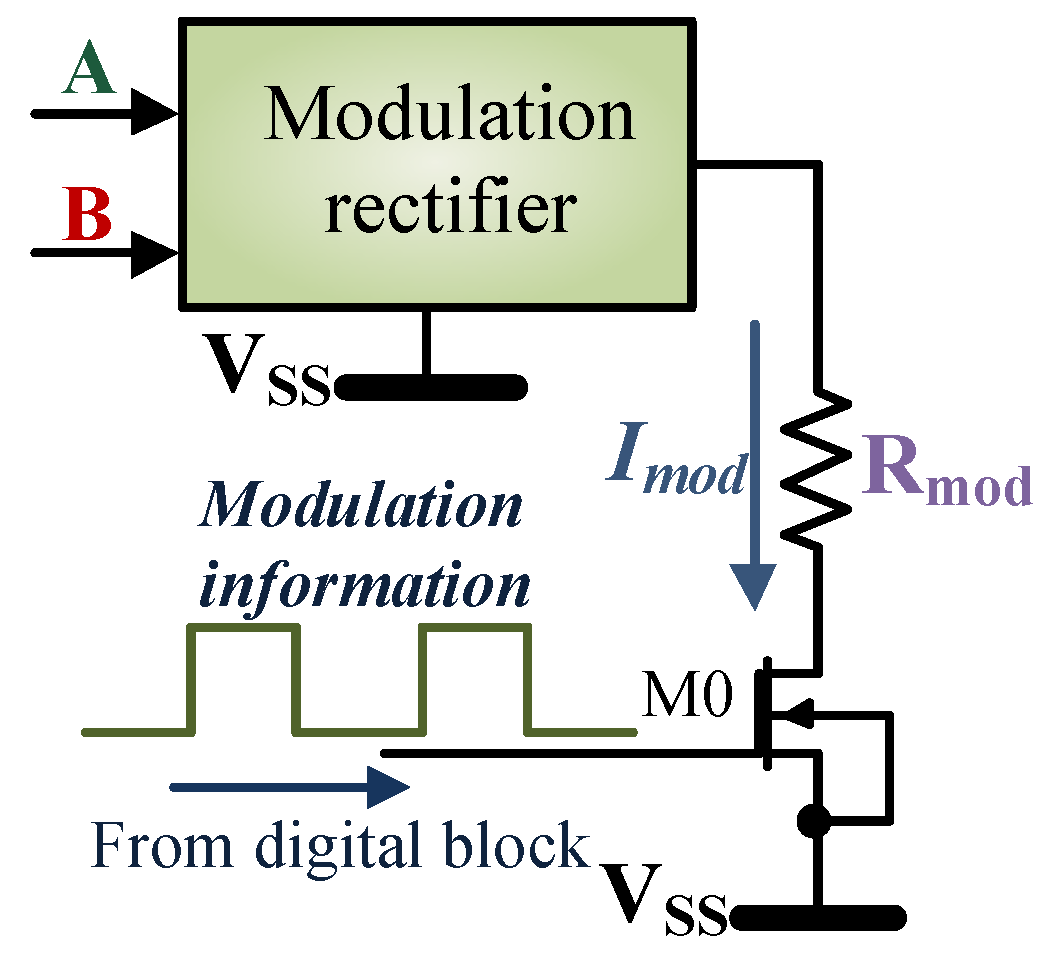

4.2.3. Modulator

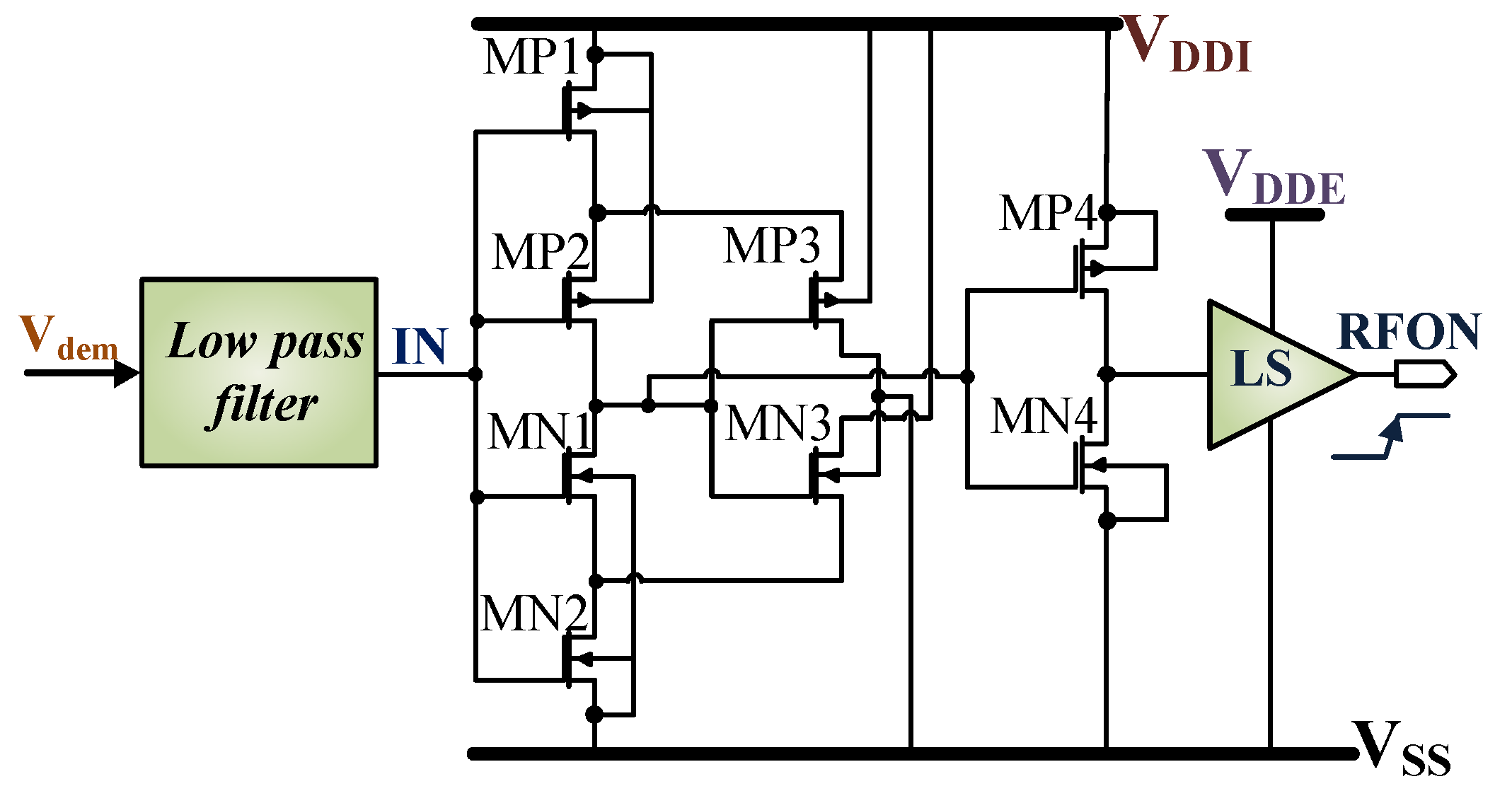

4.2.4. Field Detector

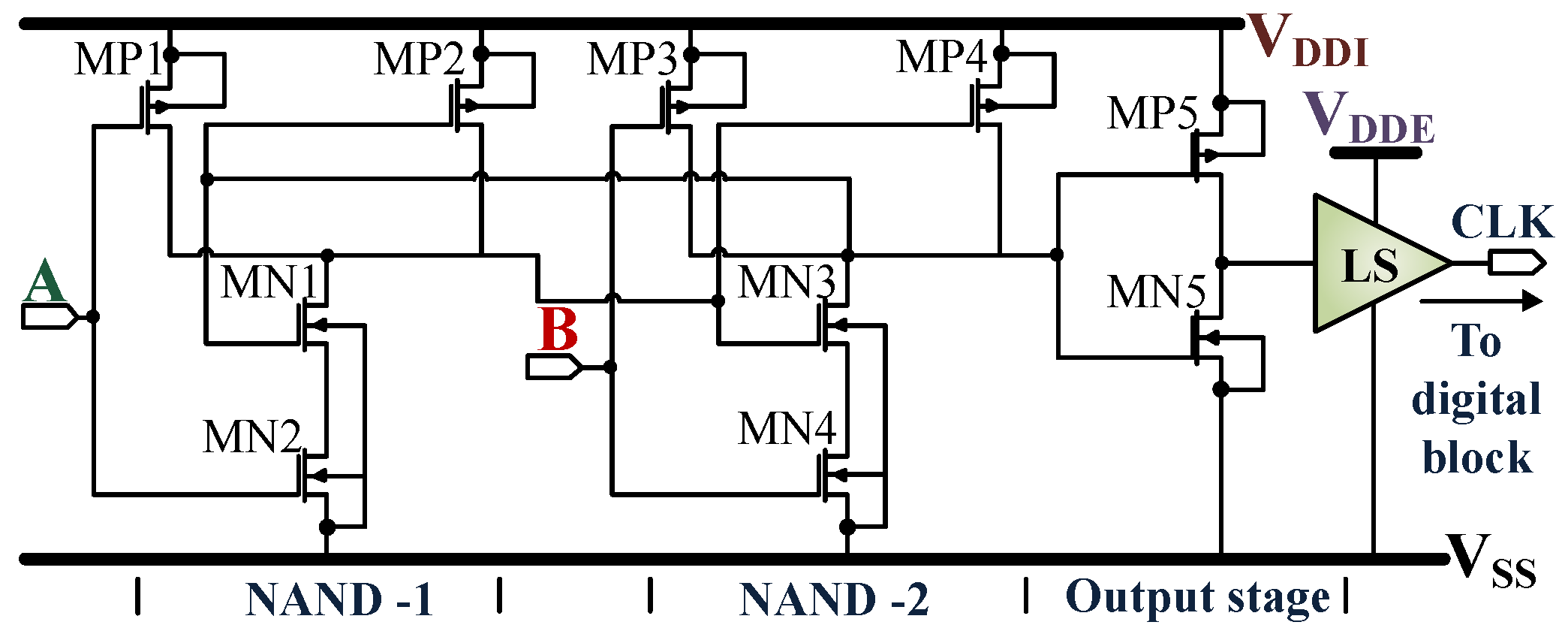

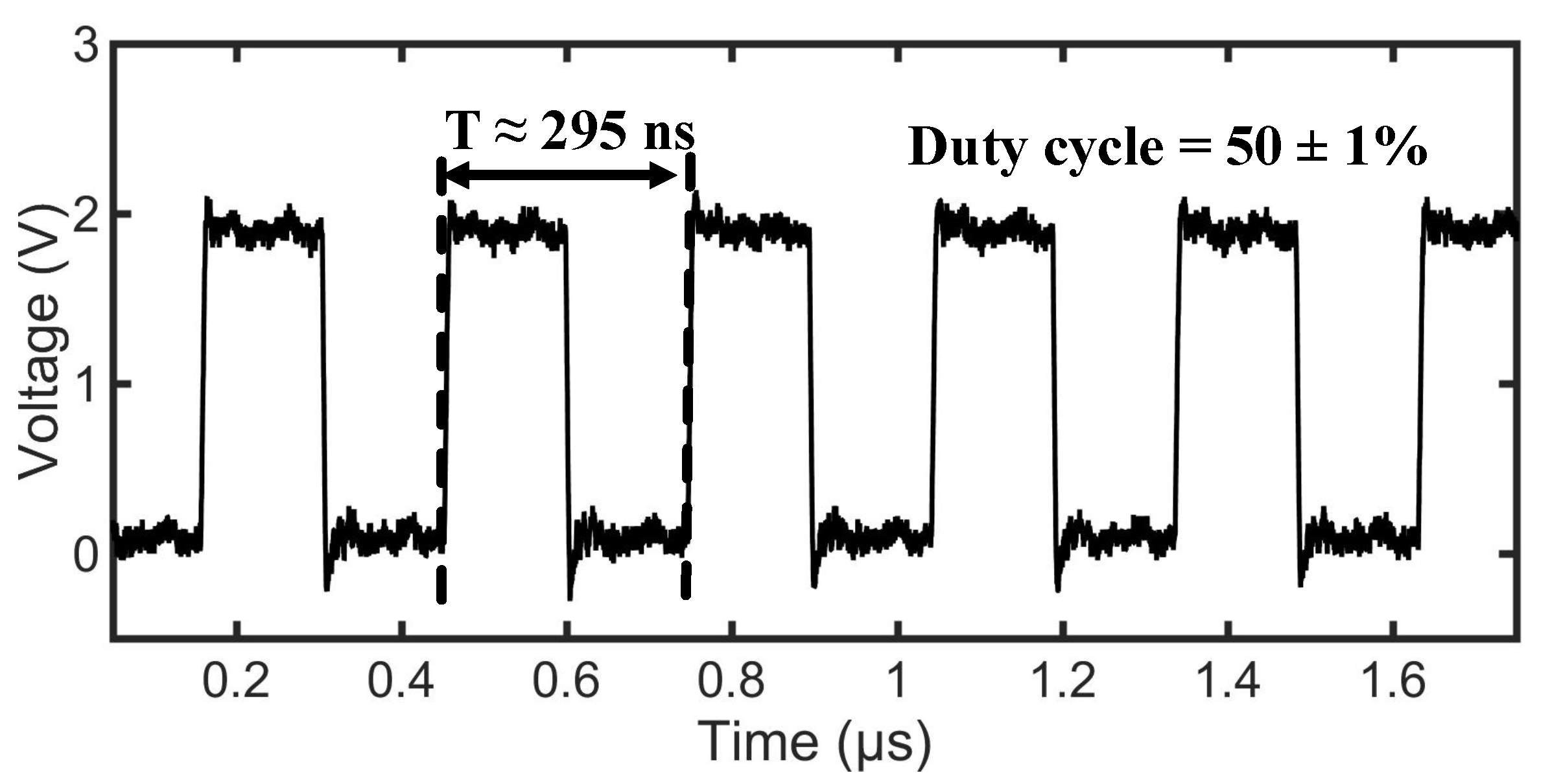

4.2.5. Clock Regenerator

4.3. Summary of the Analog Block

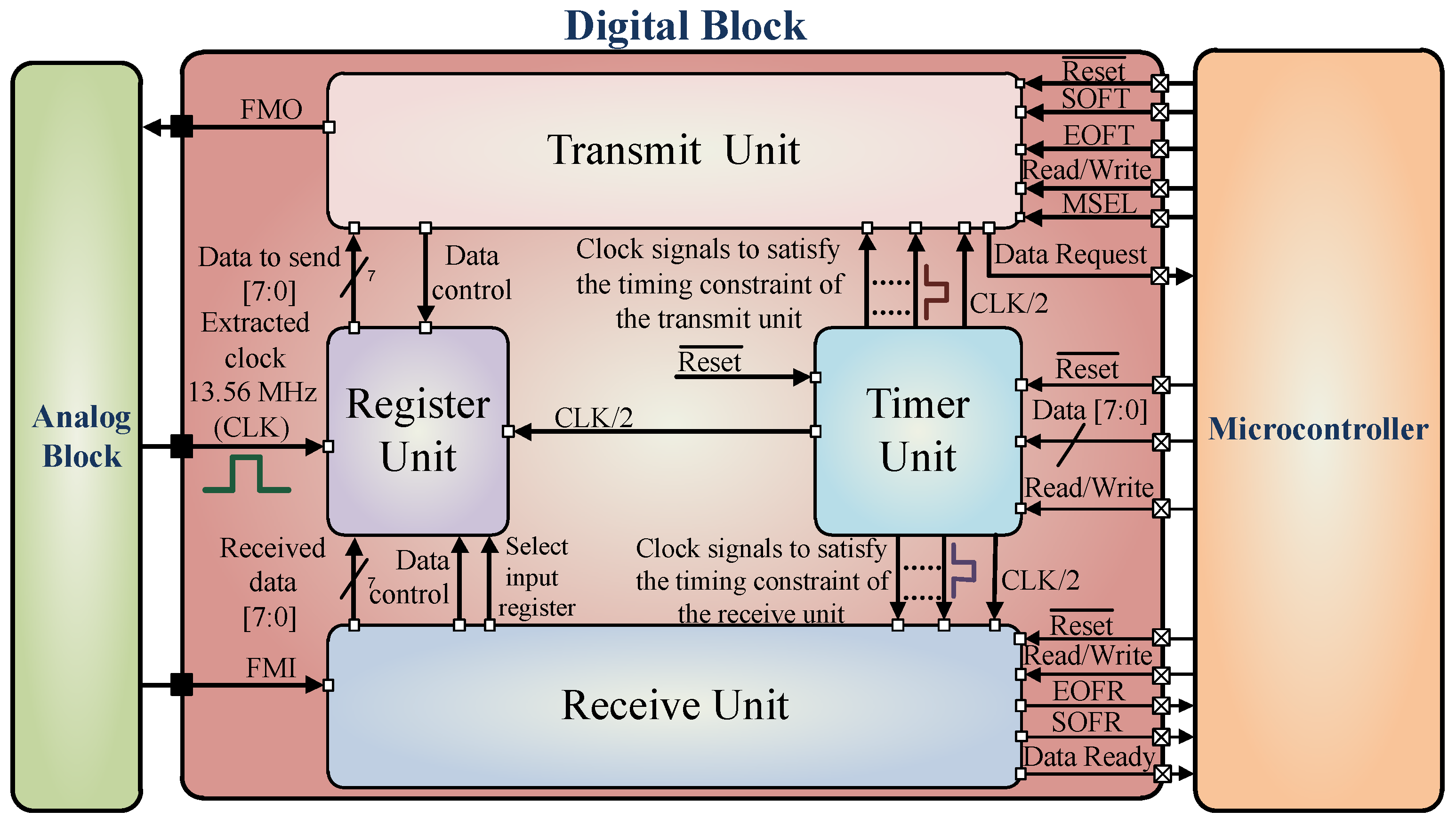

5. Digital Block

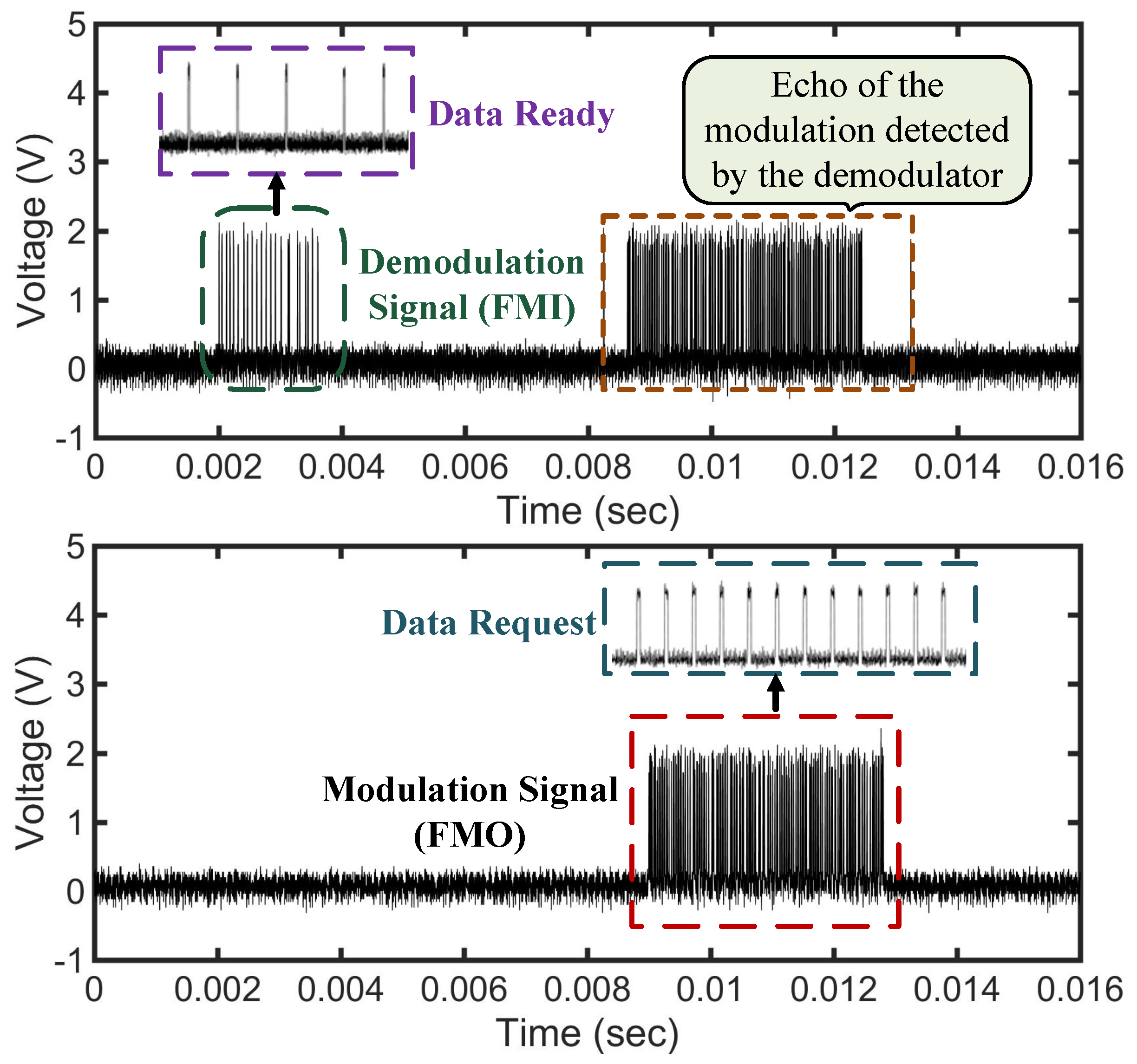

6. Measurement Results and Discussion

6.1. Power Supply and Management Block Measurements

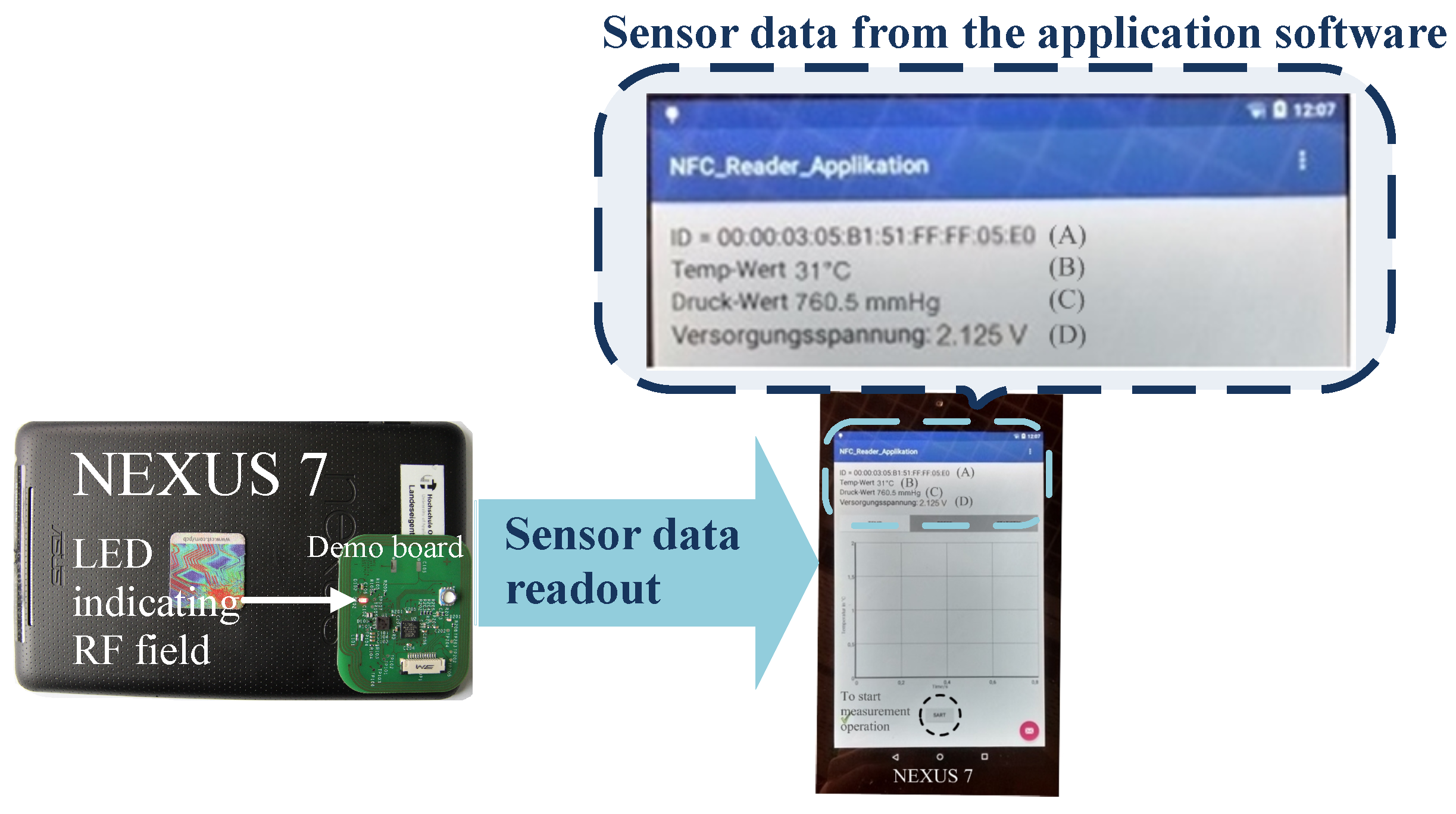

6.2. Functional Test with a Passive Tag

7. Conclusions

Author Contributions

Acknowledgments

Conflicts of Interest

References

- Cardullo, M.W. Transponder Apparatus and System. U.S. Patent 3,713,148, 23 January 1973. [Google Scholar]

- Landt, J. The History of RFID. IEEE Potentials 2005, 24, 8–11. [Google Scholar] [CrossRef]

- Lu, C.H.; Li, J.A.; Lin, T.H. A 13.56-MHz passive (NFC) tag IC in 0.18-μm CMOS process for biomedical applications. In Proceedings of the International Symposium on VLSI Design, Automation and Test (VLSI-DAT), Hsinchu, Taiwan, 25–27 April 2016; pp. 1–4. [Google Scholar]

- Lien, W.L.; Choke, T.Y.; Tan, Y.C.; Kong, M.; Low, E.C.; Li, D.P.; Jin, L.; Zhang, H.; Leow, C.H.; Chew, S.L.; et al. A Self-Calibrating NFC SoC with a Triple-Mode Reconfigurable PLL and a Single-Path PICC-PCD Receiver in 0.11 μm CMOS. In Proceedings of the IEEE International Solid-State Circuits Conference Digest of Technical Papers (ISSCC), San Francisco, CA, USA, 9–13 February 2014; pp. 158–159. [Google Scholar]

- NFC Type 1 Tag Operation Specification; NFC Forum, Inc.: Wakefield, MA, USA, 13 April 2011.

- NFC Type 2 Tag Operation Specification; NFC Forum, Inc.: Wakefield, MA, USA, 31 May 2011.

- NFC Type 3 Tag Operation Specification; NFC Forum, Inc.: Wakefield, MA, USA, 28 June 2011.

- NFC Type 4 Tag Operation Specification; NFC Forum, Inc.: Wakefield, MA, USA, 28 June 2011.

- NFC Type 5 Tag Operation Specification; NFC Forum, Inc.: Wakefield, MA, USA, 14 October 2015.

- Zhou, S.; Sheng, W.; Deng, F.; Wu, X.; Fu, Z. A Novel Passive Wireless Sensing Method for Concrete Chloride Ion Concentration Monitoring. Sensors 2017, 17, 2817. [Google Scholar] [CrossRef] [PubMed]

- Falco, A.; Salmerón, J.F.; Loghin, F.C.; Lugli, P. Fully Printed Flexible Single-Chip RFID Tag with Light Detection Capabilities. Sensors 2017, 17, 534. [Google Scholar] [CrossRef] [PubMed]

- Svete, T.; Suhadolnik, N.; Pleteršek, A. The Implementation of a High-Frequency Radio Frequency Identification System with a Battery-Free Smart Tag for Orientation Monitoring. Electronics 2016, 6, 6. [Google Scholar] [CrossRef]

- Deng, F.; He, Y.; Zhang, C.; Feng, W. A CMOS Humidity Sensor for Passive RFID Sensing Applications. Sensors 2014, 14, 8728–8729. [Google Scholar] [CrossRef] [PubMed]

- Seco, F.; Jiménez, A.R. Smartphone-Based Cooperative Indoor Localization with RFID Technology. Sensors 2017, 18, 1–23. [Google Scholar]

- Hsu, C.C.; Chen, J.H. A Novel Sensor-Assisted RFID-Based Indoor Tracking System for the Elderly Living Alone. Sensors 2011, 11, 10094–10113. [Google Scholar] [CrossRef] [PubMed]

- Chiou, J.C.; Hsu, S.H.; Huang, Y.C.; Yeh, G.T.; Liou, W.T.; Kuei, C.K. A Wirelessly Powered Smart Contact Lens with Reconfigurable Wide Range and Tunable Sensitivity Sensor Readout Circuitry. Sensors 2016, 17, 108. [Google Scholar] [CrossRef] [PubMed]

- Caldara, M.; Nodari, B.; Re, V.; Bonandrini, B. Miniaturized Blood Pressure Telemetry System with RFID Interface. Electronics 2016, 5, 51. [Google Scholar] [CrossRef]

- Xiao, Z.; Tan, X.; Chen, X.; Chen, S.; Zhang, Z.; Zhang, H.; Wang, J.; Huang, Y.; Zhang, P.; Zheng, P.; et al. An Implantable RFID Sensor Tag toward Continuous Glucose Monitoring. IEEE Trans. Biomed. Circuits Syst. 2015, 19, 910–919. [Google Scholar] [CrossRef] [PubMed]

- Volk, T.; Gorbey, S.; Bhattacharyya, M.; Grünwald, W.; Lemmer, B.; Reindl, L.M.; Stieglitz, T.; Jansen, D. RFID Technology for Continuous Monitoring of Physiological Signals in Small Animals. IEEE Trans. Biomed. Circuits Syst. 2015, 62, 4365–4373. [Google Scholar] [CrossRef] [PubMed]

- Cheong, J.H.; Ng, S.S.Y.; Liu, X.; Xue, R.-F.; Lim, H.-F.; Khannur, P.B.; Chan, K.L.; Lee, A.A.; Kang, K.; Lim, L.S.; et al. An Inductively Powered Implantable Blood Flow Sensor Microsystem for Vascular Grafts. IEEE Trans. Biomed. Eng. 2012, 59, 2466–2475. [Google Scholar] [CrossRef] [PubMed]

- Yoo, J.; Yan, L.; Lee, S.; Kim, Y.; Yoo, H.J. A 5.2 mW Self-Configured Wearable Body Sensor Network Controller and a 12 μW Wirelessly Powered Sensor for a Continuous Health Monitoring System. IEEE J. Solid-State Circuits 2010, 45, 178–188. [Google Scholar] [CrossRef]

- Wang, D.; Hu, J.; Tan, H.Z. A Highly Stable and Reliable 13.56-MHz RFID Tag IC for Contactless Payment. IEEE Trans. Ind. Electron. 2015, 62, 545–554. [Google Scholar] [CrossRef]

- Rodrigues, H.; Jose, R.; Coehlo, A.; Melro, A.; Ferreira, M.C.; Fanlcao e Cunha, J.; Monteiro, M.P.; Ribeiro, C. MobiPag: Integrated Mobile Payment, Ticketing and Couponing Solution Based on NFC. Sensors 2014, 14, 13389–13415. [Google Scholar] [CrossRef] [PubMed]

- Borrego-Jaraba, F.; Castro Garrido, P.; Garcia, G.; Ruiz, I.L.; Gomez-Nieto, A. A Ubiquitous NFC Solution for the Development of Tailored Marketing Strategies Based on Discount Vouchers and Loyalty Cards. Sensors 2013, 13, 6334–6354. [Google Scholar] [CrossRef] [PubMed]

- Palma, D.; Agudo, J.E.; Sánchez, H.; Macías, M.M. An Internet of Things Example: Classrooms Access Control over Near Field Communication. Sensors 2014, 14, 6998–7012. [Google Scholar] [CrossRef] [PubMed]

- Echevarria, J.J.; Ruiz-de-Garibay, J.; Legarda, J.; Alvarez, M.; Ayerbe, A.; Vazquez, J.I. WebTag: Web Browsing into Sensor Tags over NFC. Sensors 2012, 12, 8675–8690. [Google Scholar] [CrossRef] [PubMed]

- Gong, C.; Liu, D.; Miao, Z.; Wang, W.; Li, M. An NFC on Two-Coil WPT Link for Implantable Biomedical Sensors under Ultra-Weak Coupling. Sensors 2017, 17, 1358. [Google Scholar] [CrossRef] [PubMed]

- Donida, A.; Di-Dato, G.; Cunzolo, P.; Sala, M.; Piffaretti, F.; Orsatti, P.; Barrettino, D. A Circadian and Cardiac Intraocular Pressure Sensor for Smart Implantable Lens. IEEE Trans. Biomed. Circuits Syst. 2015, 9, 777–789. [Google Scholar] [CrossRef] [PubMed]

- Izumi, S.; Yamashita, K.; Nakano, M.; Kawaquchi, H.; Kimura, H.; Marumoto, K.; Fuchikami, T.; Fujimori, Y.; Nakajima, H.; Shiga, T.; et al. A Wearable Healthcare System With a 13.7 μA Noise Tolerant ECG Processor. IEEE Trans. Biomed. Circuits Syst. 2015, 9, 733–742. [Google Scholar] [CrossRef] [PubMed]

- Dehennise, A.D.; Mailand, M.; Grice, D.; Getzlaff, S.; Colvin, A.E. A Near-Field-Communication (NFC) Enabled Wireless Fluorimeter for Fully Implantable Biosensing Applications. In Proceedings of the 2013 IEEE International Solid-State Circuits Conference Digest of Technical Papers (ISSCC), San Francisco, CA, USA, 17–21 February 2013; pp. 298–299. [Google Scholar]

- Meillere, S.; Barthelemy, H.; Martin, M. 13.56 MHz CMOS transceiver for RFID applications. Analog Integr. Circuits Signal Process. 2006, 49, 249–256. [Google Scholar] [CrossRef]

- Hwang, Y.S.; Lin, H.C. A New CMOS Analog Front End for RFID Tags. IEEE Trans. Ind. Electron. 2009, 56, 2299–2307. [Google Scholar] [CrossRef]

- Lee, J.W.; Vo, D.H.T.; Huynh, Q.H.; Hong, S.H. A Fully Integrated HF-Band Passive RFID Tag IC Using 0.18 μm CMOS Technology for Low-Cost Security Applications. IEEE Trans. Ind. Electron. 2011, 58, 2531–2540. [Google Scholar] [CrossRef]

- Lee, J.W.; Vo, D.; Hong, S.H.; Huynh, Q.H. A fully integrated high security NFC target IC using 0.18 μm CMOS process. In Proceedings of the ESSCIRC (ESSCIRC), Helsinki, Finland, 12–16 September 2011; pp. 551–554. [Google Scholar]

- Cho, J.H.; Kim, J.; Kim, J.W.; Lee, K.; Ahn, K.D.; Kim, S. An NFC transceiver with RF-powered RFID transponder mode. In Proceedings of the IEEE Asian Solid-State Circuits Conference, Jeju, Korea, 12–14 November 2007; pp. 172–175. [Google Scholar]

- Finkenzeller, K. RFID Handbook: Fundamentals and Applications in Contactless Smart Cards, Radio Frequency Identification and Near-Field Communication; Addison-Wesley: Boston, MA, USA, 2010. [Google Scholar]

- Van Schuylenbergh, K.; Puers, R. Inductive Powering: Basic Theory and Application to Biomedical Systems (Analog Circuits and Signal Processing); Springer: Berlin, Germany, 2009. [Google Scholar]

- Lenaerts, B.; Puers, R. Omnidirectional Inductive Powering for Biomedical Implants (Analog Circuits and Signal Processing); Springer: Dordrecht, The Netherlands, 2009. [Google Scholar]

- Kazemzadeh, R.; Schnick, O.; John, W.; Mathis, W. Efficient Network Modeling of Inductively Coupled NFC Antennas in Medical Wireless Sensor Applications. In Proceedings of the 2012 International Symposium on Signals Systems, and Electronics (ISSSE), Potsdam, Germany, 3–5 October 2012; pp. 1–6. [Google Scholar]

- Scholz, P.; Ackermann, W.; Weiland, T.; Reinhold, C. Antenna Modeling for Inductive RFID Applications Using the Partial Element Equivalent Circuit Method. Proc. IEEE Trans. Mag. 2010, 46, 2967–2970. [Google Scholar] [CrossRef]

- Reinhold, C.; Scholz, P.; John, W.; Hilleringmann, U. Efficient Antenna Design of Inductive Coupled RFID-Systems with High Power Demand. IEEE J. Commun. 2007, 2, 14–23. [Google Scholar] [CrossRef]

- Chen, L.; Liu, S.; Zhou, Y.C.; Cui, T.J. An Optimizable Circuit Structure for High-Efficiency Wireless Power Transfer. IEEE Trans. Ind. Electron. 2013, 60, 339–349. [Google Scholar] [CrossRef]

- Volk, T.; Bhattacharyya, M.; Grünwald, W.; Reindl, L.M.; Jansen, D. Formal Description of Inductive Air Interfaces Using Thévenin’s Theorem and Numerical Analysis. Proc. IEEE Trans. Mag. 2014, 50, 1–9. [Google Scholar]

- Alioto, M. Ultra-Low Power VLSI Circuit Design Demystified and Explained: A Tutorial. IEEE Trans. Circuits Syst. I Regul. Pap. 2012, 59, 3–29. [Google Scholar] [CrossRef]

- Sarpeshkar, R. Universal Principles for Ultra Low Power and Energy Efficient Design. IEEE Trans. Circuits Syst. II 2012, 59, 193–198. [Google Scholar] [CrossRef]

- Comer, D.J.; Comer, D.T. Using the Weak Inversion Region to Optimize Input Stage Design of CMOS Op Amps. IEEE Trans. Circuits Syst. II 2004, 51, 8–14. [Google Scholar] [CrossRef]

- Rabaey, J. Low Power Design Essentials; Springer: New York, NY, USA, 2009. [Google Scholar]

- Vittoz, E.A. Weak Inversion for Ultra Low-Power and Very Low-Voltage Circuits. In Proceedings of the IEEE Asian Solid-State Circuits Conference (A-SSCC)’ 2009, Taipei, Taiwan, 16–18 November 2009; pp. 129–132. [Google Scholar]

- Lotze, N.; Manoli, Y. Ultra-Sub-Threshold Operation of Always-On Digital Circuits for IoT Applications by Use of Schmitt Trigger Gates. IEEE Trans. Circuits Syst. I Regul. Pap. 2017, 64, 1–14. [Google Scholar] [CrossRef]

- Dongsheng, L.; Huan, L.; Xuecheng, Z.; Liang, G.; Ke, Y.; Zilong, L. A High Sensitivity Analog Front-end Circuit for Semi-Passive HF RFID Tag Applied to Implantable Devices. IEEE Trans. Circuits Syst. I Regul. Pap. 2015, 62, 1991–2002. [Google Scholar] [CrossRef]

- Li, X.; Tsui, C.Y.; Ki, W.H. A 13.56 MHz Wireless Power Transfer System With Reconfigurable Resonant Regulating Rectifier and Wireless Power Control for Implantable Medical Devices. IEEE J. Solid-State Circuits 2015, 50, 978–989. [Google Scholar] [CrossRef]

- Liu, D.; Wang, R.; Yao, K.; Zou, X.; Guo, L. Design and Implementation of a RF Powering Circuit for RFID Tags or Other Batteryless Embedded Devices. Sensors 2014, 14, 14839–14857. [Google Scholar] [CrossRef] [PubMed]

- Wu, C.Y.; Qian, X.H.; Cheng, M.S.; Liang, Y.A.; Chen, W.M. A 13.56 MHz 40 mW CMOS High-Efficiency Inductive Link Power Supply Utilizing On-Chip Delay-Compensated Voltage Doubler Rectifier and Multiple LDOs for Implantable Medical Devices. IEEE J. Solid-State Circuits 2014, 49, 2397–2407. [Google Scholar] [CrossRef]

- Haddad, P.A.; Gosset, G.; Raskin, J.P.; Flandre, D. Automated Design of a 13.56 MHz 19 μW Passive Rectifier with 72% Efficiency Under 10 μA load. IEEE J. Solid-State Circuits 2016, 51, 1290–1301. [Google Scholar] [CrossRef]

- De Carli, L.G.; Juppa, Y.; Cardoso, A.J.; Galup-Montoro, C.; Schneider, M.C. Maximizing the Power Conversion Efficiency of Ultra-Low-Voltage CMOS Multi-Stage Rectifiers. IEEE Trans. Circuits Syst. I Regul. Pap. 2015, 62, 967–975. [Google Scholar] [CrossRef]

- Cha, H.K.; Park, W.T.; Je, M. A CMOS Rectifier With a Cross-Coupled Latched Comparator for Wireless Power Transfer in Biomedical Applications. IEEE Trans. Circuits Syst. II 2012, 59, 409–413. [Google Scholar] [CrossRef]

- Widlar, R.J. New developments in IC voltage regulators. IEEE J. Solid-State Circuits 1971, SC-6, 2–7. [Google Scholar] [CrossRef]

- Tsividis, Y.P. Accurate analysis of temperature effects in IC/-VBE characteristics with application to bandgap reference sources. IEEE J. Solid-State Circuits 1980, SC-15, 1076–1084. [Google Scholar] [CrossRef]

- Duan, Q.; Roh, J. A 1.2-V 4.2-ppm/∘C High-Order Curvature-Compensated CMOS Bandgap Reference. IEEE Trans. Circuits Syst. I Regul. Pap. 2015, 62, 662–670. [Google Scholar] [CrossRef]

- Ma, B.; Yu, F. A Novel 1.2-V 4.5-ppm/∘C Curvature-Compensated CMOS Bandgap Reference. IEEE Trans. Circuits Syst. I Regul. Pap. 2014, 61, 1026–1035. [Google Scholar] [CrossRef]

- Maity, A.; Patra, A. A Single-Stage Low-Dropout Regulator With a Wide Dynamic Range for Generic Applications. IEEE Trans. Very Large Scale Integr. (VLSI) Syst. 2016, 24, 2117–2127. [Google Scholar] [CrossRef]

- Huang, C.H.; Ma, Y.T.; Liao, W.C. Design of a Low-Voltage Low-Dropout Regulator. IEEE Trans. Very Large Scale Integr. (VLSI) Syst. 2014, 22, 1308–1313. [Google Scholar] [CrossRef]

- Heng, S.; Pham, C.K. A Low-Power High-PSRR Low-Dropout Regulator With Bulk-Gate Controlled Circuit. IEEE Trans. Circuits Syst. II 2010, 57, 245–249. [Google Scholar] [CrossRef]

- Lau, S.K.; Mok, P.K.T.; Leung, K.N. A Low-Dropout Regulator for SoC With Q-Reduction. IEEE J. Solid-State Circuits 2007, 42, 658–664. [Google Scholar] [CrossRef]

- Bhattacharyya, M.; Gruenwald, W.; Jansen, D.; Reindl, L.; Aghassi-Hagmann, J. Design of a Programmable Passive SoC for Biomedical Applications Using RFID ISO 15693/NFC5 Interface. J. Low Power Electron. Appl. 2018, 8, 3. [Google Scholar] [CrossRef]

- Identification Cards–Contactless Integrated Circuit(s) Cards—Vicinity Cards—Part 2: Radio Frequency Power and Signal Interface; International Organization for Standardization: Geneva, Switzerland, 9 March 1999.

- Sansen, W. Analog Design Essentials; Springer: Dordrecht, The Netherlands, 2006. [Google Scholar]

- Li, Y.; Liu, J.; Lee, H. Ground Switching Load Modulation With Ground Isolation for Passive HF RFID Transponders. IEEE Trans. Very Large Scale Integr. (VLSI) Syst. 2012, 20, 1443–1452. [Google Scholar] [CrossRef]

- Identification Cards–Contactless Integrated Circuit(s) Cards–Vicinity Cards–Part 3: Anti-Collision and Transmission Protocol; Standard; International Organization for Standardization: Geneva, Switzerland, 10 March 2000.

- Identification Cards—Test Methods—Part 7: Vicinity Cards; International Organization for Standardization: Geneva, Switzerland, 10 March 2000.

- Darwhekar, Y.; Braginskiy, E.; Levy, K.; Agrawal, A.; Singh, V.; Issac, R.; Blonskey, O.; Adler, O.; Benkuzari, Y.; Ben-Shachar, M.; et al. A 45 nm CMOS Near-Field Communication Radio with 0.15 A/m RX Sensitivity and 4 mA Current Consumption in Card Emulation Mode. In Proceedings of the IEEE International Solid-State Circuits Conference Digest of Technical Papers (ISSCC), San Francisco, CA, USA, 17–21 February 2013; pp. 440–441. [Google Scholar]

| Type 1 [5] | Type 2 [6] | Type 3 [7] | Type 4 [8] | Type 5 [9] | |

|---|---|---|---|---|---|

| Supported | ISO/IEC | ISO/IEC | JIS X 6319 | ISO/IEC | ISO/IEC 15693 |

| standard | 14443 A | 14443 A | –4 ( Felica) | 14443 A/B | (18000-3) |

| Carrier | 13.56 MHz | ||||

| Frequency | ± 7 KHz | ||||

| Data rate | 106/212/ | ||||

| Modulation | ASK 100 % | ASK 100 % | ASK 10% | Standard A | 10% or |

| (Reader to Tag) | + ASK 10% | 100% ASK | |||

| Data coding | modified | modified | Manchester | NRZ-L (Std B) | Pulse position |

| (Reader to Tag) | Miller | Miller | MSB first | mod. 1 out of | |

| 256 / 1 out of 4 | |||||

| Modulation | Load | ASK 10% | Load | Standard A | Load mod. |

| modulation (ASK) | modulation | + Load mod. | |||

| (Tag to Reader ) | sub-carrier | with no | (BPSK) sub carrier | OOK/FSK | |

| (± ) | sub-carrier | (Std B) | sub-carrier | ||

| Data coding | Manchester | NRZ-L | Manchester | NRZ-L | Manchester |

| (Tag to Reader ) | |||||

| Anti-collision | No | Yes | Yes | Yes | Yes |

| Operation Status | |||

|---|---|---|---|

| a. | <1 | 1000 | No |

| b. | 2.5 | 600 | Yes |

| c. | 3 | 440 | Yes |

| d. | 3.6 | 220 | Yes |

| e. | 4.4 | 180 | No (voltage above safety level) |

| Parameter | Values |

|---|---|

| Carrier Frequency | ± |

| Modulation type and index | ASK 10% NRZ |

| Data rate (max) | |

| Operating temperature | −30 °C to 85 °C |

| Bandgap reference voltage | ± |

| Demodulation depth (min) | |

| Power consumption (analog) | |

| Mode of operation | Passive |

| Technology | CMOS |

| This Work | [3] | [34] | [33] | [32] | [35] | |

|---|---|---|---|---|---|---|

| CMOS process | 0.18 | 0.18 | 0.18 | 0.18 | 0.35 | 0.35 |

| (µm) | ||||||

| Protocol | RFID ISO 15693 | NFC | NFC | RFID ISO/ | RFID ISO/ | NFC |

| /NFC 5 | IEC 14443 (type-B) | IEC 18000 | ||||

| Data rate | 6.62 to 26.48 | 106 to 848 | 106 to 848 | 106 | 10 to 1000 | 106 to 212 |

| kbps | ||||||

| Power consumed | 107 | * | NA | 360 | 960 | NA |

| (µW) | ||||||

| Die area | Effective 0.7 | |||||

| (mm) | ||||||

| FOM | 9 | NA | NA | NA |

© 2018 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).

Share and Cite

Bhattacharyya, M.; Gruenwald, W.; Jansen, D.; Reindl, L.; Aghassi-Hagmann, J. An Ultra-Low-Power RFID/NFC Frontend IC Using 0.18 μm CMOS Technology for Passive Tag Applications. Sensors 2018, 18, 1452. https://doi.org/10.3390/s18051452

Bhattacharyya M, Gruenwald W, Jansen D, Reindl L, Aghassi-Hagmann J. An Ultra-Low-Power RFID/NFC Frontend IC Using 0.18 μm CMOS Technology for Passive Tag Applications. Sensors. 2018; 18(5):1452. https://doi.org/10.3390/s18051452

Chicago/Turabian StyleBhattacharyya, Mayukh, Waldemar Gruenwald, Dirk Jansen, Leonhard Reindl, and Jasmin Aghassi-Hagmann. 2018. "An Ultra-Low-Power RFID/NFC Frontend IC Using 0.18 μm CMOS Technology for Passive Tag Applications" Sensors 18, no. 5: 1452. https://doi.org/10.3390/s18051452