Failure Analysis in Magnetic Tunnel Junction Nanopillar with Interfacial Perpendicular Magnetic Anisotropy

Abstract

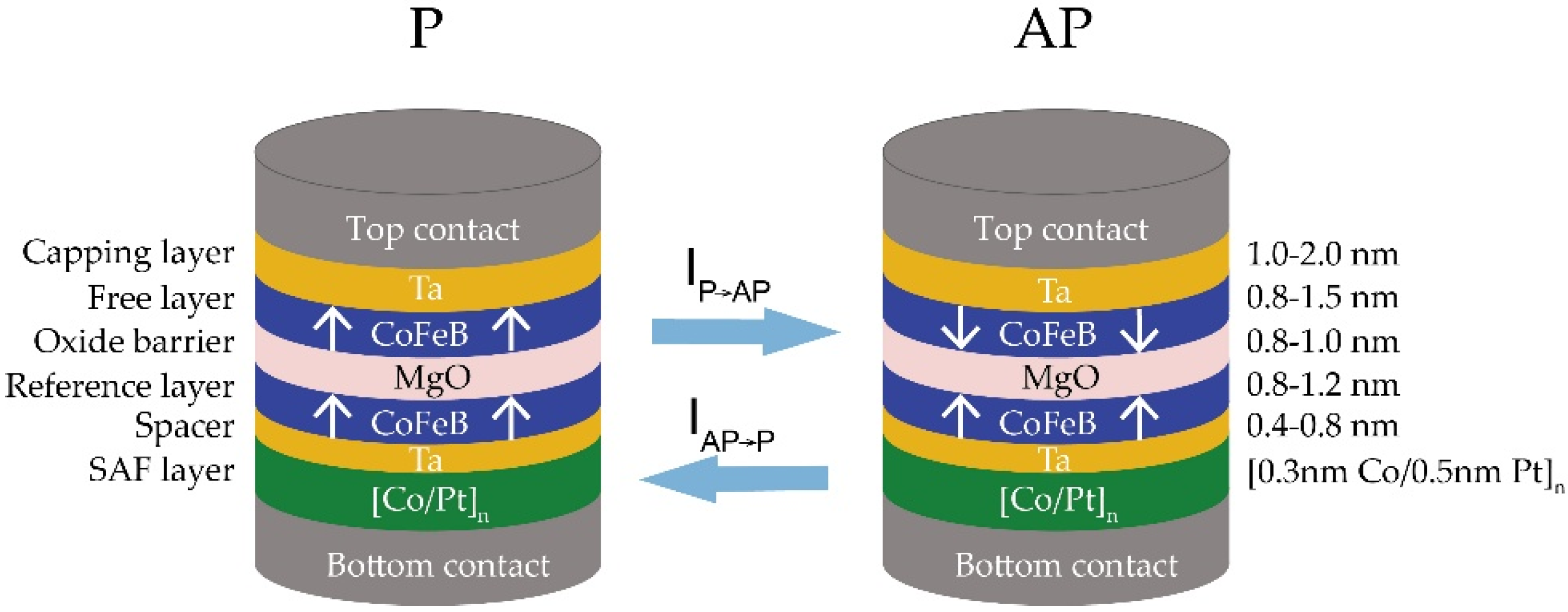

:1. Introduction

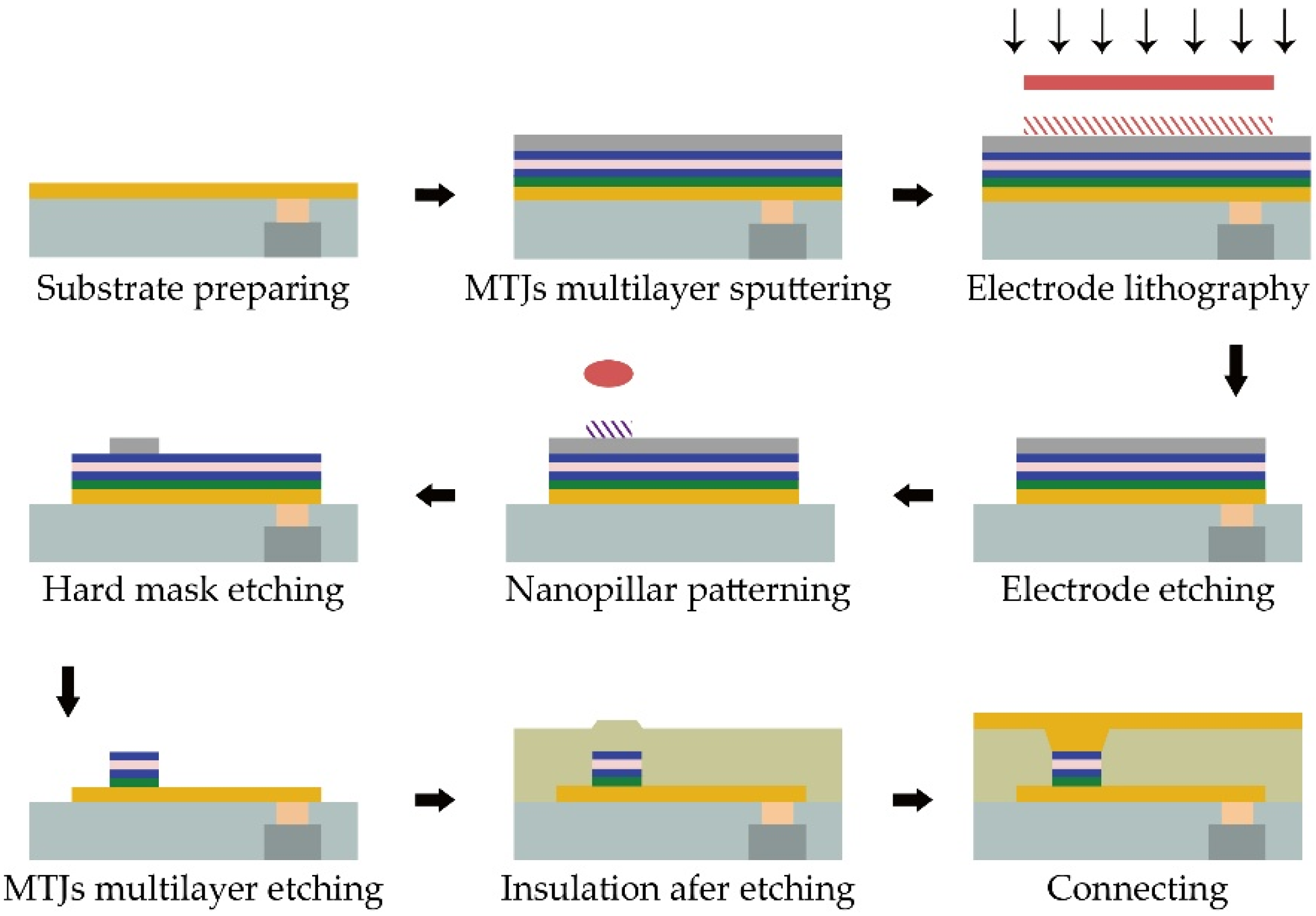

2. Failure Issues due to Nanofabrication of Magnetic Tunnel Junction Nanopillar with Perpendicular Magnetic Anisotropy

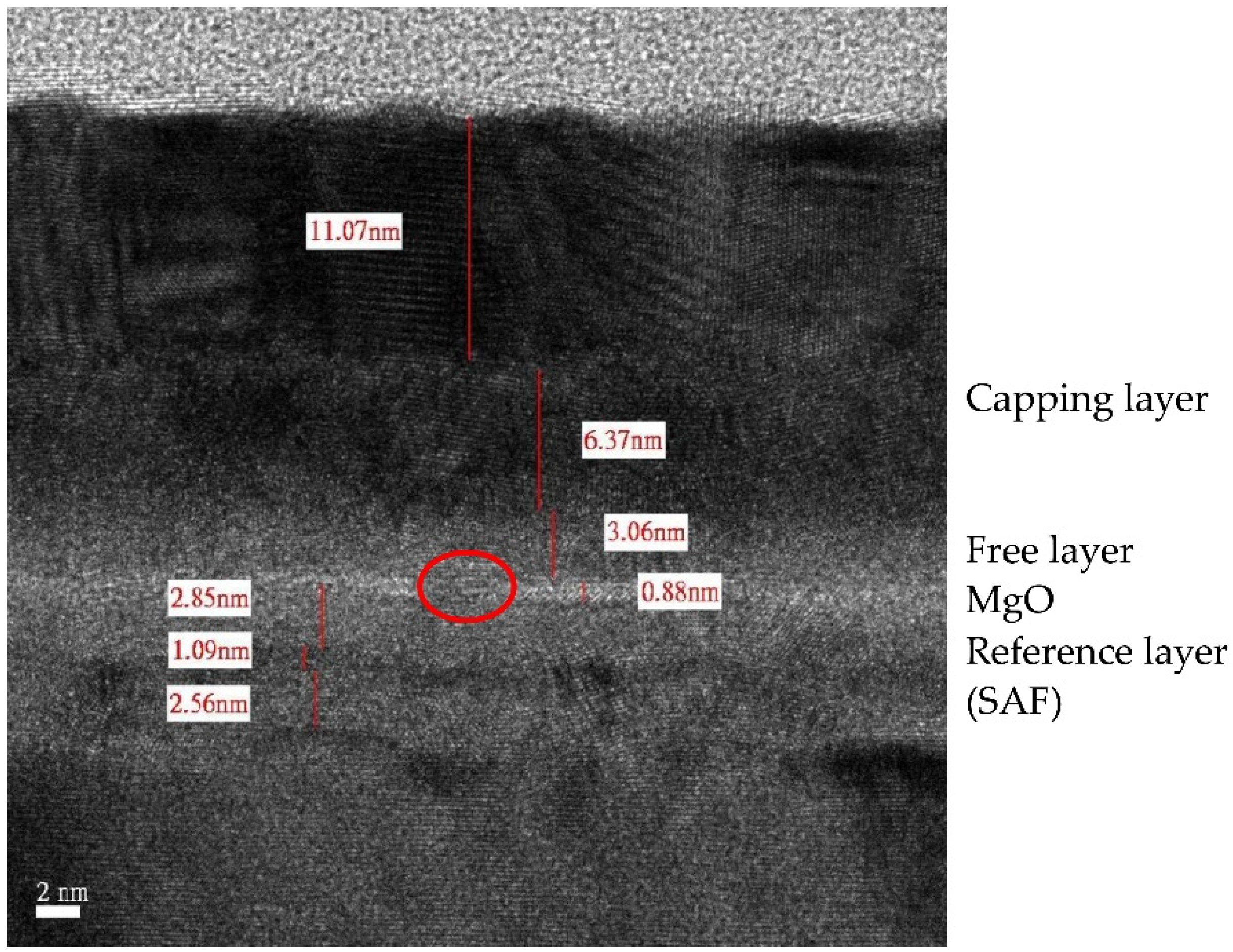

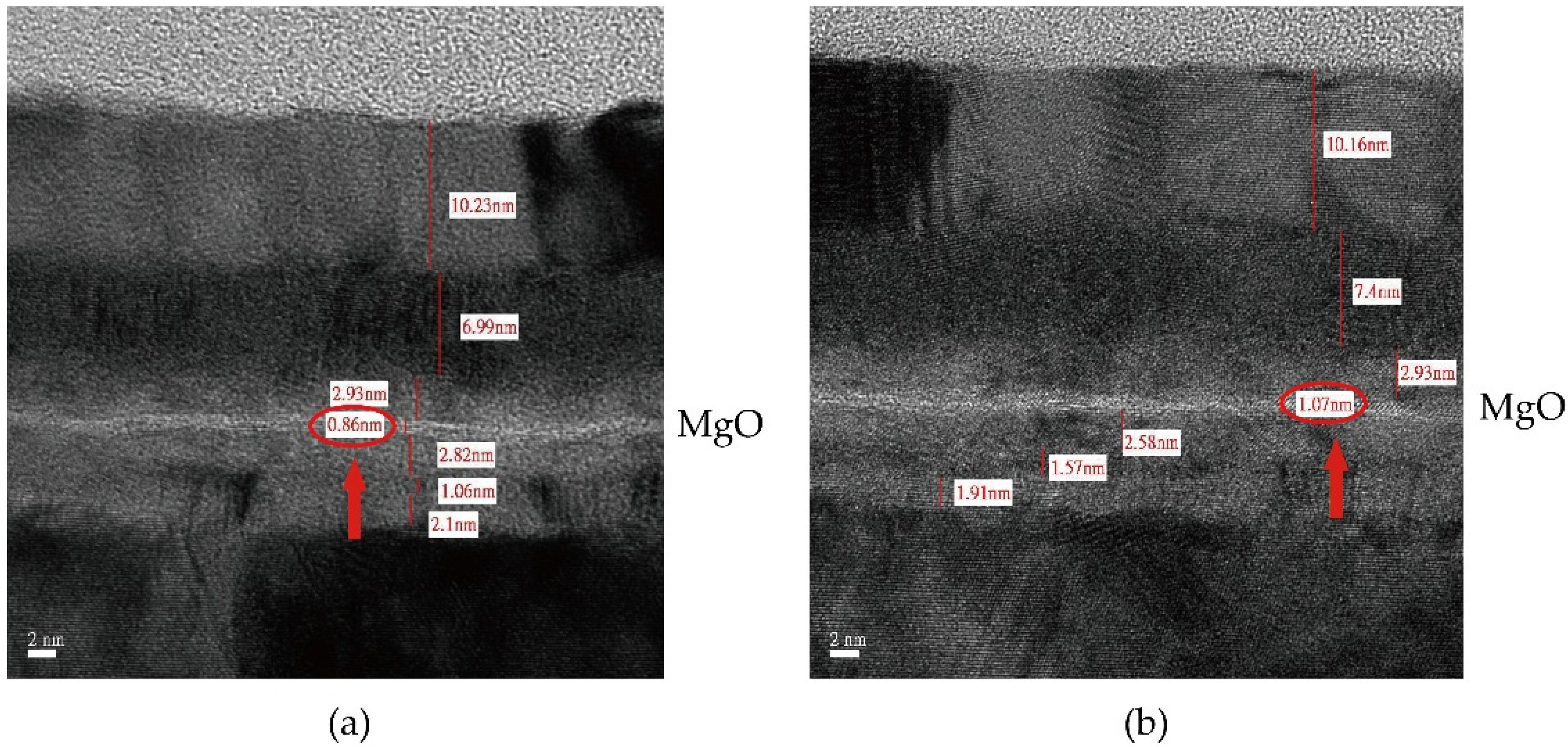

2.1. Failure Issues Caused by Deposition Variation

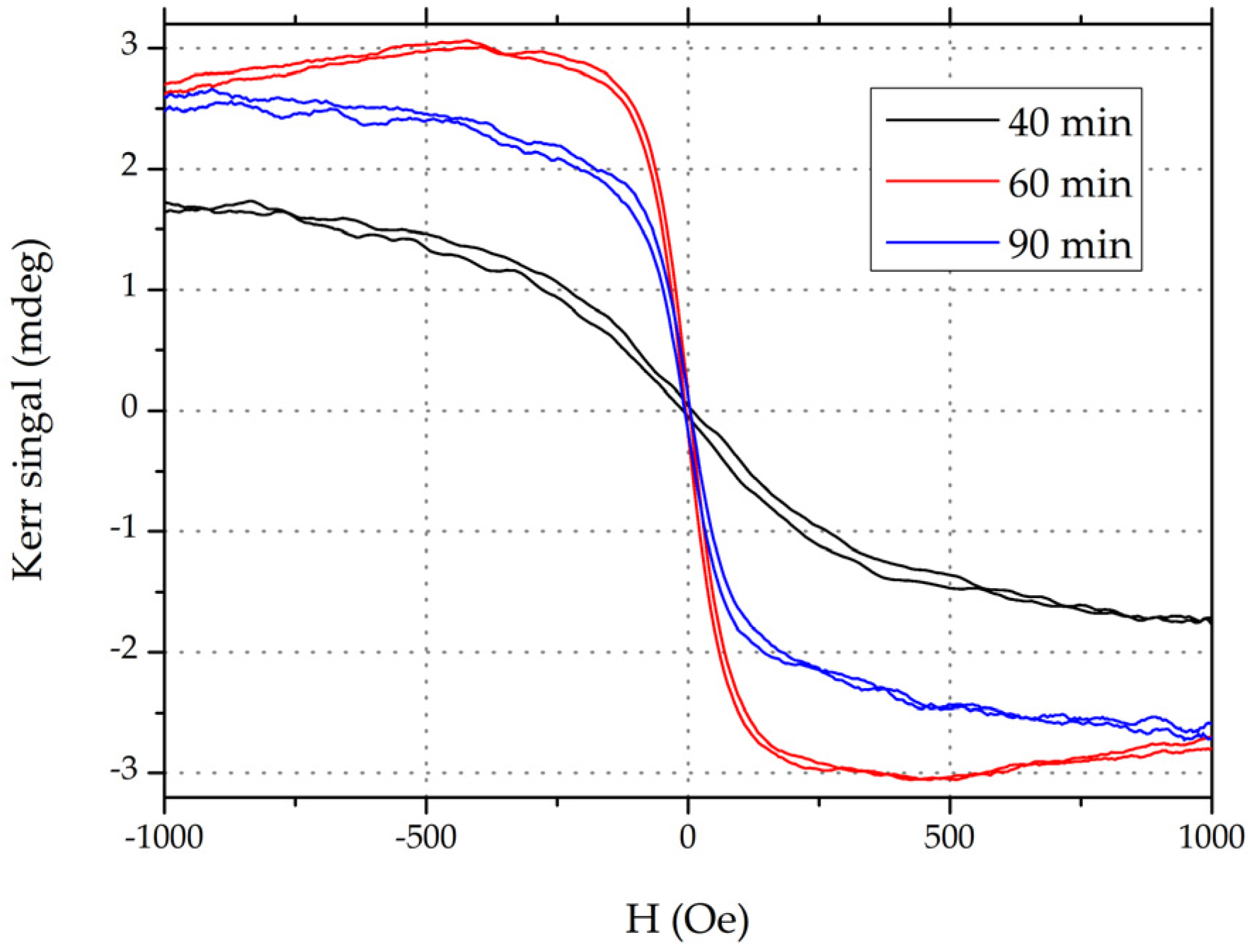

2.2. Failure Issues Caused by Annealing Parameters

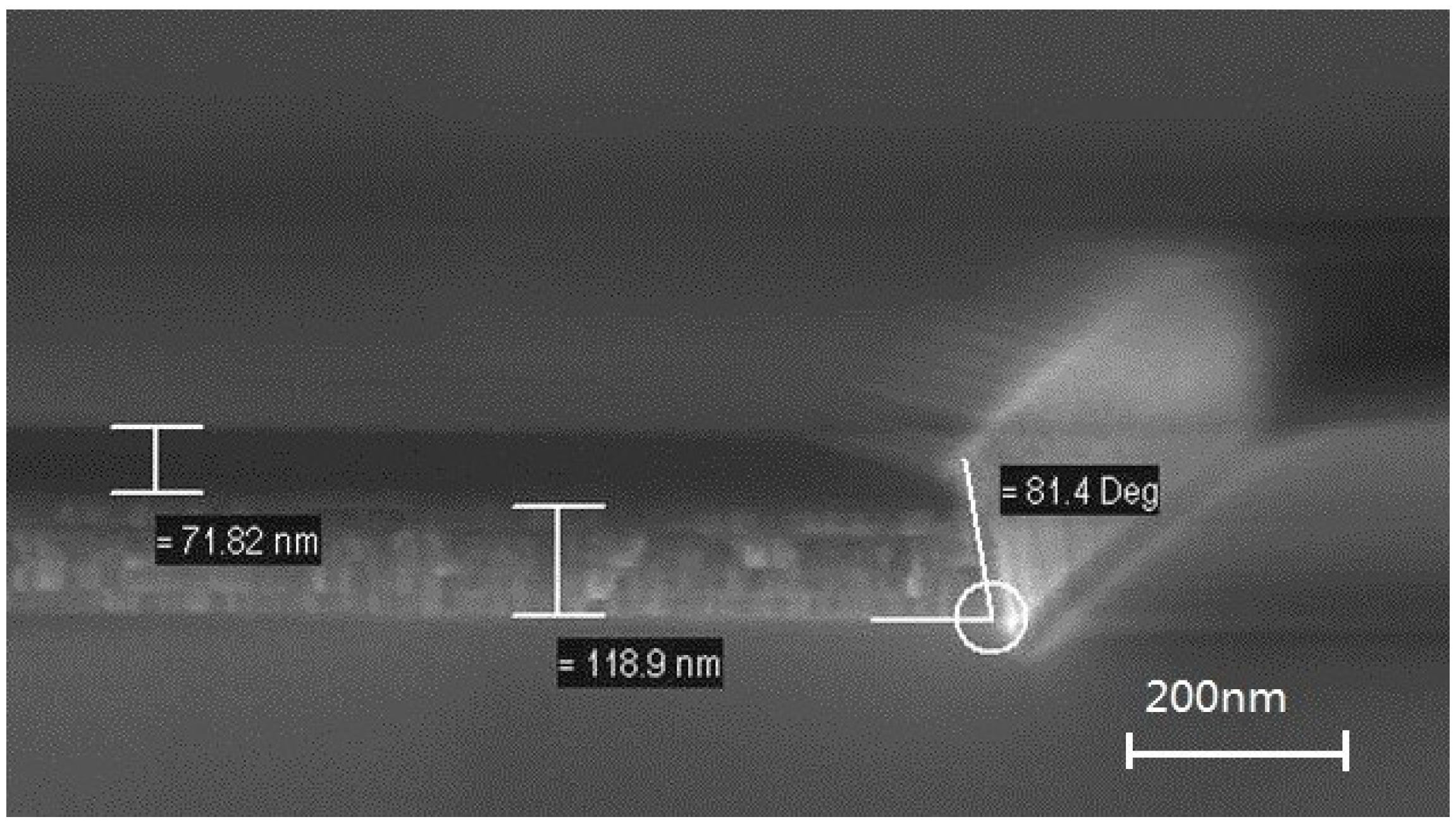

2.3. Failure Issues Caused by Etching Methods

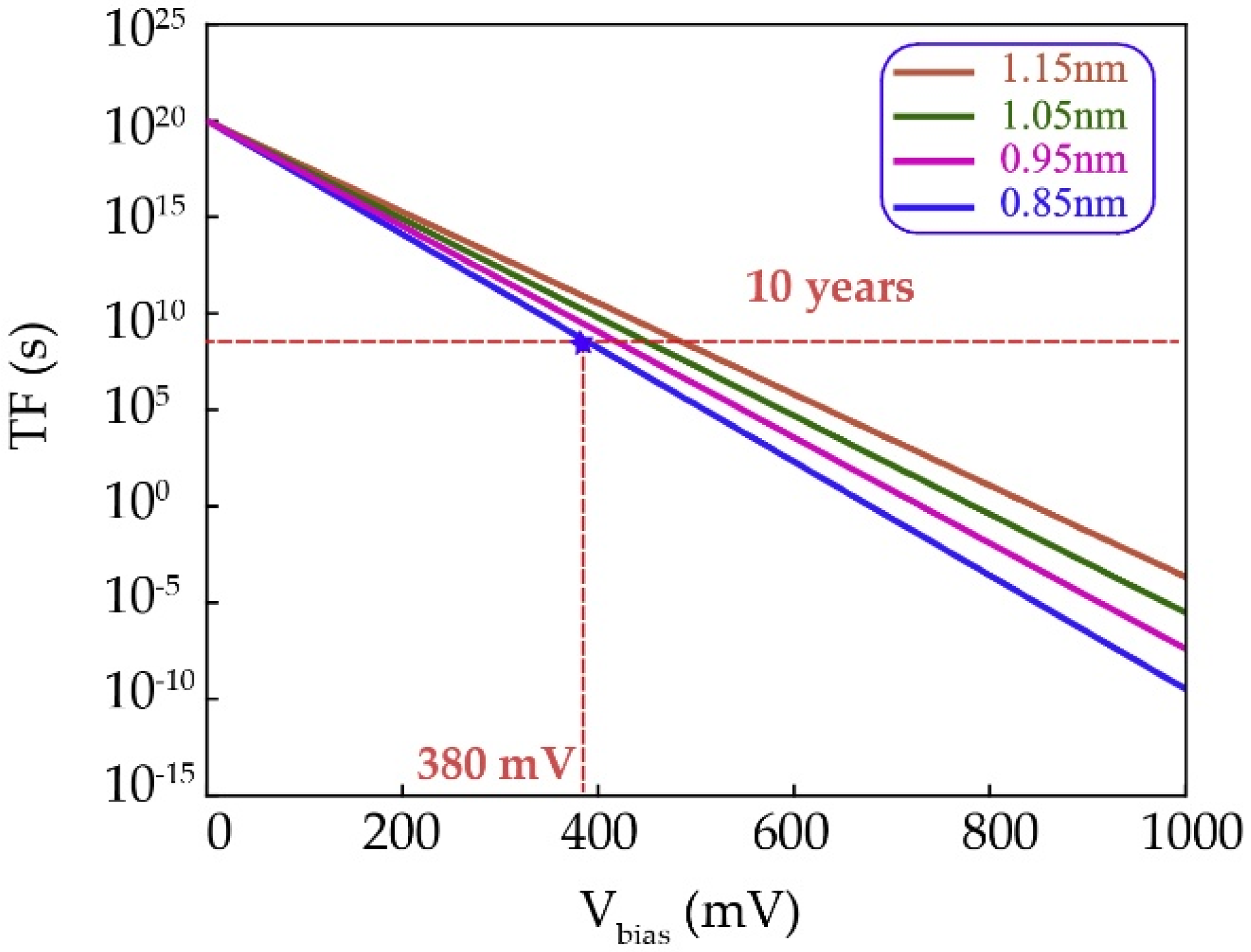

3. Failure Issues Due to Oxide Barrier Breakdown

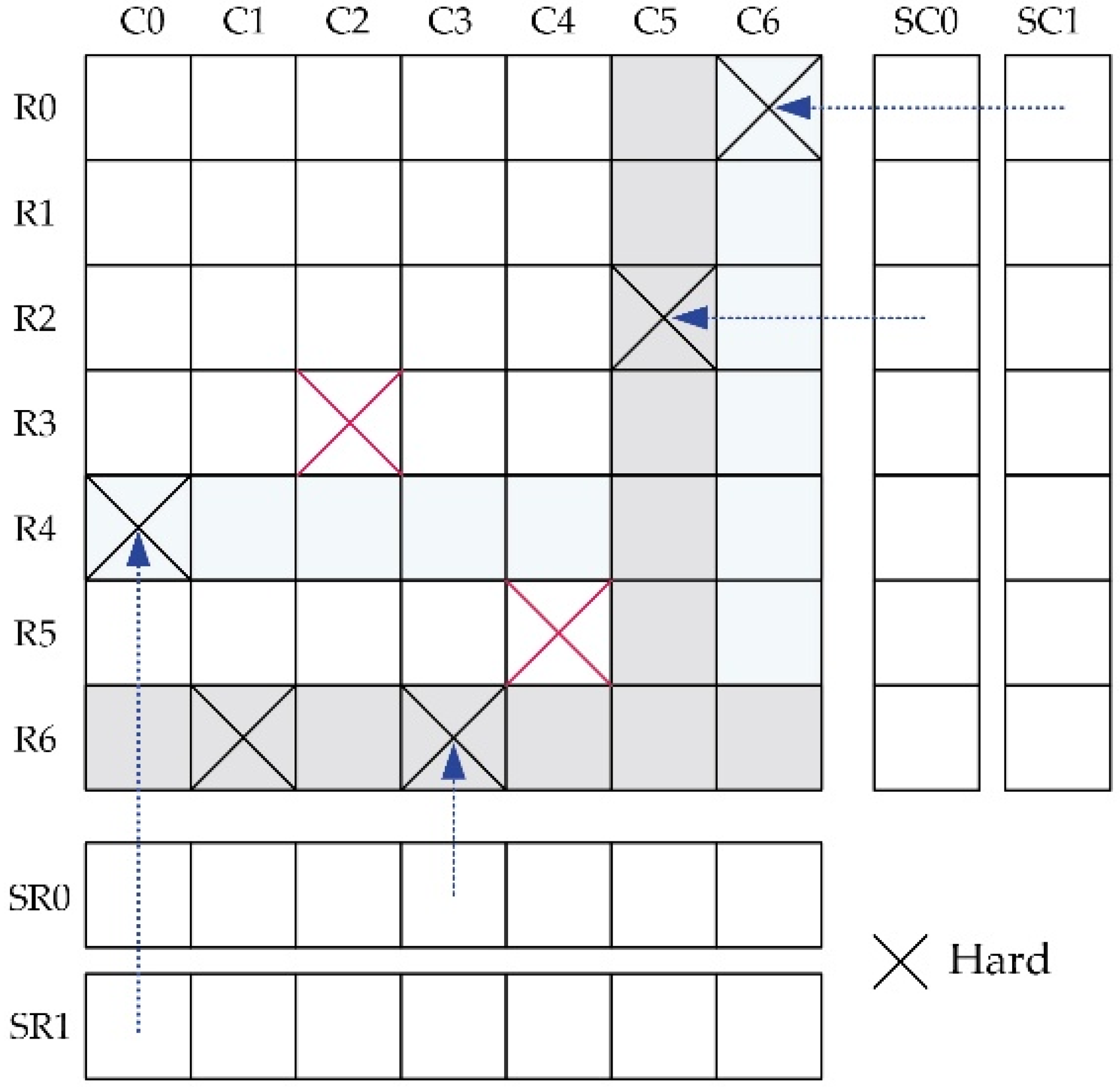

4. Failure Tolerant Design Techniques

5. Conclusions

Acknowledgments

Author Contributions

Conflicts of Interest

References

- Kim, N.S.; Austin, T.; Baauw, D.; Mudge, T.; Flautner, K.; Hu, J.S.; Irwin, M.J.; Kandemir, M.; Narayanan, V. Leakage current: Moore’s law meets static power. Computer 2003, 36, 68–75. [Google Scholar]

- Zhao, W.S.; Prenat, G. Spintronics-Based Computing; Springer: Berlin, Germany, 2015. [Google Scholar]

- Wang, Y.Q.; Liu, Y.; Li, S.; Zhang, D.; Zhao, B.; Chiang, M.F.; Yan, Y.; Sai, B.; Yang, Y.Z. A 3us wake-up time nonvolatile processor based on ferroelectric flip-flops. In Proceedings of the IEEE ESSCIRS, Bordeaux, France, 17–21 September 2012.

- Xue, C.J.; Zhang, Y.; Chen, Y.; Sun, G.; Yang, J.J.; Li, H. Emerging non-volatile memories: Opportunities and challenges. In Proceedings of the IEEE Hardware/Software Codesign and System Synthesis, Taipei, Taiwan, 9–14 October 2011.

- Kang, W.; Zhang, Y.; Wang, Z.H.; Klein, J.-O.; Chappert, C.; Ravelosona, D.; Wang, G.F.; Zhang, Y.; Zhao, W.S. Spintronics: Emerging ultra-low-power circuits and systems beyond MOS technology. ACM J. Emerg. Technol. Comput. Syst. 2015, 12. [Google Scholar] [CrossRef]

- Chappert, C.; Fert, A.; Nguyen van Dau, F. The emergence of spin electronics in data storage. Nat. Mater. 2007, 6, 813–823. [Google Scholar] [CrossRef] [PubMed]

- Wong, H.S.P.; Salahuddin, S. Memory leads the way to better computing. Nat. Nanotechnol. 2015, 10, 191–194. [Google Scholar] [CrossRef] [PubMed]

- Sun, J.Z.; Koch, R.H.; Kuan, T.S.; Katine, J.A. Spin angular momentum transfer in a current-perpendicular spin-valve nanomagnet. SPIE Proc. 2004, 5359. [Google Scholar] [CrossRef]

- Zhao, W.S.; Belhaire, E.; Mistral, Q.; Chappert, C.; Javerliac, V.; Dieny, B. Macro-model of spin-transfer torque based magnetic tunnel junction device for hybrid Magnetic-CMOS design. In Proceedings of IEEE International Behavioral Modeling and Simulation Workshop, San Jose, CA, USA, 14–15 September 2006.

- Ikeda, S.; Miura, K.; Yamamoto, H.; Mizunuma, K.; Gan, H.D.; Endo, M.; Kanai, S.; Hayakawa, J.; Matsukura, F.; Ohno, H. A perpendicular-anisotropy CoFeB-MgO magnetic tunnel junction. Nat. Mater. 2010, 9, 721–724. [Google Scholar] [CrossRef] [PubMed]

- Worledge, D.C.; Hu, G.; Abraham, D.W.; Sun, J.Z.; Trouilloud, P.L.; Nowak, J.; Brown, S.; Gaidis, M.C.; O’Sullivan, E.J.; Robertazzi, R.P. Spin torque switching of perpendicular Ta|CoFeB|MgO-based magnetic tunnel junctions. Appl. Phys. Lett. 2011, 98. [Google Scholar] [CrossRef]

- Su, L.; Zhang, Y.; Klein, J.; Zhang, Y.; Bournel, A.; Fert, A.; Zhao, W. Current-limiting challenges for all-spin logic devices. Sci. Rep. 2015, 5. [Google Scholar] [CrossRef] [PubMed]

- Kent, A.D.; Worledge, D.C. A new spin on magnetic memories. Nat. Nanotechnol. 2015, 10, 187–191. [Google Scholar] [CrossRef] [PubMed]

- Chatterjee, J.; Tahmasebi, T.; Swerts, J.; Kar, G.S.; de Boeck, J. Impact of seed layer on post-annealing behavior of transport and magnetic properties of Co/Pt multilayer-based bottom-pinned perpendicular magnetic tunnel junctions. Appl. Phys. Express 2015, 8. [Google Scholar] [CrossRef]

- Yang, H.X.; Chshiev, M.; Dieny, B. First-principles investigation of the very large perpendicular magnetic anisotropy at Fe|MgO and Co|MgO interfaces. Phys. Rev. B 2011, 84. [Google Scholar] [CrossRef]

- Peng, S.Z.; Wang, M.X.; Yang, H.; Zeng, L.; Nan, J.; Zhou, J.Q.; Zhang, Y.G.; Hallal, A.; Chshiev, M.; Wang, K.L.; et al. Origin of interfacial perpendicular magnetic anisotropy in MgO/CoFe/metallic capping layer structures. Sci. Rep. 2015, 5, 18173. [Google Scholar] [CrossRef] [PubMed]

- Zhao, W.S.; Zhang, Y.; Devolder, T.; Klein, J.O.; Ravelosona, D.; Chappert, C.; Mazoyer, P. Failure and reliability analysis of STTM-RAM. Microelectron. Reliab. 2012, 52, 1848–1852. [Google Scholar] [CrossRef]

- Min, T.; Chen, Q.; Beach, R.; Jan, G.; Horng, C.; Kula, W.; Torng, T.; Tong, R.; Zhong, T.; Tang, D.; et al. A study of write margin of S characterization of growth pin torque transfer magnetic random access memory technology. IEEE Trans. Magn. 2010, 46, 2322–2327. [Google Scholar] [CrossRef]

- Kar, G.S.; Kim, W.; Tahmasebi, T.; Swerts, J.; Mertens, S.; Heylen, N.; Min, T. Co/Ni based p-MTJ stack for sub-20 nm high density stand alone and high performance embedded memory application. In Proceedings of IEEE International Electron Devices Meeting, San Francisco, CA, USA, 15–17 December 2014.

- Sun, J.Z.; Brown, S.L.; Chen, W.; Delenia, E.A.; Gaidis, M.C.; Harms, J.; Hu, G.; Jiang, X.; Kilaru, R.; Kula, W.; et al. Spin-torque switching efficiency in CoFeB-MgO based tunnel junctions. Phys. Rev. B 2013, 88, 104426. [Google Scholar] [CrossRef]

- Chun, K.C.; Zhao, H.; Harms, J.D.; Kim, T.; Wang, J.; Kim, C.H. A scaling roadmap and performance evaluation of in-plane and perpendicular MTJ based STT-MRAMs for high-density cache memory. IEEE J. Solid State Circuits 2013, 48, 598–610. [Google Scholar] [CrossRef]

- Amara-Dababi, S.; Sousa, R.C.; Chshiev, M.; Bea, H.; Alvarez-Herault, J.; Lombard, L.; Prejbeanu, I.L.; Mackay, K.; Dieny, B. Charge trapping-detrapping mechanism of barrier breakdown in MgO magnetic tunnel junctions. Appl. Phys. Lett. 2011, 99, 083501. [Google Scholar] [CrossRef]

- Dimitrov, D.V.; Gao, Z.; Wang, X.; Jung, W.; Lou, X.; Heinonen, O.G. Dielectric breakdown of MgO magnetic tunnel junctions. Appl. Phys. Lett. 2009, 94, 123110. [Google Scholar] [CrossRef]

- Keavney, D.; Falco, C. Deposition Techniques for Magnetic Thin Films and Multilayers. In Magnetic Interactions and Spin Transport, 1st ed.; Chtchelkanova, A., Wolf, S.A., Idzerda, Y., Eds.; Springer US: New York, NY, USA, 2003; p. 445. [Google Scholar]

- Lee, D.S.; Chang, H.T.; Cheng, C.W.; Chern, G. Perpendicular magnetic anisotropy in MgO/CoFeB/Nb and a comparison of the cap layer effect. Magn. IEEE Trans. 2014, 50, 1–4. [Google Scholar] [CrossRef]

- Yamanouchi, M.; Koizumi, R.; Ikeda, S.; Sato, H.; Mizunuma, K.; Miura, K.; Ohno, H. Dependence of magnetic anisotropy on MgO thickness and buffer layer in Co20Fe60B20-MgO structure. J. Appl. Phys. 2011, 109, 07C712. [Google Scholar] [CrossRef]

- Hallal, A.; Yang, H.X.; Dieny, B.; Chshiev, M. Anatomy of perpendicular magnetic anisotropy in Fe/MgO magnetic tunnel junctions: First-principles insight. Phys. Rev. B 2013, 88. [Google Scholar] [CrossRef]

- Gottwald, M.; Kan, J.J.; Lee, K.; Zhu, X.; Park, C.; Kang, S.H. Scalable and thermally robust perpendicular magnetic tunnel junctions for STT-MRAM. Appl. Phys. Lett. 2015, 106, 32413. [Google Scholar] [CrossRef]

- Park, C.; Kan, J.; Ching, C.; Ahn, J.; Xue, L.; Wang, R.; Kontos, A.; Liang, S.; Bangar, M.; Chen, H.; et al. Systematic optimization of 1 Gbit perpendicular magnetic tunnel junction arrays for 28 nm embedded STT-MRAM and beyond. In Proceeding of the 2015 IEEE International Conference on Electron Devices Meeting (IEDM), Washington, DC, USA, 7–9 December 2015.

- O’Sullivan, E.J. Magnetic Tunnel Junction-Based MRAM and Related Processing Issues. Available online: http://domino.research.ibm.com/library/cyberdig.nsf/papers/0753EECAF4B315BC85256FAA0054EA91/$File/rc23525.pdf (accessed on 7 January 2016).

- Swagten, H.J.M. Spin-Dependent Tunneling in Magnetic Junctions. In Handbook of Magnetic Materials; Buschow, K.H.J., Ed.; Elsevier: Amsterdam, The Netherlands, 2003; Volume 15, pp. 45–48. [Google Scholar]

- Oliver, B. Two breakdown mechanisms in ultrathin alumina barrier magnetic tunnel junctions. J. Appl. Phys. 2004, 95, 1315. [Google Scholar] [CrossRef]

- Se, Y.; Lee, C.; Shapiro, A.J., Jr.; Egelhoff, W.F.; Vaudin, M.D.; Ruglovsky, J.L.; Mallett, J.; Pong, P.W.T. X-ray diffraction study of the optimization of MgO growth conditions for magnetic tunnel junctions. J. Appl. Phys. 2008, 103. [Google Scholar] [CrossRef]

- Shin, I.; Min, B.; Hong, J.; Shin, K. Consistent Relationship between the tunnel magnetoresistance of CoFeB/MgO/CoFeB Junctions and X-Ray Diffraction Properties. IEEE Trans. Magn. 2009, 45, 2393–2395. [Google Scholar] [CrossRef]

- Choi, Y.S.; Nagamine, Y.; Tsunekawa, K.; Maehara, H.; Djayaprawira, D.D.; Yuasa, S.; Ando, K. Effect of Ta getter on the quality of MgO tunnel barrier in the polycrystalline CoFeB/MgO/CoFe magnetic tunnel junction. Appl. Phys. Lett. 2007, 90, 012505. [Google Scholar] [CrossRef]

- Meng, H.; Lum, W.H.; Sbiaa, R.; Lua, S.Y.H.; Tan, H.K. Annealing effects on CoFeB-MgO magnetic tunnel junctions with perpendicular anisotropy. J. Appl. Phys. 2011, 110. [Google Scholar] [CrossRef]

- Chen, X.; Freitas, P.P. Magnetic tunnel junction based on MgO barrier prepared by natural oxidation and direct sputtering deposition. Nano Micro Lett. 2012, 4, 25–29. [Google Scholar] [CrossRef]

- Wang, W.G.; Jordan-sweet, J.; Miao, G.X.; Ni, C.; Rumaiz, A.K.; Shah, L.R.; Fan, X.; Parsons, P.; Stearrett, R.; Nowak, E.R.; et al. In-situ characterization of rapid crystallization of amorphous CoFeB electrodes in CoFeB/MgO/CoFeB junctions during thermal annealing. Appl. Phys. Lett. 2009, 95. [Google Scholar] [CrossRef]

- Maehara, H.; Nishimura, K.; Nagamine, Y.; Tsunekawa, K.; Seki, T.; Kubota, H.; Fukushima, A.; Yakushiji, K.; Ando, K.; Yuasa, S. Tunnel magnetoresistance above 170% and resistance—Area product of 1 Ω (μm) 2 attained by in situ annealing of ultra-thin MgO tunnel barrier. Appl. Phys. Express 2011, 4. [Google Scholar] [CrossRef]

- Naik, V.B.; Meng, H.; Sbiaa, R. Thick CoFeB with perpendicular magnetic anisotropy in CoFeB-MgO based magnetic tunnel junction. AIP Adv. 2012, 2, 42182. [Google Scholar] [CrossRef]

- Sinha, J.; Gruber, M.; Kodzuka, M.; Ohkubo, T.; Mitani, S.; Hono, K.; Hayashi, M. Influence of boron diffusion on the perpendicular magnetic anisotropy in Ta|CoFeB|MgO ultrathin films. J. Appl. Phys. 2015, 117, 43913. [Google Scholar] [CrossRef]

- Hayakawa, J.; Ikeda, S.; Matsukura, F.; Takahashi, H.; Ohno, H. Dependence of giant tunnel magnetoresistance of sputtered CoFeB/MgO/CoFeB magnetic tunnel junctions on MgO barrier thickness and annealing temperature. Jpn. J. Appl. Phys. 2005, 44, L587–L589. [Google Scholar] [CrossRef]

- Park, J.G.; Shim, T.H.; Chae, K.S.; Lee, D.Y.; Takemura, Y.; Lee, S.E.; Hong, J.P. Challenging issues for terra-bit-level perpendicular STT-MRAM. In Proceedings of IEEE International Electron Devices Meeting, San Francisco, CA, USA, 15–17 December 2014.

- Yuasa, S.; Suzuki, Y.; Katayama, T.; Ando, K. Characterization of growth and crystallization processes in CoFeB/MgO/CoFeB magnetic tunnel junction structure by reflective high-energy electron diffraction. Appl. Phys. Lett. 2005, 87, 242503. [Google Scholar] [CrossRef]

- Singh, B.B.; Chaudhary, S. Effect of MgO spacer and annealing on interface and magnetic properties of ion beam sputtered NiFe/Mg/MgO/CoFe layer structures. J. Appl. Phys. 2012, 112. [Google Scholar] [CrossRef]

- Isogami, S.; Tsunoda, M.; Komagaki, K.; Sunaga, K.; Uehara, Y.; Sato, M.; Miyajima, T.; Takahashi, M. In situ heat treatment of ultrathin MgO layer for giant magnetoresistance ratio with low resistance area product in CoFeB/MgO/CoFeB magnetic tunnel junctions. Appl. Phys. Lett. 2008, 93. [Google Scholar] [CrossRef]

- Sato, H.; Ikeda, S.; Fukami, S.; Honjo, H.; Ishikawa, S.; Yamanouchi, M.; Mizunuma, K.; Matsukura, F.; Ohno, H. Co/Pt multilayer based reference layers in magnetic tunnel junctions for nonvolatile spintronics VLSIs. Jpn. J. Appl. Phys. 2014, 53. [Google Scholar] [CrossRef]

- Ikeda, S.; Sato, H.; Honjo, H.; Enobio, E.C.I.; Ishikawa, S.; Yamanouchi, M.; Fukami, M.; Kanai, S.; Matsukura, F.; Endoh, T.; et al. Perpendicular-anisotropy CoFeB-MgO based magnetic tunnel junctions scaling down to 1× nm. In 2014 IEEE International Conference on Electron Devices Meeting (IEDM), San Francisco, CA, USA, 15–17 December 2014.

- Honjo, H.; Sato, H.; Ikeda, S.; Sato, S.; Watanebe, T.; Miura, S.; Nasuno, T.; Noguchi, Y.; Yasuhira, M.; Tanigawa, T.; et al. 10 nm perpendicular-anisotropy CoFeB-MgO magnetic tunnel junction with over 400 °C high thermal tolerance by boron diffusion control. In Proceedin of the 2015 Symposium on VLSI Technology and Circuits, Kyoto, Japan, 16–18 June 2015.

- Chen, E.; Schwarz, B.; Choi, C.J.; Kula, W.; Wolfman, J.; Ounadjela, K.; Geha, S. Magnetic tunnel junction pattern technique. J. Appl. Phys. 2003, 93, 8379–8381. [Google Scholar] [CrossRef]

- Boullart, W.; Radisic, D.; Paraschiv, V.; Cornelissen, S.; Manfrini, M.; Yatsuda, K.; Nishimura, E.; Ohishi, T.; Tahara, S. STT MRAM patterning challenges. In Proceedings of SPIE Advanced Lithography, San Jose, CA, USA, 29 March 2013; Zhang, Y., Oehrlein, G.S., Lin, Q., Eds.; International Society for Optics and Photonics: Bellingham, WA, USA, 2013. [Google Scholar]

- Takahashi, S.; Kai, T.; Shimomura, N.; Ueda, T.; Amano, M.; Yoshikawa, M.; Kitagawa, E.; Asao, Y.; Ikegawa, S.; Kishi, T.; et al. Ion-beam-etched profile control of MTJ cells for improving the switching characteristics of high-density MRAM. IEEE Trans. Magn. 2006, 42, 2745–2747. [Google Scholar] [CrossRef]

- Sugiura, K.; Takahashi, S.; Amano, M.; Kajiyama, T.; Iwayama, M.; Asao, Y.; Shimomura, N.; Kishi, T.; Ikegawa, S.; Yoda, H.; et al. Ion beam etching technology for high-density spin transfer torque magnetic random access memory. Jpn. J. Appl. Phys. 2009, 48. [Google Scholar] [CrossRef]

- Kinoshita, K.; Utsumi, H.; Suemitsu, K.; Hada, H.; Sugibayashi, T. Etching magnetic tunnel junction with metal etchers. Jpn. J. Appl. Phys. 2010, 49. [Google Scholar] [CrossRef]

- Chun, S.; Kim, D.; Kwon, J.; Kim, B.; Choi, S.; Lee, S. Multi-step ion beam etching of sub-30 nm magnetic tunnel junctions for reducing leakage and MgO barrier damage. J. Appl. Phys. 2012, 111, 7C–722C. [Google Scholar] [CrossRef]

- Jung, K.B.; Lambers, E.S.; Childress, J.R.; Pearton, S.J.; Jenson, M.; Hurst, A.T. High rate dry etching of Ni0.8Fe0.2 and NiFeCo. Appl. Phys. Lett. 1997, 71, 1255–1257. [Google Scholar] [CrossRef]

- Vasile, M.J.; Mogab, C.J. Chemically assisted sputter-etching of permalloy using CO or CL2. J. Vac. Sci. Technol. A 1986, 4, 1841–1849. [Google Scholar] [CrossRef]

- Kinoshita, K.; Yamada, K.; Matsutera, H. Reactive ion etching of Fe-Si-Al alloy for thin film head. IEEE Trans. Magn. 1991, 27, 4888–4890. [Google Scholar] [CrossRef]

- Yang, K.C.; Jeon, M.H.; Yeom, G.Y. A study on the etching characteristics of magnetic tunneling junction materials using DC pulse-biased inductively coupled plasmas. Jpn. J. Appl. Phys. 2015, 54. [Google Scholar] [CrossRef]

- Matsutani, A.; Koyama, F.; Iga, K. Low bias voltage dry etching of InP by inductively coupled plasma using SiCl4/Ar. Jpn. J. Appl. Phys. 1998, 37. [Google Scholar] [CrossRef]

- Maeda, T.; Lee, J.W.; Shul, R.J.; Han, J.; Hong, J.; Lambers, E.S.; Hobson, W.S. Inductively coupled plasma etching of III–V semiconductors in BCl3-based chemistries: I. GaAs, GaN, GaP, GaSb and AlGaAs. Appl. Surf. Sci. 1999, 143, 174–182. [Google Scholar] [CrossRef]

- Kim, E.H.; Lee, T.Y.; Chung, C.W. Evolution of etch profile of magnetic tunnel junction stacks etched in a CH3OH/Ar plasma. J. Electrochem. Soc. 2012, 159, H230–H234. [Google Scholar] [CrossRef]

- Garay, A.A.; Choi, J.H.; Hwang, S.M.; Chung, C.W. Inductively coupled plasma reactive ion etching of magnetic tunnel junction stacks in a CH3COOH/Ar gas. ECS Solid State Lett. 2015, 4, P77–P79. [Google Scholar] [CrossRef]

- Kinoshita, K.; Yamamoto, T.; Honjo, H.; Kasai, N.; Ikeda, S.; Ohno, H. Damage recovery by reductive chemistry after methanol-based plasma etch to fabricate magnetic tunnel junctions. Jpn. J. Appl. Phys. 2012, 51. [Google Scholar] [CrossRef]

- Kinoshita, K.; Honjo, H.; Fukami, S.; Sato, H.; Mizunuma, K.; Tokutome, K.; Murahata, M.; Ikeda, S.; Miura, S.; Kasai, N.; et al. Process-induced damage and its recovery for a CoFeB-MgO magnetic tunnel junction with perpendicular magnetic easy axis. Jpn. J. Appl. Phys. 2014, 53, 103001. [Google Scholar] [CrossRef]

- Noguchi, H.; Ikegami, K.; Kushida, K.; Abe, K.; Itai, S.; Takaya, S.; Fujita, S. 7.5 A 3.3 ns-access-time 71.2 μW/MHz 1 Mb embedded STT-MRAM using physically eliminated read-disturb scheme and normally-off memory architecture. In Proceedings of the 2015 IEEE International conference on Solid-State Circuits Conference-(ISSCC), San Francisco, CA, USA, 22–26 February 2015.

- Wang, Y.; Zhang, Y.; Deng, E.Y.; Klein, J.O.; Naviner, L.A.B.; Zhao, W.S. Compact model of magnetic tunnel junction with stochastic spin transfer torque switching for reliability analyses. Microelectron. Reliab. 2014, 54, 1774–1778. [Google Scholar] [CrossRef]

- Van Beek, S.; Martens, K.; Roussel, P.; Donadio, G.; Swerts, J.; Mertens, S.; Groeseneken, G. Four point probe ramped voltage stress as an efficient method to understand breakdown of STT-MRAM MgO tunnel junctions. In 2015 IEEE International Conference on Proceedings of Reliability Physics Symposium (IRPS), Monterey, CA, USA, 19–23 April 2015.

- McPherson, J.W.; Mogul, H.C. Underlying physics of the thermochemical E model in describing low-field time-dependent dielectric breakdown in SiO2 thin films. J. Appl. Phys. 1998, 84, 1513–1523. [Google Scholar] [CrossRef]

- Zhao, W.S.; Wang, Y.; Cai, H.; Naviner, L.; Zhao, X.X.; Zhang, Y.; Deng, E.Y.; Klein, J.O. Compact model of dielectric breakdown in spin transfe torque magnetic tunnel junction. IEEE Trans. Electron Devices 2016. under review. [Google Scholar]

- Khan, A.A. Analysis of dielectric breakdown in CoFeB/MgO/CoFeB magnetic tunnel junction. Microelectron. Reliab. 2015, 55, 894–902. [Google Scholar] [CrossRef]

- Hu, G.; Lee, J.H.; Nowak, J.J.; Sun, J.Z.; Harms, J.; Annunziata, A.; Brown, S.; Chen, W.; Kim, Y.H.; Lauer, G.; et al. STT-MRAM with double magnetic tunnel junctions. In Proceeding of the 2015 IEEE International Conference on Electron Devices Meeting (IEDM), Washington, DC, USA, 7–9 December 2015.

- Kang, W.; Zhao, W.S.; Wang, Z.H.; Klein, J.O.; Zhang, Y.; Chabi, D.; Zhang, Y.G.; Ravelosona, D.; Chappert, C. An overview of spin-based integrated circuits. In Proceedings of the IEEE Asia and South Pacific Design Automation Conference, Singapore, 20–23 January 2014.

- Kang, W.; Cheng, Y.; Zhang, Y.; Ravelosona, D.; Zhao, W. Readability challenges in deeply scaled STT-MRAM. In Proceedings of the 2014 14th Annual Conference on Non-Volatile Memory Technology Symposium (NVMTS), Jeju Island, Korea, 27–29 October 2014.

- Zhang, Y.; Wang, X.; Chen, Y. STT-RAM cell design optimization for persistent and non-persistent error rate reduction: A statistical design view. In Proceedings of the IEEE International Conference on Computer-Aided Design (ICCAD), San Jose, CA, USA, 7–10 November 2011.

- Kang, W.; Zhao, W.; Deng, E.; Klein, J.; Cheng, Y.; Ravelosona, D.; Zhang, Y.; Chappert, C. A radiation hardened hybrid spintronic/CMOS nonvolatile unit using magnetic tunnel junctions. J. Phys. D Appl. Phys. 2014, 47, 405003. [Google Scholar] [CrossRef]

- Seong, N.H.; Woo, D.H.; Srinivasan, V.; Rivers, J.A.; Lee, H.H.S. SAFER: Stuck-at-fault error recovery for memories. In Proceedings of the 2010 43rd Annual IEEE/ACM International Symposium on Microarchitecture, Washington, DC, USA, 4–8 December 2010.

- Chen, T.; Li, J.; Tseng, T. Cost-efficient built-in redundancy analysis with optimal repair rate for RAMs. IEEE Trans. Comput. Aided Des. Integr. Circuits Syst. 2012, 31, 930–940. [Google Scholar] [CrossRef]

- Segal, J.; Jee, A.; Lepejian, D.; Chu, B. Using electrical bitmap results from embedded memory to enhance yield. IEEE Des. Test Comput. 2001, 18, 28–39. [Google Scholar] [CrossRef]

- Huang, C.T.; Wu, C.F.; Li, J.F.; Wu, C.W. Built-in redundancy analysis for memory yield improvement. Reliab. IEEE Trans. 2003, 52, 386–399. [Google Scholar] [CrossRef]

- Benso, A.; Chiusano, S.; di Natale, G.; Prinetto, P. An on-line BIST RAM architecture with self-repair capabilities. Reliab. IEEE Trans. 2002, 51, 123–128. [Google Scholar] [CrossRef]

- Lu, S.K.; Huang, H.H.; Huang, J.L.; Ning, P. Synergistic reliability and yield enhancement techniques for embedded SRAMs. Comput. Aided Des. Integr. Circuits Syst. IEEE Trans. 2013, 32, 165–169. [Google Scholar] [CrossRef]

- Kang, W.; Li, Z.; Klein, J.; Chen, Y.; Zhang, Y.; Ravelosona, D.; Chappert, C.; Zhao, W. Variation-tolerant and disturbance-free sensing circuit for deep nanometer STT-MRAM. IEEE Trans. Nanotechnol. 2014, 13, 1088–1092. [Google Scholar] [CrossRef]

- Zhang, Y.; Wang, X.; Li, H.; Chen, Y. STT-RAM cell optimization considering MTJ and CMOS variations. IEEE Trans. Magn. 2011, 47, 2962–2965. [Google Scholar] [CrossRef]

- Kang, W.; Zhang, L.; Klein, J.; Zhang, Y.; Ravelosona, D.; Zhao, W. Reconfigurable codesign of STT-MRAM under process variations in deeply scaled technology. IEEE Trans. Electron Devices 2015, 62, 1769–1777. [Google Scholar] [CrossRef]

- Lakys, Y.; Zhao, W.S.; Devolder, T.; Zhang, Y.; Klein, J.; Ravelosona, D.; Chappert, C. Self-enabled “error-free” switching circuit for spin transfer torque MRAM and logic. IEEE Trans. Magn. 2012, 48, 2403–2406. [Google Scholar] [CrossRef]

- Suzuki, D.; Natsui, M.; Mochizuki, A.; Hanyu, T. Cost-efficient self-terminated write driver for spin-transfer-torque RAM and logic. Magn. IEEE Trans. 2014, 50, 1–4. [Google Scholar] [CrossRef]

- Kang, W.; Zhao, W.; Klein, J.O.; Zhang, Y.; Chappert, C.; Ravelosona, D. High reliability sensing circuit for deep submicron spin transfer torque magnetic random access memory. Electron. Lett. 2013, 49, 1283–1284. [Google Scholar] [CrossRef]

- Wen, W.J.; Mao, M.J.; Zhu, X.C.; Kang, S.H.; Wang, D.H.; Chen, Y.R. CD-ECC: Content-dependent error correction codes for combating asymmetric nonvolatile memory operation errors. In Proceedings of the ICCAD-IEEE ACM International Conference on Computer-Aided Design, San Jose, CA, USA, 18–21 November 2013.

- Kang, W.; Zhao, W.; Wang, Z.; Zhang, Y.; Klein, J.; Zhang, Y.; Chappert, C.; Ravelosona, D. A low-cost built-in error correction circuit design for STT-MRAM reliability improvement. Microelectron. Reliab. 2013, 53, 1224–1229. [Google Scholar] [CrossRef]

- Kang, W.; Zhang, L.; Zhao, W.; Klein, J.; Zhang, Y.; Ravelosona, D.; Chappert, C. Yield and reliability improvement techniques for emerging nonvolatile STT-MRAM. IEEE J. Emerg. Sel. Top. Circuits Syst. 2015, 5, 28–39. [Google Scholar] [CrossRef]

© 2016 by the authors; licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons by Attribution (CC-BY) license (http://creativecommons.org/licenses/by/4.0/).

Share and Cite

Zhao, W.; Zhao, X.; Zhang, B.; Cao, K.; Wang, L.; Kang, W.; Shi, Q.; Wang, M.; Zhang, Y.; Wang, Y.; et al. Failure Analysis in Magnetic Tunnel Junction Nanopillar with Interfacial Perpendicular Magnetic Anisotropy. Materials 2016, 9, 41. https://doi.org/10.3390/ma9010041

Zhao W, Zhao X, Zhang B, Cao K, Wang L, Kang W, Shi Q, Wang M, Zhang Y, Wang Y, et al. Failure Analysis in Magnetic Tunnel Junction Nanopillar with Interfacial Perpendicular Magnetic Anisotropy. Materials. 2016; 9(1):41. https://doi.org/10.3390/ma9010041

Chicago/Turabian StyleZhao, Weisheng, Xiaoxuan Zhao, Boyu Zhang, Kaihua Cao, Lezhi Wang, Wang Kang, Qian Shi, Mengxing Wang, Yu Zhang, You Wang, and et al. 2016. "Failure Analysis in Magnetic Tunnel Junction Nanopillar with Interfacial Perpendicular Magnetic Anisotropy" Materials 9, no. 1: 41. https://doi.org/10.3390/ma9010041

APA StyleZhao, W., Zhao, X., Zhang, B., Cao, K., Wang, L., Kang, W., Shi, Q., Wang, M., Zhang, Y., Wang, Y., Peng, S., Klein, J.-O., De Barros Naviner, L. A., & Ravelosona, D. (2016). Failure Analysis in Magnetic Tunnel Junction Nanopillar with Interfacial Perpendicular Magnetic Anisotropy. Materials, 9(1), 41. https://doi.org/10.3390/ma9010041