Recent Progress of Ferroelectric-Gate Field-Effect Transistors and Applications to Nonvolatile Logic and FeNAND Flash Memory

Abstract

:1. Introduction

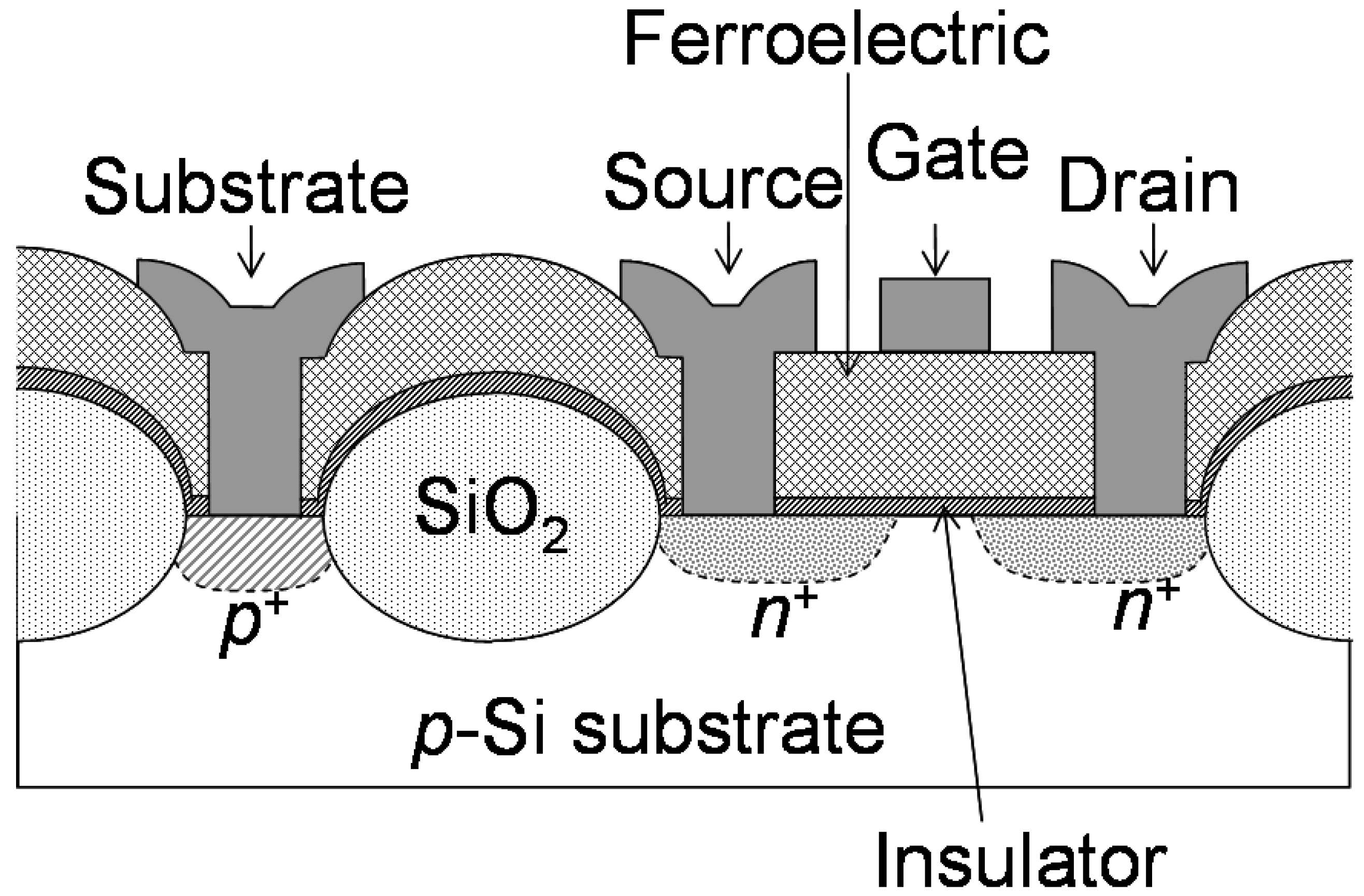

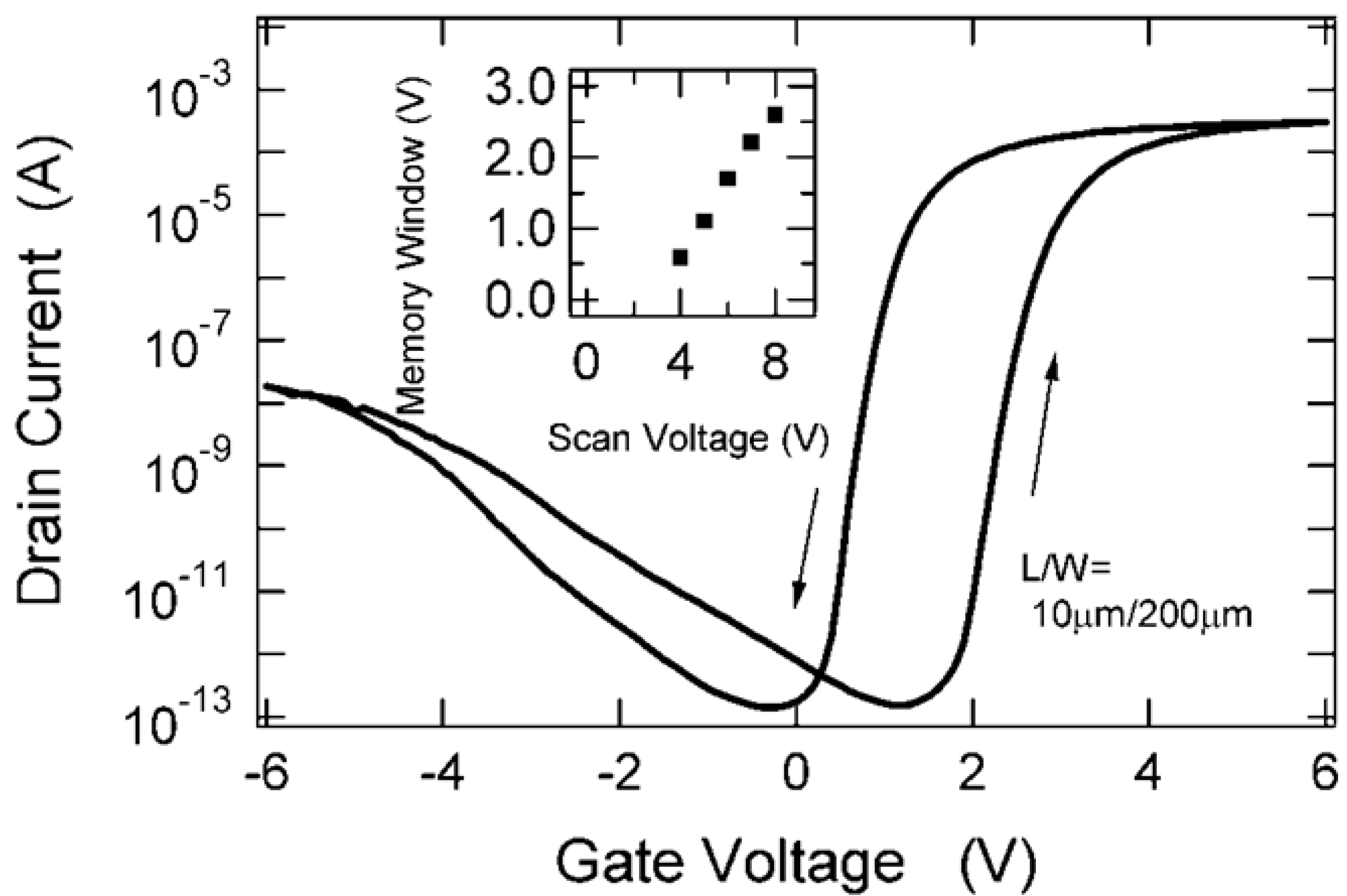

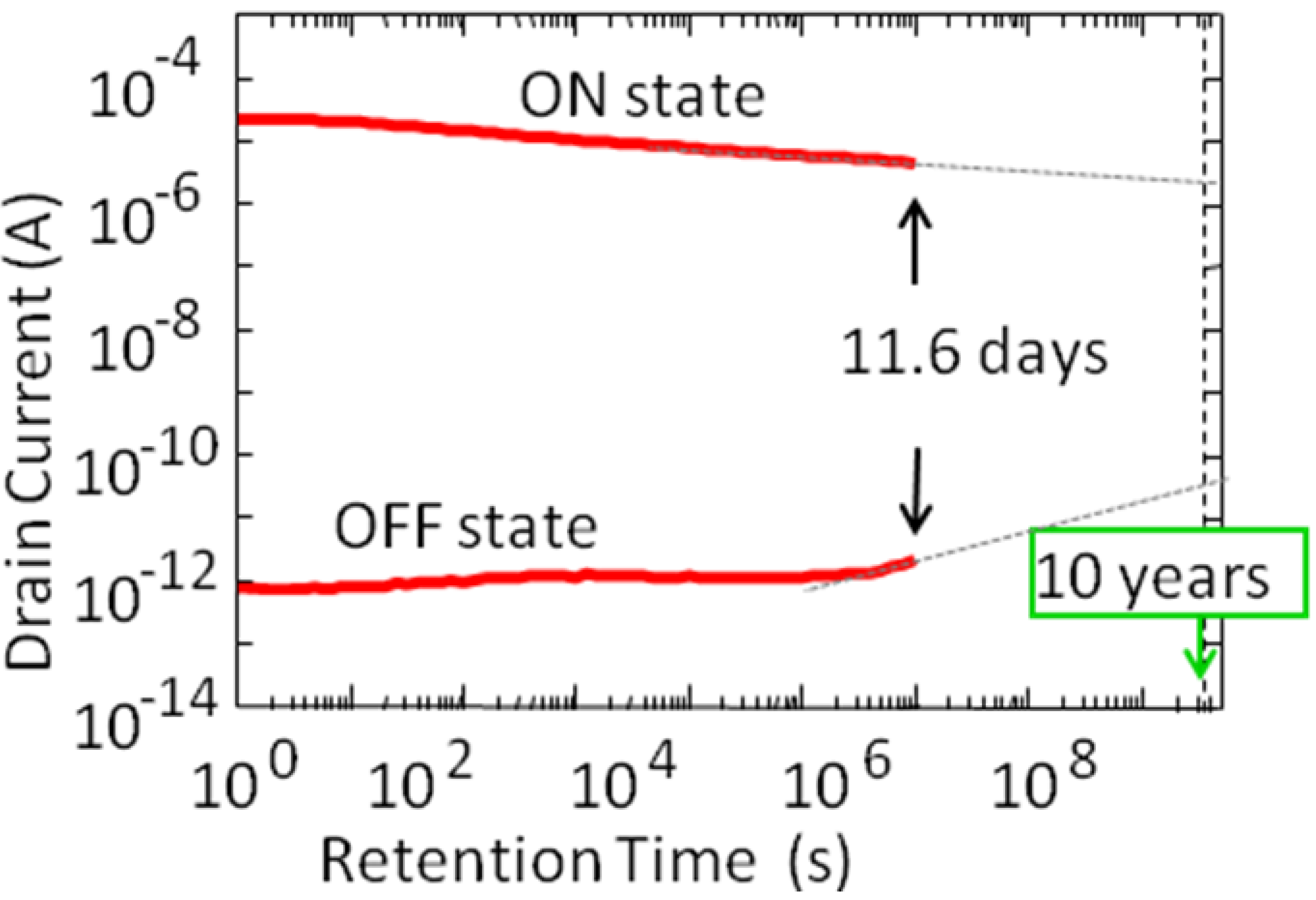

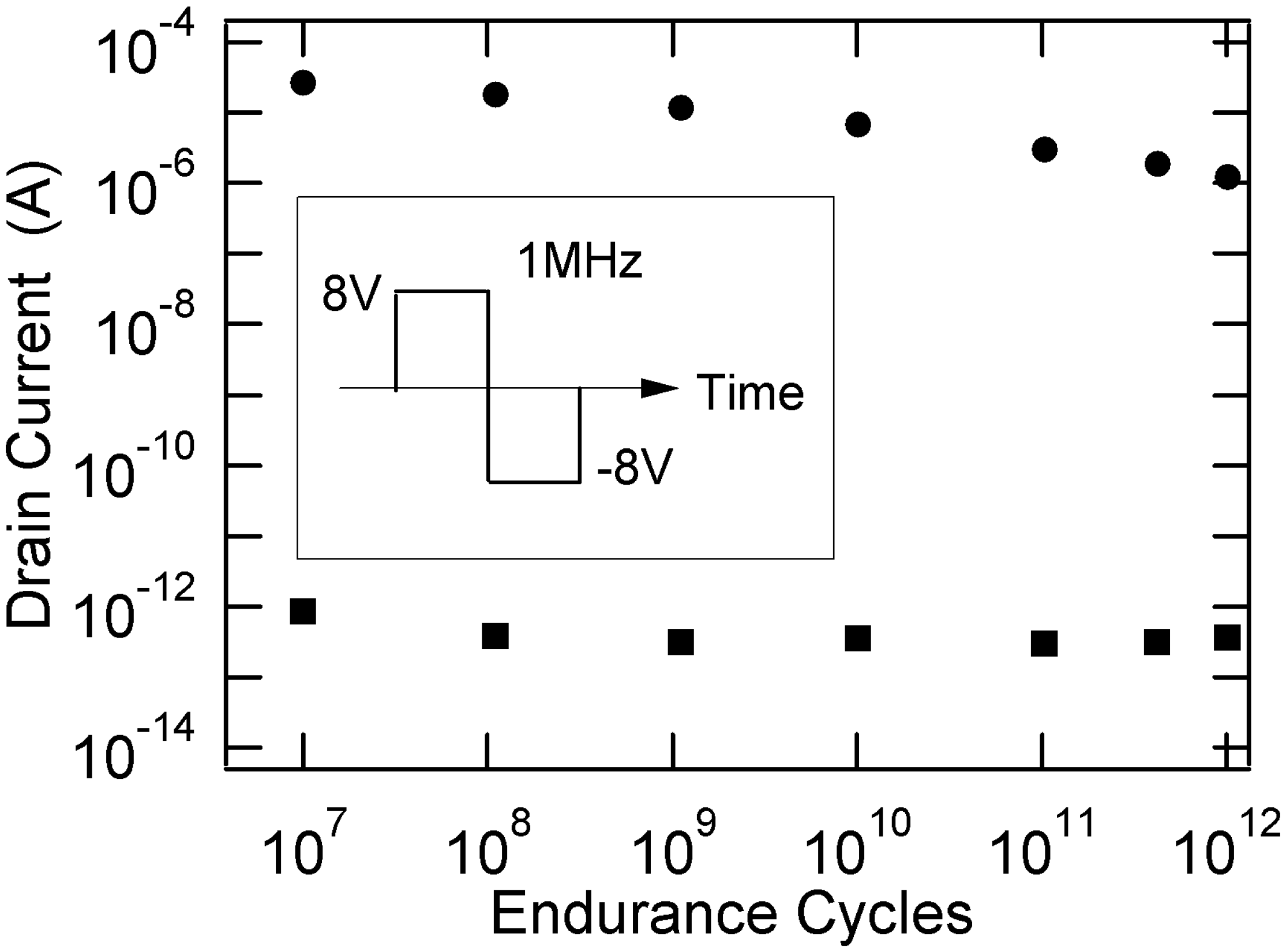

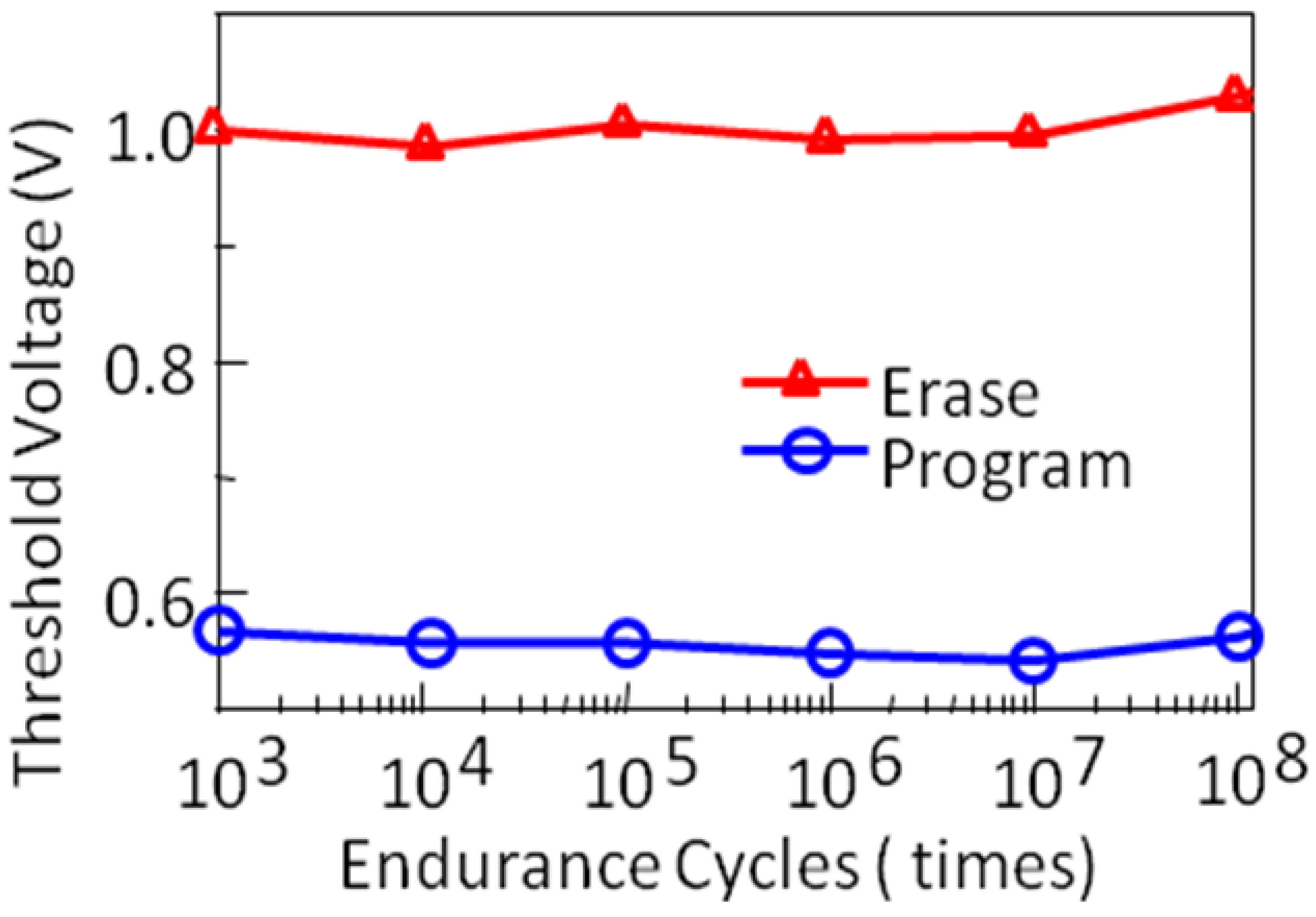

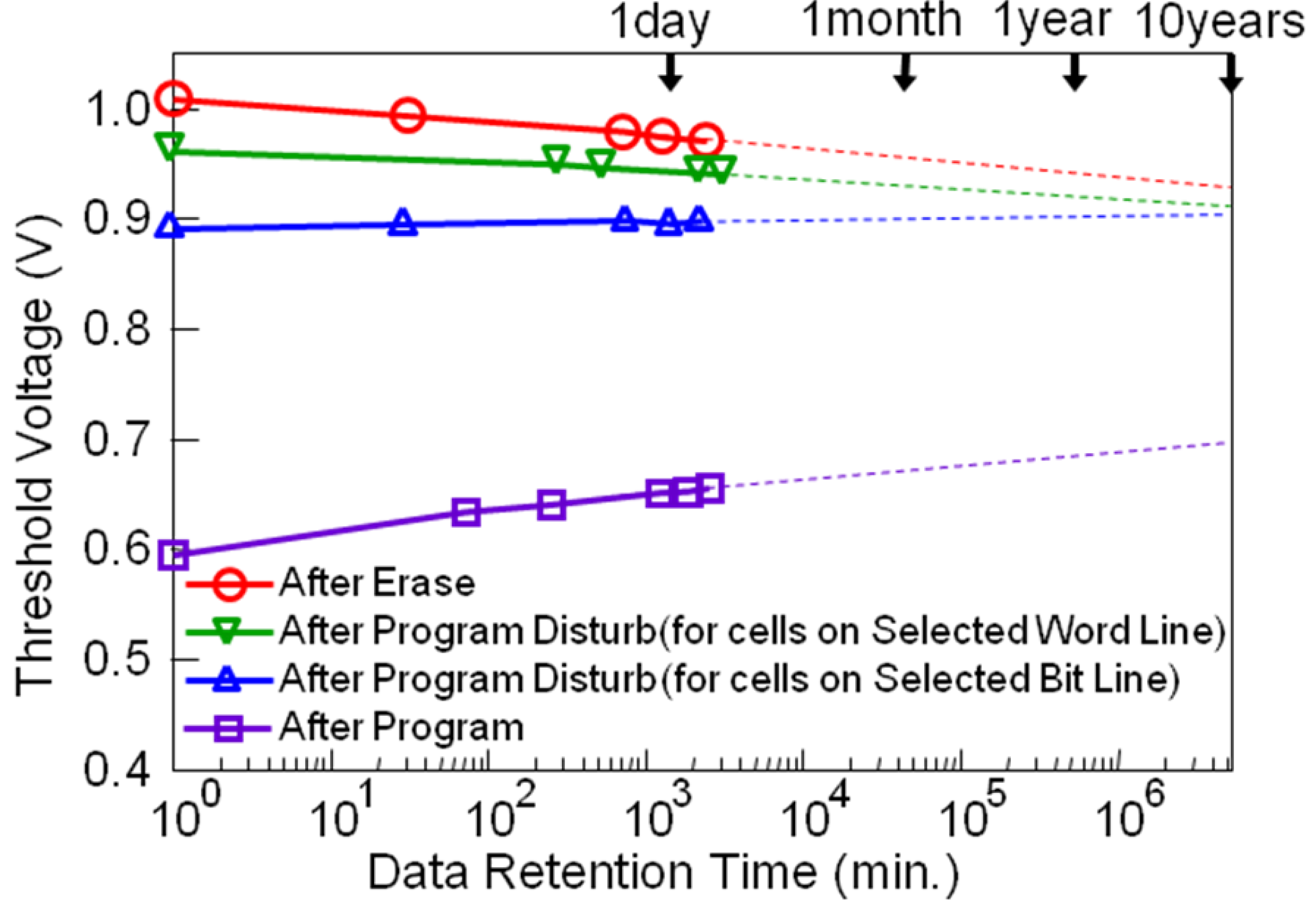

2. Progress of Ferroelectric-Gate Field-Effect-Transistors

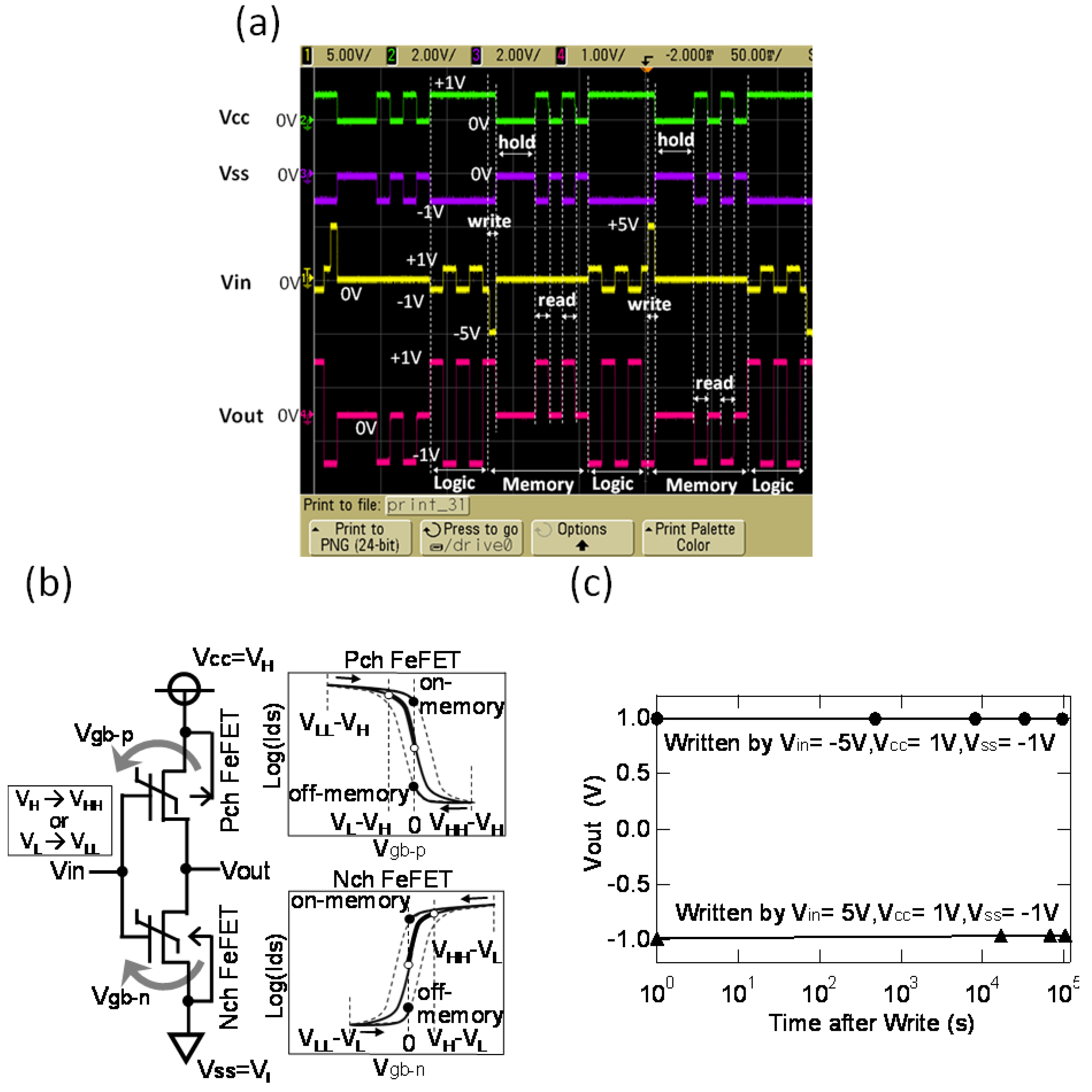

3. FeCMOS Nonvolatile Logic Circuits

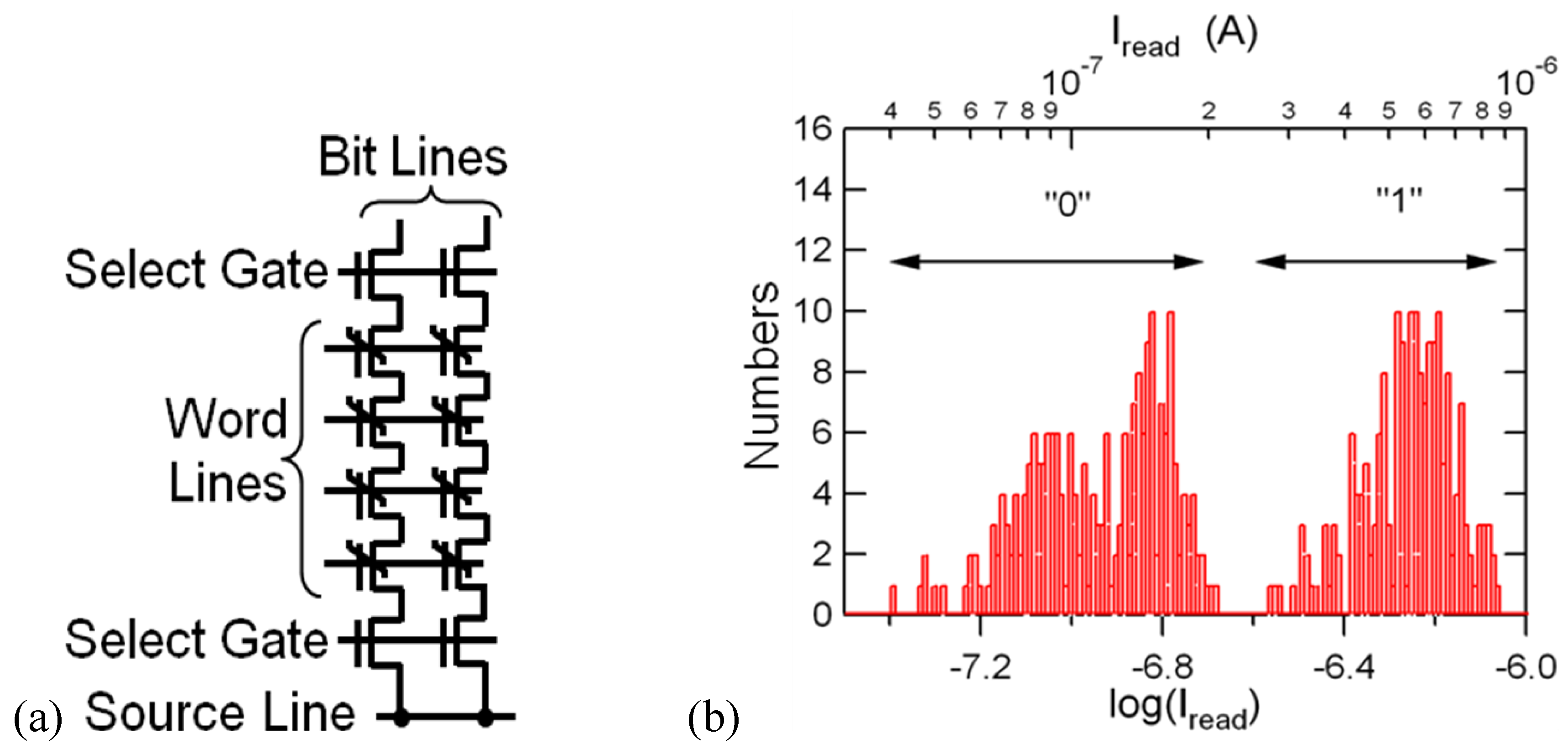

4. FeNAND Flash Memory

5. Conclusions

Acknowledgements

References

- Tarui, Y.; Hirai, T.; Teramoto, K.; Koike, H.; Nagashima, K. Application of the ferroelectric materials to ULSI memories. Appl. Surf. Sci. 1997, 113, 656–663. [Google Scholar] [CrossRef]

- Wu, S.Y. A new ferroelectric memory device, metal-ferroelectric-semiconductor transistor. IEEE Trans. Electron Devices 1974, ED-21, 499–504. [Google Scholar]

- Sugibuchi, K.; Kurogi, Y.; Endo, N. Ferroelectric field-effect memory device using Bi4Ti3O12 film. J. Appl. Phys. 1975, 46, 2877–2881. [Google Scholar] [CrossRef]

- Higuma, Y.; Matsui, Y.; Okuyama, M.; Nakagawa, T.; Hamakawa, Y. “MFS FET”—A new type of nonvolatile memory switch using PLZT film. Jpn. J. Appl. Phys. 1978, 17 Suppl. 17, 209–214. [Google Scholar]

- Rost, T.A.; Lin, H.; Rabson, T.A. Ferroelectric switching of a field-effect transistor with a lithium niobate gate insulator. Appl. Phys. Lett. 1991, 59, 3654–3656. [Google Scholar] [CrossRef]

- Rabson, T.A.; Rost, T.A.; Lin, H. Ferroelectric gate transistors. Integr. Ferroelectr. 1995, 6, 15–22. [Google Scholar] [CrossRef]

- Hirai, T.; Fujisaki, Y.; Nagashima, K.; Koike, H.; Tarui, Y. Preparation of SrBi2Ta2O9 film at low temperatures and fabrication of a metal/ferroelectric/insulator/semiconductor field effect transistor using Al/SrBi2Ta2O9/CeO2/Si(100) structures. Jpn. J. Appl. Phys. 1997, 36, 5908–5911. [Google Scholar] [CrossRef]

- Fujimori, Y.; Izumi, N.; Nakamura, T.; Kamisawa, A. Application of Sr2Nb2O7 family ferroelectric films for ferroelectric memory field effect transistor. Jpn. J. Appl. Phys. 1998, 37, 5207–5210. [Google Scholar] [CrossRef]

- Tokumitsu, E.; Fujii, G.; Ishiwara, H. Electrical properties of metal-ferroelectric-insulator-semiconductor (MFIS)- and metal-ferroelectric-metal-insulator-semiconductor (MFMIS)-FETs using ferroelectric SrBi2Ta2O9 film and SrTa2O6/SiON buffer layer. Jpn. J. Appl. Phys. 2000, 39, 2125–2130. [Google Scholar] [CrossRef]

- Sugiyama, H.; Kodama, K.; Nakaiso, T.; Noda, M.; Okuyama, M. Electrical properties of metal-ferroelectric-insulator-semiconductor-FET using SrBi2Ta2O9 film prepared at low temperature by pulsed laser deposition. Integr. Ferroelectr. 2001, 34, 1521–1531. [Google Scholar] [CrossRef]

- Ma, T.P.; Han, J.P. Why is nonvolatile ferroelectric memory field-effect transistor still elusive? IEEE Electron. Device Lett. 2002, 23, 386–388. [Google Scholar]

- Tokumitsu, E.; Okamoto, K.; Ishiwara, H. Low voltage operation of nonvolatile metal-ferroelectric-metal-insulator-semiconductor (MFMIS)-field-effect-transistors (FETs) using Pt/SrBi2Ta2O9/Pt/SrTa2O6/SiON/Si structures. Jpn. J. Appl. Phys. 2001, 40, 2917–2922. [Google Scholar] [CrossRef]

- Sakai, S. Semiconductor-ferroelectric storage devices and processes for producing the same. U.S. Patent 7,226,795, 2007. [Google Scholar]

- Development of the 1T FeRAM: Towards the realization of the ultra-Gbit next-generation semiconductor memory. AIST Press Release. Available online: http://www.aist.go.jp/aist_e/latest_research/2002/20021024/20021024.html (accessed on 24 October 2002).

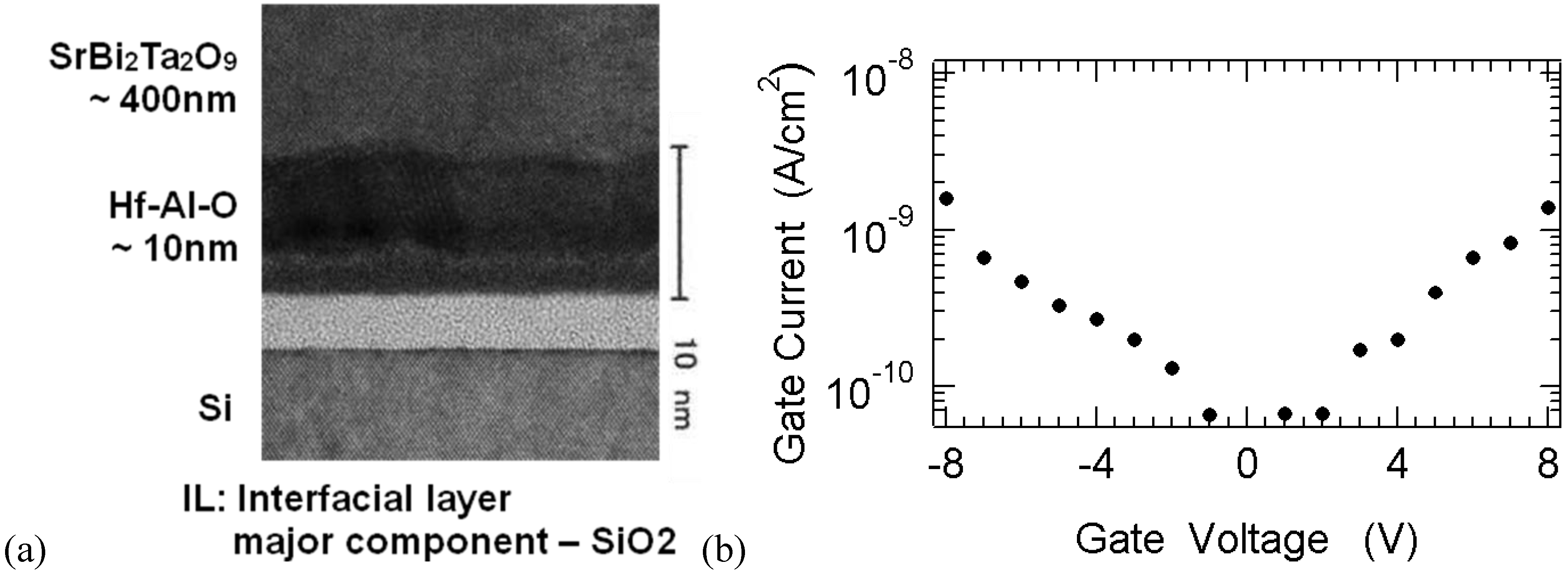

- Sakai, S.; Ilangovan, R. Metal-ferroelectric-insulator-semiconductor memory FET with long retention and high endurance. IEEE Electron Device Lett. 2004, 25, 369–371. [Google Scholar] [CrossRef]

- Sakai, S.; Takahashi, M.; Ilangovan, R. Long-retention ferroelectrie-gate FET with a (HfO2)x(Al2O3)1−x buffer-insulating layer for 1T FeRAM. Int. Electron Device Meet. Tech. Dig. 2004, 915–918. [Google Scholar]

- Sakai, S.; Ilangovan, R.; Takahashi, M. Pt/SrBi2Ta2O9/Hf-Al-O/Si field-effect-transistor with long retention using unsaturated ferroelectric polarization switching. Jpn. J. Appl. Phys. 2004, 43, 7876–7878. [Google Scholar] [CrossRef]

- Sakai, S. Gate Materials and Fabrication-processes of Metal-ferroelectric-insulator-semiconductor Memory FETs with Long Data Retention. Adv. Sci. Technol. 2006, 45, 2382–2391. [Google Scholar] [CrossRef]

- Zhang, F.; Hsu, S.T.; Ono, Y.; Ulrich, B.; Zhang, W.W.; Ying, H.; Stecker, L.; Evans, D.R.; Maa, J. Fabrication and characterization of sub-micron metal-ferroelectric-insulator-semiconductor field effect transistors with Pt/Pb5Ge3O11/ZrO2/Si Structure. Jpn. J. Appl. Phys. 2001, 40, L635–L637. [Google Scholar] [CrossRef]

- Li, T.; Hsu, S.T.; Ulrich, B.; Stecker, L.; Evans, D. One transistor ferroelectric memory devices with improved retention characteristics. Jpn. J. Appl. Phys. 2002, 41, 6890–6894. [Google Scholar] [CrossRef]

- Su, Y.D.; Shih, W.C.; Lee, J.Y.M. The characterization of retention properties of metal-ferroelectric (PbZr0.53Ti0.47O3)-insulator (Dy2O3, Y2O3)-semiconductor devices. Microelectron. Rel. 2007, 47, 619–622. [Google Scholar] [CrossRef]

- Cai, D.; Li, P.; Zhang, S.; Zhai, Y.; Ruan, A.; Ou, Y.; Chen, Y.; Wu, D. Fabrication and characteristics of a metal/ferroelectric/polycrystalline silicon/insulator/silicon field effect transistor. Appl. Phys. Lett. 2007, 90, 153513. [Google Scholar] [CrossRef]

- Chiang, Y.W.; Wu, J.M. Characterization of metal-ferroelectric (BiFeO3)-insulator (ZrO2)-silicon capacitors for nonvolatile memory applications. Appl. Phys. Lett. 2007, 91, 142103. [Google Scholar] [CrossRef]

- Shih, W.C.; Juan, P.C.; Lee, J.Y.M. Fabrication and characterization of metal-ferroelectric (PbZr0.53Ti0.47O3)-Insulator (Y2O3)-semiconductor field effect transistors for nonvolatile memory applications. J. Appl. Phys. 2008, 103, 094110. [Google Scholar] [CrossRef]

- Lu, X.B.; Maruyama, K.; Ishiwara, H. Metal-ferroelectric-insulator-Si devices using HfTaO buffer layers. Semicond. Sci. Technol. 2008, 23, 045002. [Google Scholar] [CrossRef]

- Kim, J.N.; Choi, Y.S.; Park, B.E. (Bi,La)4Ti3O12 as a ferroelectric layer and SrTa2O6 as a buffer layer for metal-ferroelectric-metal-insulator-semiconductor field-effect transistor. J. Ceram. Soc. Jpn. 2009, 117, 1032–1034. [Google Scholar] [CrossRef]

- Aizawa, K.; Park, B.E.; Kawashima, Y.; Takahashi, K.; Ishiwara, H. Impact of HfO2 buffer layers on data retention characteristics of ferroelectric-gate field-effect transistors. Appl. Phys. Lett. 2004, 85, 3199–3201. [Google Scholar] [CrossRef]

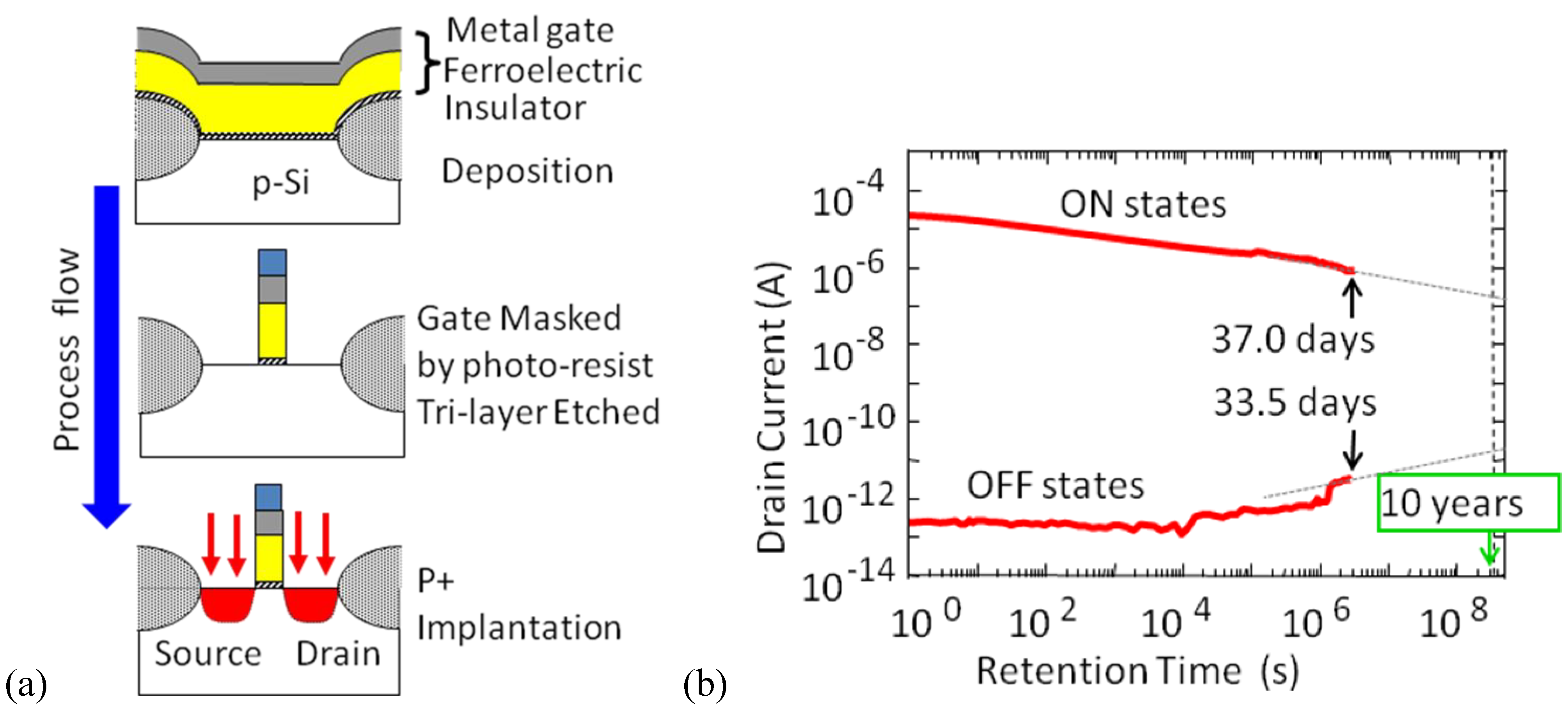

- Takahashi, M.; Sakai, S. Self-aligned-gate metal/ferroelectric/insulator/semiconductor field-effect transistors with long memory retention. Jpn. J. Appl. Phys. 2005, 44, L800–L802. [Google Scholar] [CrossRef]

- Takahashi, K.; Aizawa, K.; Park, B.E.; Ishiwara, H. Thirty-day-long data retention in ferroelectric-gate field-effect transistors with HfO2 buffer layers. Jpn. J. Appl. Phys. 2005, 44, 6218–6220. [Google Scholar] [CrossRef]

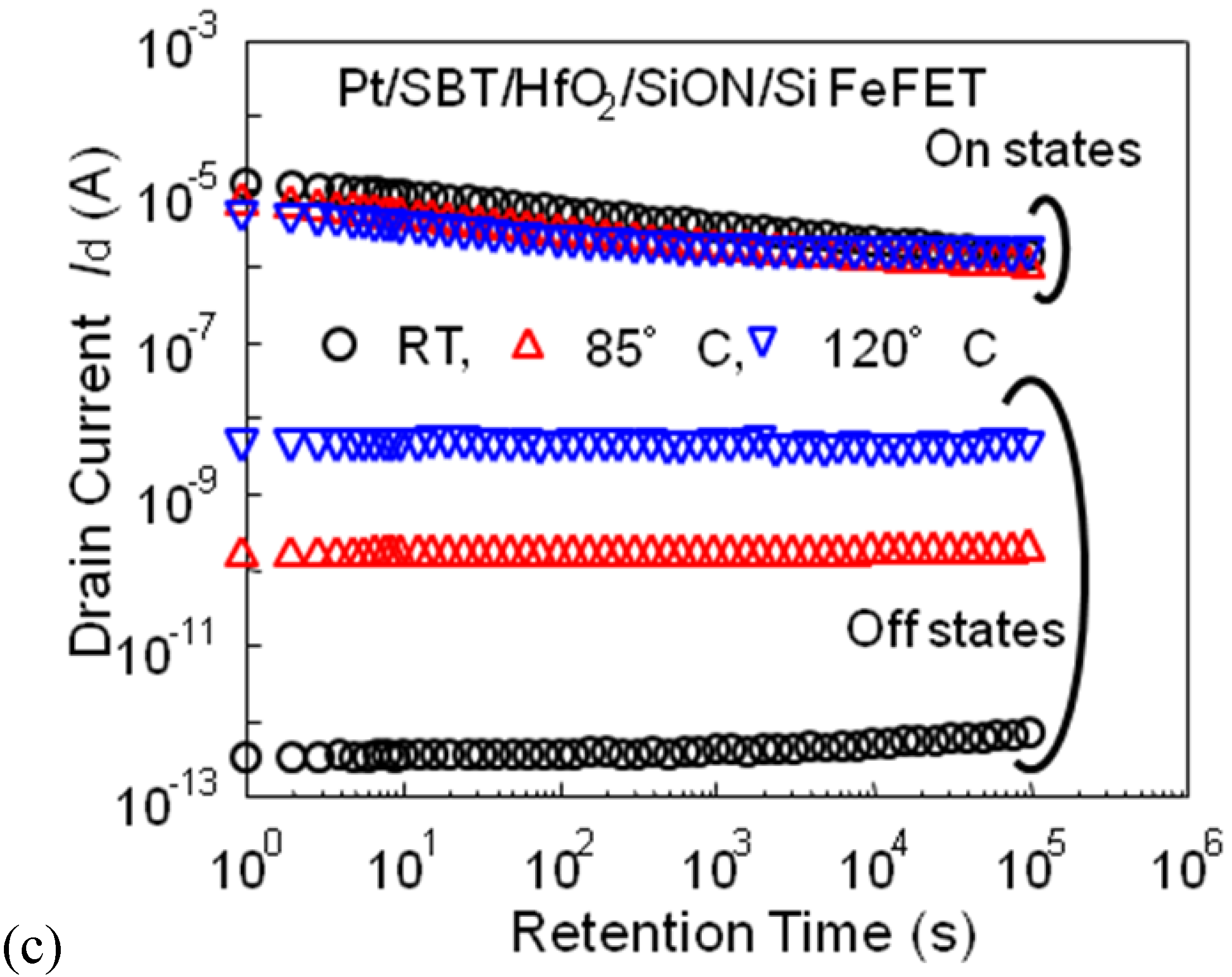

- Li, Q.H.; Sakai, S. Characterization of Pt/SrBi2Ta2O9/Hf-Al-O/Si field-effect transistors at elevated temperatures. Appl. Phys. Lett. 2006, 89, 222910. [Google Scholar] [CrossRef]

- Horiuchi, T.; Takahashi, M.; Li, Q.H.; Wang, S.Y.; Sakai, S. Lowered operation voltage in Pt/SBi2Ta2O9/HfO2/Si ferroelectric-gate field-effect transistors by oxynitriding Si. Semicond. Sci. Technol. 2010, 25, 055005. [Google Scholar] [CrossRef]

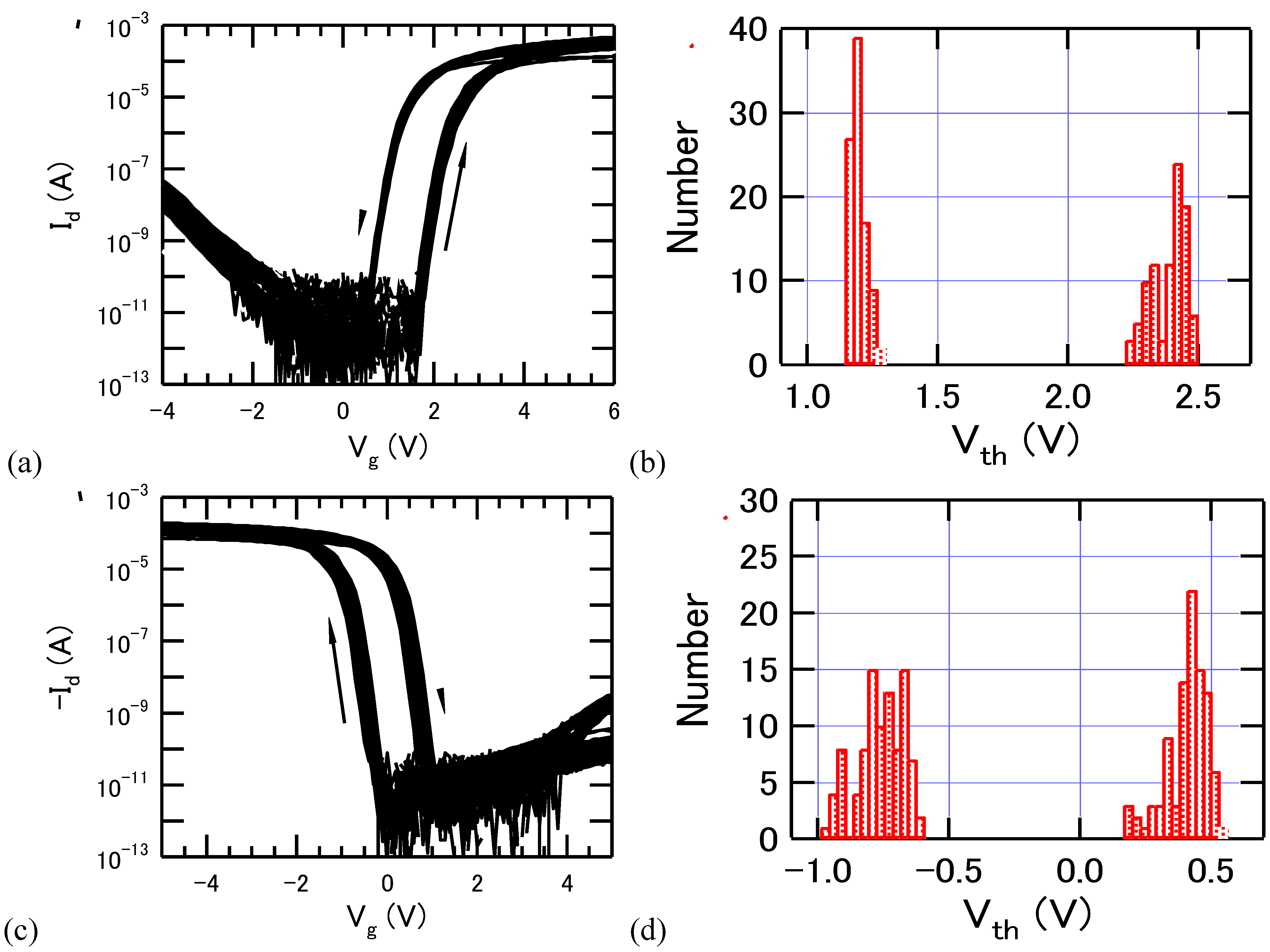

- Li, Q.H.; Takahashi, M.; Horiuchi, T.; Wang, S.Y.; Sakai, S. Threshold-voltage distribution of Pt/SrBi2Ta2O9/Hf-Al-O/Si MFIS FETs. Semicond. Sci. Technol. 2008, 23, 045011. [Google Scholar] [CrossRef]

- Li, Q.H.; Horiuchi, T.; Wang, S.Y.; Takahashi, M.; Sakai, S. Threshold voltage adjustment of ferroelectric-gate field effect transistors by ion implantation. Semicond. Sci. Technol. 2009, 24, 025012. [Google Scholar] [CrossRef]

- Le, V.H.; Takahashi, M.; Sakai, S. Fabrication and characterization of sub-0.6-μm ferroelectric-gate field-effect transistors. Semicond. Sci. Technol. 2010, 25, 115013. [Google Scholar]

- Kimura, H.; Hanyu, T.; Kameyama, M.; Fujimori, Y.; Nakamura, T.; Takasu, H. Complementary ferroelectric-capacitor logic for low-power logic-in-memory VLSI. IEEE J. Solid-State Circuits 2004, 39, 919–926. [Google Scholar] [CrossRef]

- Matsunaga, S.; Hayakawa, J.; Ikeda, S.; Miura, K.; Hasegawa, H.; Endoh, T.; Ohno, H.; Hanyu, T. Fabrication of a nonvolatile full adder based on logic-in-memory architecture using magnetic tunnel junctions. Appl. Phys. Express 2008, 1, 091301. [Google Scholar] [CrossRef]

- Takahashi, M.; Horiuchi, T.; Li, Q.H.; Wang, S.Y.; Sakai, S. Basic operation of novel ferroelectric CMOS circuits. Electron. Lett. 2008, 44, 467–468. [Google Scholar] [CrossRef]

- Takahashi, M.; Wang, S.Y.; Horiuchi, T.; Sakai, S. FeCMOS logic inverter circuits with nonvolatile-memory function. IEICE Electron. Express 2009, 6, 831–836. [Google Scholar] [CrossRef]

- Takeuchi, K.; Kameda, Y.; Fujimura, S.; Otake, H.; Hosono, K.; Shiga, H.; Watanabe, Y.; Futatsuyama, T.; Shindo, Y.; Kojima, M.; Iwai, M.; Shirakawa, M.; Ichige, M.; Hatakeyama, K.; Tanaka, S.; Kamei, T.; Fu, J.Y.; Cernea, A.; Li, Y.; Higashitani, M.; Hemink, G.; Sato, S.; Oowada, K.; Lee, S.C.; Hayashida, N.; Wan, J.; Lutze, J.; Tsao, S.; Mofidi, M.; Sakurai, K.; Tokiwa, N.; Waki, H.; Nozawa, Y.; Kanazawa, K.; Ohshima, S. A 56nm CMOS 99 mm2 8Gb multi-level NAND flash memory with 10 MB/s program throughput. IEEE J. Solid-State Circuits 2006, 507–516. [Google Scholar]

- Takeuchi, K. Novel co-design of NAND flash memory and NAND flash controller circuits sub-30 nm low-power high-speed Solid-State Drives (SSD). In Proceedings of IEEE Symposium on VLSI Circuits, Honolulu, HI, USA, 18–20 June 2008; pp. 124–125.

- Sakai, S.; Takahashi, M.; Takeuchi, K.; Li, Q.H.; Horiuchi, T.; Wang, S.Y.; Yun, K.Y.; Takamiya, M.; Sakurai, T. Highly scalable Fe(ferroelectric)-NAND cell with MFIS (metal-ferroelectric-insulator-semiconductor) structure for sub-10 nm Tera-bit capacity NAND flash memories. In Proceedings of 23rd IEEE Non-Volatile Semiconductor Memory Workshop/3rd International Conference on Memory Technology and Design, Opio, France, 18–22 May 2008; pp. 103–105.

- Wang, S.Y.; Takahashi, M.; Li, Q.H.; Takauchi, K.; Sakai, S. Operational method of a ferroelectric (Fe)-NAND flash memory array. Semicond. Sci. Technol. 2009, 24, 105029. [Google Scholar] [CrossRef]

© 2010 by the authors; licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution license (http://creativecommons.org/licenses/by/3.0/).

Share and Cite

Sakai, S.; Takahashi, M. Recent Progress of Ferroelectric-Gate Field-Effect Transistors and Applications to Nonvolatile Logic and FeNAND Flash Memory. Materials 2010, 3, 4950-4964. https://doi.org/10.3390/ma3114950

Sakai S, Takahashi M. Recent Progress of Ferroelectric-Gate Field-Effect Transistors and Applications to Nonvolatile Logic and FeNAND Flash Memory. Materials. 2010; 3(11):4950-4964. https://doi.org/10.3390/ma3114950

Chicago/Turabian StyleSakai, Shigeki, and Mitsue Takahashi. 2010. "Recent Progress of Ferroelectric-Gate Field-Effect Transistors and Applications to Nonvolatile Logic and FeNAND Flash Memory" Materials 3, no. 11: 4950-4964. https://doi.org/10.3390/ma3114950