Remarkable Reduction in IG with an Explicit Investigation of the Leakage Conduction Mechanisms in a Dual Surface-Modified Al2O3/SiO2 Stack Layer AlGaN/GaN MOS-HEMT

Abstract

:1. Introduction

2. Materials and Methods

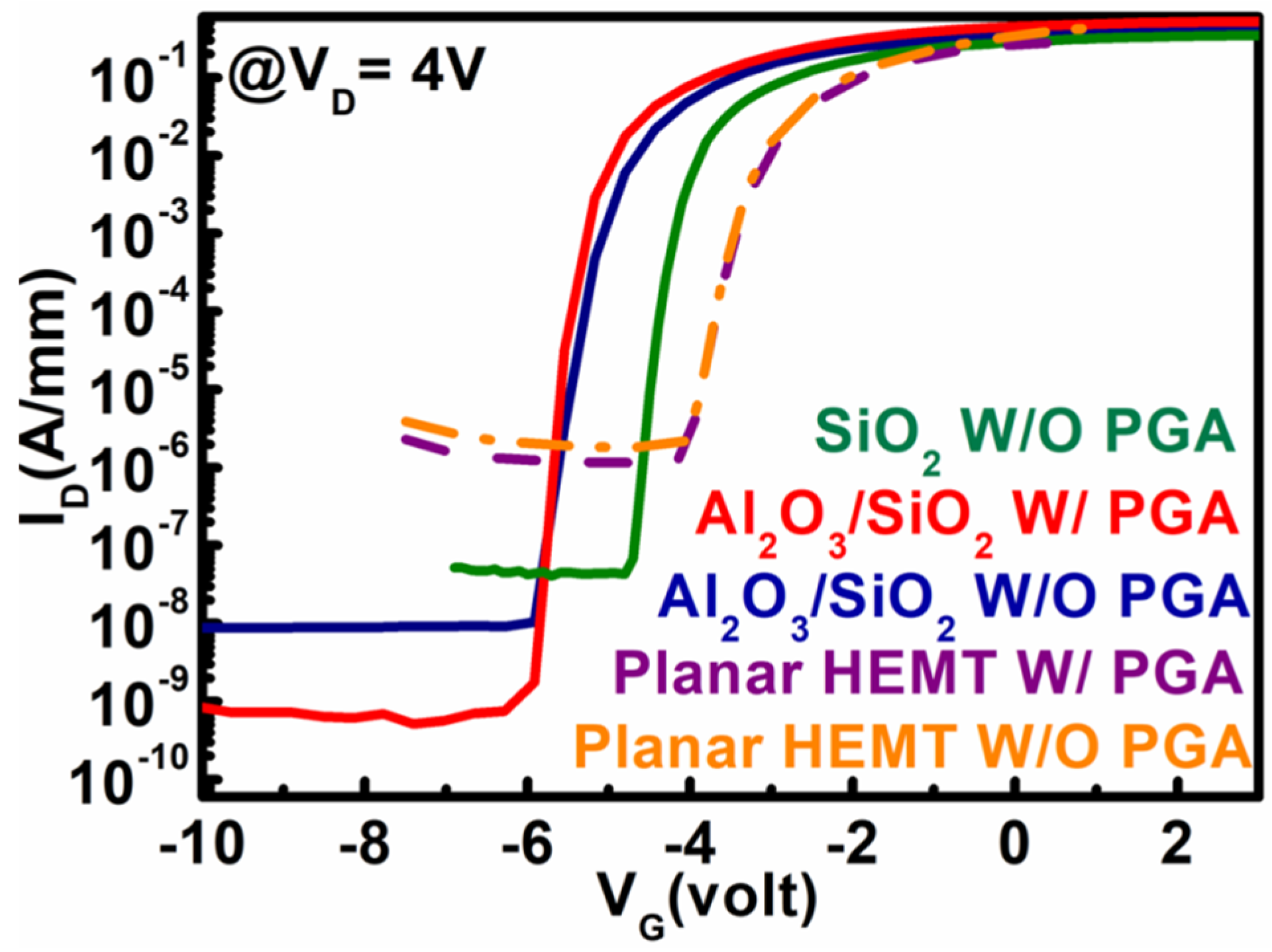

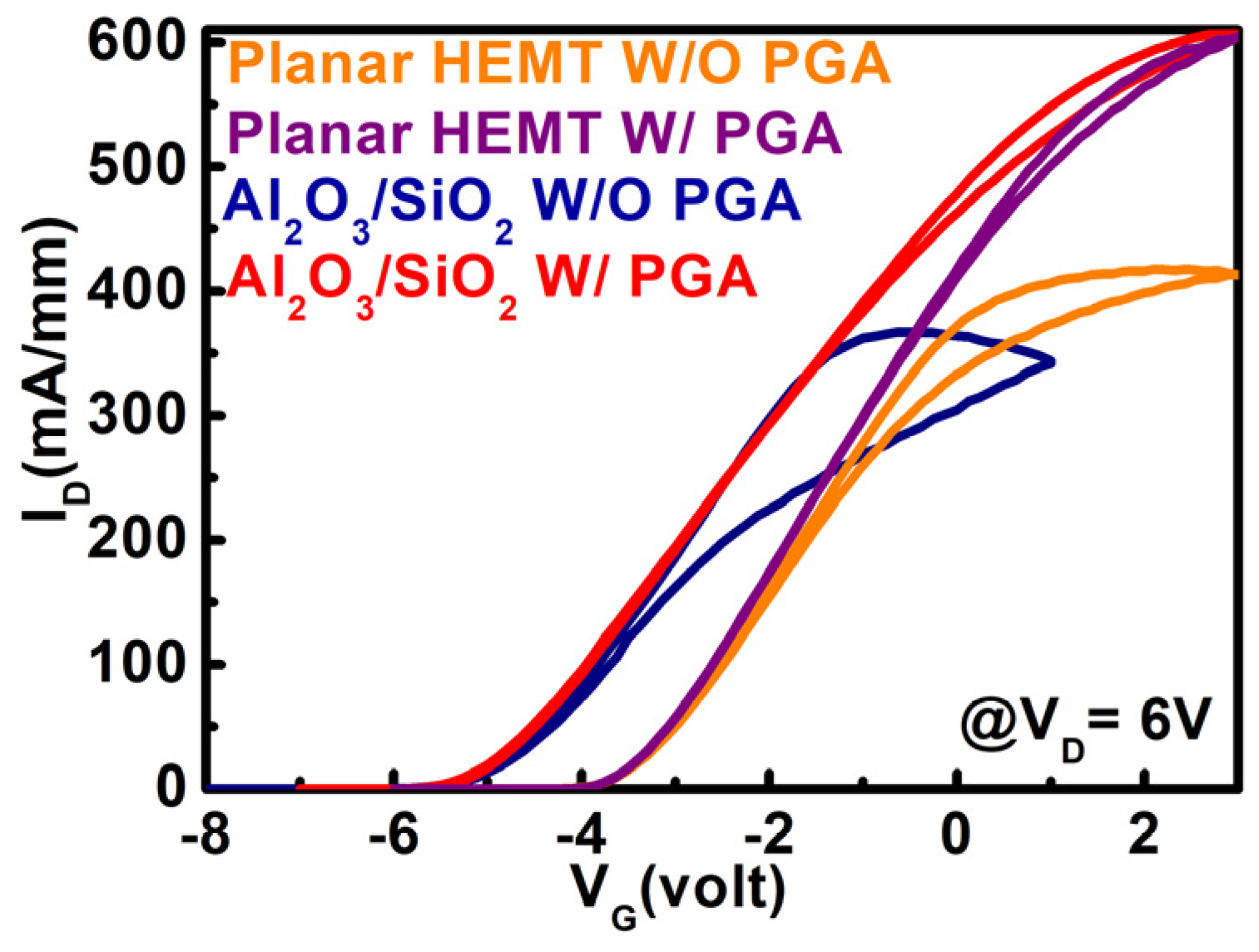

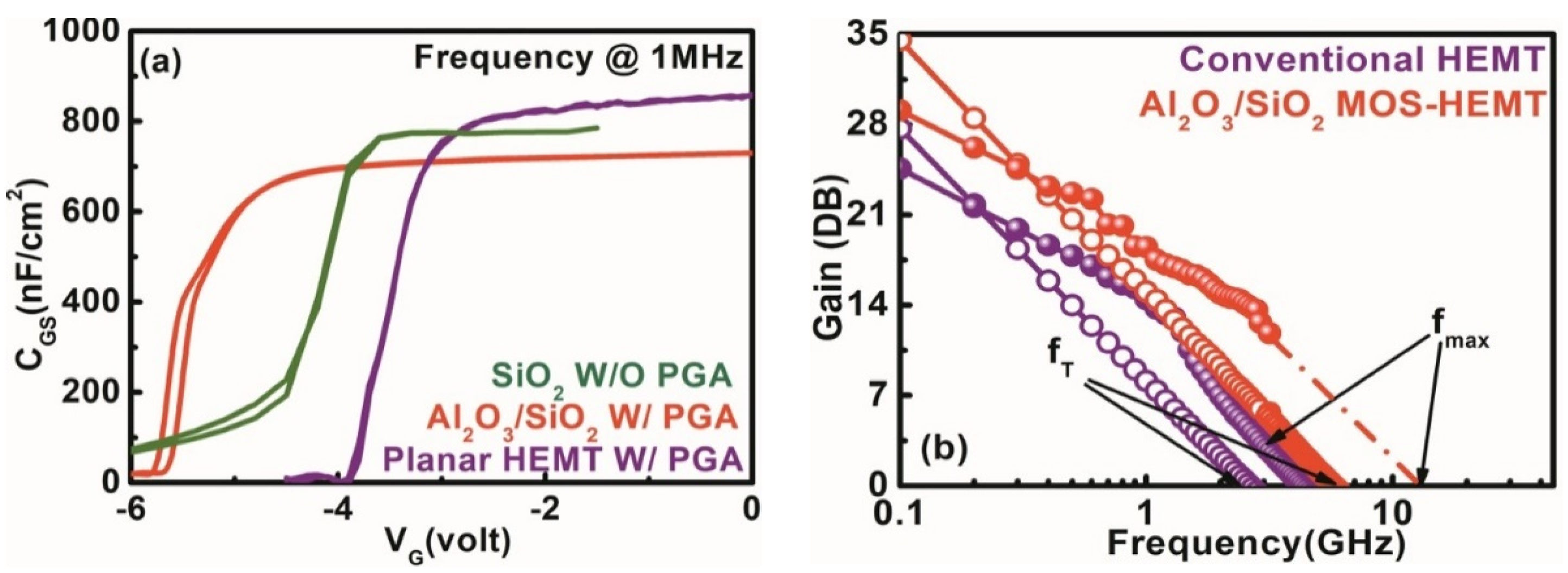

3. Results

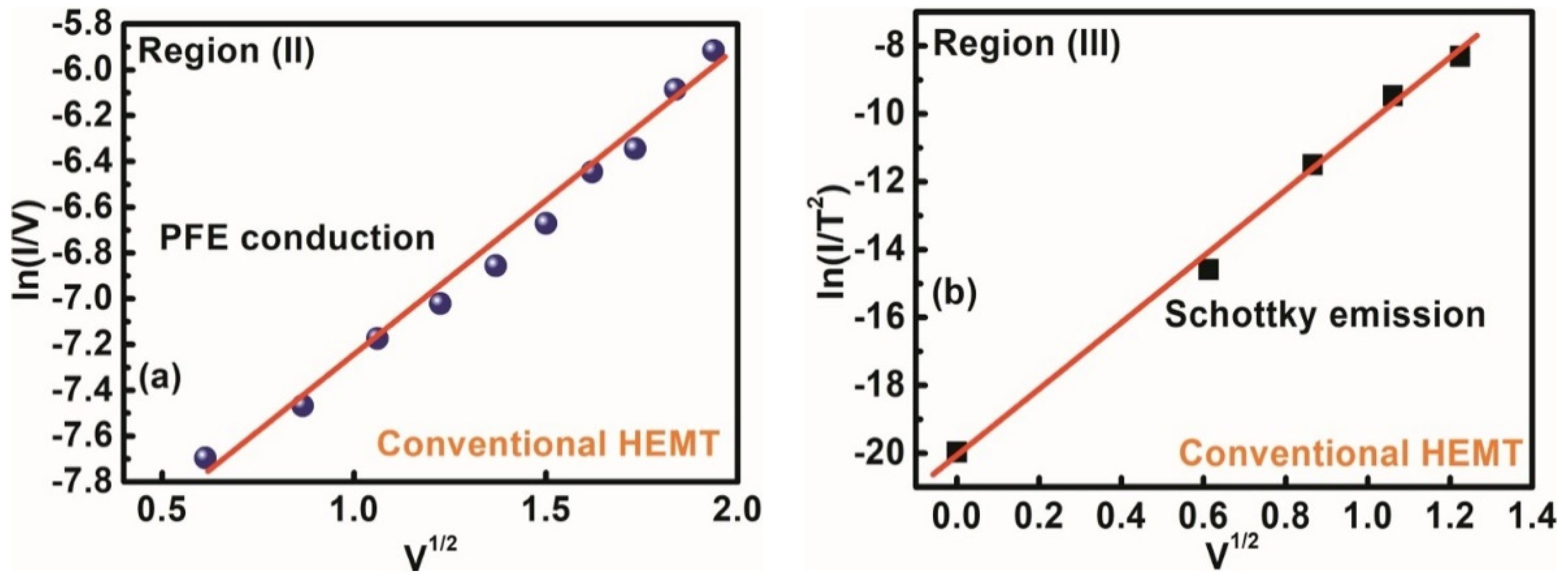

3.1. Gate Leakage Mechanisms in the AlGaN/GaN MOS–HEMT before Gate Annealing

3.2. Gate Leakage Mechanisms in the AlGaN/GaN MOS–HEMT after Gate Annealing

3.3. Gate Leakage Mechanisms in the AlGaN/GaN HEMT

4. Conclusions

Author Contributions

Funding

Institutional Review Board Statement

Informed Consent Statement

Data Availability Statement

Acknowledgments

Conflicts of Interest

References

- Borga, M.; Meneghini, M.; Benazzi, D.; Canato, E.; Püsche, R.; Derluyn, J.; Abid, I.; Medjdoub, F.; Meneghesso, G.; Zanoni, E. Buffer breakdown in GaN-on-Si HEMTs: A comprehensive study based on a sequential growth experiment. Microelectron. Reliab. 2019, 100–101, 113461. [Google Scholar] [CrossRef]

- Ardaravĭcius, L.; Matulionis, A.; Liberis, J.; Kiprijanovic, O.; Ramonas, M.; Eastman, L.F.; Shealy, J.R.; Vertiatchikh, A. Electron drift velocity in AlGaN/GaN channel at high electric fields. Appl. Phys. Lett. 2003, 83, 4038–4040. [Google Scholar] [CrossRef]

- Mazumder, S.; Wang, Y.H. Investigation of HfSiOX passivation effect on AlGaN/GaN HEMT. In Proceedings of the 2020 International Symposium on Devices, Circuits and Systems, ISDCS, Howrah, India, 4–6 March 2020; pp. 1–4. [Google Scholar]

- Hori, Y.; Yatabe, Z.; Hashizume, T. Characterization of interface states in Al2O3/AlGaN/GaN structures for improved performance of high-electron-mobility transistors. J. Appl. Phys. 2013, 114, 244503. [Google Scholar] [CrossRef] [Green Version]

- Dutta, G.; DasGupta, N.; DasGupta, A. Gate Leakage Mechanisms in AlInN/GaN and AlGaN/GaN MIS-HEMTs and Its Modelling. IEEE Trans. Electron Devices 2017, 64, 3609–3615. [Google Scholar] [CrossRef]

- Jun, L.; Lei, Z.S.; Han, M.M.; Bin, H.; Lei, Y.X.; Cheng, Z.J.; Hua, M.X.; Yue, H. Trap states induced by reactive ion etching in AlGaN/GaN high-electron-mobility transistors. Chin. Phys. B 2015, 24, 117305. [Google Scholar]

- Reddy, M.S.P.; Park, W.S.; Im, K.S.; Lee, J.H. Dual-surface modification of AlGaN/GaN HEMTs using TMAH and piranha solutions for enhancing current and 1/f-Noise Characteristics. IEEE J. Electron Devices Soc. 2018, 6, 791–796. [Google Scholar] [CrossRef]

- Eller, B.S.; Yang, J.; Nemanich, R.J. Electronic surface and dielectric interface states on GaN and AlGaN. J. Vac. Sci. Technol. A 2013, 31, 050807. [Google Scholar] [CrossRef]

- Koyama, Y.; Hashizume, T.; Hasegawa, H. Formation processes and properties of Schottky and ohmic contacts on n-type GaN for field effect transistor applications. Solid State Electron. 1999, 43, 1483–1488. [Google Scholar] [CrossRef]

- Rickert, K.A.; Ellis, A.B.; Himpsel, F.J.; Sun, J.; Kuech, T.F. n-GaN surface treatments for metal contacts studied via X-ray photoemission spectroscopy. Appl. Phys. Lett. 2002, 80, 204–206. [Google Scholar] [CrossRef] [Green Version]

- Hashizume, T.; Ootomo, S.; Oyama, S.; Konishi, M.; Hasegawa, H. Chemistry and electrical properties of surfaces of GaN and GaN/AlGaN heterostructures. J. Vac. Sci. Technol. B 2001, 19, 1675–1681. [Google Scholar] [CrossRef] [Green Version]

- Nepal, N.; Garces, N.Y.; Meyer, D.J.; Hite, J.K.; Mastro, M.A.; Eddy, C.R., Jr. Assessment of GaN surface pre-treatment for atomic layer deposited high-k dielectrics. Appl. Phys. Exp. 2011, 4, 055802. [Google Scholar] [CrossRef]

- Ganguly, S.; Verma, J.; Hu, Z.; Xing, H.; Jena, D. Performance enhancement of InAlN/GaN HEMTs by KOH surface treatment. Appl. Phys. Exp. 2014, 7, 034102. [Google Scholar] [CrossRef]

- Zhuang, D.; Edgar, J.H. Wet etching of GaN, AlN, and SiC: A review. Mater. Sci. Eng. R Rep. 2005, 48, 1–46. [Google Scholar] [CrossRef]

- Son, D.H.; Jo, Y.W.; Won, C.H.; Lee, J.H.; Seo, J.H.; Lee, S.H.; Lim, J.W.; Kim, J.H.; Kang, I.M.; Cristoloveanu, S.; et al. Normally-off AlGaN/GaN-based MOS-HEMT with self-terminating TMAH wet recess etching. Solid State Electron. 2018, 141, 7–12. [Google Scholar] [CrossRef]

- Lee, K.W.; Chou, D.W.; Wu, H.R.; Huang, J.J.; Wang, Y.H.; Houng, M.P.; Chang, S.J.; Su, Y.K. GaN MOSFET with liquid phase deposited oxide gate. Electron. Lett. 2002, 38, 829–830. [Google Scholar] [CrossRef]

- Tsurumi, N.; Ueno, H.; Murata, T.; Ishida, H.; Uemoto, Y.; Ueda, T.; Inoue, K.; Tanaka, T. AlN passivation over AlGaN/GaN HFETs for surface heat spreading. IEEE Trans. Electron Devices 2010, 57, 980–985. [Google Scholar] [CrossRef]

- Mazumder, S.; Li, S.H.; Wu, Z.G.; Wang, Y.H. Combined Implications of UV/O3 Interface Modulation with HfSiOX Surface Passivation on AlGaN/AlN/GaN MOS-HEMT. Crystals 2021, 11, 136. [Google Scholar] [CrossRef]

- Zhou, H.; Lou, X.; Sutherlin, K.; Summers, J.; Kim, S.B.; Chabak, K.D.; Gordon, R.G.; Ye, P.D. DC and RF Performance of AlGaN/GaN/SiC MOSHEMTs With Deep Sub-Micron T-Gates and Atomic Layer Epitaxy MgCaO as Gate Dielectric. IEEE Electron Device Lett. 2017, 38, 1409–1412. [Google Scholar] [CrossRef]

- Yue, Y.; Hao, Y. AlGaN/GaN MOS-HEMT with HfO2 Dielectric and Al2O3 Interfacial Passivation Layer Grown by Atomic Layer Deposition. IEEE Electron Device Lett. 2008, 29, 838–840. [Google Scholar] [CrossRef]

- Dutta, G.; DasGupta, N.; DasGupta, A. Effect of Sputtered-Al2O3 Layer Thickness on the Threshold Voltage of III-Nitride MIS-HEMTs. IEEE Trans. Electron Devices 2016, 63, 1450–1458. [Google Scholar] [CrossRef]

- Yang, S.K.; Mazumder, S.; Wu, Z.G.; Wang, Y.H. Performance enhancement in N2 plasma modified AlGaN/AlN/GaN MOS-HEMT using HfAlOX gate dielectric with Γ-shaped gate engineering. Materials 2021, 14, 1534. [Google Scholar] [CrossRef] [PubMed]

- Byun, Y.C.; Lee, J.G.; Meng, X.; Lee, J.S.; Lucero, A.T.; Kim, S.J.; Young, C.D.; Kim, M.J.; Kim, J. Low temperature (100 °C) atomic layer deposited-ZrO2 for recessed gate GaN HEMTs on Si. Appl. phys. Lett. 2017, 111, 082905. [Google Scholar] [CrossRef]

- Wu, T.Y.; Lin, S.K.; Sze, P.W.; Huang, J.J.; Chien, W.C.; Hu, C.C.; Tsai, M.J.; Wang, Y.H. AlGaN/GaN MOSHEMTs with liquid-phase deposited TiO2 as gate dielectric. IEEE Trans. Electron Devices 2009, 56, 2911–2916. [Google Scholar] [CrossRef]

- Hashizume, T.; Ootomo, S.; Hasegawa, H. Suppression of current collapse in insulated gate AlGaN/GaN heterostructure field-effect transistors using ultrathin Al2O3 dielectric. Appl. Phys. Lett. 2003, 83, 2952–2954. [Google Scholar] [CrossRef] [Green Version]

- Rawat, A.; Meer, M.; Surana, V.K.; Bhardwaj, N.; Pendem, V.; Garigapati, N.S.; Yadav, Y.; Ganguly, S.; Saha, D. Thermally Grown TiO2 and Al2O3 for GaN-Based MOS-HEMTs. IEEE Trans. Electron Devices 2018, 65, 3725–3731. [Google Scholar] [CrossRef]

- Liu, H.Y.; Ou, W.C.; Hsu, W.C. Investigation of post oxidation annealing effect on H2O2-Grown Al2O3/AlGaN/GaN MOS-HEMTs. IEEE J. Electron Devices Soc. 2016, 4, 358–364. [Google Scholar] [CrossRef]

- Liu, Z.H.; Ng, G.I.; Arulkumaran, S.; Maung, Y.K.T.; Zhou, H. Temperature-dependent forward gate current transport in atomic layer-deposited Al2O3/AlGaN/GaN metal-insulator-semiconductor high electron mobility transistor. Appl. Phys. Lett. 2011, 98, 163501-1–163501-3. [Google Scholar] [CrossRef]

- Hua, M.; Liu, C.; Yang, S.; Liu, S.; Fu, K.; Dong, Z.; Cai, Y.; Zhang, B.; Chen, K.J. Characterization of leakage and reliability of SiNXgate dielectric by low-pressure chemical vapor deposition for GaN based MIS-HEMTs. IEEE Trans. Electron Devices 2015, 62, 3215–3222. [Google Scholar] [CrossRef]

- Mazumder, S.; Pal, P.; Tsai, T.J.; Lin, P.C.; Wang, Y.H. A low program voltage enabled flash like AlGaN/GaN stack layered MIS-HEMTs using trap assisted technique. ECS J. Solid State Sci. Technol. 2021, 10, 055019. [Google Scholar] [CrossRef]

- Wang, C.; Chen, Y.C.; Hsu, H.T.; Tsao, Y.F.; Lin, Y.C.; Dee, C.F.; Chang, E.Y. Adoption of the Wet Surface Treatment Technique for the Improvement of Device Performance of Enhancement-Mode AlGaN/GaN MOS-HEMTs for Millimeter-Wave Applications. Materials 2021, 14, 6558. [Google Scholar] [CrossRef]

- Do, J.W.; Jung, H.W.; Shin, M.J.; Ahn, H.K.; Kim, H.; Kim, R.H.; Cho, K.J.; Chang, S.J.; Min, B.G.; Yoon, H.S.; et al. The effects of tetramethylammonium hydroxide treatment on the performance of recessed-gate AlGaN/GaN high electron mobility transistors. Thin Solid Film. 2017, 628, 31–35. [Google Scholar] [CrossRef]

- Sharma, P.; Sundaram, M.M.; Singh, D.; Ahuja, R. Highly Energetic and Stable Gadolinium/Bismuth Molybdate with a Fast Reactive Species, Redox Mechanism of Aqueous Electrolyte. ACS Appl. Energy Mater. 2020, 3, 12385–12399. [Google Scholar] [CrossRef]

- Manickam, M.; Singh, P.; Issa, T.B.; Thurgate, S.; Marco, R.D. Lithium insertion into manganese dioxide electrode in MnO2/Zn aqueous battery: Part I. A preliminary study. J. Power Source 2004, 130, 254–259. [Google Scholar] [CrossRef]

- Zheng, Y.Y.; Yue, H.; Cheng, Z.J.; Qian, F.; Yu, N.J.; Hua, M.X. A study on Al2O3 passivation in GaN MOS- HEMT by pulsed stress. Chin. Phys. B 2008, 17, 1405–1409. [Google Scholar] [CrossRef]

- Vetury, R.; Zhang, N.Q.; Keller, S.; Mishra, U.K. The impact of surface states on the DC and RF characteristics of AlGaN/GaN HFETs. IEEE Trans. Electron Devices 2001, 48, 560–566. [Google Scholar] [CrossRef]

- Liu, C.; Chor, E.F.; Tan, L.S. Improved DC performance of AlGaN/GaN high electron mobility transistors using hafnium oxide for surface passivation. Thin Solid Film. 2007, 515, 4369–4372. [Google Scholar] [CrossRef]

- Ozaki, S.; Makiyama, K.; Ohki, T.; Okamoto, N.; Kumazaki, Y.; Kotani, J.; Kaneki, S.; Nishiguchi, K.; Nakamura, N.; Hara, N.; et al. Improved DC performance and current stability of ultrathin-Al2O3/InAlN/GaN MOSHEMTs with post-metallization-annealing process. Semicond. Sci. Technol. 2020, 35, 035027. [Google Scholar] [CrossRef]

- Mazumder, S.; Wu, Z.G.; Pan, P.C.; Li, S.H.; Wang, Y.H. DC performance improvement of nanochannel AlGaN/AlN/GaN HEMTs with reduced OFF-state leakage current by post-gate annealing modulation. Semicond. Sci. Technol. 2021, 36, 095003. [Google Scholar] [CrossRef]

- Sze, S.M.; Ng, K.K. Physics of Semiconductor Devices, 3rd ed.; Springer Science & Business Media: Berlin, Germany, 2006. [Google Scholar]

- Sareni, B.; Krahenbuhl, L.; Beroual, A.; Brosseau, C. Effective dielectric constant of random composite materials. J. Appl. Phys. 1997, 81, 2375–2383. [Google Scholar] [CrossRef] [Green Version]

- Pal, P.; Mazumder, S.; Huang, C.W.; Lu, D.D.; Wang, Y.H. Impact of Barrier Layer on High Thermal and Mechanical Stability of a Flexible Resistive Memory in Neural Network Application. ACS Appl. Electron. Mater. 2021, 4, 1072–1081. [Google Scholar] [CrossRef]

- Wang, Q.; Periasamy, K.; Fu, Y.; Chan, Y.T.; Tan, C.M.; Bajalovic, N.; Wang, J.C.; Loke, D.K. Analytical modeling electrical conduction in resistive-switching memory through current-limiting-friendly combination frame works. AIP Adv. 2020, 10, 085117. [Google Scholar] [CrossRef]

- Kim, H.; Lee, J.; Liu, D.; Lu, W. Gate current leakage and breakdown mechanism in unpassivated AlGaN/GaN high electron mobility transistors by post-gate annealing. Appl. Phys. Lett. 2005, 86, 143505. [Google Scholar] [CrossRef]

- Turuvekere, S.; Karumuri, N.; Rahman, A.A.; Bhattacharya, A.; Dasgupta, A.; DasGupta, N. Gate leakage mechanisms in AlGaN/GaN and AlInN/GaN HEMTs: Comparison and modeling. IEEE Trans. Electron Devices 2013, 60, 3157–3165. [Google Scholar] [CrossRef]

- Chikhaoui, W.; Bluet, J.M.; Bru-Chevallier, C.; Dua, C.; Aubry, R. Deep traps analysis in AlGaN/GaN heterostructure transistor. Phys. Status Solidi C 2010, 7, 92–95. [Google Scholar] [CrossRef]

- Mazumder, S.; Wu, Z.G.; Wang, Y.H. Positive Shifting of Vth with Enhanced DC Performance in AlGaN/GaN Schottky-Gate HEMT through Optimized UV/O3 Treated Gate Interface and Thermal Engineering. ECS J. Solid State Electron. 2022, 11, 065002. [Google Scholar] [CrossRef]

- Shi, Y.T.; Xu, W.Z.; Zeng, C.K.; Ren, F.F.; Ye, J.D.; Zhou, D.; Chen, D.J.; Zhang, R.; Zheng, Y.; Lu, H. High-k HfO2-Based AlGaN/GaN MIS-HEMTs With Y2O3 Interfacial Layer for High Gate Controllability and Interface Quality. IEEE J. Electron Devices Soc. 2019, 8, 15–19. [Google Scholar] [CrossRef]

- Chou, B.Y.; Hsu, W.C.; Liu, H.Y.; Lee, C.S.; Wu, Y.S.; Sun, W.C.; Wei, S.Y.; Yu, S.M.; Chiang, M.H. Investigations of AlGaN/GaN MOS-HEMT with Al2O3 deposition by ultrasonic spray pyrolysis method. Semicond. Sci. Technol. 2015, 30, 015009. [Google Scholar] [CrossRef]

- Meng, D.; Lin, S.; Wen, C.P.; Wang, M.; Wang, J.; Hao, Y.; Zhang, Y.; Lau, K.M.; Wu, W. Low leakage current and high-cut off frequency AlGaN/GaN MOSHEMT using submicrometer-footprint thermal oxidized TiO2/NiO as gate dielectric. IEEE Electron Device Lett. 2013, 34, 738–740. [Google Scholar] [CrossRef]

- Huang, C.Y.; Mazumder, S.; Lin, P.C.; Lee, K.W.; Wang, Y.H. Improved electrical characteristics of AlGaN/GaN high-electron-mobility transistor with Al2O3/ZrO2 stacked gate dielectrics. Materials 2022, 15, 6895. [Google Scholar] [CrossRef]

| Reference | LG (µm) | Gate Dielectric (Thickness) | IDMAX (mA/mm) | GMMAX (mS/mm) | SS (mV/dec) | ION/ IOFF | Gate Leakage (A/mm) | fMAX (GHz) | fMAX × LG (GHz·µm) |

|---|---|---|---|---|---|---|---|---|---|

| [19] | 0.09 (T-gate) | Mg0.25Ca0.75O (4 nm) | 1250 | 345 (@ VD = 9 V) | 104 | ~108 | ~10−7 (@VG = −7 V) | 160 | 14.4 |

| [27] | 1 (rectangular gate) | Al2O3 (12 nm) | 853.3 | 159 (@ VD = 7 V) | 90.3 | ~107 | ~10−8 (@ VG = −100 V) | 23.4 | 23.4 |

| [48] | 1 (rectangular gate) | HfO2/Y2O3 (12/1 nm) | 600 | 4.5 (@ VD = 0.05 V) | 70 | 109 | ~10−10 (@ VG = −9 V) | - | - |

| [31] | 0.15 (T-gate) | Al2O3 (7 nm) | 859 | 484 (@ VD = 5 V) | - | - | ~10−8 (@ VG = −4 V) | 100 | 15 |

| [49] | 1 (rectangular gate) | Al2O3 (20 nm) | 855 | 140.6 (@ VD = 7 V) | - | - | ~10−9 (@ VG = −50 V) | 19.1 | 19.1 |

| [50] | 0.4 (T-gate) | TiO2/NiO (>35 nm) | 709 | 149 (@ VD = 10 V) | - | - | ~10−9 (@ VG = −10 V) | 40 | 16 |

| [51] | 1 (rectangular gate) | ZrO2/Al2O3 (12/1 nm) | 847 | 181 (@ VD = 4 V) | 95 | ~107 | - | 9.1 | 9.1 |

| This work | 2 (rectangular gate) | Al2O3/SiO2 (10/5 nm) | 720 | 120 (@ VD = 4 V) | 82 | 109 | 10−12 (@ VG = −12 V) | 13.58 | 27.16 |

Publisher’s Note: MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations. |

© 2022 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Mazumder, S.; Pal, P.; Lee, K.-W.; Wang, Y.-H. Remarkable Reduction in IG with an Explicit Investigation of the Leakage Conduction Mechanisms in a Dual Surface-Modified Al2O3/SiO2 Stack Layer AlGaN/GaN MOS-HEMT. Materials 2022, 15, 9067. https://doi.org/10.3390/ma15249067

Mazumder S, Pal P, Lee K-W, Wang Y-H. Remarkable Reduction in IG with an Explicit Investigation of the Leakage Conduction Mechanisms in a Dual Surface-Modified Al2O3/SiO2 Stack Layer AlGaN/GaN MOS-HEMT. Materials. 2022; 15(24):9067. https://doi.org/10.3390/ma15249067

Chicago/Turabian StyleMazumder, Soumen, Parthasarathi Pal, Kuan-Wei Lee, and Yeong-Her Wang. 2022. "Remarkable Reduction in IG with an Explicit Investigation of the Leakage Conduction Mechanisms in a Dual Surface-Modified Al2O3/SiO2 Stack Layer AlGaN/GaN MOS-HEMT" Materials 15, no. 24: 9067. https://doi.org/10.3390/ma15249067