InGaAs FinFETs Directly Integrated on Silicon by Selective Growth in Oxide Cavities

Abstract

:1. Introduction

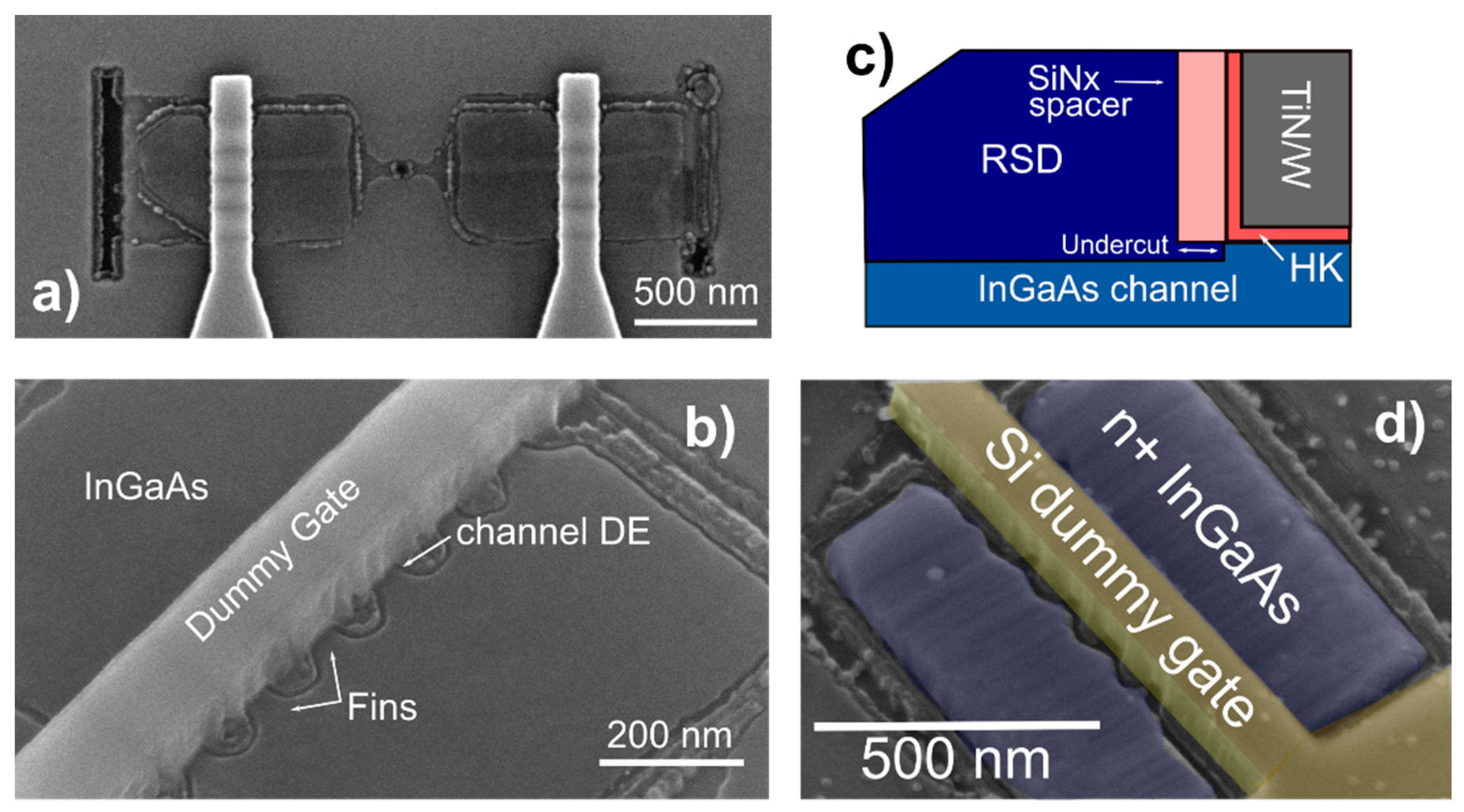

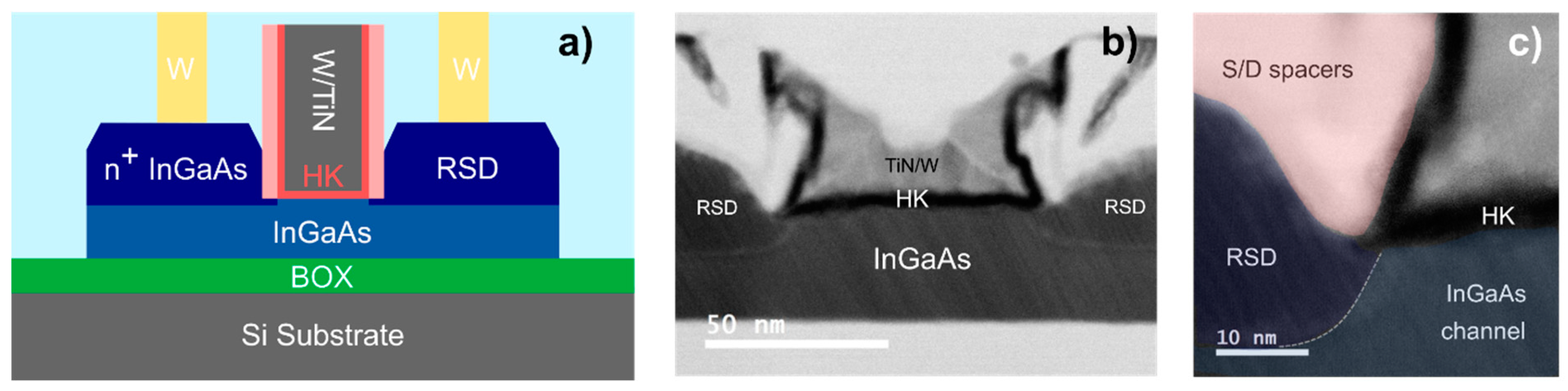

2. Materials and Methods

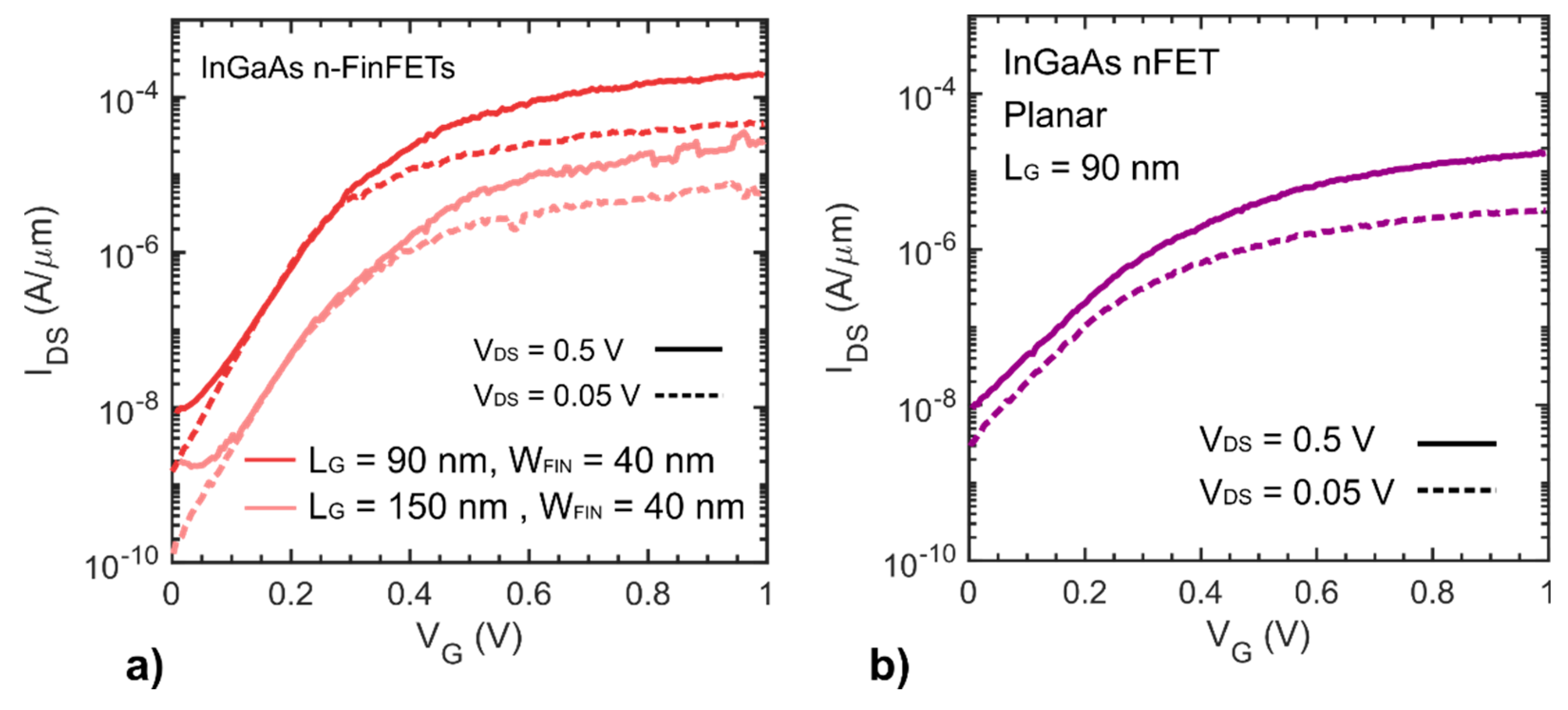

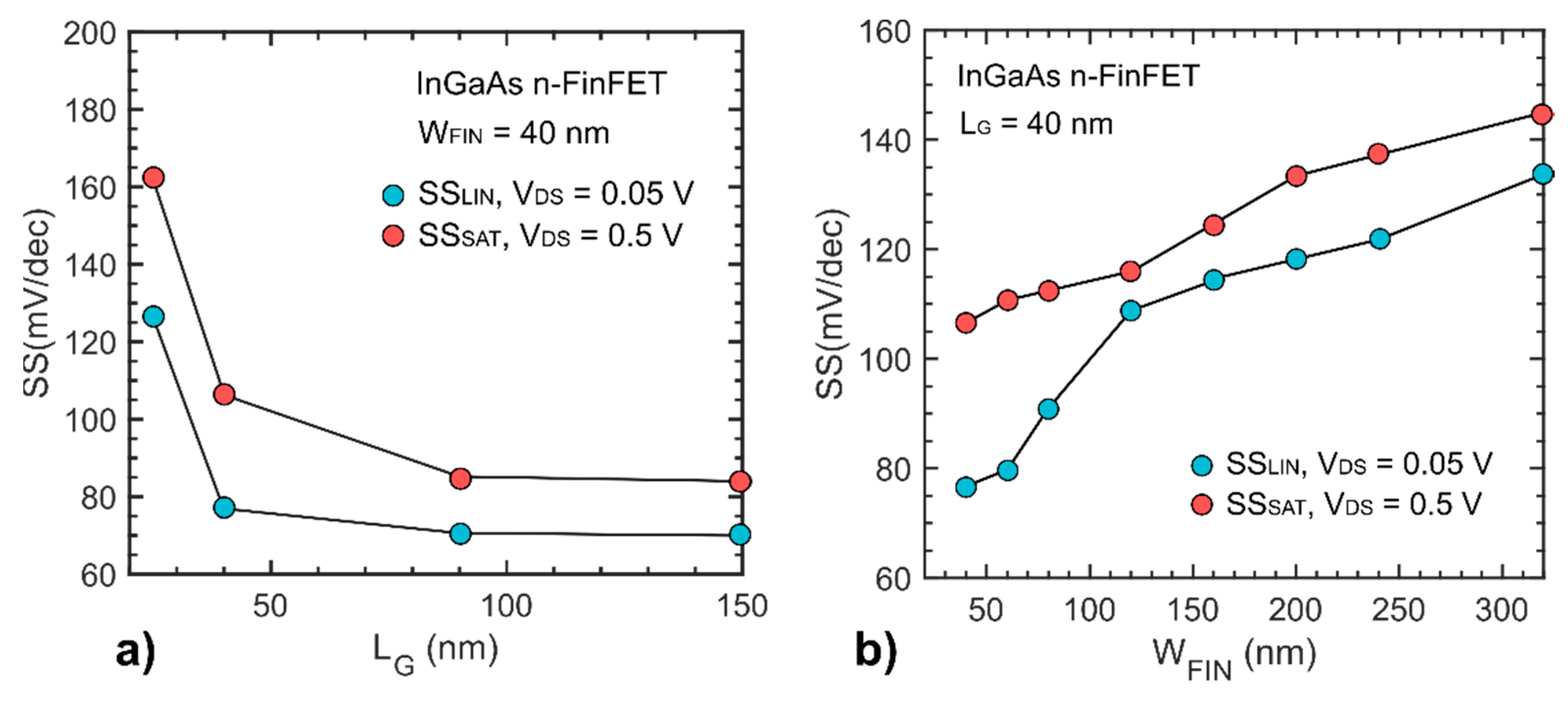

3. Results and Discussion

4. Conclusions

Author Contributions

Funding

Acknowledgments

Conflicts of Interest

References

- Del Alamo, J.A. Nanometre-scale electronics with III–V compound semiconductors. Nature 2011, 479, 317–323. [Google Scholar] [CrossRef] [PubMed]

- Hahn, H.; Deshpande, V.; Caruso, E.; Sant, S.; O’Connor, E.; Baumgartner, Y.; Sousa, M.; Caimi, D.; Olziersky, A.; Palestri, P.; et al. A scaled replacement metal gate InGaAs-on-Insulator n-FinFET on Si with record performance. In Proceedings of the 2017 IEEE International Electron Devices Meeting, San Francisco, CA, USA, 2–6 December 2017; pp. 17.5.1–17.5.4. [Google Scholar]

- Zota, C.B.; Convertino, C.; Deshpande, V.; Merkle, T.; Sousa, M.; Caimi, D.; Czomomaz, L. InGaAs-on-Insulator MOSFETs Featuring Scaled Logic Devices and Record RF Performance. In Proceedings of the 2018 IEEE Symposium on VLSI Technology, Honolulu, HI, USA, 18–22 June 2018. [Google Scholar]

- Sun, X.; D’Emic, C.; Cheng, C.-W.; Majumdar, A.; Sun, Y.; Cartier, E.; Bruce, R.L.; Frank, M.; Miyazoe, H.; Shiu, K.-T.; et al. High performance and Low Leakage Current InGaAs-on-Silicon FinFETs with 20 nm Gate Length. In Proceedings of the 2017 Symposia on VLSI Technology and Circuits, Kyoto, Japan, 5–8 June 2017; pp. 40–41. [Google Scholar]

- Vardi, A.; del Alamo, J. Sub-10-nm fin-width self-aligned InGaAs FinFETs. IEEE Electron Device Lett. 2016, 37, 1104–1107. [Google Scholar] [CrossRef]

- Czornomaz, L.; Daix, N.; Kerber, P.; Lister, K.; Caimi, D.; Rossel, C.; Sousa, M.; Uccelli, E.; Fompeyrine, J. Scalability of ultra-thin- body and BOX InGaAs MOSFETs on silicon. In Proceedings of the 2013 European Solid-State Device Research Conference, Bucharest, Romania, 16–20 September 2013; pp. 143–146. [Google Scholar]

- Djara, V.; Deshpande, V.; Uccelli, E.; Daix, N.; Caimi, D.; Rossel, C.; Sousa, M.; Siegwart, H.; Marchiori, C.; Lubyshev, D.; et al. An InGaAs on Si platform for CMOS with 200 mm InGaAs-OI substrate, gate-first, replacement gate planar and FinFETs down to 120 nm contact pitch. In Proceedings of the 2015 Symposium on VLSI Technology (VLSI Technology), Kyoto, Japan, 16–18 June 2015; pp. T176–T177. [Google Scholar]

- Convertino, C.; Zota, C.B.; Caimi, D.; Sousa, M.; Czornomaz, L. InGaAs FinFETs 3D Sequentially Integrated on FDSOI Si CMOS with Record Perfomance. In Proceedings of the 48th European Solid-State Device Research Conference (ESSDERC), Dresden, Germany, 3–6 September 2018; pp. 162–165. [Google Scholar]

- Zota, C.B.; Lindelow, F.; Wernersson, L.E.; Lind, E. InGaAs tri-gate MOSFETs with record on-current. In Proceedings of the 2016 IEEE International Electron Devices Meeting (IEDM), San Francisco, CA, USA, 3–7 Decemebr 2016; pp. 3.2.1–3.2.4. [Google Scholar]

- Lindelow, F. Gated Hall effect measurements on selectively grown InGaAs nanowires. Nanotechnology 2017, 28, 205204. [Google Scholar] [CrossRef] [PubMed]

- Li, J.Z.; Bai, J.; Park, J.-S.; Adekore, B.; Fox, K.; Carroll, M.; Lochtefeld, A.; Shellenbarger, Z. Defect reduction of GaAs epitaxy on Si (001) using selective aspect ratio trapping. Appl. Phys. Lett. 2007, 91, 021114. [Google Scholar] [CrossRef]

- Waldron, N.; Merckling, C.; Guo, W.; Ong, P.; Teugels, L.; I, S.A.; Tsvetanova, D.; Sebaai, F.; van Dorp, D.H.; Milenin, A.; et al. An InGaAs/InP quantum well finfet using the replacement fin process integrated in an RMG flow on 300 mm Si substrates. In Proceedings of the 2014 Symposia on VLSI Technology & Circuits, Honolulu, HI, USA, 9–13 June 2014; pp. 26–27. [Google Scholar]

- Schmid, H.; Borg, M.; Moselund, K.; Gignac, L.; Breslin, C.M.; Bruley, J.; Cutaia, D.; Riel, H. Template-assisted selective epitaxy of III–V nanoscale devices for co-planar heterogeneous integration with Si. Appl. Phys. Lett. 2015, 106, 233101. [Google Scholar] [CrossRef] [Green Version]

- Borg, M.; Schmid, H.; Moselund, K.E.; Cutaia, D.; Riel, H. Mechanisms of template-assisted selective epitaxy of InAs nanowires on Si. J. Appl. Phys. 2015, 117, 144303. [Google Scholar] [CrossRef]

- Czornomaz, L.; Uccelli, E.; Sousa, M.; Deshpande, V.; Djara, V.; Caimi, D.; Rossell, M.D.; Erni, R.; Fompeyrine, J. Confined epitaxial lateral overgrowth (CELO): A novel concept for scalable integration of CMOS compatible InGaAs-on-insulator MOSFETs on large-area Si substrates. In Proceedings of the 2015 Symposium on VLSI Technology (VLSI Technology), Kyoto, Japan, 16–18 June 2015. [Google Scholar]

- Cutaia, D.; Moselund, K.E.; Schmid, H.; Borg, M.; Olziersky, A.; Riel, H. Complementary III-V heterojunction lateral NW Tunnel FET technology on Si. In Proceedings of the 2016 IEEE Symposium on VLSI Technology, Honolulu, HI, USA, 14–16 June 2016; p. 403. [Google Scholar]

- Convertino, C.; Zota, C.B.; Schmid, H.; Ionescu, A.M.; Moselund, K.E. III–V heterostructure tunnel field-effect transistor. J. Phys. Condens. Matter 2018, 30, 264005. [Google Scholar] [CrossRef] [PubMed] [Green Version]

- Gooth, J.; Schaller, V.; Wirths, S.; Schmid, H.; Borg, M.; Bologna, N.; Karg, S.; Riel, H. Ballistic one-dimensional transport in InAs nanowires monolithically integrated on silicon. Appl. Phys. Lett. 2017, 110, 083105. [Google Scholar] [CrossRef]

- Mauthe, S.; Mayer, B.; Sousa, M.; Villares, G.; Staudinger, P.; Schmid, H.; Moselund, K. Monolithically integrated InGaAs microdisk lasers on silicon using template-assisted selective epitaxy. SPIE 2018. [Google Scholar] [CrossRef]

- Borg, M.; Gignac, L.; Bruley, J.; Malmgren, A.; Sant, S.; Convertino, C.; Rossell, M.D.; Sousa, M.; Breslin, C.; Riel, H. Facet-selective group-III incorporation in InGaAs Template Assisted Selective Epitaxy. IOP Nanotechnol. 2018. [Google Scholar] [CrossRef] [PubMed]

© 2018 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).

Share and Cite

Convertino, C.; Zota, C.; Schmid, H.; Caimi, D.; Sousa, M.; Moselund, K.; Czornomaz, L. InGaAs FinFETs Directly Integrated on Silicon by Selective Growth in Oxide Cavities. Materials 2019, 12, 87. https://doi.org/10.3390/ma12010087

Convertino C, Zota C, Schmid H, Caimi D, Sousa M, Moselund K, Czornomaz L. InGaAs FinFETs Directly Integrated on Silicon by Selective Growth in Oxide Cavities. Materials. 2019; 12(1):87. https://doi.org/10.3390/ma12010087

Chicago/Turabian StyleConvertino, Clarissa, Cezar Zota, Heinz Schmid, Daniele Caimi, Marilyne Sousa, Kirsten Moselund, and Lukas Czornomaz. 2019. "InGaAs FinFETs Directly Integrated on Silicon by Selective Growth in Oxide Cavities" Materials 12, no. 1: 87. https://doi.org/10.3390/ma12010087