Series-Parallel Reconfiguration Technique with Voltage Equalization Capability for Electric Double-Layer Capacitor Modules

Abstract

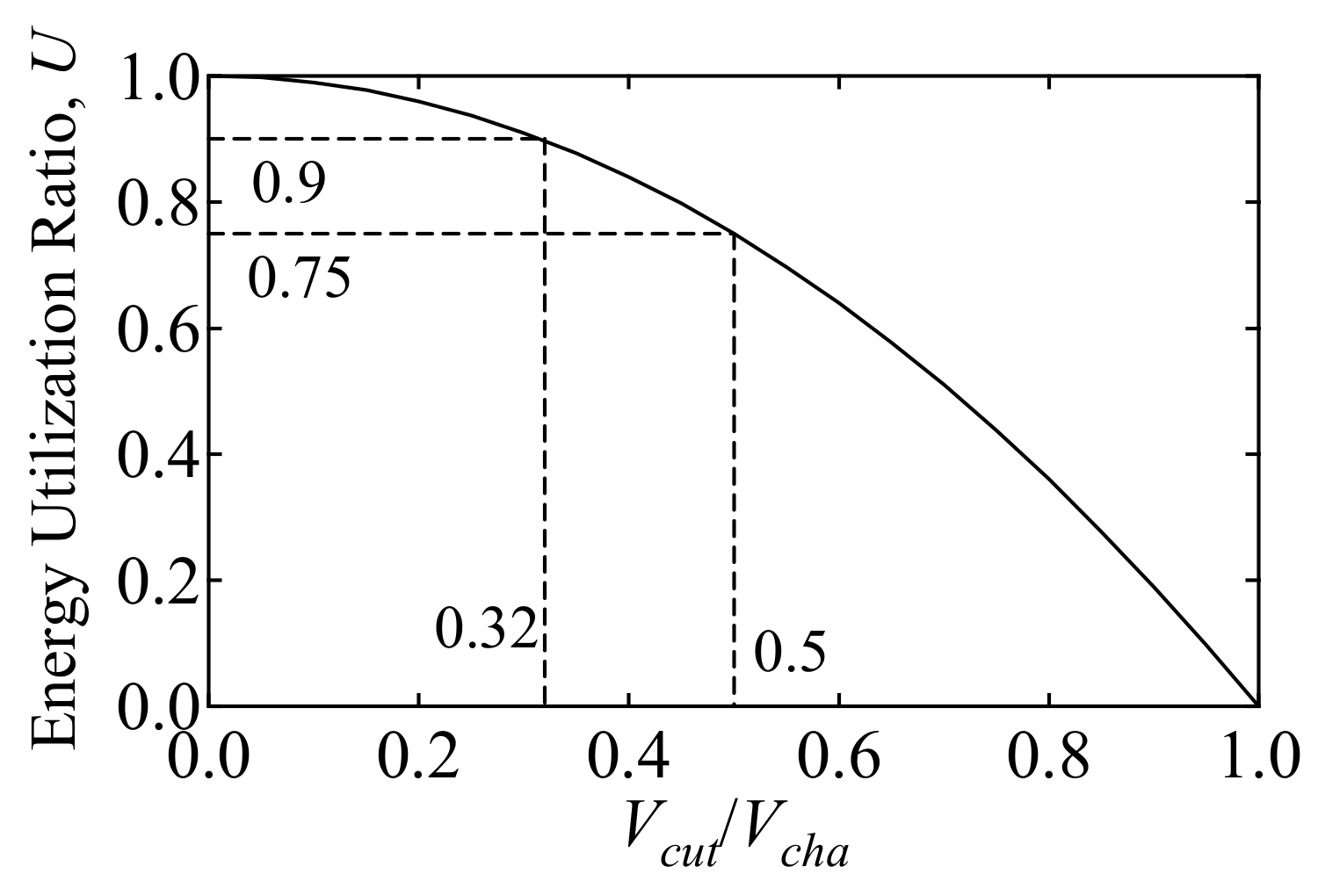

:1. Introduction

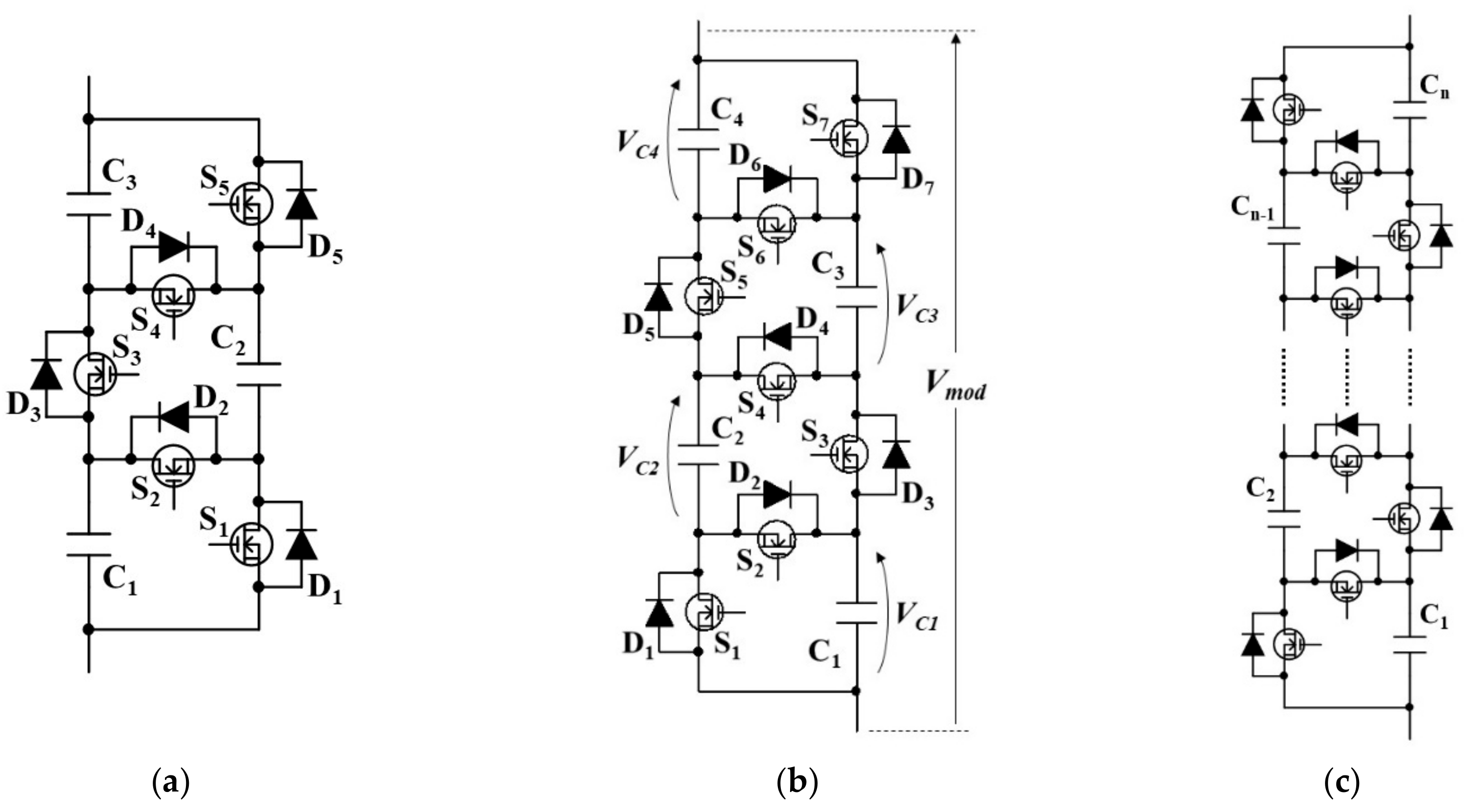

2. Series-Parallel Reconfiguration Circuit with Voltage Equalization Capability

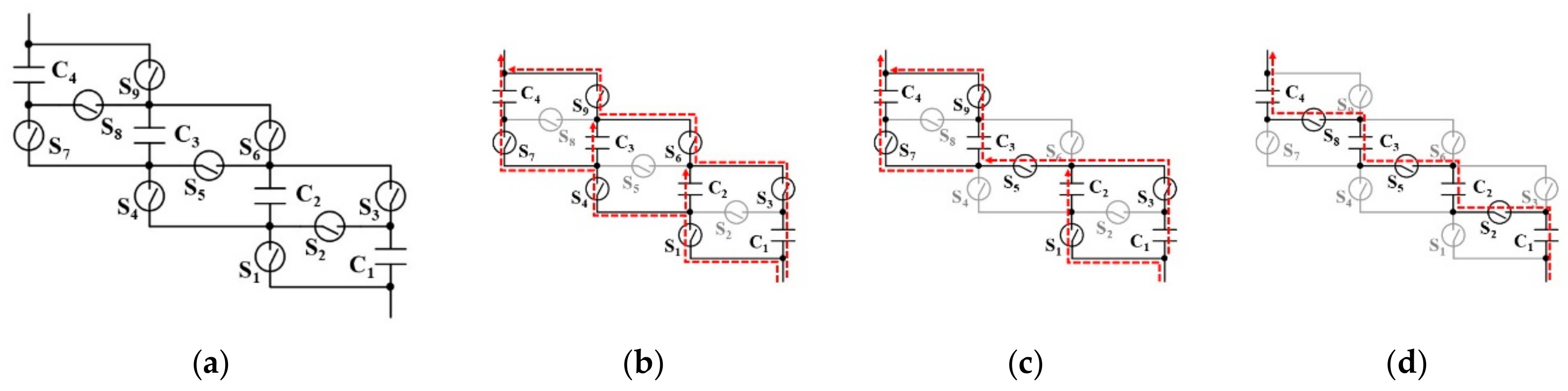

2.1. Circuit Description

2.2. Major Features

3. Operation Analysis

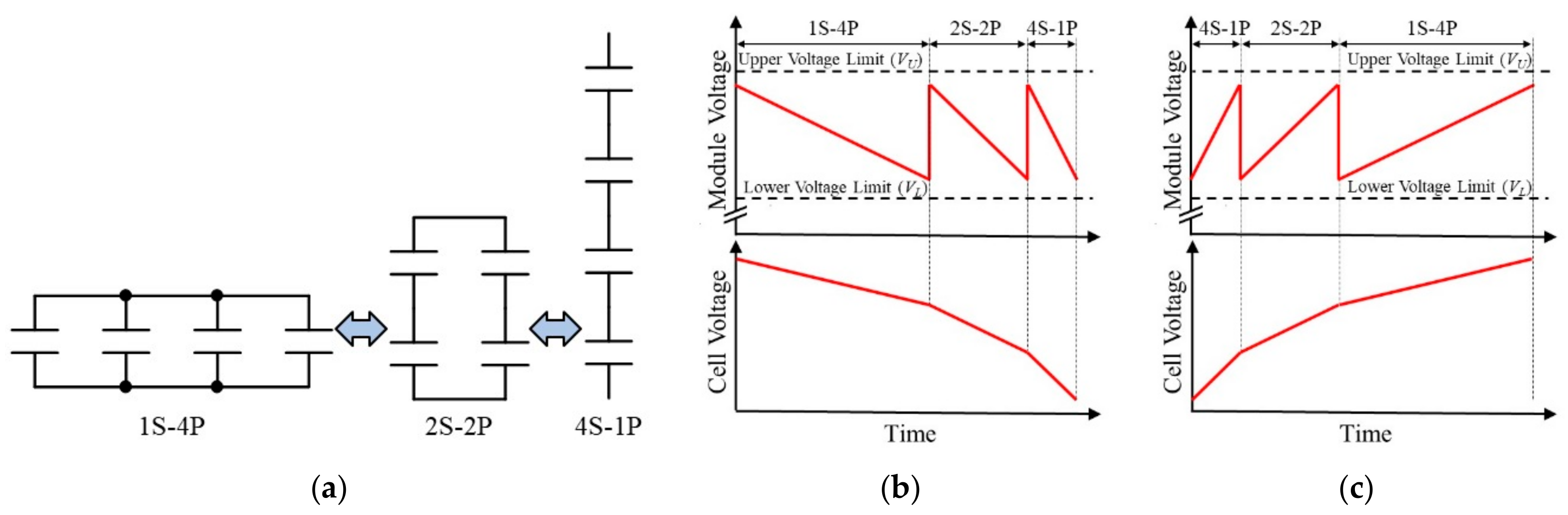

3.1. Voltage Profiles and Mode Transitions

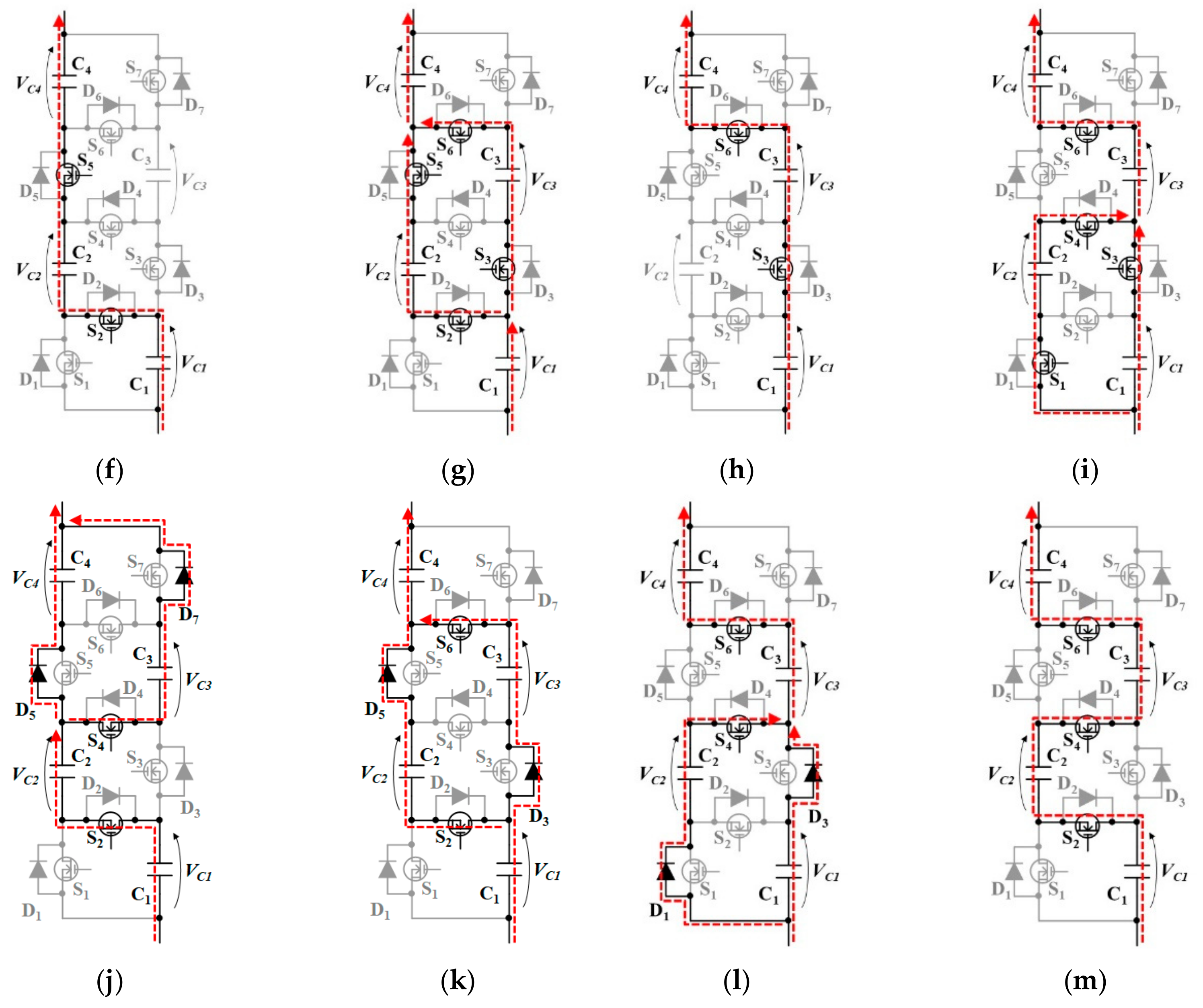

3.2. Operation in Discharging Mode

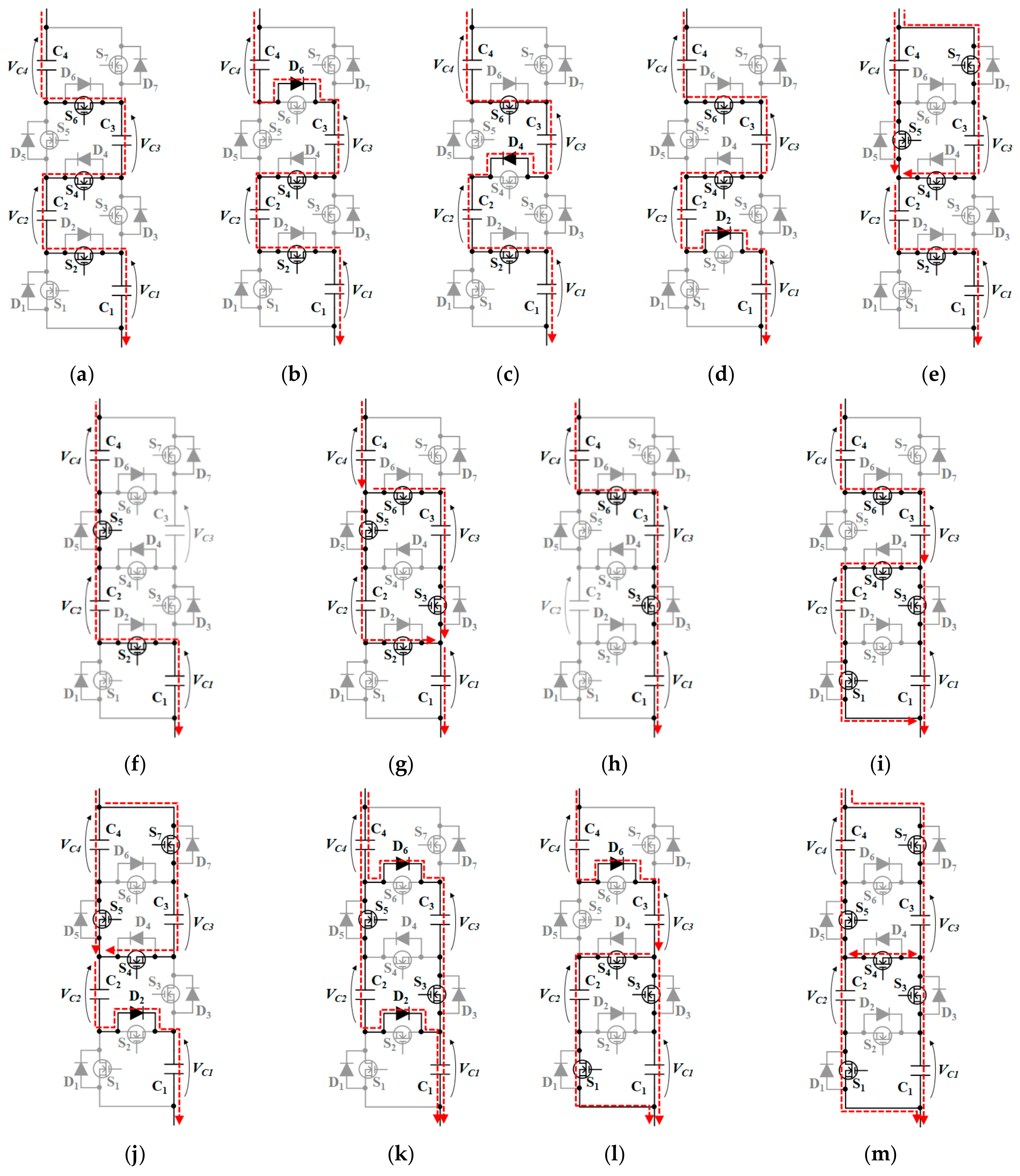

3.3. Operation in Charging Mode

3.4. Operation Conditions

3.5. Reconfiguration Algorithm

4. Design Example

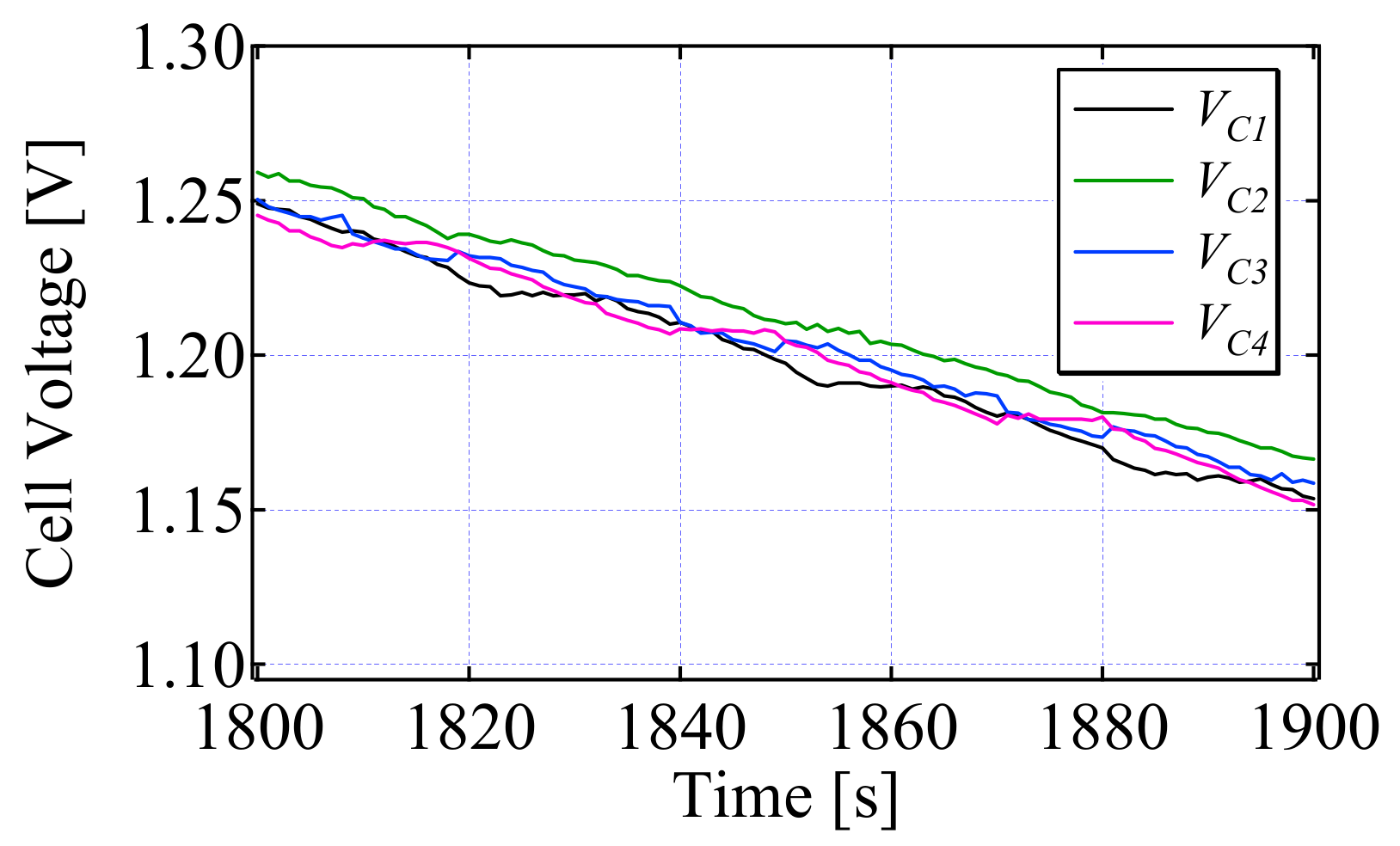

5. Experimental Results

6. Conclusions

Author Contributions

Funding

Conflicts of Interest

References

- Uno, M.; Tanaka, K. Accelerated charge-discharge cycling test and cycle life prediction model for supercapacitors in alternative battery applications. IEEE Trans. Ind. Electron. 2012, 59, 4704–4712. [Google Scholar] [CrossRef]

- Carbone, R. Energy Storage in the Emerging Era of Smart Grids; InTech: London, UK, 2011; pp. 21–40. ISBN 978-953-307-269-2. [Google Scholar]

- Gualous, H.; Alcicek, G.; Diab, Y.; Hammar, A.; Venet, P.; Adams, K.; Akiyama, M.; Marumo, C. Lithium ion capacitor characterization and modeling. In Proceedings of the ESSCAP’2008, Rome, Italy, 6–7 November 2008; pp. 1–4. [Google Scholar]

- Lambert, S.M.; Pickert, V.; Holden, J.; He, X.; Li, W. Comparison of supercapacitor and lithium-ion capacitor technologies for power electronics applications. In Proceedings of the Power Electronics Machines and Drives, Brighton, UK, 19–21 April 2010; pp. 1–5. [Google Scholar]

- Böckenfeld, N.; Kühnel, R.S.; Passerini, S.; Winter, M.; Balducci, A. Composite LiFePO4/AC high rate performance electrodes for Li-ion capacitors. J. Power Sources 2011, 196, 4136–4142. [Google Scholar] [CrossRef]

- Omar, N.; Daowd, M.; Hegazy, O.; Sakka, M.A.; Choosemans, T.; Bossche, P.V.D.; Mierlo, J.V. Assessment of lithium-ion capacitor for using in battery electric vehicle and hybrid electric vehicle applications. Electrochem. Acta 2012, 86, 305–315. [Google Scholar] [CrossRef]

- Omar, N.; Sakka, M.A.; Mierlo, J.V.; Bossche, P.V.; Gualous, H. Electric and thermal characterization of advanced hybrid Li-ion capacitor rechargeable energy storage system. In Proceedings of the Power Engineering Energy Electrical Drives (POWERENG), Istanbul, Turkey, 13–17 May 2013; pp. 1574–1580. [Google Scholar]

- Uno, M.; Kukita, A. Cycle life evaluation based on accelerated aging testing for lithium-ion capacitors as alternative to rechargeable batteries. IEEE Trans. Ind. Appl. 2016, 63, 1607–1617. [Google Scholar] [CrossRef]

- Zoran, S. Supercapacitor Design and Applications; InTech: London, UK, 2016; pp. 121–143. ISBN 978-953-51-2749-9. [Google Scholar]

- Uno, M.; Tanaka, K. Spacecraft electrical power system using lithium-ion capacitors. IEEE Trans. Aerosp. Electron. Syst. 2013, 49, 175–188. [Google Scholar] [CrossRef]

- Monthéard, R.; Bafleur1, M.; Boitier, V.; Dilhac, J.M.; Lafontan, X. Self-adaptive switched ultra-capacitors: A new concept for efficient energy harvesting and storage. In Proceedings of the Power MEMS 2012, Atlanta, GA, USA, 2–5 December 2012; pp. 283–286. [Google Scholar]

- Kim, Y.; Park, S.; Wang, Y.; Xie, Q.; Chang, N.; Poncino, M.; Pedram, M. Balanced reconfiguration of storage banks in a hybrid electrical energy storage system. In Proceedings of the IEEE/ACM International Conference Computer-Aided Design (ICCAD), San Jose, CA, USA, 7–10 November 2011; pp. 624–631. [Google Scholar]

- Monteiro, J.; Garrido, N. An experimental study of an efficient supercapacitor stacking scheme to power mobile phones. In Proceedings of the IEEE 33rd International Telecommunications Energy Conference (INTELEC), Amsterdam, The Netherlands, 9–13 October 2011; pp. 1–5. [Google Scholar]

- Mahboubi, F.E.; Bafleur, M.; Boitier, V.; Alvarez, A.; Colomer, J.; Miribel, P.; Dilhac, J.M. Self-powered adaptive switched architecture storage. In Proceedings of the Power MEMS 2016, Paris, France, 6–9 December 2016; pp. 1–4. [Google Scholar]

- Uno, M. Series-parallel reconfiguration technique for supercapacitor energy storage systems. In Proceedings of the the IEEE Region Ten Conference (TENCON), Singapore, 23–26 January 2009; pp. 1–5. [Google Scholar]

- Fang, X.; Kutkut, N.; Shen, J.; Batarseh, I. Analysis of generalized parallel-series ultracapacitor shift circuits for energy storage systems. Renew. Energy 2011, 36, 2599–2604. [Google Scholar] [CrossRef]

- Sugimoto, S.; Ogawa, S.; Katsukawa, H.; Mizutani, H.; Okamura, M. A study of series-parallel changeover circuit of a capacitor bank for an energy storage system utilizing electric double layer capacitors. Electr. Eng. Jpn. 2003, 145, 33–42. [Google Scholar] [CrossRef]

- Baughman, A.; Ferdowsi, M. Double-tiered switched-capacitor battery charge equalization technique. IEEE Trans. Ind. Appl. 2008, 55, 2277–2285. [Google Scholar] [CrossRef]

- Uno, M.; Tanaka, K. Influence of high-frequency charge-discharge cycling induced by cell voltage equalizers on the life performance of lithium-ion cells. IEEE Trans. Veh. Technol. 2011, 60, 1505–1515. [Google Scholar] [CrossRef]

- Kim, M.Y.; Kim, C.H.; Kim, J.H.; Moon, G.W. A chain structure of switched capacitor for improved cell balancing speed of lithium-ion batteries. IEEE Trans. Ind. Electron. 2014, 61, 3989–3999. [Google Scholar] [CrossRef]

- Uno, M.; Akio, K. PWM converter integrating switched capacitor converter and series-resonant voltage multiplier as equalizers for photovoltaic modules and series-connected energy storage cells for exploration rovers. IEEE Trans. Power Electron. 2017, 32, 8500–8513. [Google Scholar] [CrossRef]

| Topology | Balance-Shift Circuit | Unbalance-Shift Circuit | Proposed |

|---|---|---|---|

| Switch Count | 3(n − 1) | n + 1 | 2n − 1 |

| Applicable Cell Number | Even Number | Even Number | Any Number Cells |

| Voltage Balance | Balanced | Unbalanced | Balanced |

© 2019 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).

Share and Cite

Uno, M.; Iwasaki, K.; Hasegawa, K. Series-Parallel Reconfiguration Technique with Voltage Equalization Capability for Electric Double-Layer Capacitor Modules. Energies 2019, 12, 2741. https://doi.org/10.3390/en12142741

Uno M, Iwasaki K, Hasegawa K. Series-Parallel Reconfiguration Technique with Voltage Equalization Capability for Electric Double-Layer Capacitor Modules. Energies. 2019; 12(14):2741. https://doi.org/10.3390/en12142741

Chicago/Turabian StyleUno, Masatoshi, Koyo Iwasaki, and Koki Hasegawa. 2019. "Series-Parallel Reconfiguration Technique with Voltage Equalization Capability for Electric Double-Layer Capacitor Modules" Energies 12, no. 14: 2741. https://doi.org/10.3390/en12142741