Research on the Filters for Dual-Inverter Fed Open-End Winding Transformer Topology in Photovoltaic Grid-Tied Applications

Abstract

:1. Introduction

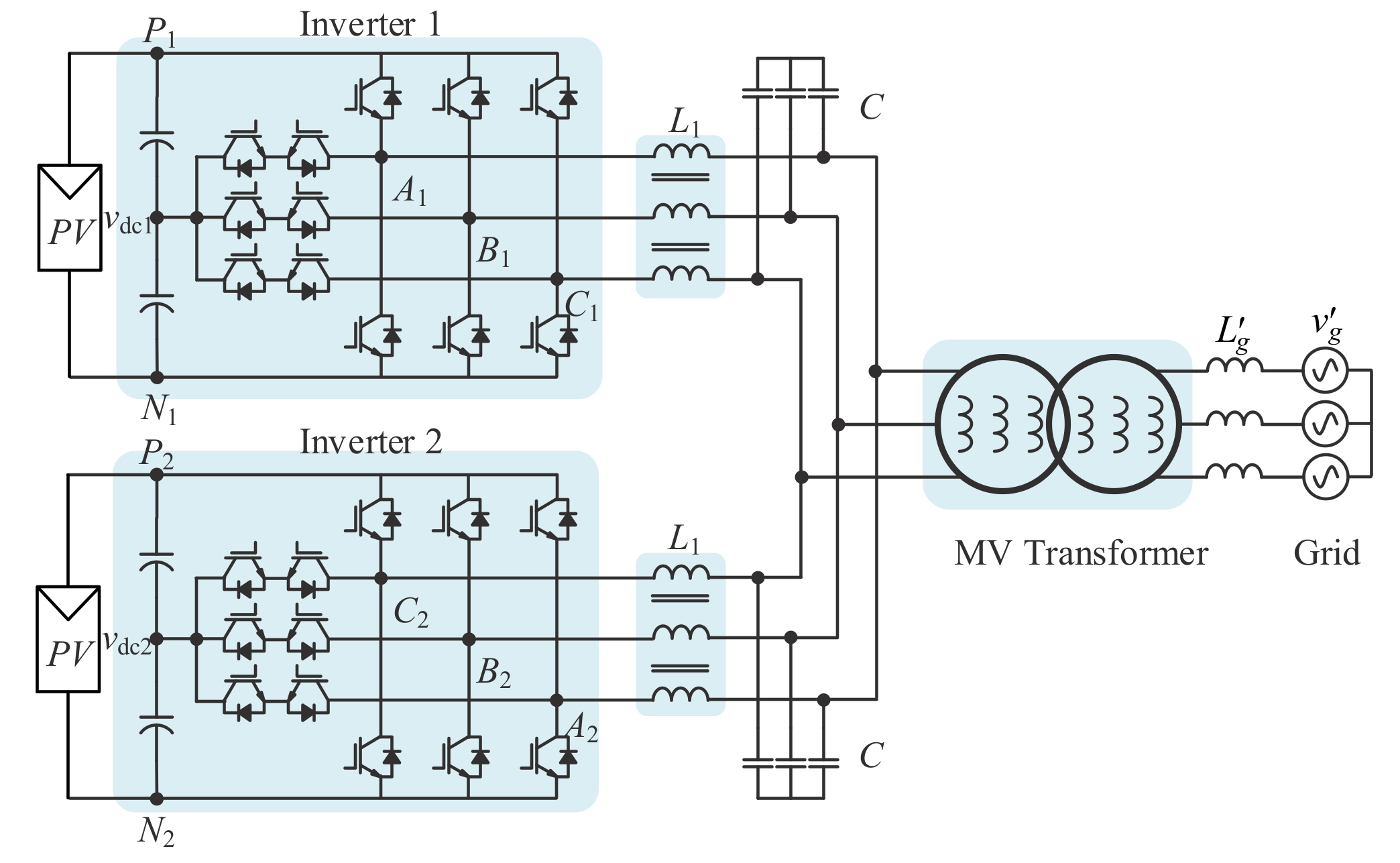

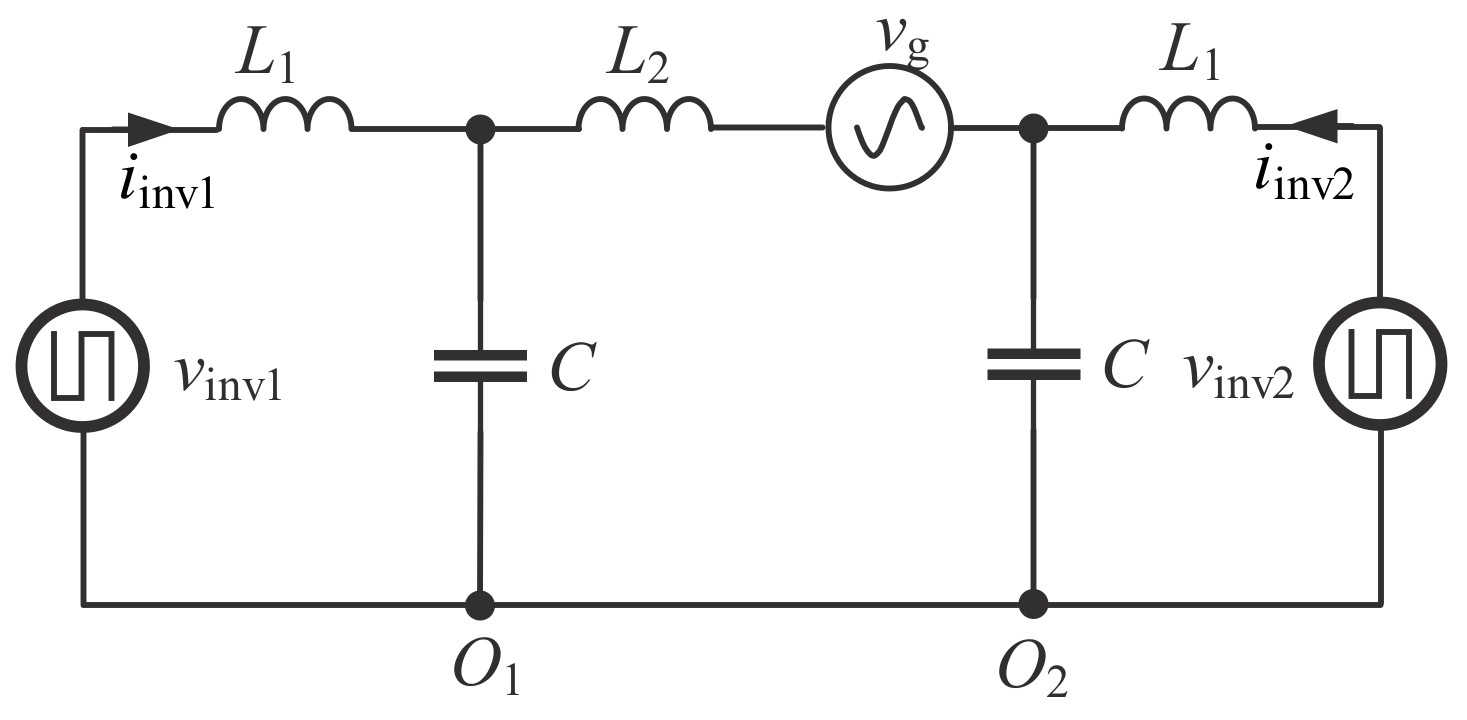

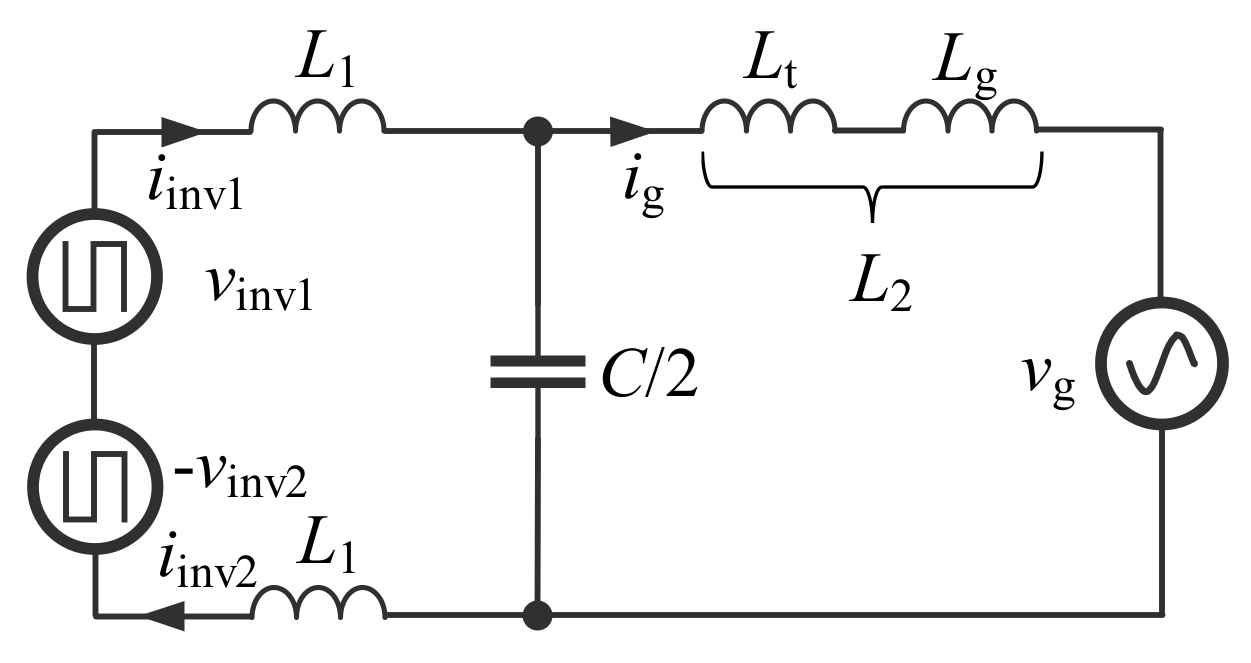

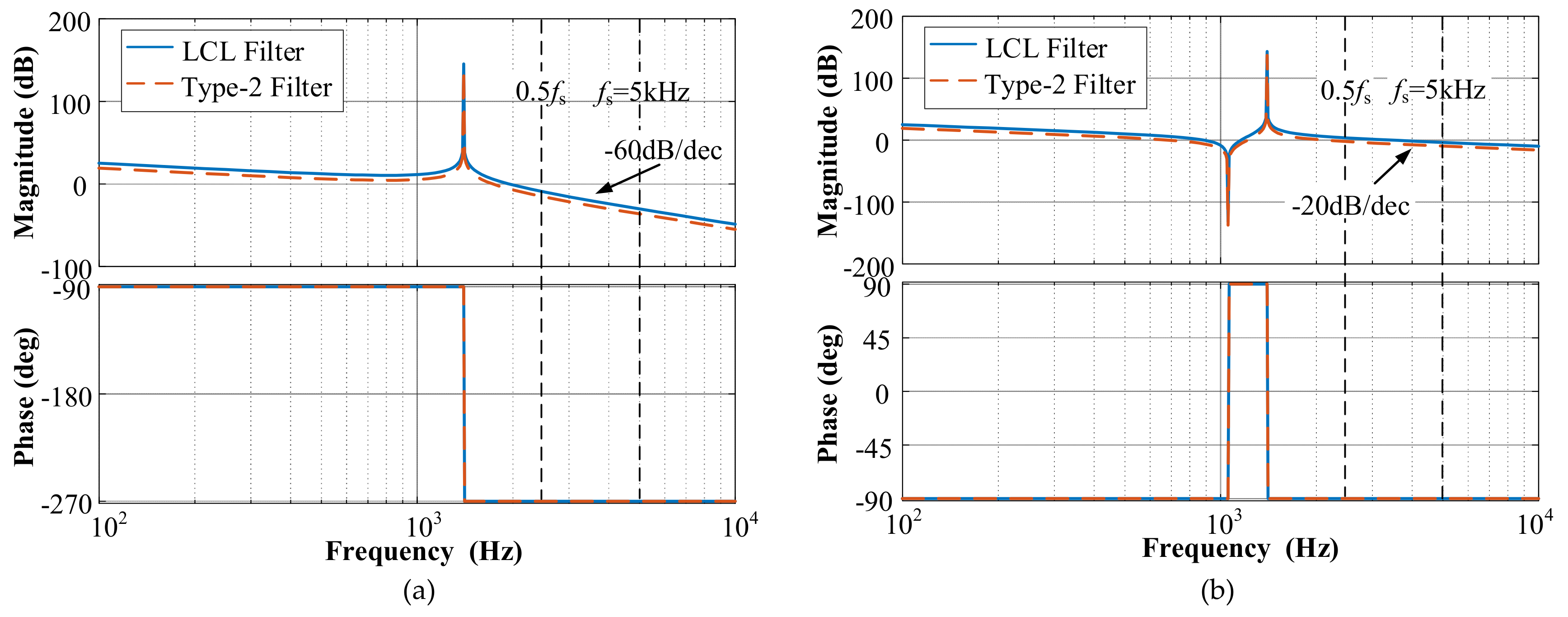

2. LCL Filter for the Conventional Multi-Parallel Inverters

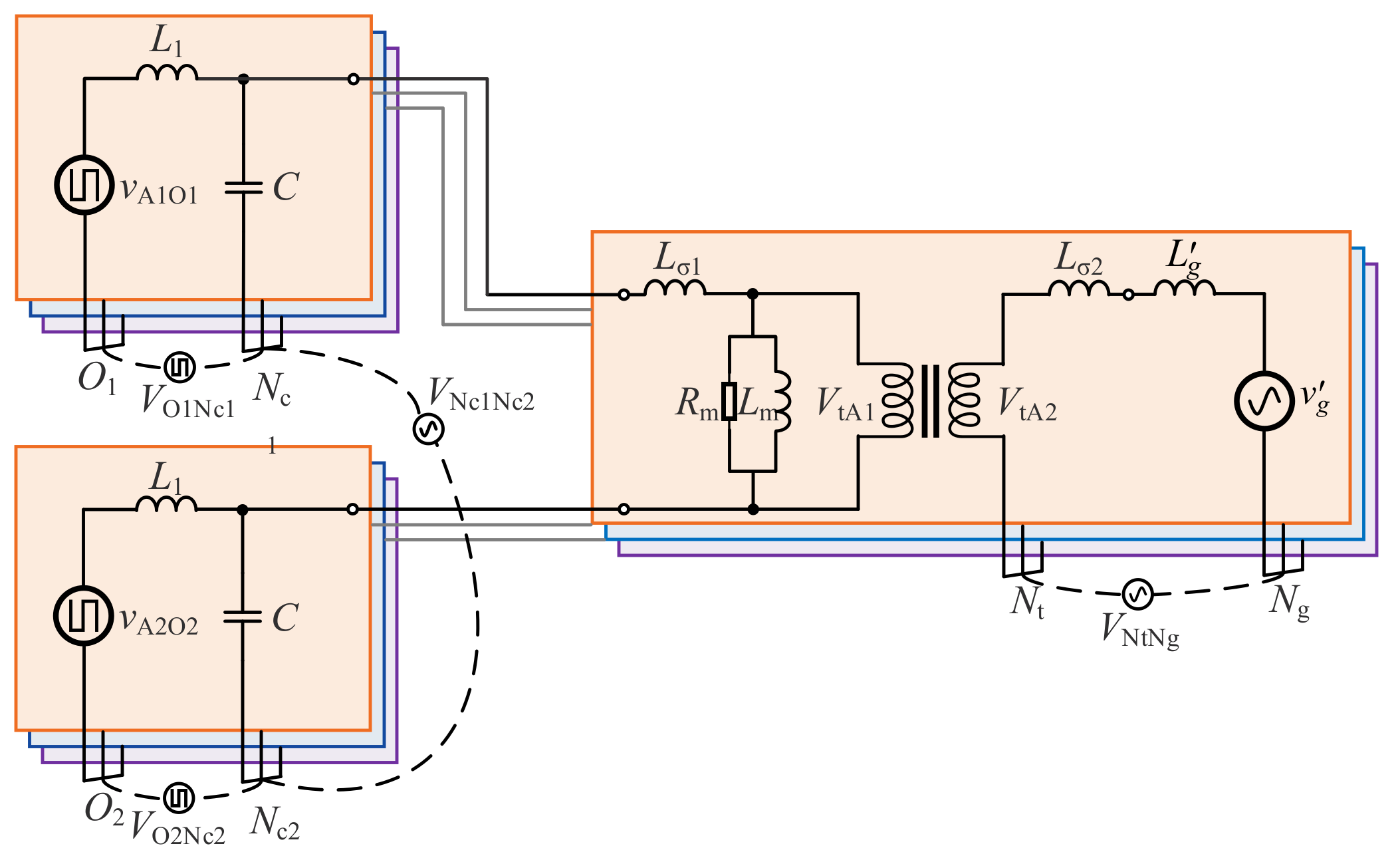

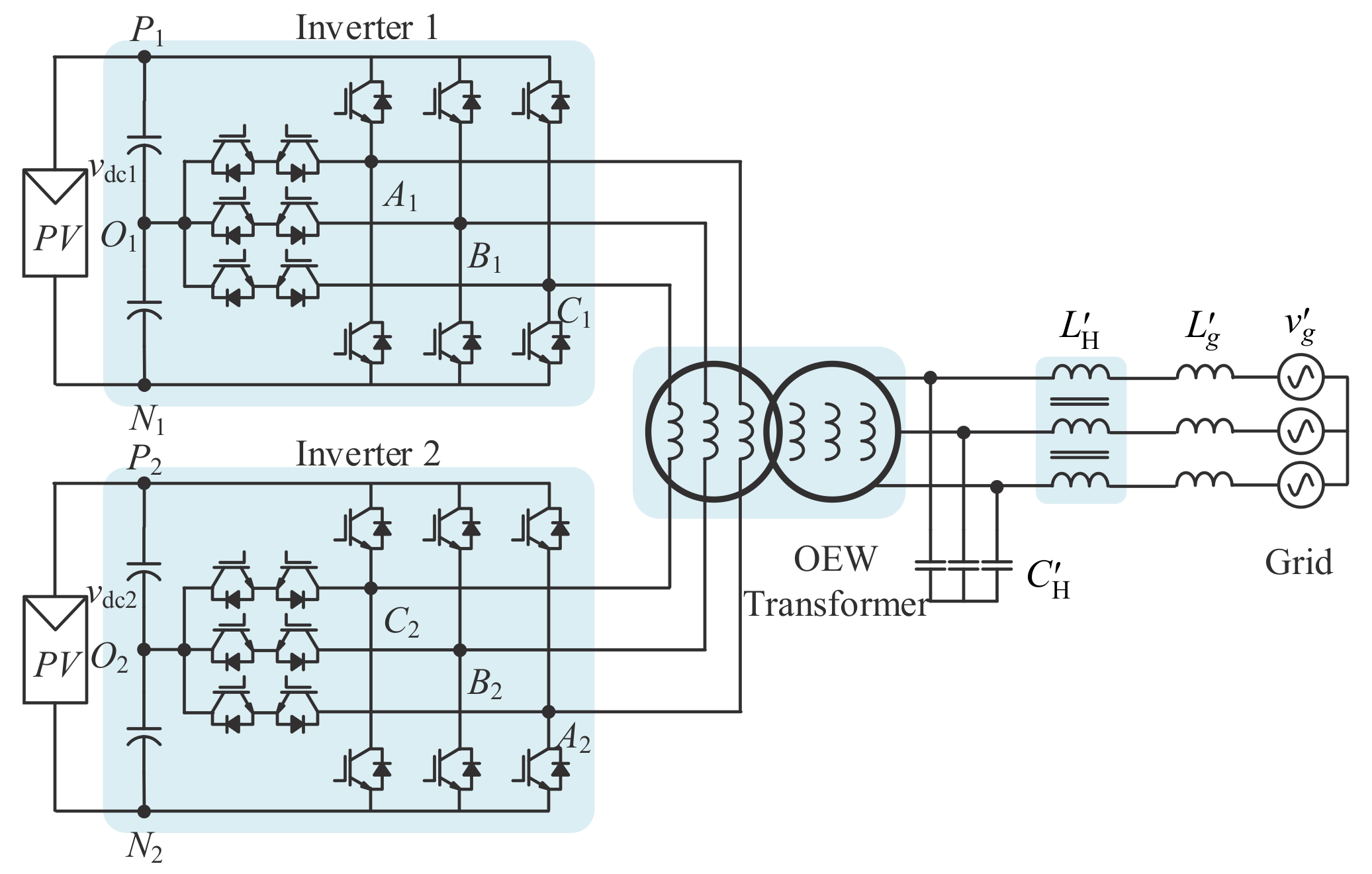

3. Existing and Proposed Filters for the DI-OEWT Topology

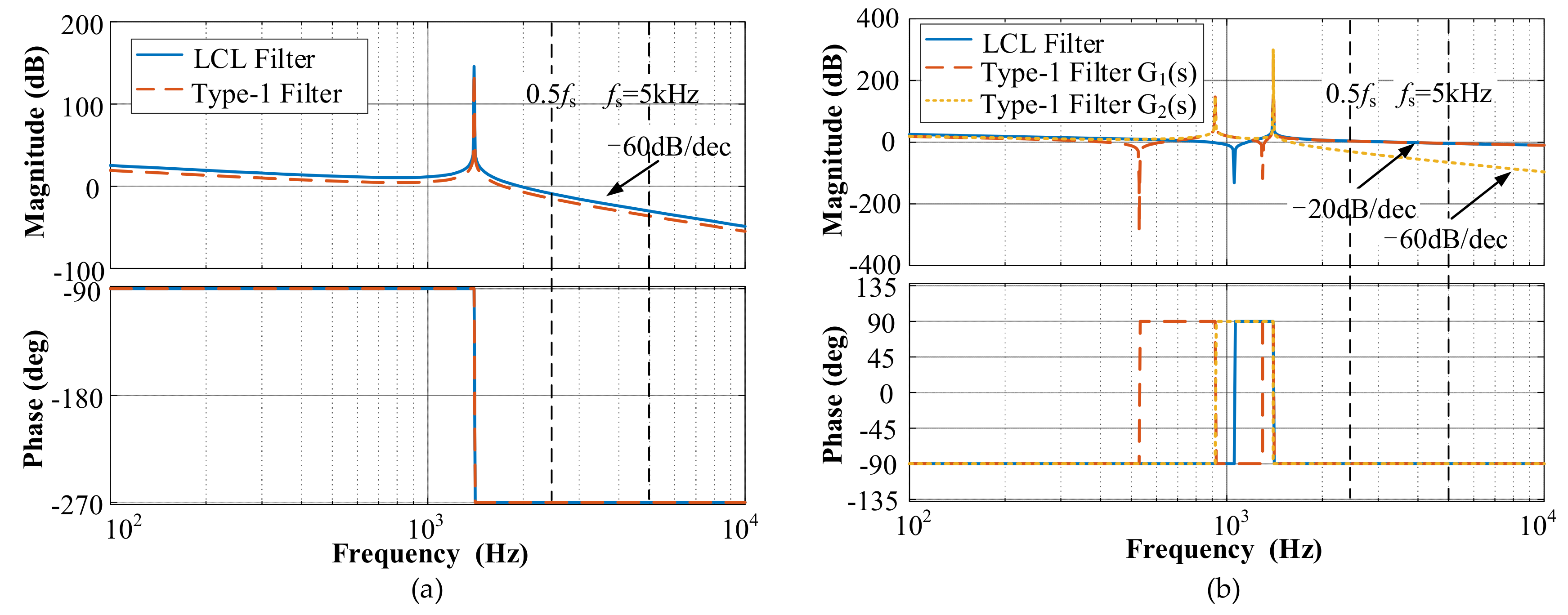

3.1. Type-1 Filter for the DI-OEWT Topology

3.2. Type-2 Filter for the DI-OEWT Topology

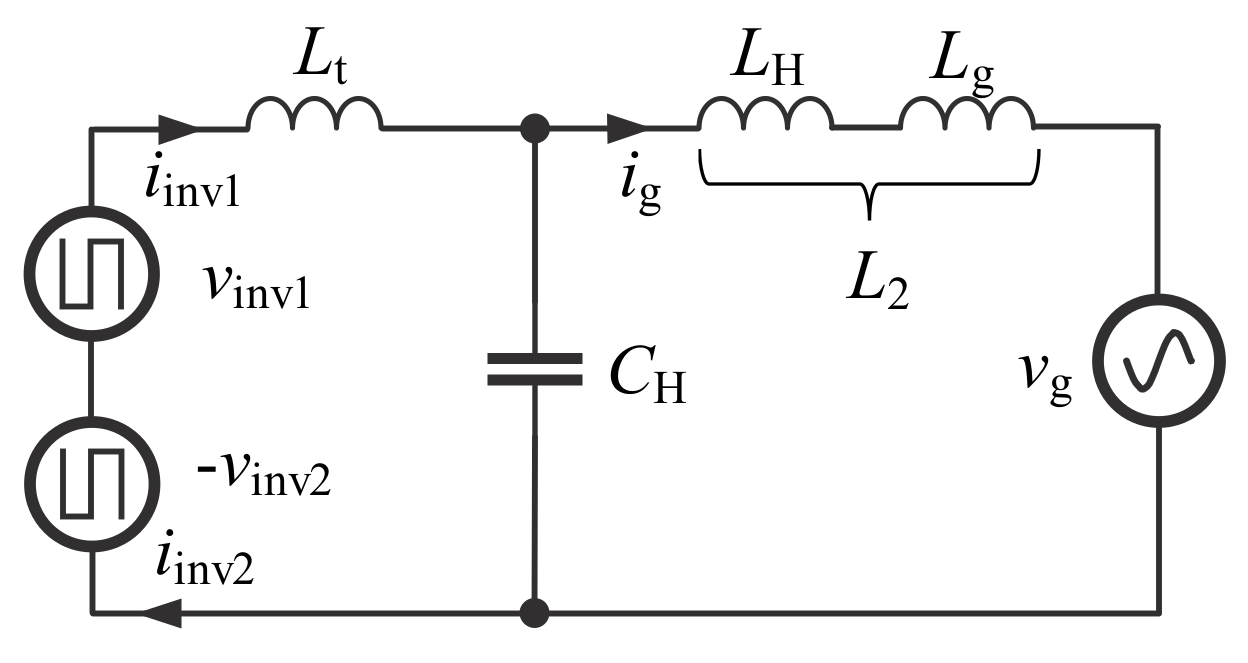

3.3. The Proposed Type-3 Filter for the DI-OEWT Topology

4. Parameter Design and Evaluations of the Filters

4.1. Parameter Design of the Filters

4.2. Fault-Tolerant Configuration for DI-OEWT Topology

4.3. Summary and Discussion

5. Experiment Results

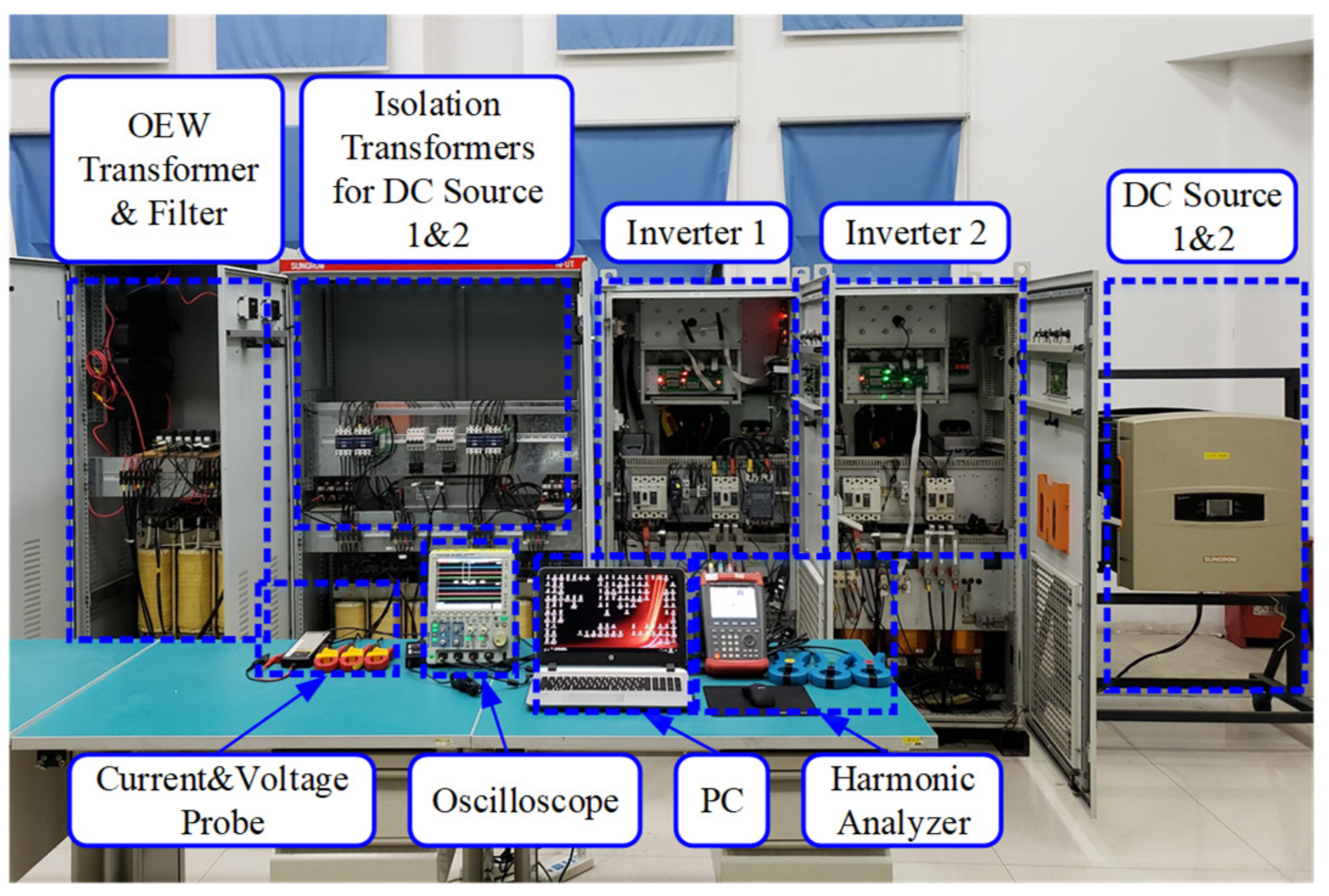

5.1. Experiment Setup Description

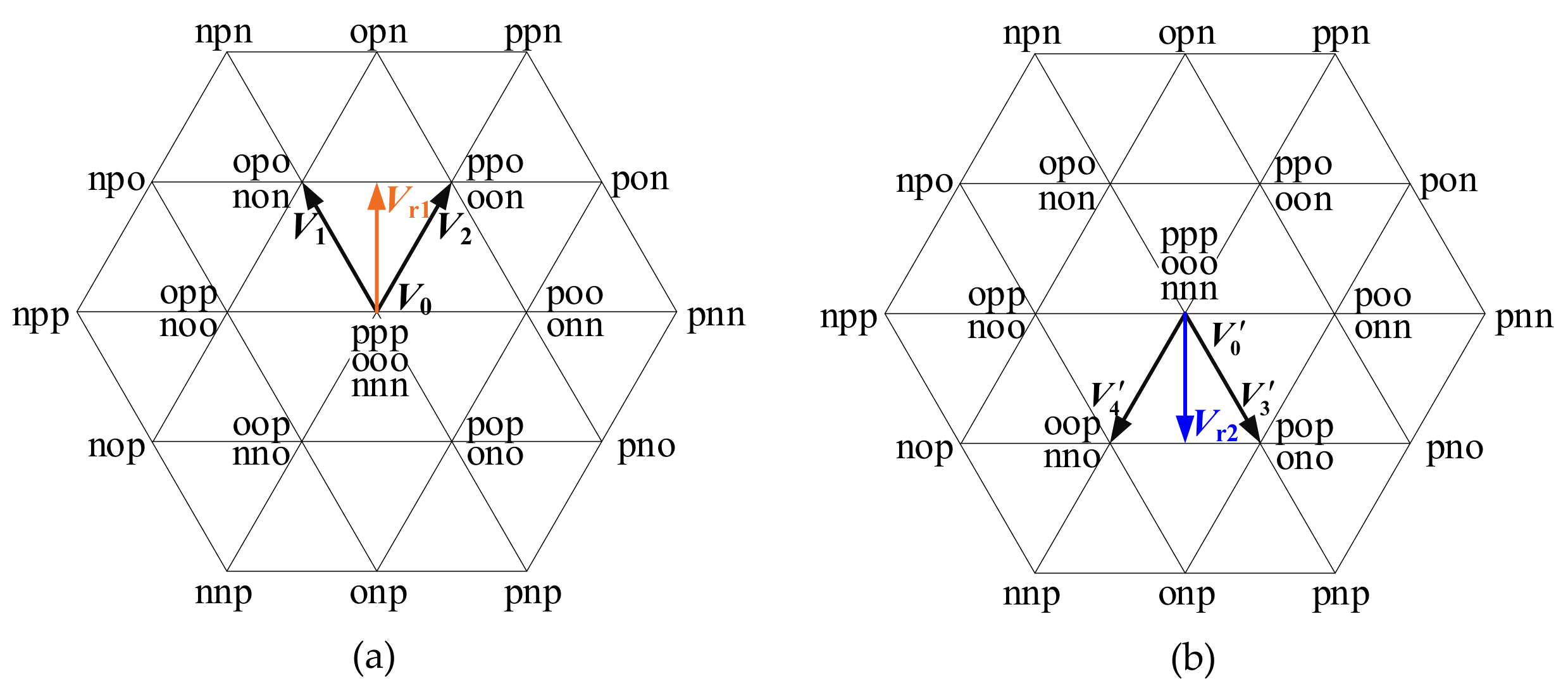

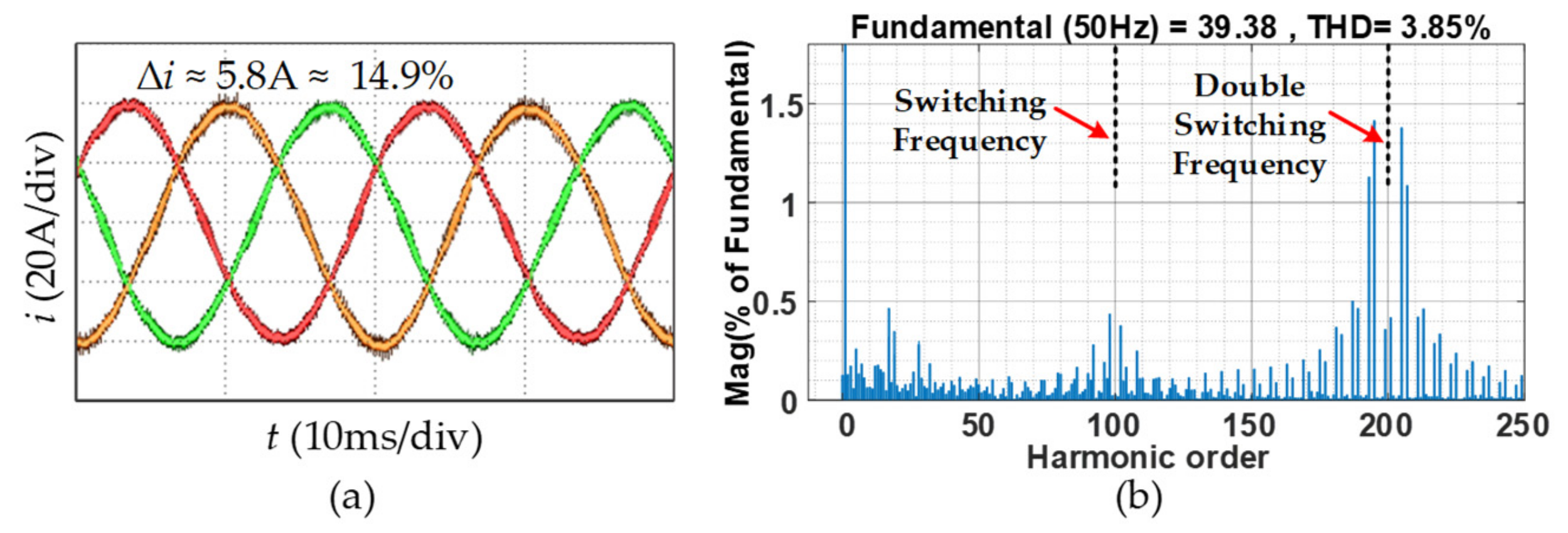

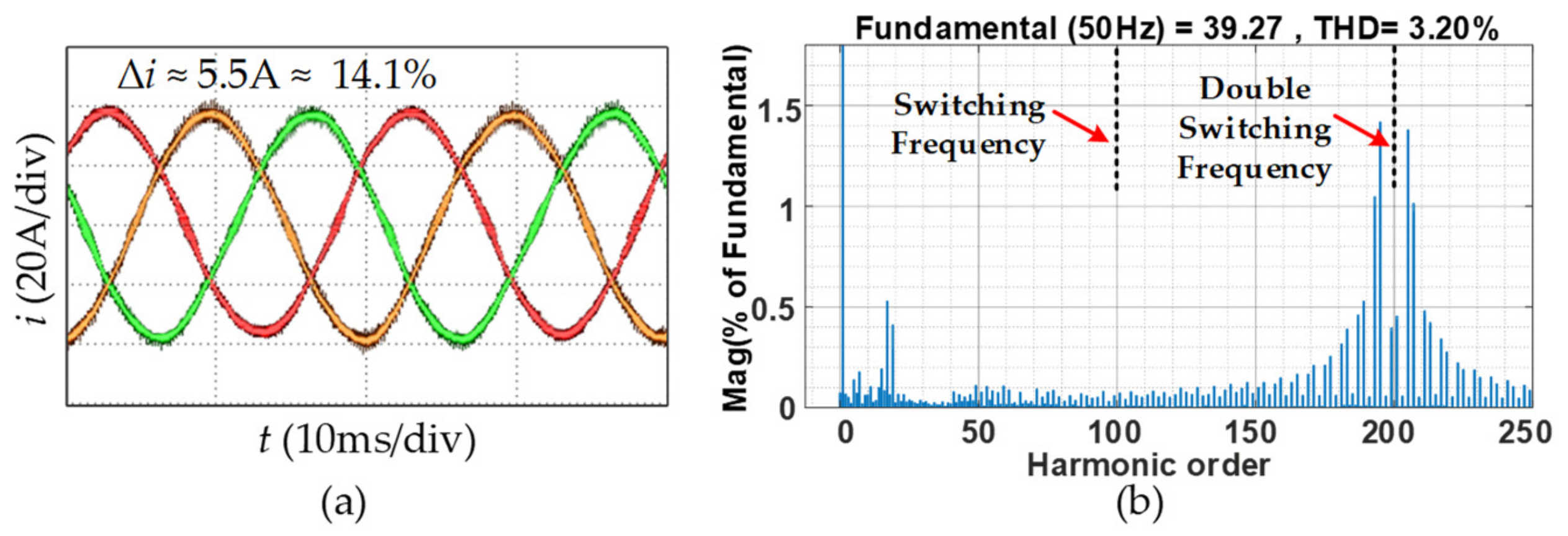

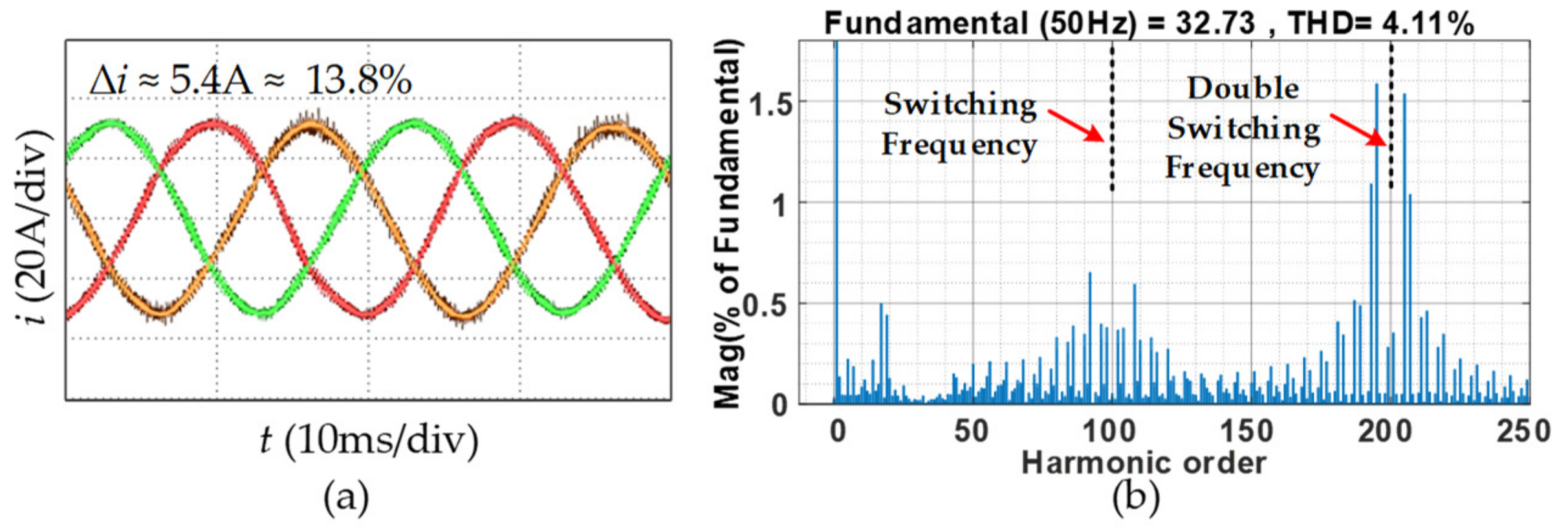

5.2. Inverter-Side Current Analysis

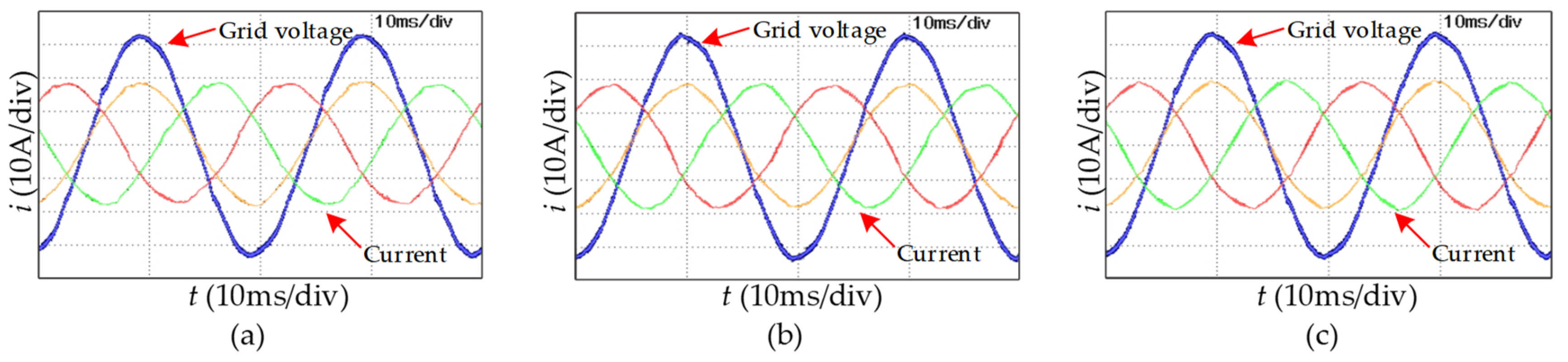

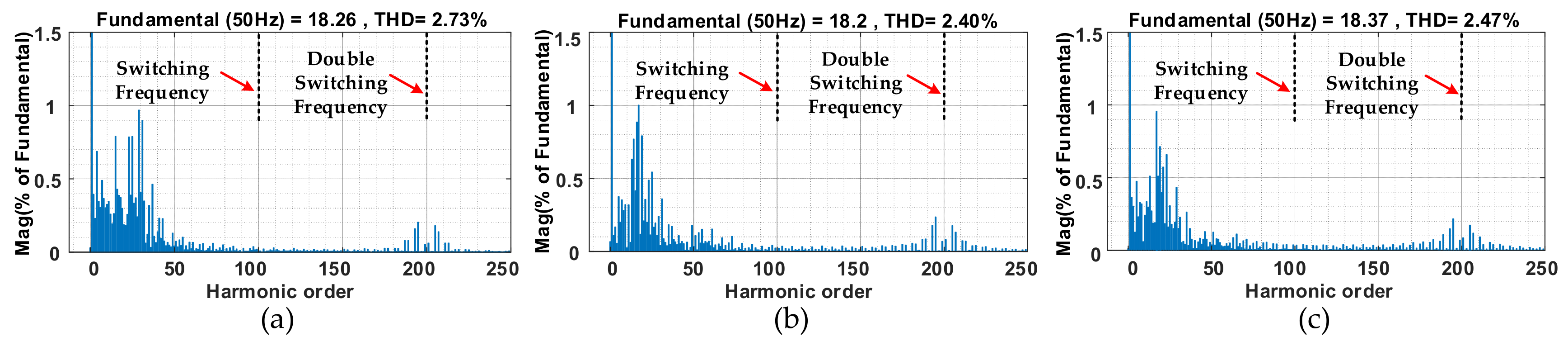

5.3. Grid Current Analysis

6. Conclusions

Author Contributions

Funding

Acknowledgments

Conflicts of Interest

Nomenclature

| List of Abbreviations | |

| LCL | inductor-capacitor-inductor |

| MV | medium-voltage |

| DI-OEWT | dual-inverter fed open-end winding transformer |

| NPC | neutral point clamp |

| VSI | voltage source inverter |

| MPPT | maximum power point tracking |

| SCR | short-circuit ratio |

| OEW | open-end winding |

| CM | common-mode |

| KVL | Kirchhoff’s voltage law |

| FFT | fast Fourier transformation |

| p.u. | per unit |

| List of Symbols | |

| vinv1 | inverter 1 output phase voltage |

| vinv2 | inverter 2 output phase voltage |

| iinv1 | inverter 1 output phase current |

| iinv2 | inverter 2 output phase current |

| vg | grid voltage |

| ig | grid current |

| L1 | inverter-side inductor |

| Lt | transformer leakage inductance |

| Lg | grid inductance |

| L2 | combined inductance of Lt and Lg |

| C | filter capacitor |

| shunt capacitor of Type-3 filter | |

| grid-side inductor of Type-3 filter | |

| CH | shunt capacitor of Type-3 filter referred to the low-voltage side |

| LH | grid-side inductor of Type-3 filter referred to the low-voltage side |

| Vk | impedance voltage |

| Prated | system rated power |

| f0 | fundamental frequency |

| VX1O1 | pole voltage of phase X1 of inverter 1, X = A,B,C |

| VX2O2 | pole voltage of phase X2 of inverter 2 |

| VO1Nc1 | CM voltage of inverter 1 |

| VO2Nc2 | CM voltage of inverter 2 |

| VNc1Nc2 | voltage across the two capacitor common points Nc1, Nc2 |

| VNtNg | voltage across Nt and Ng |

| VCX1 | voltage on filter capacitor of phase X1 |

| VCX2 | voltage on filter capacitor of phase X2 |

| VLσ1X | phase X voltage on the leakage inductance at transformer low voltage side (Lσ1) |

| VLσ2X | phase X voltage on the leakage inductance at transformer high voltage side (Lσ2) |

| VLgX | phase X voltage on the grid inductance |

| VtX1 | voltage of the low voltage side of the MV transformer |

| VtX2 | voltage of the high voltage side of the MV transformer |

| phase X voltage of the MV grid | |

| vdc1 | DC voltage of inverter 1 |

| vdc2 | DC voltage of inverter 2 |

| ωres | filter resonant frequency |

| Ts | switching period |

| fs | switching frequency |

| mf | modulation frequency index |

| h | dominant harmonic order |

References

- Zhao, Z.; Lei, Y.; He, F.; Lu, Z. Overview of large-scale grid-connected photovoltaic power plants. Autom. Electr. Power Syst. 2011, 12, 101–107. [Google Scholar]

- Serban, E.; Ordonez, M.; Pondiche, C. DC-bus voltage range extension in 1500 V photovoltaic inverters. IEEE J. Emerg. Sel. Top. Power Electron. 2015, 3, 901–917. [Google Scholar] [CrossRef]

- Sungrow. SG1250UD Inverter Product Datasheet. Available online: http://en.sungrowpower.com/product_view?id=146.html (accessed on 18 June 2019).

- Takahashi, I.; Ohmori, Y. High-performance direct torque control of an induction motor. IEEE Trans. Ind. Appl. 1989, 25, 257–264. [Google Scholar] [CrossRef]

- Anand, S.; Fernandes, B.G.; Chatterjee, K. DC voltage controller for asymmetric-twin-converter-topology-based high-power STATCOM. IEEE Trans. Ind. Electron. 2013, 60, 11–19. [Google Scholar] [CrossRef]

- De Almeida Carlos, G.A.; Jacobina, C.B.; dos Santos, E.C.; Fabrício, E.L.L.; dos Santos Rocha, N. Shunt active power filter with open-end winding transformer and series-connected converters. IEEE Trans. Ind. Appl. 2015, 51, 3273–3283. [Google Scholar] [CrossRef]

- De Almeida Carlos, G.A.; dos Santos, E.C.; Jacobina, C.B.; Mello, J.P.R.A. Dynamic voltage restorer based on three-phase inverters cascaded through an open-end winding transformer. IEEE Trans. Power Electron. 2016, 31, 188–199. [Google Scholar] [CrossRef]

- Grandi, G.; Rossi, C.; Ostojic, D.; Casadei, D. A new multilevel conversion structure for grid-connected PV applications. IEEE Trans. Ind. Electron. 2009, 56, 4416–4426. [Google Scholar] [CrossRef]

- Corzine, K.A.; Wielebski, M.W.; Peng, F.Z.; Wang, J. Control of cascaded multilevel inverters. IEEE Trans. Power Electron. 2004, 19, 732–738. [Google Scholar] [CrossRef]

- Edpuganti, A.; Rathore, A.K. New optimal pulsewidth modulation for single dc-link dual-inverter fed open-end stator winding induction motor drive. IEEE Trans. Power Electron. 2015, 30, 4386–4393. [Google Scholar] [CrossRef]

- Kubasiak, N.; Mercorelli, P.; Liu, S. Model predictive control of transistor pulse converter for feeding electromagnetic valve actuator with energy storage. In Proceedings of the 44th IEEE Conference on Decision and Control, Seville, Spain, 15 December 2005. [Google Scholar]

- Mercorelli, P. A multilevel inverter bridge control structure with energy storage using model predictive control for flat systems. J. Eng. 2013, 2013, 750190. [Google Scholar] [CrossRef]

- Mercorelli, P.; Kubasiak, N.; Liu, S. Multilevel bridge governor by using model predictive control in wavelet packets for tracking trajectories. In Proceedings of the IEEE International Conference on Robotics and Automation (ICRA), New Orleans, LA, USA, 26 April–1 May 2004; pp. 4079–4084. [Google Scholar]

- Kiadehi, A.D.; Drissi, K.E.K.; Pasquier, C. Adapted NSPWM for single DC-link dual-inverter fed open-end motor with negligible low-order harmonics and efficiency enhancement. IEEE Trans. Power Electron. 2016, 31, 8271–8281. [Google Scholar]

- Srinivas, S.; Ramachandra Sekhar, K. Theoretical and experimental analysis for current in a dual-inverter-fed open-end winding induction motor drive with reduced switching PWM. IEEE Trans. Ind. Electron. 2013, 60, 4318–4328. [Google Scholar] [CrossRef]

- Somasekhar, V.T.; Srinivas, S.; Kumar, K.K. Effect of zero-vector placement in a dual-inverter fed open-end winding induction motor drive with alternate sub-hexagonal center PWM switching scheme. IEEE Trans. Power. Electron. 2008, 23, 1584–1591. [Google Scholar] [CrossRef]

- Wu, D.; Wu, X.; Su, L.; Yuan, X.; Xu, J. A dual three-level inverter based open-end winding induction motor drive with averaged zero-sequence voltage elimination and neutral-point voltage balance. IEEE Trans. Ind. Electron. 2016, 63, 4783–4795. [Google Scholar] [CrossRef]

- Zhao, W.; Zhao, P.; Xu, D.; Chen, Z.; Zhu, J. Hybrid modulation fault-tolerant control of open-end windings linear vernier permanent-magnet motor with floating capacitor inverter. IEEE Trans. Power Electron. 2018, 34, 2563–2572. [Google Scholar] [CrossRef]

- Yu, Z.; Kong, W.; Jiang, D.; Qu, R.; Li, D.; Jia, S.; Sun, J.; Gan, C. Fault-tolerant control strategy of the open-winding inverter for DC-biased vernier reluctance machines. IEEE Trans. Power Electron. 2019, 34, 1658–1671. [Google Scholar] [CrossRef]

- Zhao, W.; Wu, B.; Chen, Q.; Zhu, J. Fault-tolerant direct thrust force control for a dual inverter fed open-end winding linear vernier permanent-magnet motor using improved SVPWM. IEEE Trans. Ind. Electron. 2018, 65, 7458–7467. [Google Scholar] [CrossRef]

- Gohil, G.; Bede, L.; Teodorescu, R.; Kerekes, T.; Blaabjerg, F. Dual-converter-fed open-end transformer topology with parallel converters and integrated magnetics. IEEE Trans. Ind. Electron. 2016, 63, 4929–4941. [Google Scholar] [CrossRef]

- Gohil, G.; Bede, L.; Teodorescu, R.; Kerekes, T.; Blaabjerg, F. Optimized integrated harmonic filter inductor for dual-converter-fed open-end transformer topology. IEEE Trans. Power Electron. 2017, 32, 1818–1831. [Google Scholar] [CrossRef]

- Kumar, N.; Saha, T.; Dey, J. Sliding-mode control of PWM dual inverter-based grid-connected PV system: Modeling and performance analysis. IEEE J. Emerg. Sel. Top. Power Electron. 2016, 4, 435–444. [Google Scholar] [CrossRef]

- Kumar, N.; Saha, T.K.; Dey, J. Control, implementation, and analysis of a dual two-level photovoltaic inverter based on modified proportional resonant controller. IET Renew. Power Gener. 2018, 12, 598–604. [Google Scholar] [CrossRef]

- Pires, V.F.; Foito, D.; Sousa, D.M. Conversion structure based on a dual T-type three-level inverter for grid connected photovoltaic applications. In Proceedings of the 2014 IEEE 5th International Symposium on Power Electronics for Distributed Generation Systems (PEDG), Galway, Ireland, 24–27 June 2014; pp. 1–7. [Google Scholar]

- Oleschuk, V.; Ermuratskii, V. Dual-inverter-based photovoltaic system with discontinuous synchronized PWM. In Proceedings of the 2014 IEEE International Conference on Intelligent Energy and Power Systems (IEPS), Kiev, Ukraine, 2–6 June 2014; pp. 86–89. [Google Scholar]

- Pires, V.F.; Martins, J.F.; Hao, C. Dual-inverter for grid connected photovoltaic system: modeling and sliding mode control. Sol. Energy 2012, 86, 2106–2115. [Google Scholar] [CrossRef]

- Anand, S.; Fernandes, B.G. Multilevel open-ended transformer based grid feeding inverter for solar photovoltaic application. In Proceedings of the IECON 2012-38th Annual Conference on IEEE Industrial Electronics Society, Montreal, QC, Canada, 25–28 October 2012; pp. 5738–5743. [Google Scholar]

- Beres, R.N.; Wang, X.; Blaabjerg, F.; Liserre, M.; Bak, C.L. Optimal design of high-order passive-damped filters for grid-connected applications. IEEE Trans. Power Electron. 2016, 31, 2083–2098. [Google Scholar] [CrossRef]

- Yin, J. Research on the Control Strategies of Dual Converter Based on Open-End Winding Topology. Ph.D. Dissertation, Beijing Jiaotong University, Beijing, China, April 2015; pp. 92–93. [Google Scholar]

- Siemens, A.G. GEAFOL Cast-Resin Transformer 100 to 16000 kVA. In Cast-Resin Transformers Catalog TV1; Siemens AG: München, Germany, 2007. [Google Scholar]

- Jiao, Y.; Lee, F.C. LCL filter design and inductor current ripple analysis for a three-level NPC grid interface converter. IEEE Trans. Power Electron. 2015, 30, 4659–4668. [Google Scholar] [CrossRef]

- Juntunen, R.; Korhonen, J.; Musikka, T.; Smirnova, L.; Pyrhönen, O.; Silventoinen, P. Comparative analysis of LCL-filter designs for paralleled inverters. In Proceedings of the 2015 IEEE Energy Conversion Congress and Exposition (ECCE), Montreal, QC, Canada, 20–24 September 2015; pp. 2664–2672. [Google Scholar]

- National Energy Administration. Technical Specification of PV Grid-Connected Inverter. NB/T 32004-2018; China. July 2018. Available online: https://www.chinesestandard.net/PDF/English.aspx/NBT32004-2018 (accessed on 18 June 2019).

- Rockhill, A.A.; Liserre, M.; Teodorescu, R.; Rodriguez, P. Grid-filter design for a multimegawatt medium-voltage voltage-source inverter. IEEE Trans. Ind. Electron. 2011, 58, 1205–1217. [Google Scholar] [CrossRef]

- Dannehl, J.; Liserre, M.; Fuchs, F.W. Filter-based active damping of voltage source converters with LCL filter. IEEE Trans. Ind. Electron. 2011, 58, 3623–3633. [Google Scholar] [CrossRef]

| Symbol | Parameter | Formula | Value |

|---|---|---|---|

| PB | Rated base power | - | 30 kW |

| VB | Ac base voltage | - | 364 V |

| IB | Ac base current | 27.5 A | |

| fB | Base frequency | - | 50 Hz |

| ZB | Base impedance | 13.2496 Ω | |

| LB | Base inductance | 42.17 mH | |

| CB | Base capacitance | 240 μF |

| Filters | Type-1 Filter | Type-2 Filter | Type-3 Filter |

|---|---|---|---|

| Inverter-side Inductor | 0.02845 p.u. × 2 with 2 magnetic cores | 0.0569 p.u. with 1 magnetic core | Tr leakage inductance 0.06 p.u. |

| Grid-side Inductor | Tr leakage inductance 0.06 p.u. | Tr leakage inductance 0.06 p.u. | 0.0237 p.u. |

| Shunt CapacitoR | 0.0208 p.u. | 0.0208 p.u. | 0.0416 p.u. |

| Total Inductance | 0.1169 p.u. | 0.1169 p.u. | 0.0837 p.u. |

| Fault-tolerant applicability | Yes | No | Yes |

| Cases | Case-1 | Case-2 | Case-3 | |||

|---|---|---|---|---|---|---|

| Working Modes | Balance | Unbalance | Balance | Unbalance | Balance | Unbalance |

| THD | 2.73% | 3.08% | 2.4% | 2.67% | 2.47% | 2.79% |

| Dominant Harmonic Percentage | 0.2% | 0.25% | 0.22% | 0.2% | 0.21% | 0.28% |

© 2019 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).

Share and Cite

Wang, B.; Zhang, X.; Song, C.; Cao, R. Research on the Filters for Dual-Inverter Fed Open-End Winding Transformer Topology in Photovoltaic Grid-Tied Applications. Energies 2019, 12, 2338. https://doi.org/10.3390/en12122338

Wang B, Zhang X, Song C, Cao R. Research on the Filters for Dual-Inverter Fed Open-End Winding Transformer Topology in Photovoltaic Grid-Tied Applications. Energies. 2019; 12(12):2338. https://doi.org/10.3390/en12122338

Chicago/Turabian StyleWang, Baoji, Xing Zhang, Chao Song, and Renxian Cao. 2019. "Research on the Filters for Dual-Inverter Fed Open-End Winding Transformer Topology in Photovoltaic Grid-Tied Applications" Energies 12, no. 12: 2338. https://doi.org/10.3390/en12122338