A DC Short-Circuit Fault Ride Through Strategy of MMC-HVDC Based on the Cascaded Star Converter

Abstract

:1. Introduction

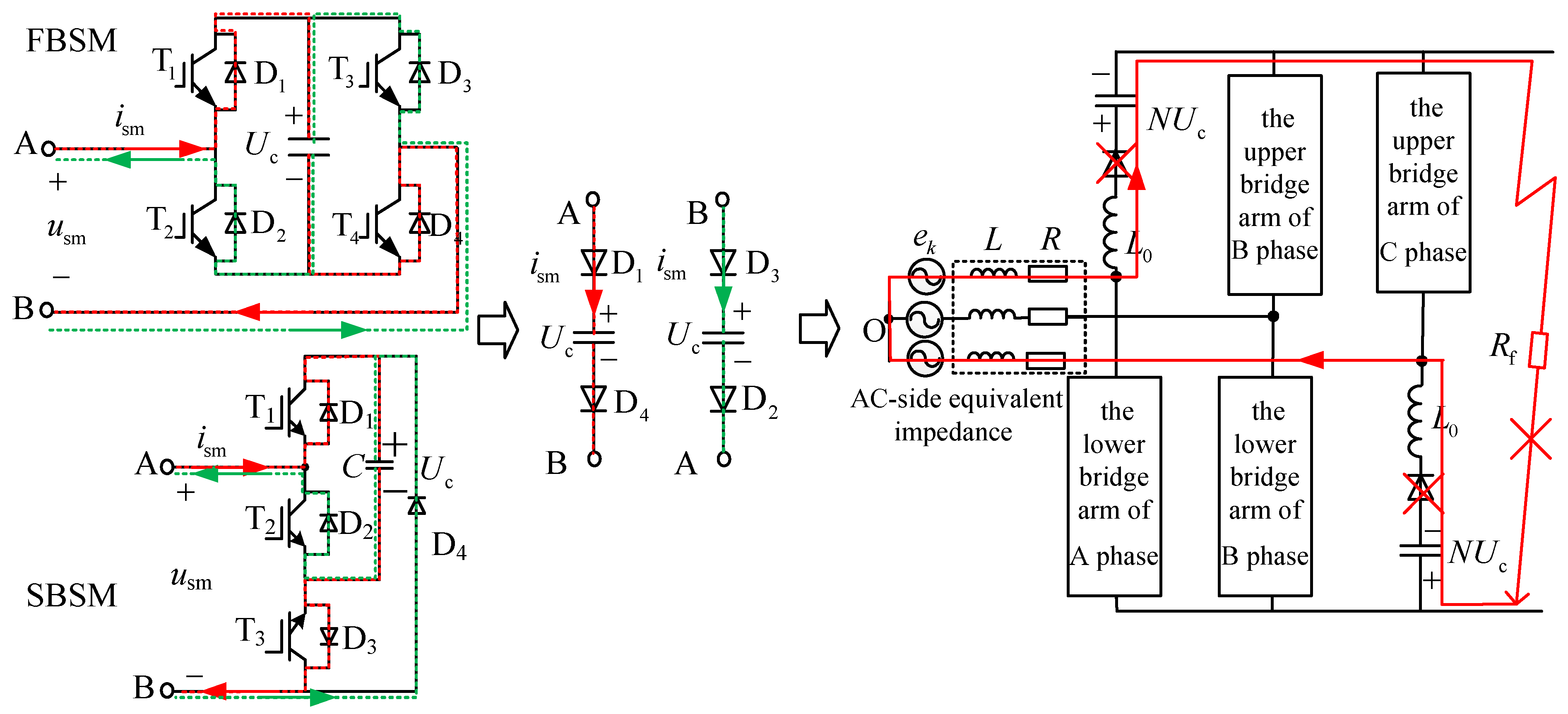

2. The DC-Side Fault Isolation of MMC-HVDC and Capacitor Voltage Divergence

2.1. The DC Fault Isolation of MMC-HVDC Using the SM with DC Fault Self-Clearing

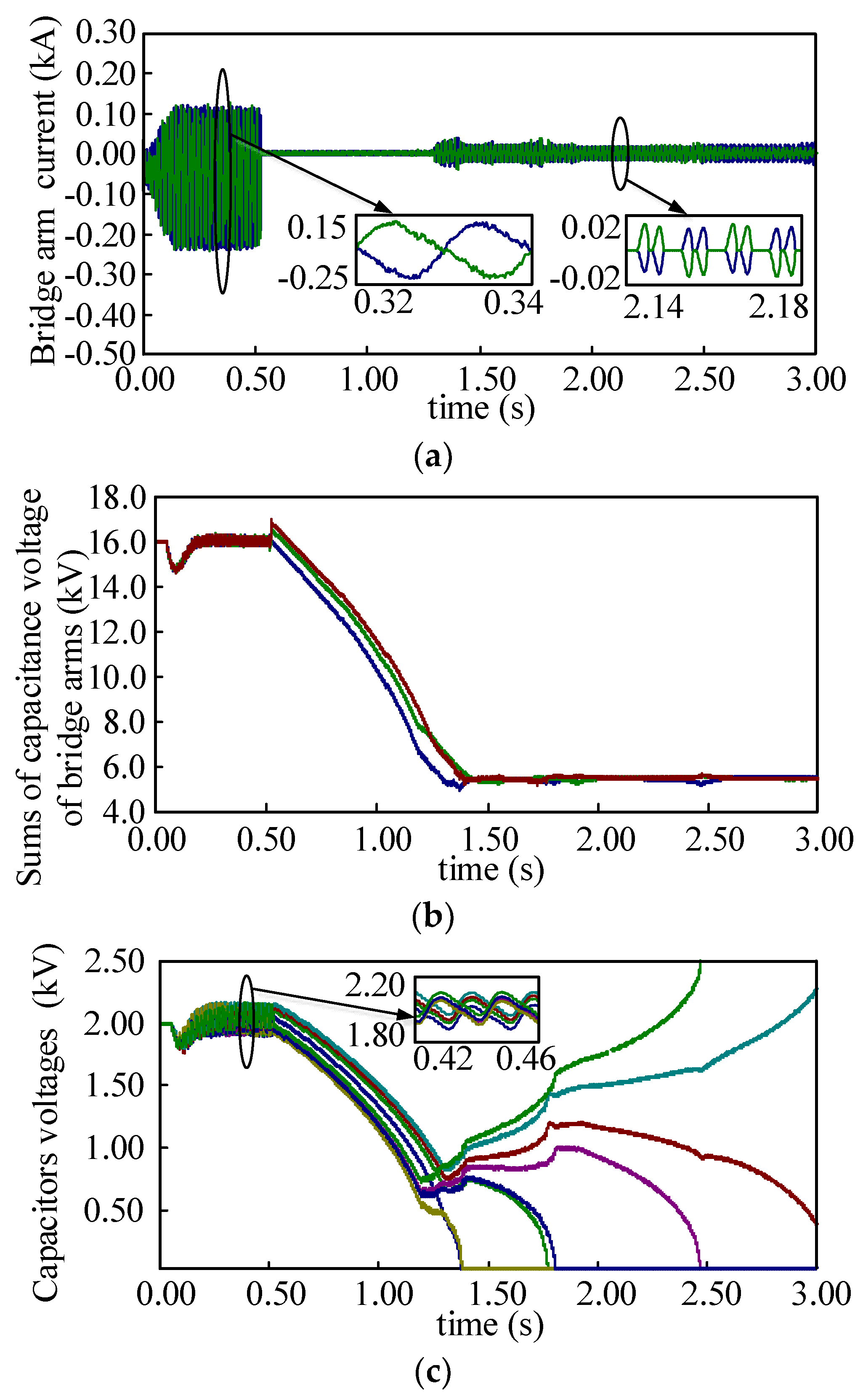

2.2. Capacitor Voltage Divergence of MMC-HVDC Using the SM with DC Fault Self-Clearing

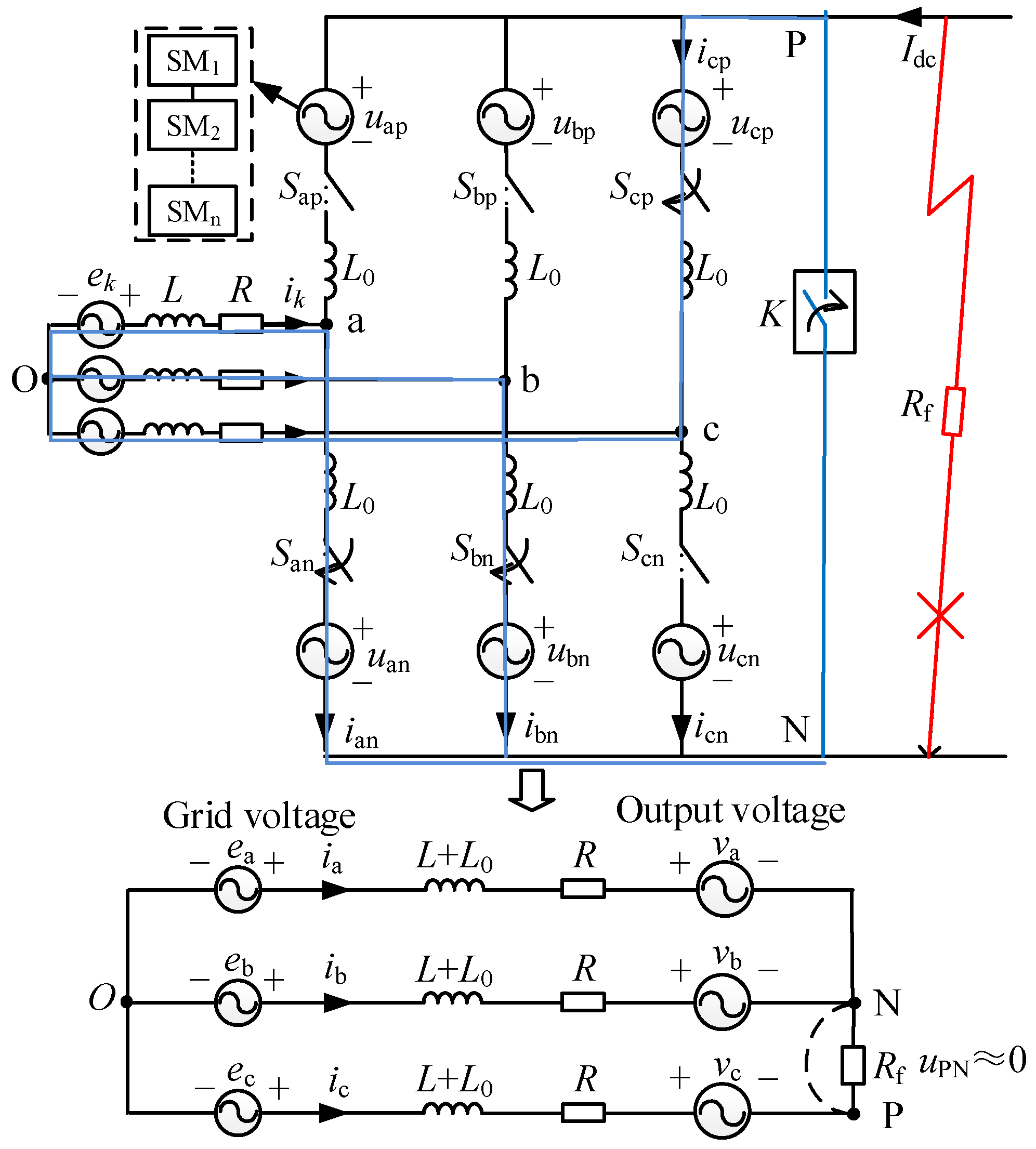

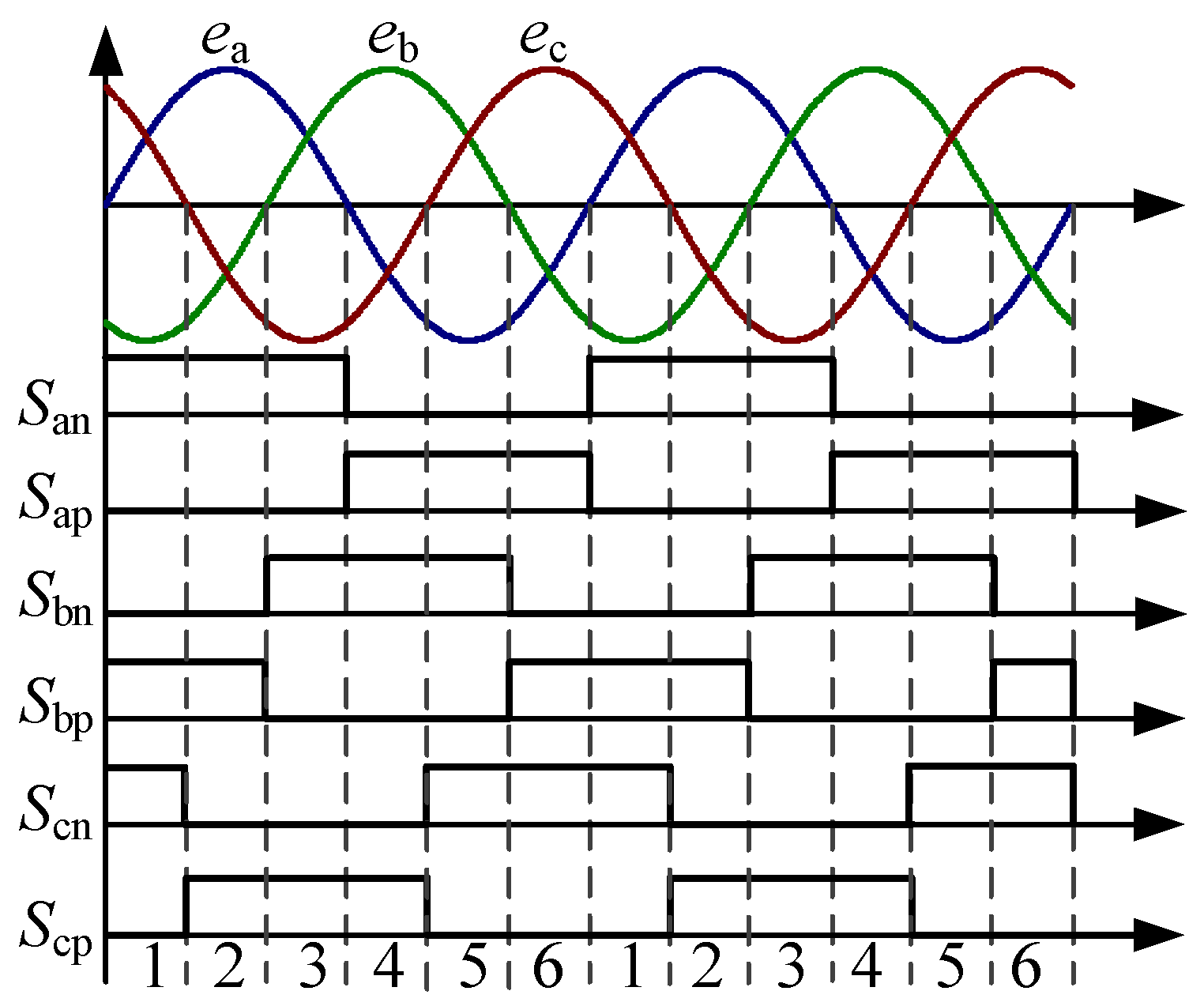

3. DC Short-Circuit Fault Ride Through Principle Based on the Cascaded Star Converter

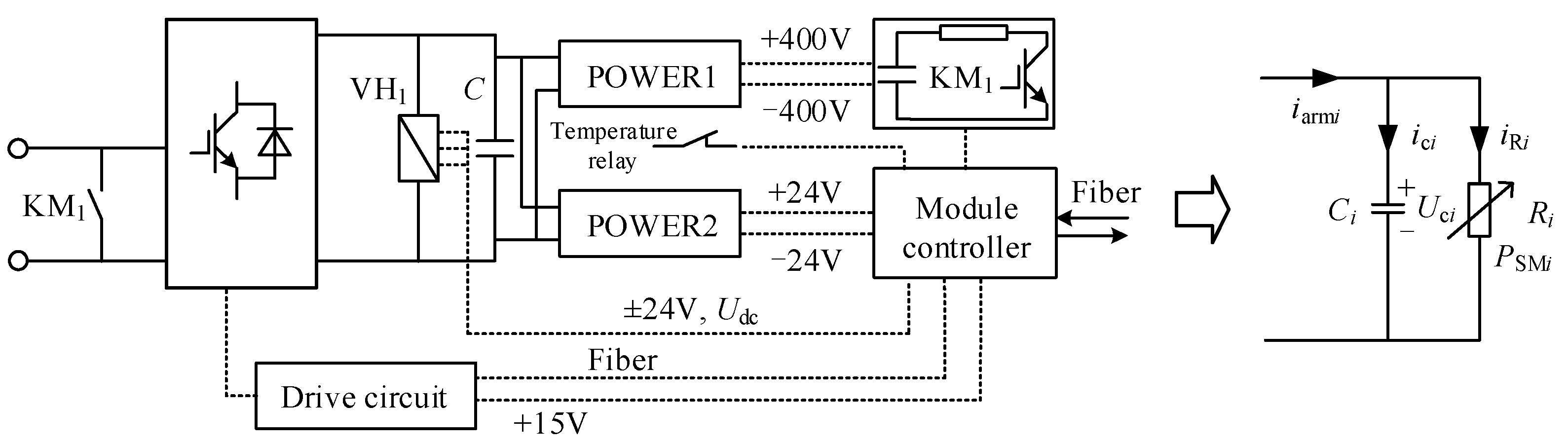

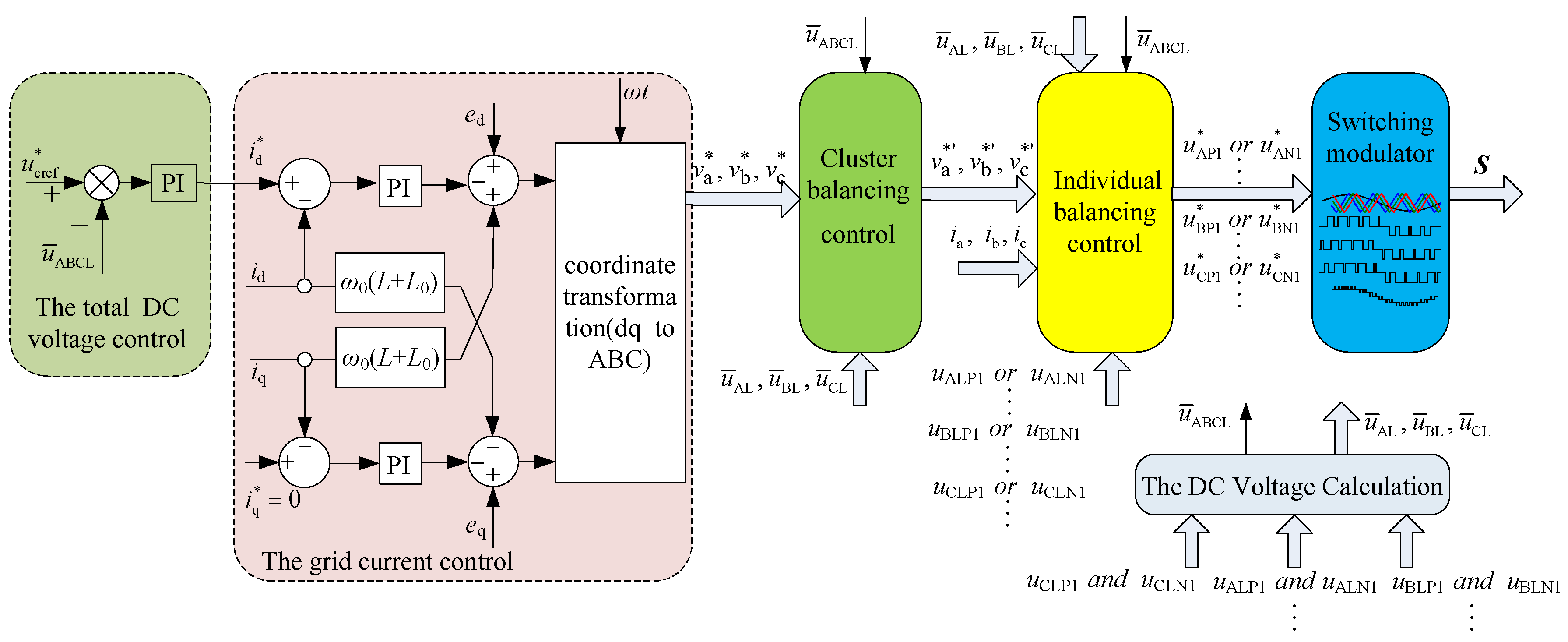

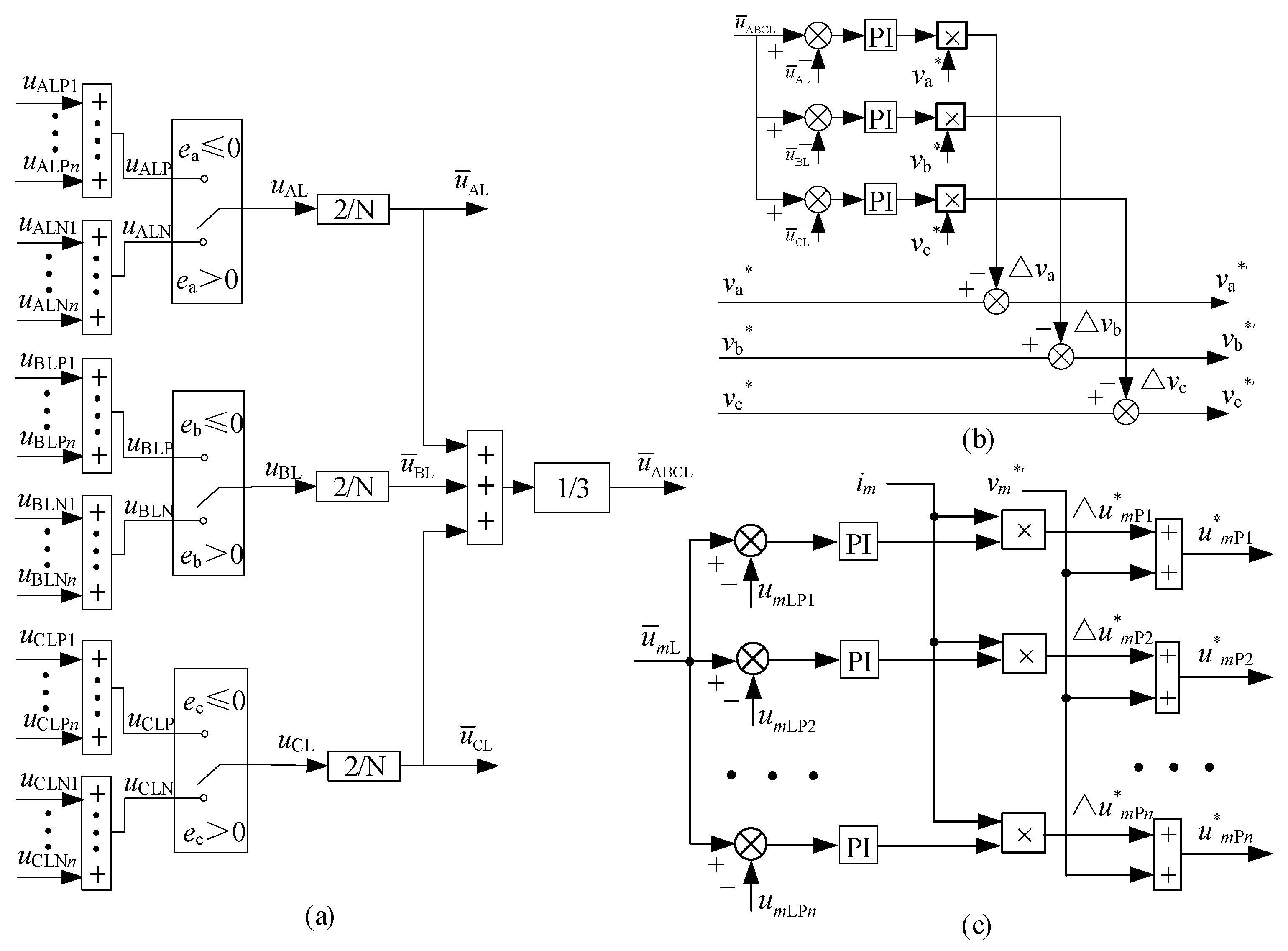

4. Implementation of DC Short-Circuit Fault Ride Through Strategy Based on the Cascaded Star Converter

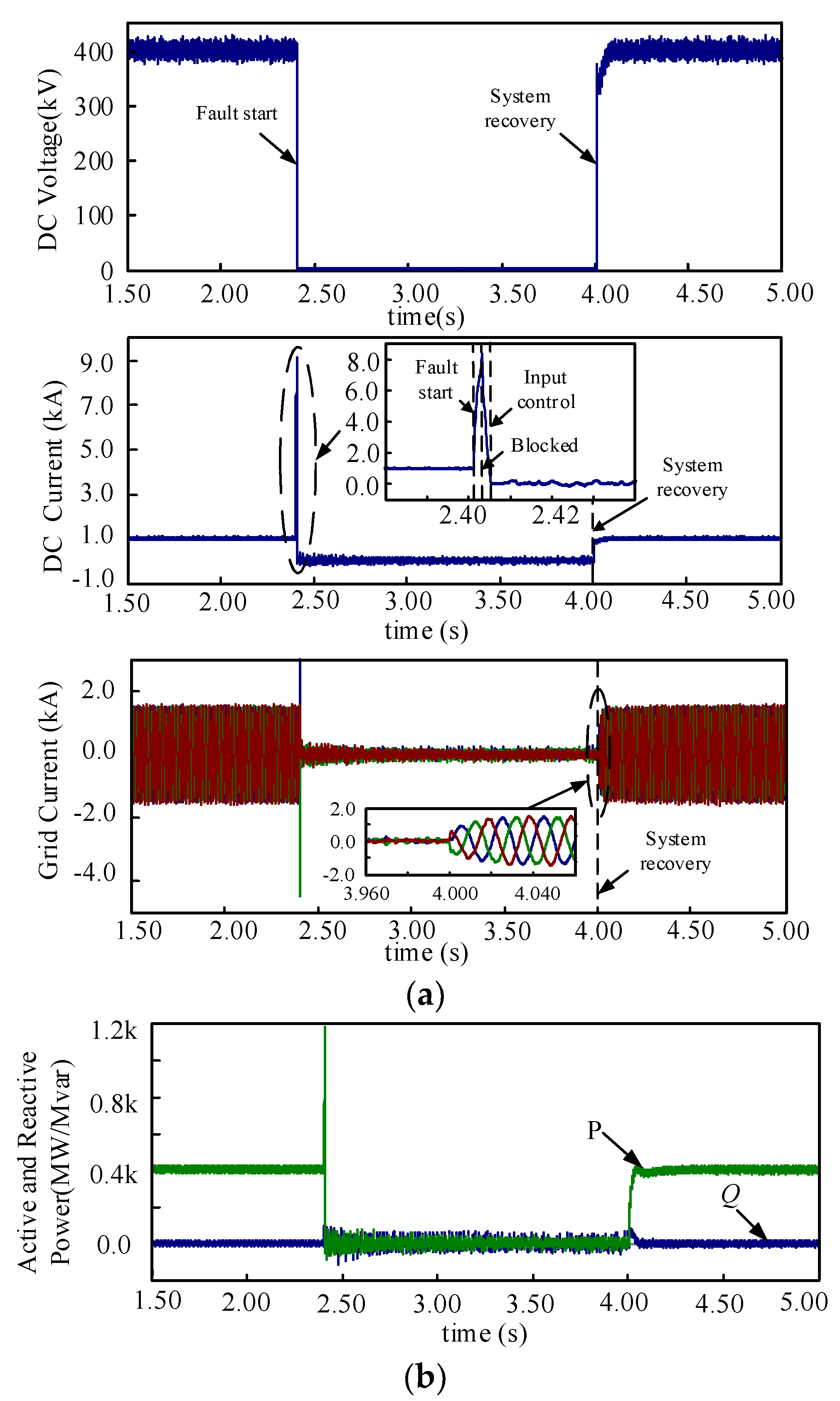

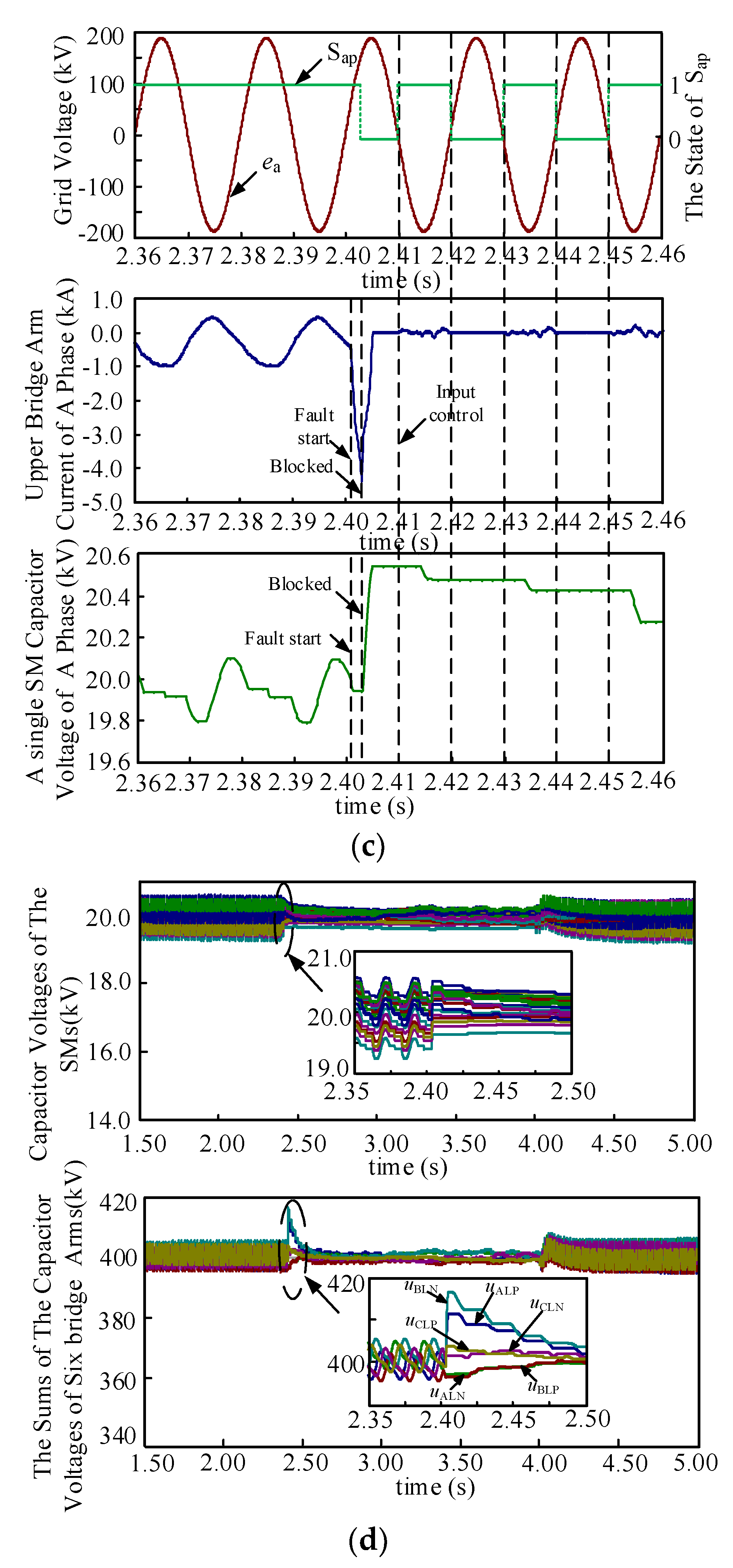

5. Simulation Verification

6. Conclusions

- (a)

- The short-circuit current does not exist during DC short-circuit fault ride through;

- (b)

- The converter is controllable during fault ride through, which avoids the divergence of the capacitor voltages;

- (c)

- The AC breaker will not be tripped. After the fault is cleared, the power transmission is recovered quickly; and

- (d)

- The strategy can be applied to more MMC-HVDC topologies including in the topologies using the SMs with DC fault self-clearing but not generating −1 level.

Author Contributions

Funding

Conflicts of Interest

References

- Flourentzou, N.; Agelidis, V.G.; Demetriades, G.D. VSC-based HVDC power transmission systems: An overview. IEEE Trans. Power Electron. 2009, 24, 592–602. [Google Scholar] [CrossRef]

- Wang, S.; Tang, G.; He, Z. Comprehensive evaluation of VSC-HVDC transmission based on improved analytic hierarchy process. In Proceedings of the 2008 Third International Conference on Electric Utility Deregulation and Restructuring and Power Technologies, Nanjing, China, 6–9 April 2008. [Google Scholar]

- Li, R.; Fletcher, J.E.; Xu, L.; Holliday, D.; Williams, B.W. A hybrid modular multilevel converter with novel three-level cells for DC fault blocking capability. IEEE Trans. Power Deliv. 2015, 30, 2017–2026. [Google Scholar] [CrossRef]

- Lesnicar, A.; Marquardt, R. An innovative modular multilevel converter topology suitable for a wide power range. In Proceedings of the 2003 IEEE Bologna Power Tech Conference, Bologna, Italy, 23–26 June 2003. [Google Scholar]

- Song, Q.; Liu, W.; Li, X.; Rao, H.; Xu, S.; Li, L. A steady-state analysis method for a modular multilevel converter. IEEE Trans. Power Electron. 2013, 28, 3702–3713. [Google Scholar] [CrossRef]

- Saeedifard, M.; Iravani, R. Dynamic performance of modular multilevel back-to-back HVDC system. IEEE Trans. Power Deliv. 2011, 25, 2903–2912. [Google Scholar] [CrossRef]

- Meyer, J.M.; Rufer, A. A DC hybrid circuit breaker with ultra-fast contact opening and integrated gate-commutated thyristors (IGCTs). IEEE Trans. Power Deliv. 2006, 21, 646–651. [Google Scholar] [CrossRef]

- Franck, C.M. HVDC circuit breakers: A review identifying future research needs. IEEE Trans. Power Deliv. 2011, 26, 998–1007. [Google Scholar] [CrossRef]

- Nakao, H.; Nakagoshi, Y.; Hatano, M.; Koshizuka, T.; Nishiwaki, S.; Kobayashi, A.; Murao, T.; Yanabu, S. DC current interruption in HVDC SF/sub6/gas MRTB by means of self-excited oscillation superimposition. IEEE Trans. Power Deliv. 2002, 16, 687–693. [Google Scholar] [CrossRef]

- Candelaria, J.; Park, J.D. VSC-HVDC system protection: A review of current methods. In Proceedings of the 2011 IEEE/PES Power Systems Conference and Exposition, Phoenix, AZ, USA, 20–23 March 2011. [Google Scholar]

- Schmitt, D.; Wang, Y.; Weyh, T.; Marquardt, R. DC-side fault current management in extended multiterminal-HVDC-grids. In Proceedings of the International Multi-Conference on Systems, Sygnals & Devices, Chemnitz, Germany, 20–23 March 2012. [Google Scholar]

- Debnath, S.; Qin, J.; Bahrani, B.; Saeedifard, M.; Barbosa, P. Operation, control, and applications of the modular multilevel converter: A review. IEEE Trans. Power Electron. 2014, 30, 37–53. [Google Scholar] [CrossRef]

- Tang, G.; Xu, Z.; Zhou, Y. Impacts of three MMC-HVDC configurations on AC system stability under DC line faults. IEEE Trans. Power Syst. 2014, 29, 3030–3040. [Google Scholar] [CrossRef]

- Yang, J.; Fletcher, J.E.; O’Reilly, J. Short-circuit and ground fault analyses and location in VSC-based DC network cables. IEEE Trans. Ind. Electron. 2014, 29, 3030–3040. [Google Scholar] [CrossRef]

- Elserougi, A.A.; Abdel-Khalik, A.S.; Massoud, A.M.; Ahmed, S. A new protection scheme for HVDC converters against DC-side faults with current suppression capability. IEEE Trans. Power Deliv. 2014, 29, 1569–1577. [Google Scholar] [CrossRef]

- Li, X.; Song, Q.; Liu, W.; Rao, H.; Xu, S.; Li, L. Protection of nonpermanent faults on DC overhead lines in MMC-based HVDC systems. IEEE Trans. Power Deliv. 2013, 28, 483–490. [Google Scholar] [CrossRef]

- Marquardt, R. Modular Multilevel Converter: An universal concept for HVDC-Networks and extended DC-Bus-applications. In Proceedings of the 2010 International Power Electronics Conference—ECCE Asia, Sapporo, Japan, 21–24 June 2010. [Google Scholar]

- Soto-Sanchez, D.; Green, T.C. Control of a modular multilevel converter-based HVDC transmission system. In Proceedings of the 2011 14th European Conference on Power Electronics and Applications, Birmingham, UK, 30 August–1 September 2011. [Google Scholar]

- Marquardt, R. Modular Multilevel Converter topologies with DC-Short circuit current limitation. In Proceedings of the 8th International Conference on Power Electronics—ECCE Asia, Jeju, Korea, 30 May–3 June 2011. [Google Scholar]

- Zhang, J.; Zhao, C.; Sun, H.; Huang, X.; Yi, L.; Peng, Q. Improved topology of modular multilevel converter and application. Trans. China Electrotech. Soc. 2014, 29, 173–179. [Google Scholar]

- Zeng, R.; Xu, L.; Yao, L. An improved modular multilevel converter with DC fault blocking capability. In Proceedings of the 2014 IEEE PES General Meeting | Conference & Exposition, National Harbor, MD, USA, 27–31 July 2014. [Google Scholar]

- Wang, X.; Lin, W.; Wen, J.; Cheng, S. A new topology of sub-modules with DC fault current blocking capability and a new type of hybrid MMC converter. Proc. CSEE 2014, 34, 5171–5179. [Google Scholar]

- Li, X.; Liu, W.; Song, Q.; Rao, H.; Xu, S. An enhanced MMC topology with DC fault ride-through capability. In Proceedings of the IECON 2013—39th Annual Conference of the IEEE Industrial Electronics Society, Vienna, Austria, 10–13 November 2013. [Google Scholar]

- Elserougi, A.A.; Massoud, A.M.; Ahmed, S. A switched-capacitor submodule for modular multilevel HVDC converters with DC-fault blocking capability and a reduced number of sensors. IEEE Trans. Power Deliv. 2016, 31, 313–322. [Google Scholar] [CrossRef]

- Oliveira, R.; Yazdani, A. A modular multilevel converter with DC fault handling capability and enhanced efficiency for HVDC system applications. IEEE Trans. Power Electron. 2017, 32, 11–22. [Google Scholar] [CrossRef]

- Luo, Y.; Li, Y.; Li, Z.; Wang, P.; Chu, Z.; Xu, L.; Zhao, C. DC short-circuit fault ride-through control strategy of full-bridge MMC-HVDC systems. Proc. CSEE 2016, 36. [Google Scholar] [CrossRef]

- Adam, G.P.; Davidson, I.E. Robust and generic control of full-bridge modular multilevel converter high-voltage DC transmission systems. EEE Trans. Power Deliv. 2015, 30, 2468–2476. [Google Scholar] [CrossRef]

- Cui, S.; Sul, S.K. A comprehensive DC short-circuit fault ride through strategy of hybrid modular multilevel converters (MMCs) for overhead line transmission. IEEE Trans. Power Electron. 2016, 31, 7780–7796. [Google Scholar] [CrossRef]

- Akagi, H.; Inoue, S.; Yoshii, T. Control and performance of a transformerless cascade PWM STATCOM with star configuration. IEEE Trans. Ind. Appl. 2007, 43, 1041–1049. [Google Scholar] [CrossRef]

- Song, Q.; Liu, W. Control of a cascade STATCOM with star configuration under unbalanced conditions. IEEE Trans. Power Electron. 2009, 24, 45–57. [Google Scholar] [CrossRef]

- Zhao, T.; Wang, G.; Bhattacharya, S. Voltage and power balance control for a cascaded h-bridge converter-based solid-state transformer. IEEE Trans. Power Electron. 2013, 28, 1523–1532. [Google Scholar] [CrossRef]

| Description | Symbol | Value |

|---|---|---|

| Grid voltage | Us | 230 kV |

| AC-side equivalent inductance | L | 0.05 H |

| Fundamental frequency | fb | 50 Hz |

| Rated active power | P | 400 MW |

| DC voltage | Udc | ±200 kV |

| No. of SMs(per arm) | N | 20 |

| Capacitor voltage | Uc | 20 kV |

| Capacitor value | C | 5000 μF |

| Bridge arm inductance | L0 | 0.05 H |

| Switching frequency | fsw | 200 Hz |

| Short-circuit resistance | Rf | 0.01 Ω |

| Parameter | Conventional Blocking Protection | Strategy of [26] | Fault Ride Though Protection | |||

|---|---|---|---|---|---|---|

| Temporary | Permanent | Temporary | Permanent | Temporary | Permanent | |

| Fault clear time | short | short | long | long | short | short |

| Fault ride through capability | yes | no | yes | yes | yes | yes |

| Recovery time | short | long | short | short | short | short |

| Condition of MMC | uncontrolled | uncontrolled | controlled | controlled | controlled | controlled |

| IGBTs of single bridge arm | 4n | 4n | 3n | |||

© 2018 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).

Share and Cite

Wang, Y.; Yang, B.; Zuo, H.; Liu, H.; Yan, H. A DC Short-Circuit Fault Ride Through Strategy of MMC-HVDC Based on the Cascaded Star Converter. Energies 2018, 11, 2079. https://doi.org/10.3390/en11082079

Wang Y, Yang B, Zuo H, Liu H, Yan H. A DC Short-Circuit Fault Ride Through Strategy of MMC-HVDC Based on the Cascaded Star Converter. Energies. 2018; 11(8):2079. https://doi.org/10.3390/en11082079

Chicago/Turabian StyleWang, Yingjie, Bo Yang, Huifang Zuo, Haiyuan Liu, and Haohao Yan. 2018. "A DC Short-Circuit Fault Ride Through Strategy of MMC-HVDC Based on the Cascaded Star Converter" Energies 11, no. 8: 2079. https://doi.org/10.3390/en11082079

APA StyleWang, Y., Yang, B., Zuo, H., Liu, H., & Yan, H. (2018). A DC Short-Circuit Fault Ride Through Strategy of MMC-HVDC Based on the Cascaded Star Converter. Energies, 11(8), 2079. https://doi.org/10.3390/en11082079