Studies on a Hybrid Full-Bridge/Half-Bridge Bidirectional CLTC Multi-Resonant DC-DC Converter with a Digital Synchronous Rectification Strategy

Abstract

:1. Introduction

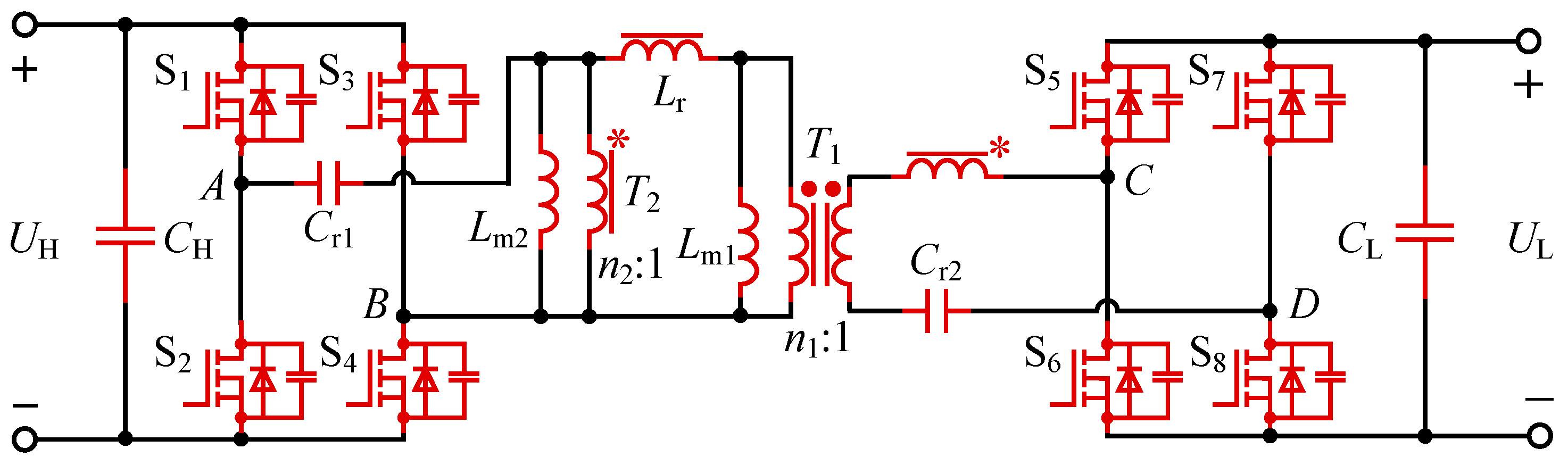

2. Operation Principles and Characteristic Description

2.1. Operation Principles

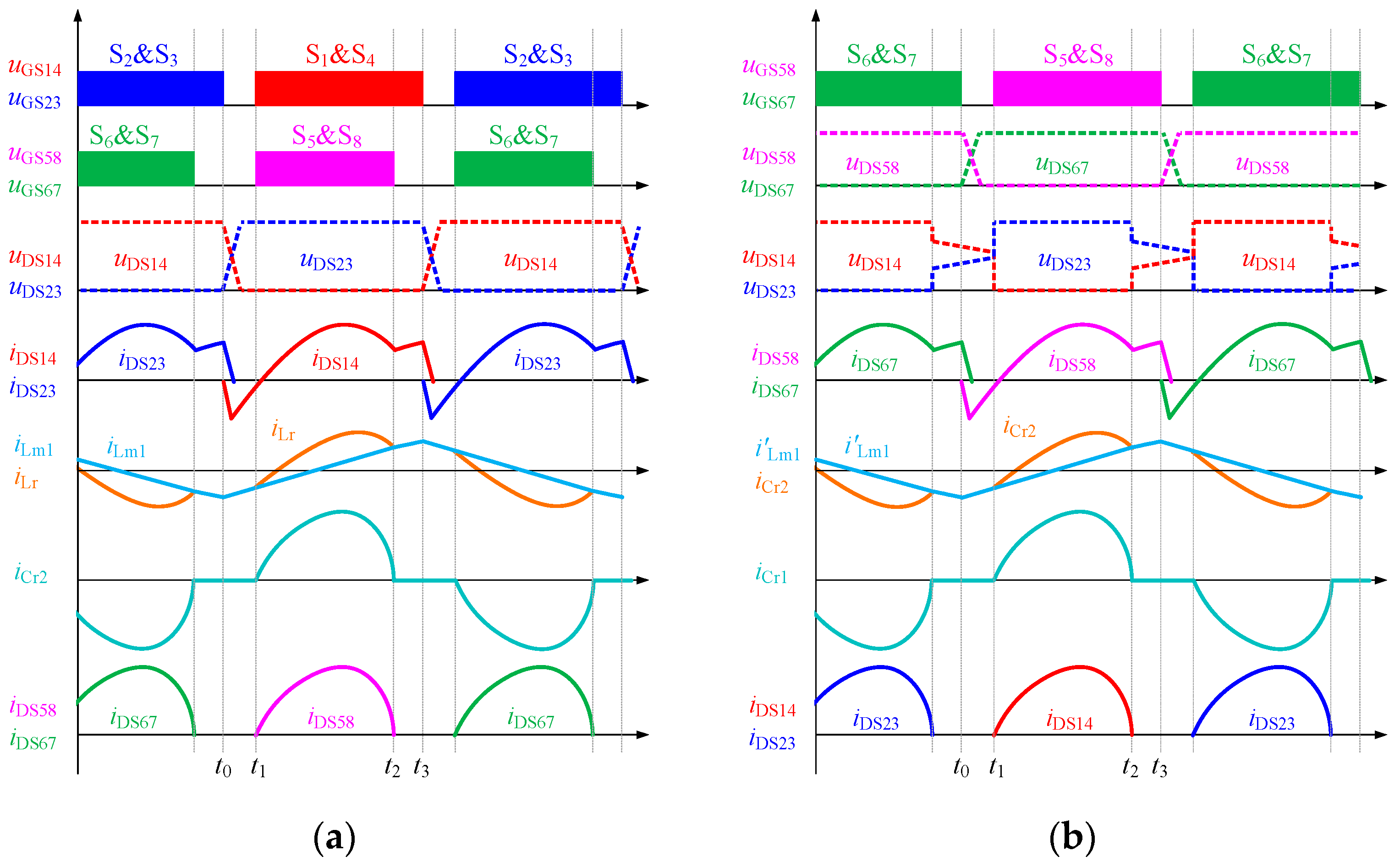

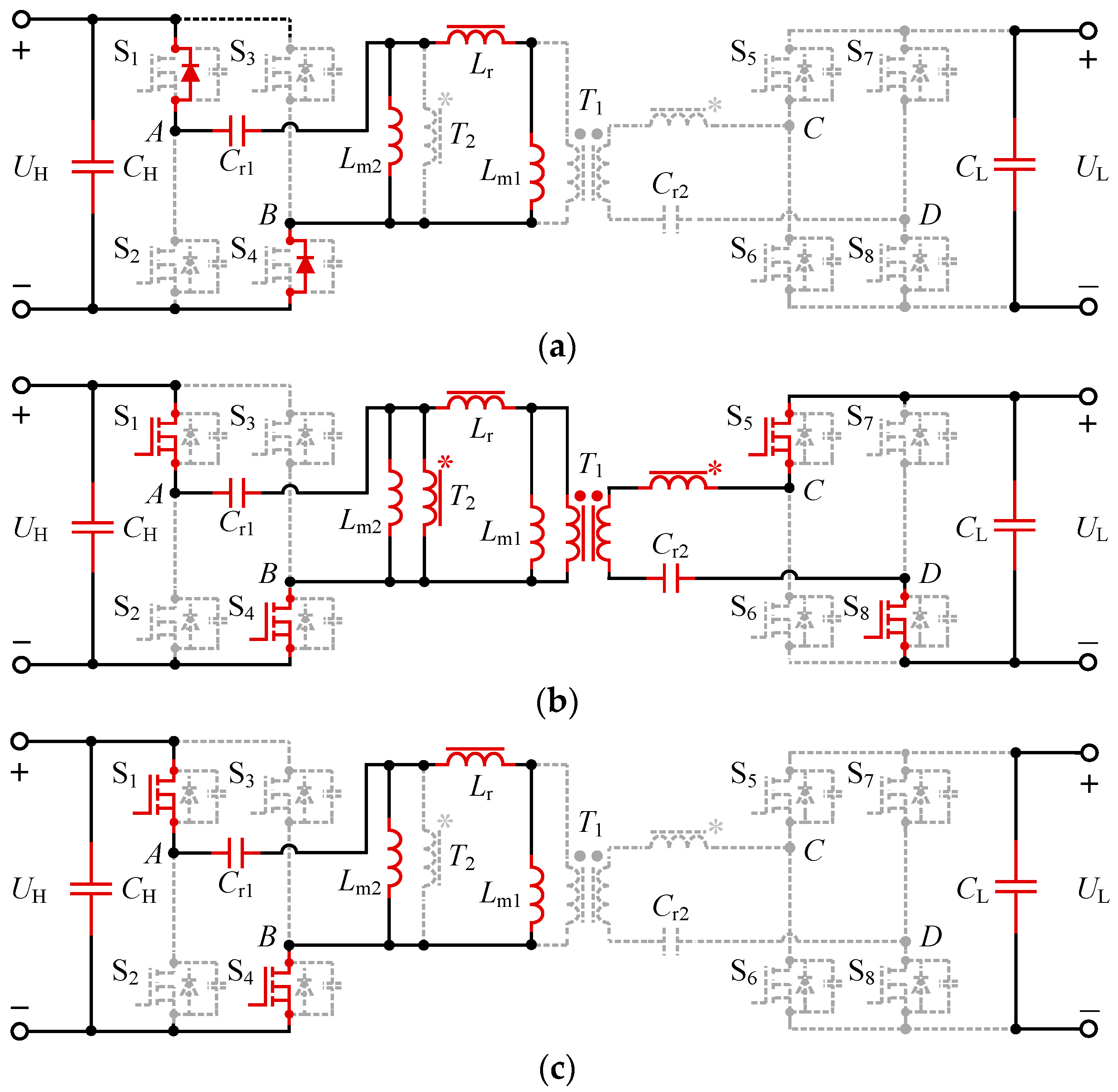

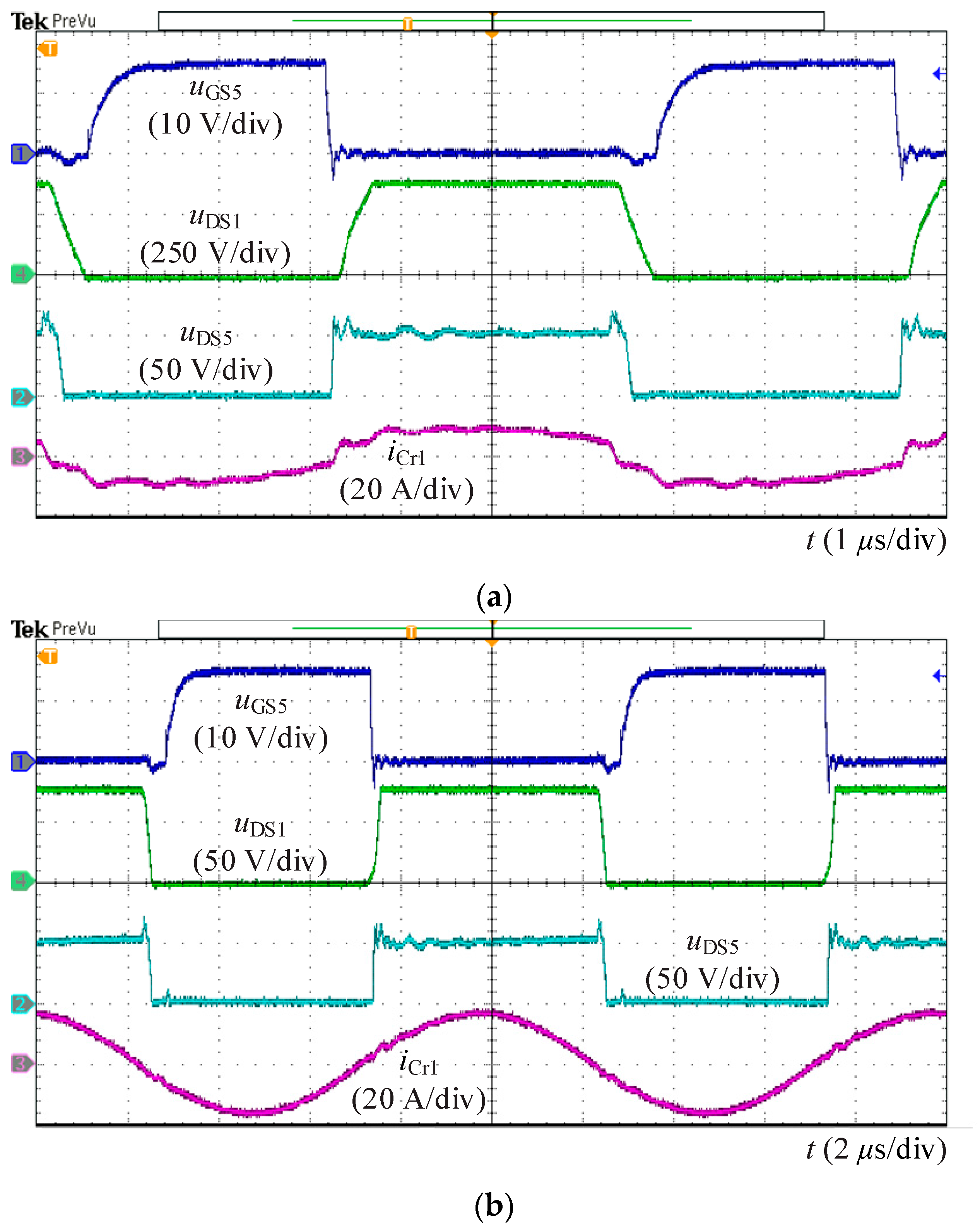

2.1.1. Forward Mode

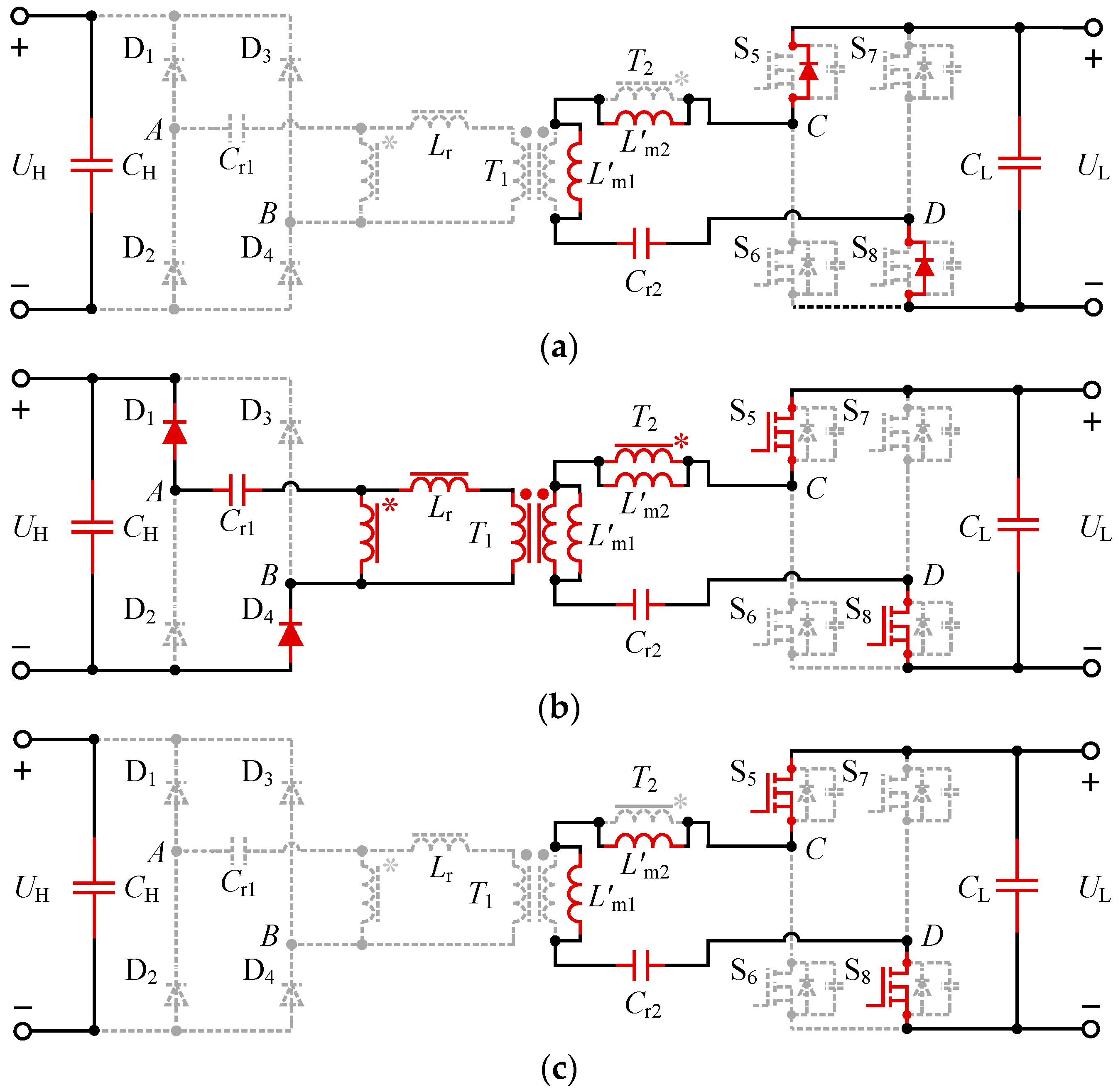

2.1.2. Backward Mode

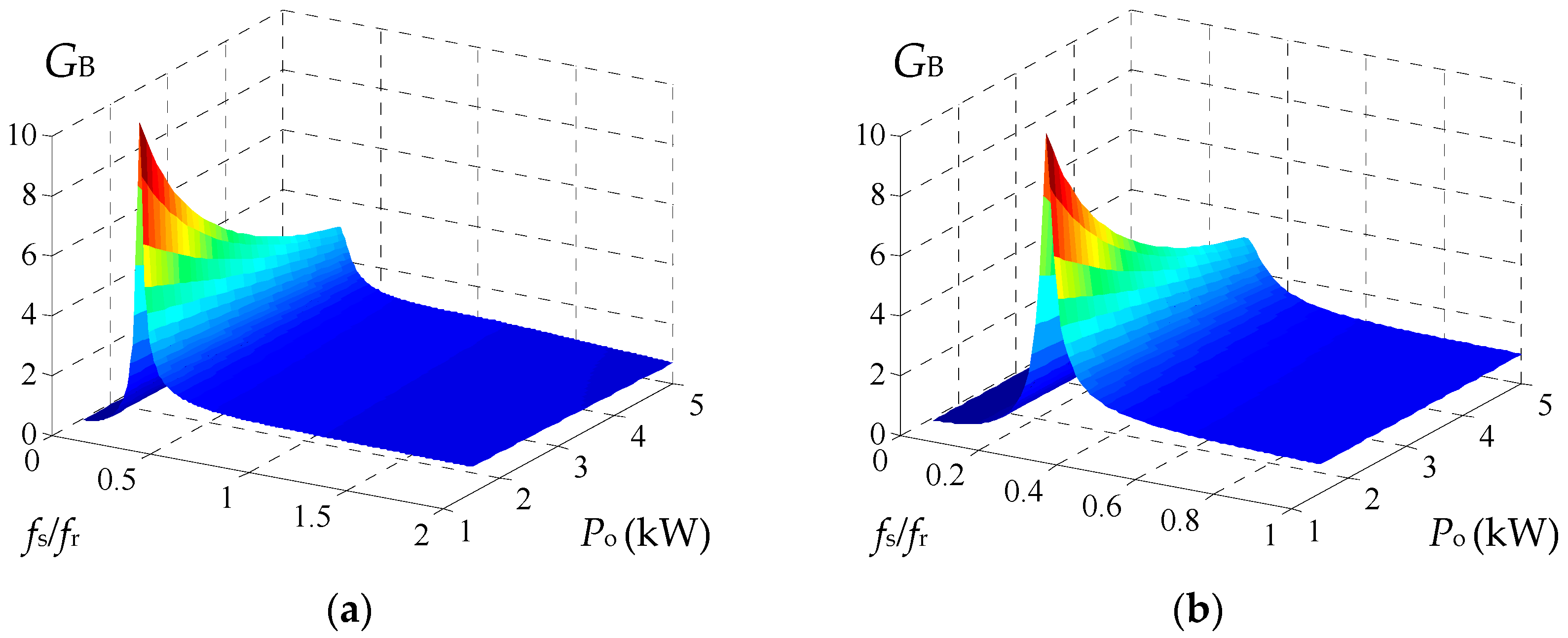

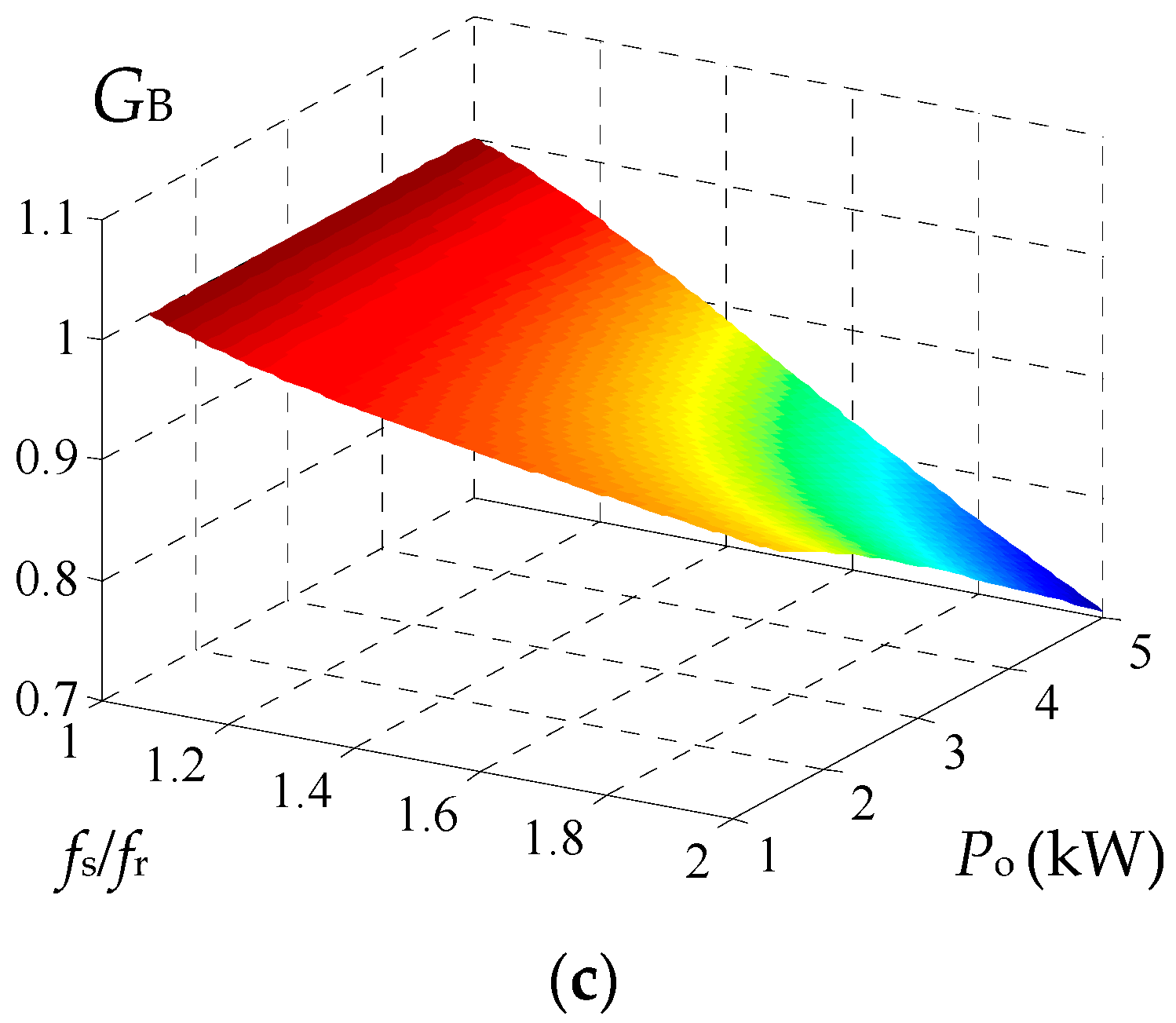

2.2. Characteristic Description

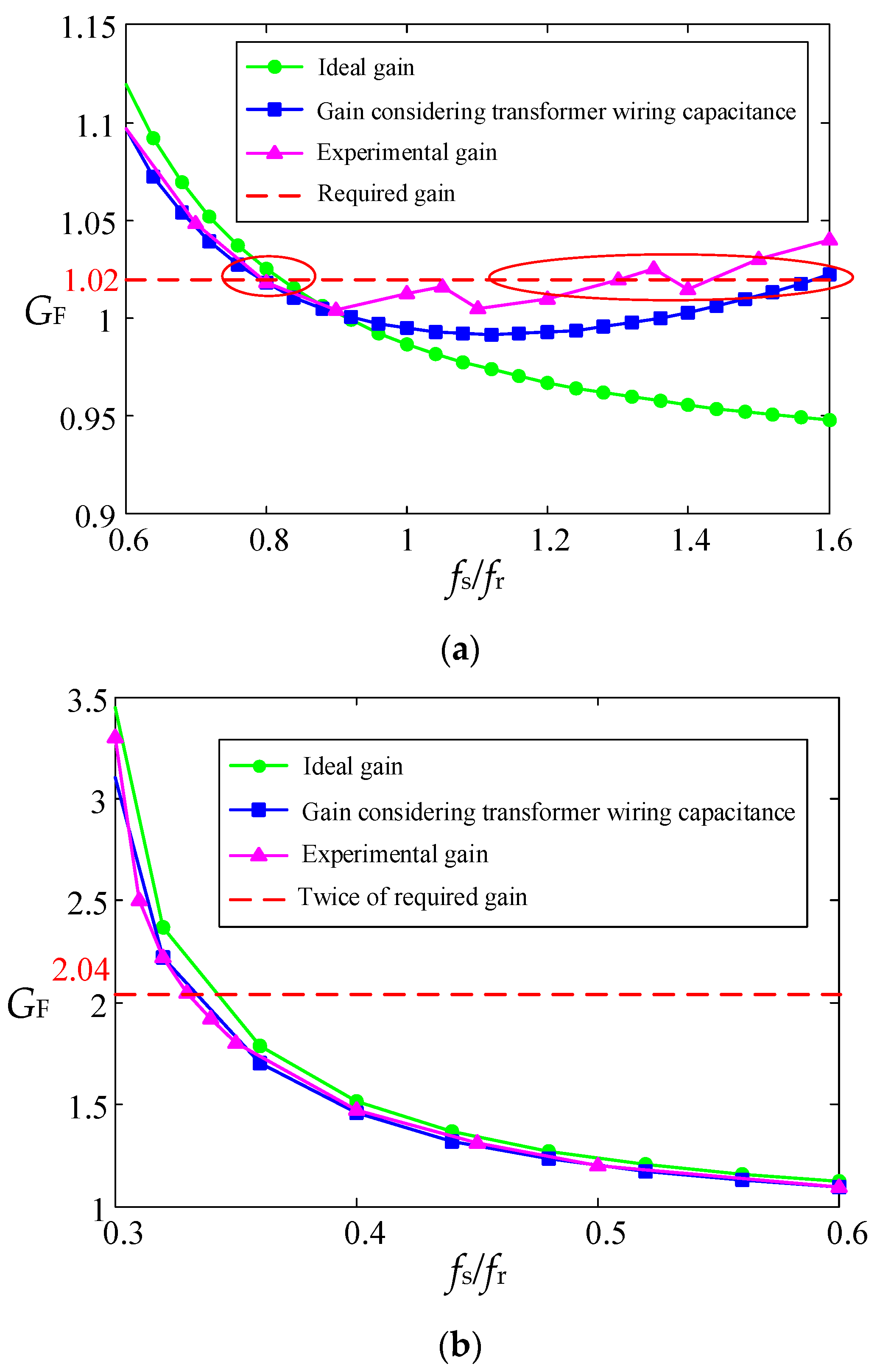

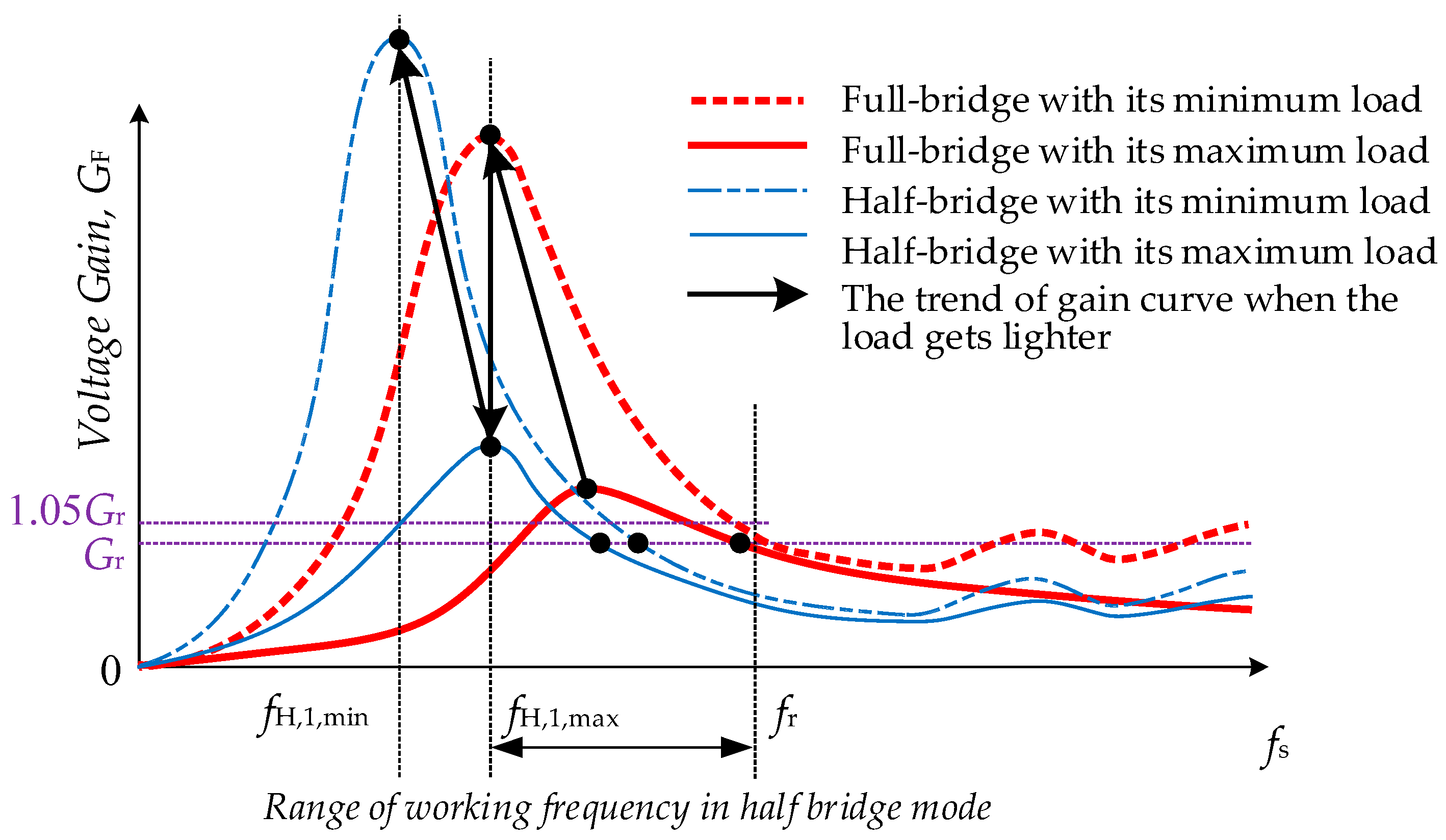

3. Hybrid Full-Bridge/Half-Bridge Configuration

3.1. Half-Bridge Configuration at Light Load Condition

3.2. Voltage and Current Stresses

3.3. Load and Working Frquency Range

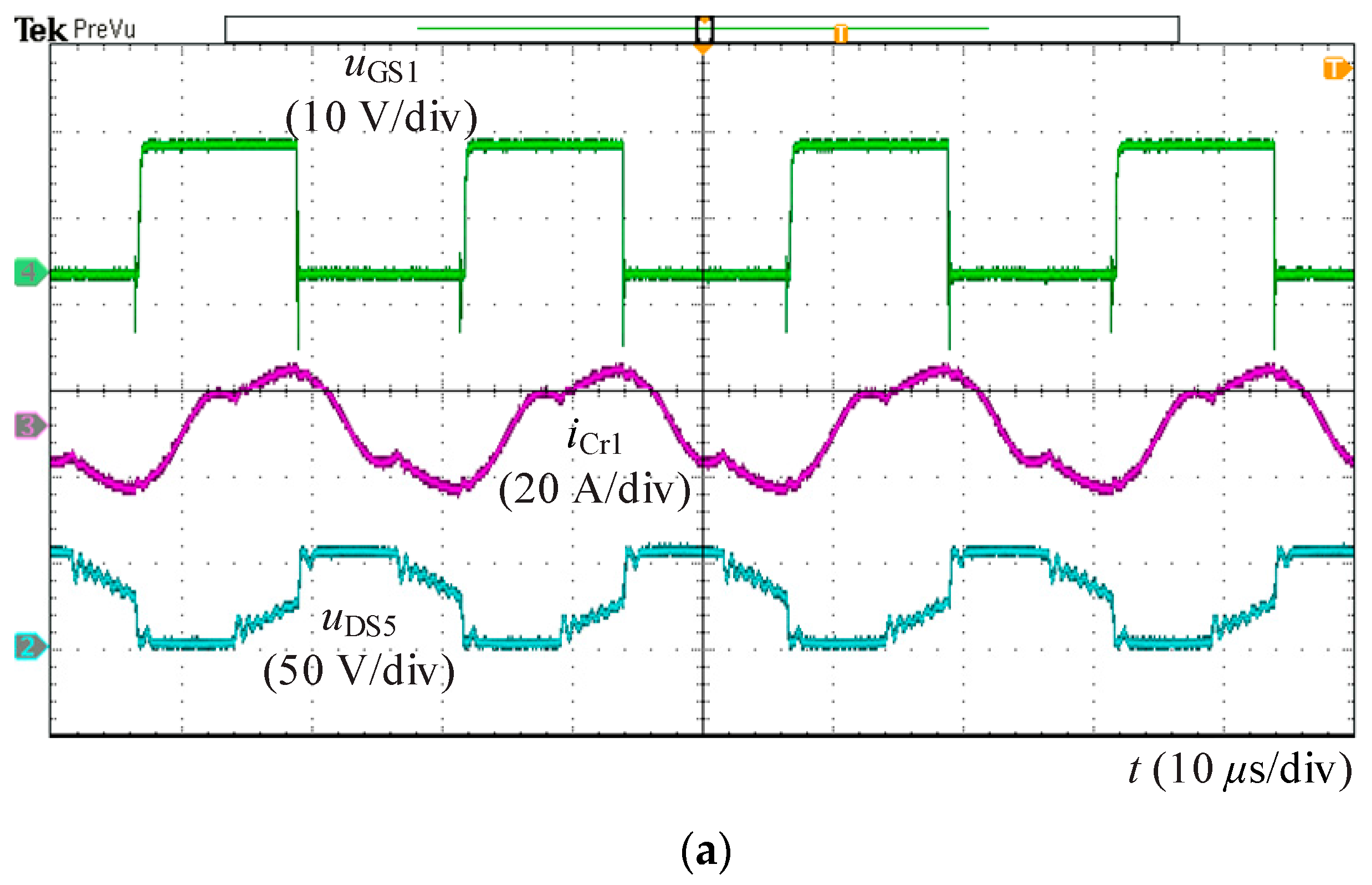

4. Synchronous Rectification Strategy Based on Estimation of Body Diodes’ Conduction Time

4.1. Synchornous Rectification Strategy

4.2. Estimation of the Body Diodes’ Conduction Time

5. Power Loss Analysis

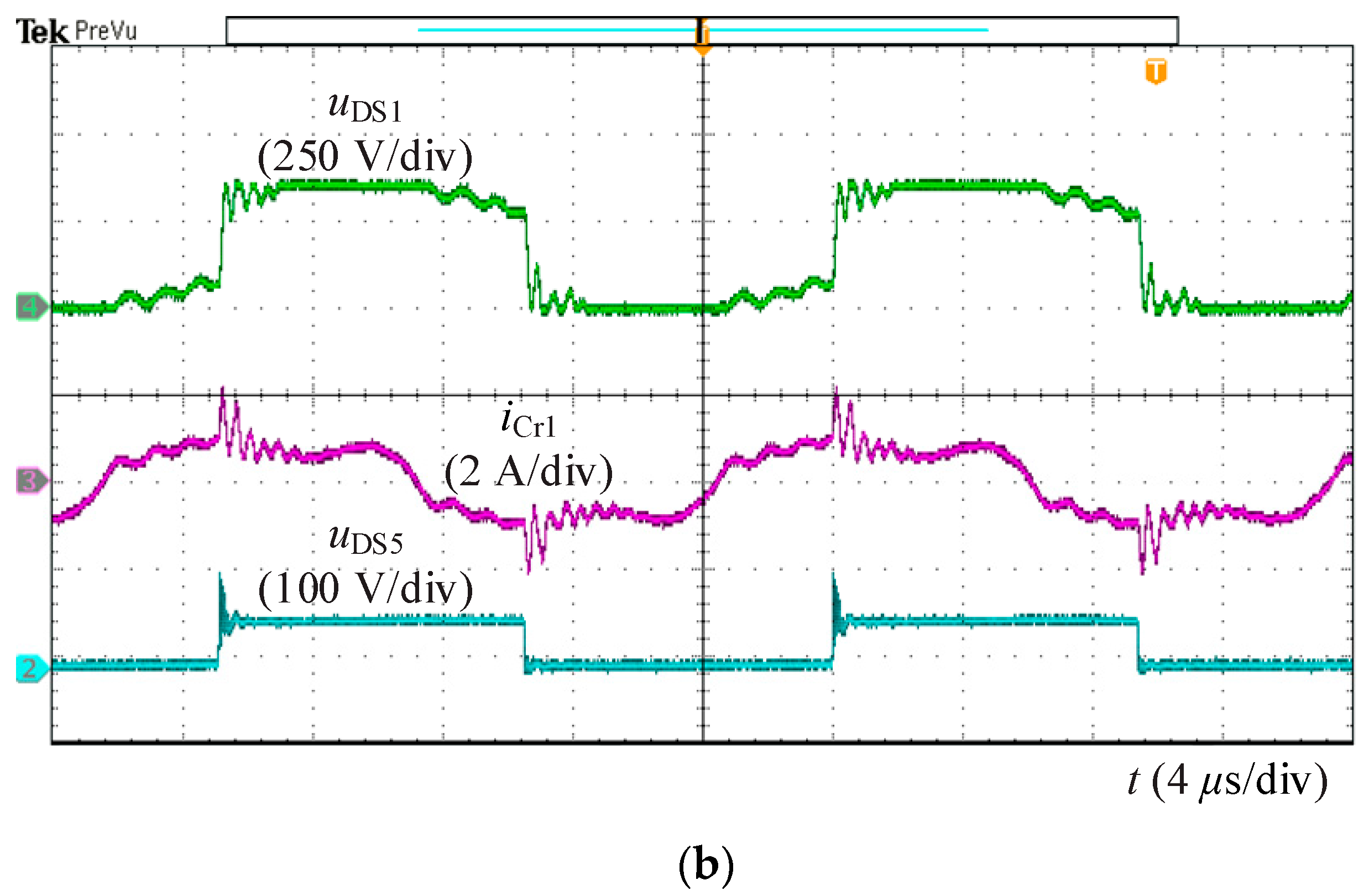

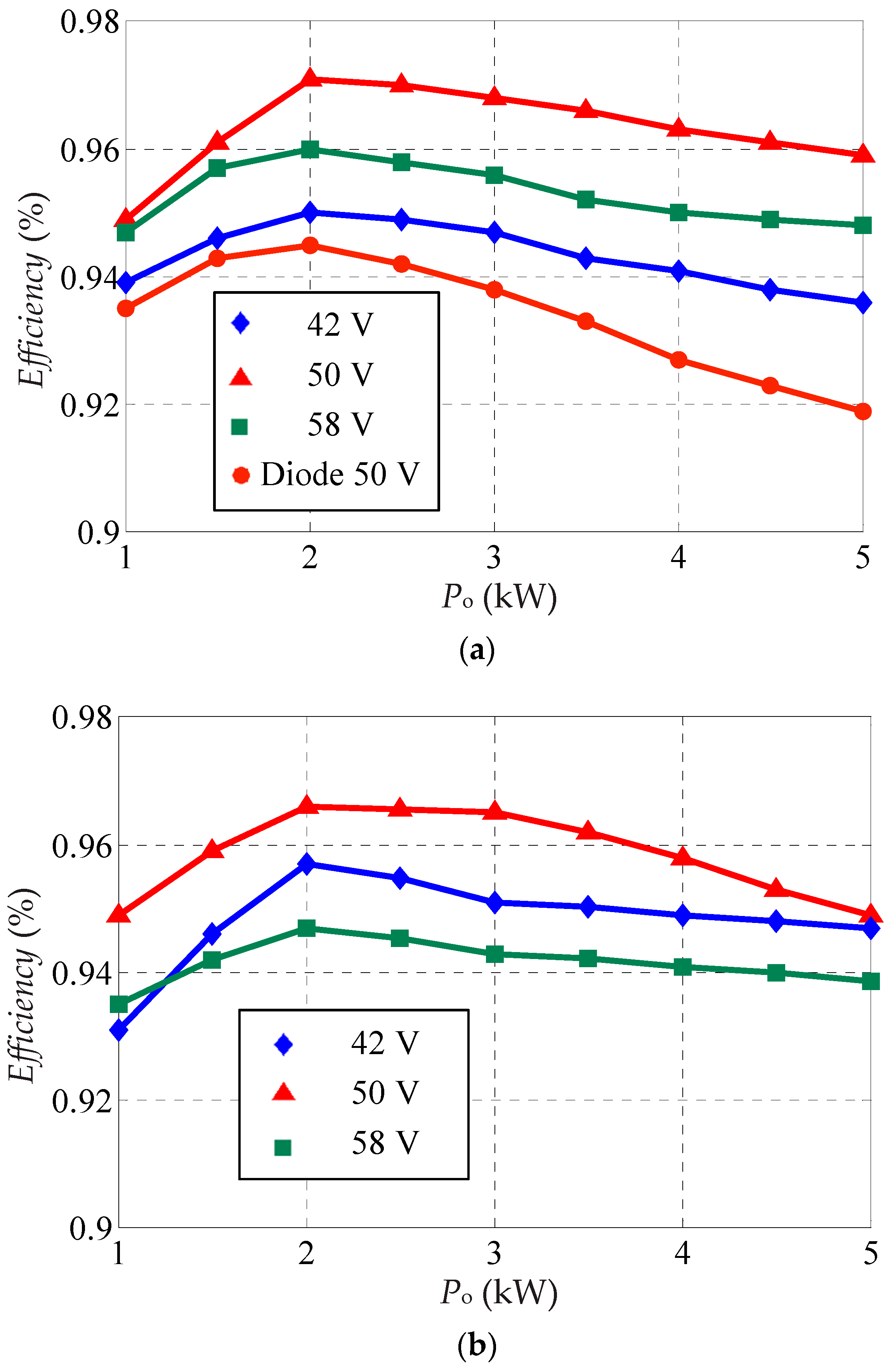

5.1. Loss Distribution with Different LVS DC Voltages

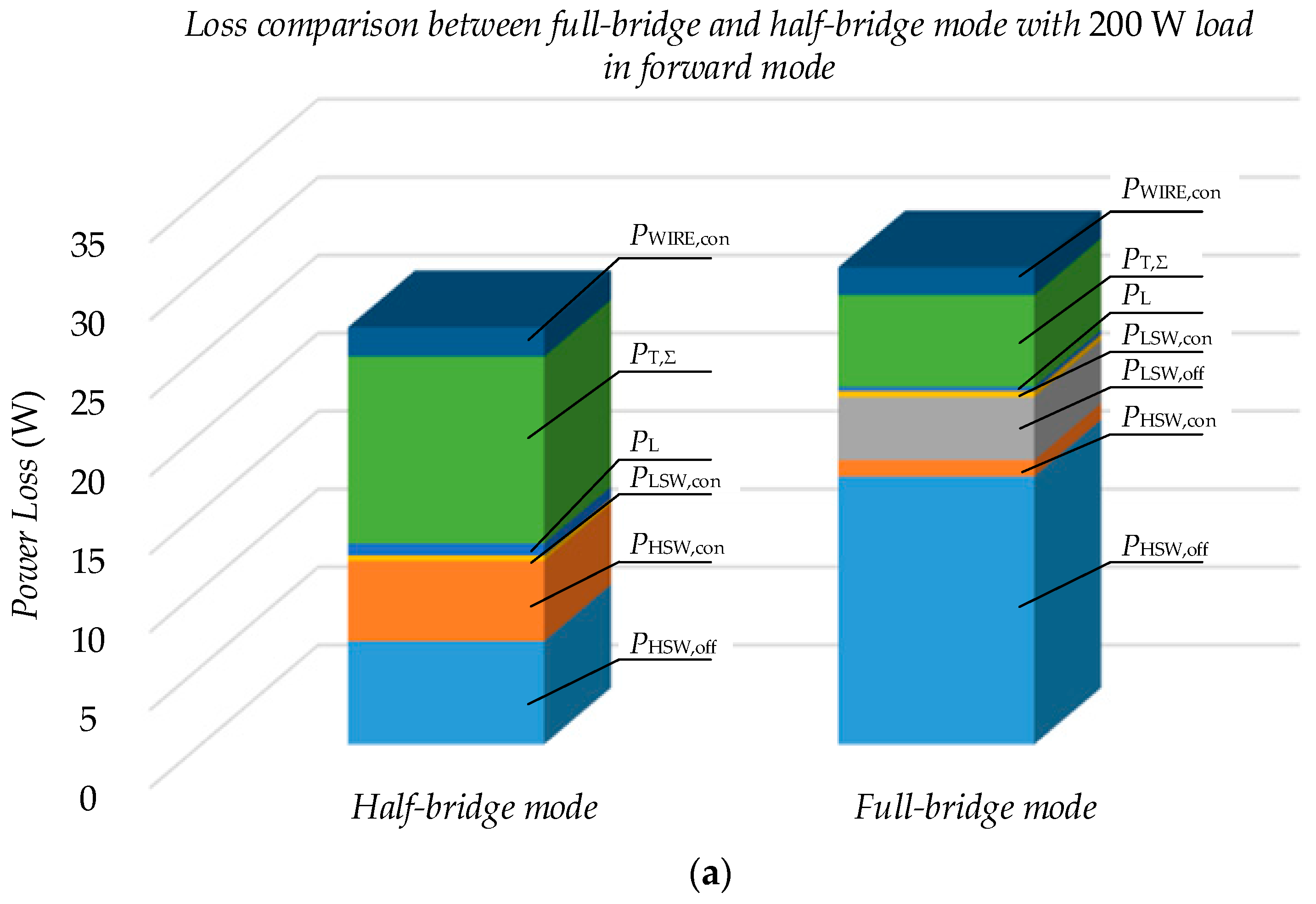

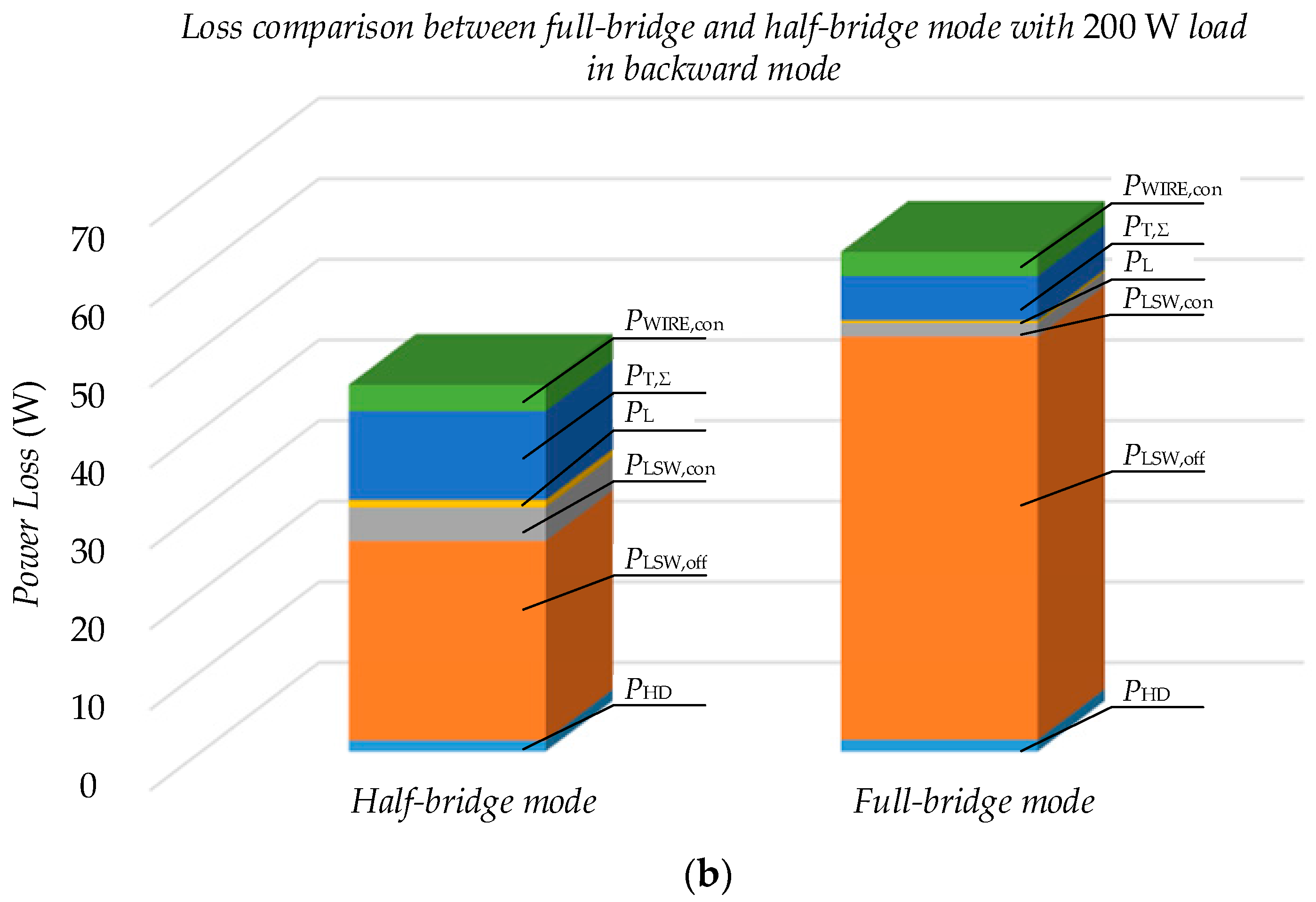

5.2. Power Loss Distribution and Comparison between Full-Bridge and Half-Bridge Configuration

- (1)

- PHSW,off and PLSW,off decrease largely. In forward mode, switches staying on on-off mode in HVS decrease from 4 to 2, and their working frequency decreases from 160 kHz to around 40 kHz. So PHSW,off decreases largely with half-bridge configuration. Also, PLSW,off decreases with less turn-off current and lower working frequency.

- (2)

- The conduction loss of all devices increases. Resonant current on HVS increases to about twice, so PHSW,con, conduction loss of resonant inductor and primary windings of transformers are amplified. However, as resonant current on LVS changes little, PLSW,con and the conduction loss of secondary windings in transformers stay the same.

- (3)

- Core loss of resonant inductor and transformers stays the same. In half-bridge LLC, working frequency fs decreases. However, Bmax, the peak flux density, increases because peak value of current increases. With Steinmetz’s equation Pcore = KfsαBmaxβVe, the core losses of resonant inductor and transformers in half-bridge configuration change little.

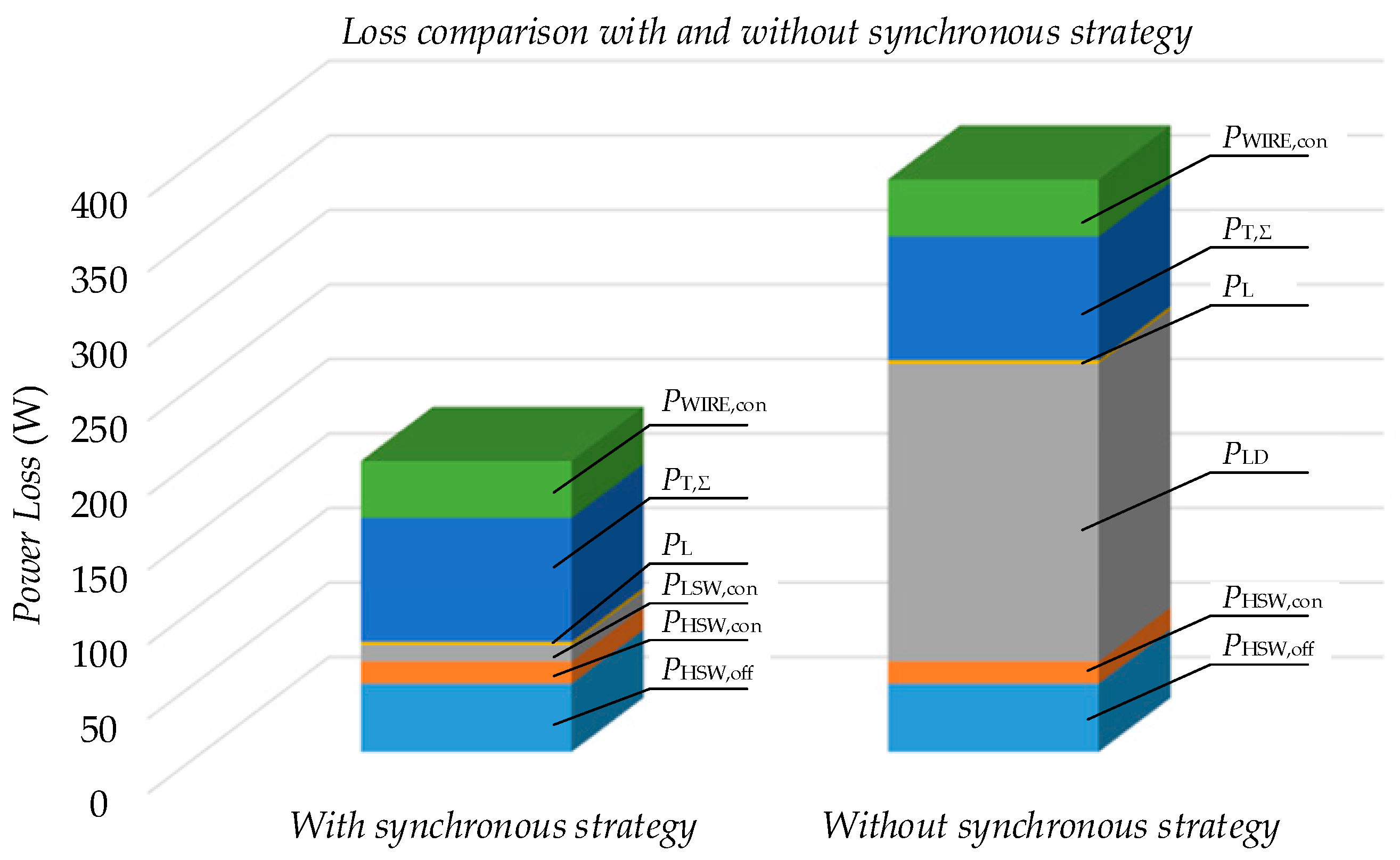

5.3. Power Loss Distribution and Comparison with and without Synchronous Strategy

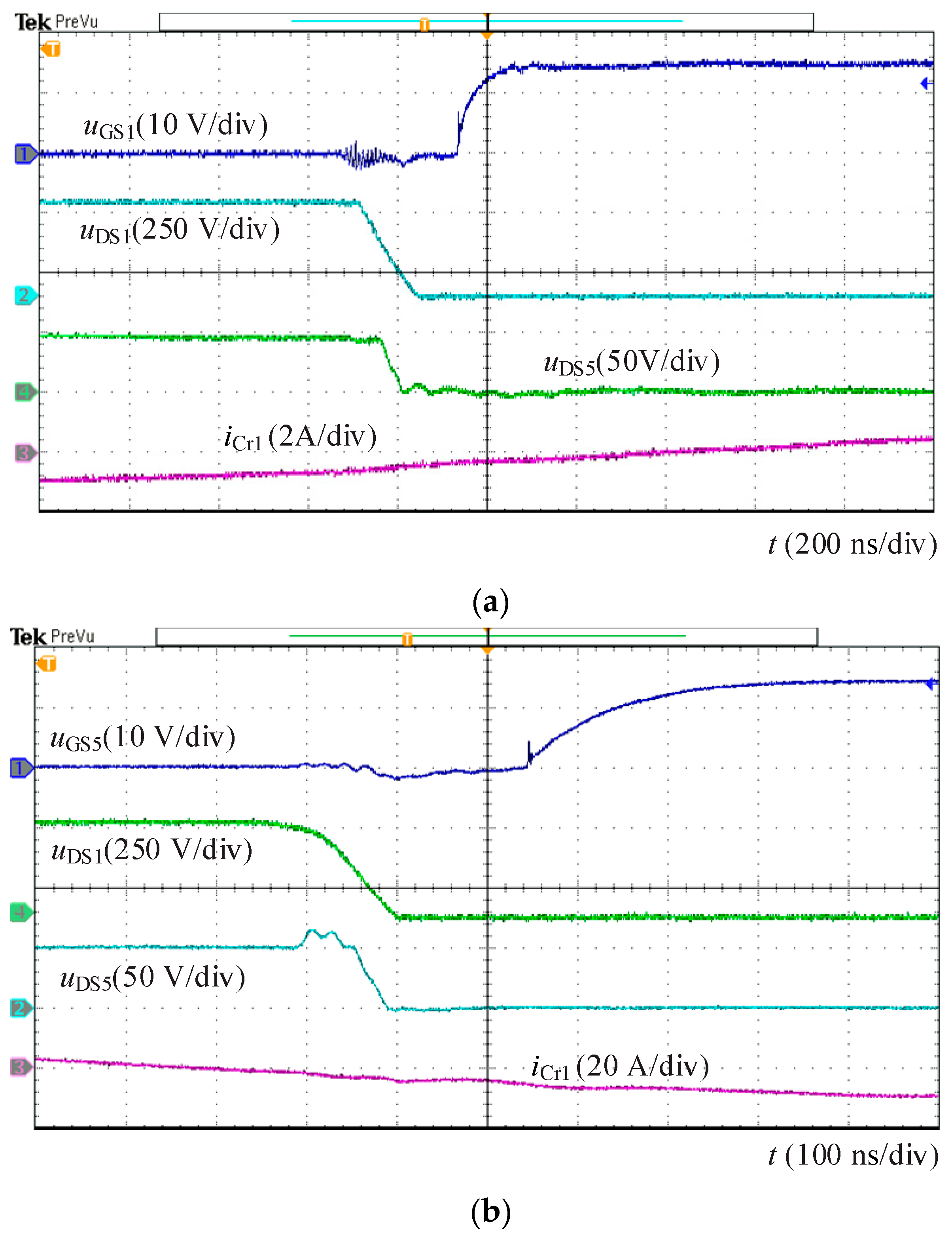

6. Experimental Results

7. Conclusions

Acknowledgments

Author Contributions

Conflicts of Interest

References

- Fang, Z.; Wang, J.; Duan, S.; Shao, J.; Hu, G. Stability Analysis and Trigger Control of LLC Resonant Converter for a Wide Operational Range. Energies 2017, 10, 1448. [Google Scholar] [CrossRef]

- Wang, C.; Li, W.; Wang, Y.; Han, F.; Meng, Z.; Li, G. An Isolated Three-Port Bidirectional DC-DC Converter with Enlarged ZVS Region for HESS Applications in DC Microgrids. Energies 2017, 10, 446. [Google Scholar] [CrossRef]

- Wang, C.; Li, W.; Wang, Y.; Han, F.; Chen, B. A High-Efficiency Isolated LCLC Multi-Resonant Three-Port Bidirectional DC-DC Converter. Energies 2017, 10, 934. [Google Scholar] [CrossRef]

- Chen, B.; Wang, P.; Wang, Y.; Li, W.; Han, F.; Zhang, S. Comparative Analysis and Optimization of Power Loss Based on the Isolated Series/Multi Resonant Three-Port Bidirectional DC-DC Converter. Energies 2017, 10, 1565. [Google Scholar] [CrossRef]

- Twiname, R.P.; Thrimawithana, D.J.; Madawala, U.K.; Baguley, C.A. A New Resonant Bidirectional DC–DC Converter Topology. IEEE Trans. Power Electron. 2014, 29, 4733–4740. [Google Scholar] [CrossRef]

- Wu, H.; Ding, S.; Sun, K.; Zhang, L.; Li, Y.; Xing, Y. Bidirectional Soft-Switching Series-Resonant Converter With Simple PWM Control and Load-Independent Voltage-Gain Characteristics for Energy Storage System in DC Microgrids. IEEE Trans. Power Electron. 2013, 28, 995–1007. [Google Scholar] [CrossRef]

- Park, J.; Choi, S. Design and Control of a Bidirectional Resonant DC–DC Converter for Automotive Engine/Battery Hybrid Power Generators. IEEE Trans. Power Electron. 2014, 29, 3748–3757. [Google Scholar] [CrossRef]

- Shen, Y.; Wang, H.; Al-Durra, A.; Qin, Z.; Blaabjerg, F. A Fixed-Frequency Bidirectional Resonant DC-DC Converter Suitable for Wide Voltage Gain Range. IEEE Trans. Power Electron. 2017, 99, 1–19. [Google Scholar]

- Hu, S.; Deng, J.; Mi, C.; Zhang, M. Optimal design of line level control resonant converters in plug-in hybrid electric vehicle battery chargers. IET Electron. Syst. Transp. 2013, 4, 21–28. [Google Scholar] [CrossRef]

- Tan, X.; Ruan, X. Equivalence relations of resonant tanks: A new perspective for selection and design of resonant converters. IEEE Trans. Ind. Electron. 2016, 63, 2111–2123. [Google Scholar] [CrossRef]

- Corradini, L.; Seltzer, D.; Bloomquist, D.; Zane, R.; Maksimović, D.; Jacobson, B. Minimum Current Operation of Bidirectional Dual-Bridge Series Resonant DC/DC Converters. IEEE Trans. Power Electron. 2012, 27, 3266–3276. [Google Scholar] [CrossRef]

- Ibanez, F.; Echeverria, J.; Vadillo, J.; Fontan, L. State-Plane Analysis of Anomalous Step-Up Behavior in Series-Resonant Converters. IEEE J. Emerg. Sel. Top. Power Electron. 2016, 4, 1026–1035. [Google Scholar] [CrossRef]

- Li, X.; Bhat, A. Analysis and Design of High-Frequency Isolated Dual-Bridge Series Resonant DC/DC Converter. IEEE Trans. Power Electron. 2010, 25, 850–862. [Google Scholar]

- Ibanez, F.; Echeverria, J.; Fontan, L. Novel technique for bidirectional series-resonant DC/DC converter in discontinuous mode. IET Power Electron. 2013, 6, 1019–1028. [Google Scholar] [CrossRef]

- Ibanez, F.; Echeverria, J.; Vadillo, J.; Fontan, L. Frequency response analysis for bidirectional series resonant DC/DC converter in discontinuous mode. IET Power Electron. 2014, 7, 2374–2386. [Google Scholar] [CrossRef]

- Ibanez, F.; Echeverria, J.; Vadillo, J.; Fontan, L. A Step-Up Bidirectional Series Resonant DC/DC Converter Using a Continuous Current Mode. IEEE Trans. Power Electron. 2015, 30, 1393–1402. [Google Scholar] [CrossRef]

- Jiang, T.; Zhang, J.; Wu, X.; Sheng, K.; Wang, Y. A Bidirectional Three-Level LLC Resonant Converter with PWAM Control. IEEE Trans. Power Electron. 2016, 31, 2213–2225. [Google Scholar] [CrossRef]

- Jiang, T.; Zhang, J.; Wu, X.; Sheng, K.; Wang, Y. A Bidirectional LLC Resonant Converter with Automatic Forward and Backward Mode Transition. IEEE Trans. Power Electron. 2015, 30, 757–770. [Google Scholar] [CrossRef]

- Jung, J.; Kim, H.; Ryu, M.; Baek, J. Design Methodology of Bidirectional CLLC Resonant Converter for High-Frequency Isolation of DC Distribution Systems. IEEE Trans. Power Electron. 2013, 28, 1741–1755. [Google Scholar] [CrossRef]

- Zahid, Z.; Dalala, Z.; Chen, R.; Chen, B.; Lai, J. Design of Bidirectional DC-DC Resonant Converter for Vehicle-to-Grid (V2G) Applications. IEEE Trans. Transp. Electr. 2015, 1, 232–244. [Google Scholar] [CrossRef]

- He, P.; Khaligh, A. Comprehensive Analyses and Comparison of 1 kW Isolated DC-DC Converters for Bidirectional EV Charging Systems. IEEE Trans. Transp. Electr. 2017, 3, 147–156. [Google Scholar] [CrossRef]

- Lee, B.H.; Kim, M.Y.; Kim, C.E.; Park, K.-B.; Moon, G.W. Analysis of LLC resonant converter considering effects of parasitic components. In Proceedings of the INTELEC 31st International Telecommunications Energy Conference, Incheon, Korea, 18–22 October 2009; pp. 1–6. [Google Scholar]

- Zhao, S.; Xu, J.; Trescases, O. Burst-Mode Resonant LLC Converter for an LED Luminaire With Integrated Visible Light Communication for Smart Buildings. IEEE Trans. Power Electron. 2014, 9, 4392–4402. [Google Scholar] [CrossRef]

- Musavi, F.; Craciun, M.; Gautam, D.; Eberle, W. Control Strategies for Wide Output Voltage Range LLC Resonant DC–DC Converters in Battery Chargers. IEEE Trans. Veh. Technol. 2014, 63, 1117–1125. [Google Scholar] [CrossRef]

- Cai, G.; Liu, D.; Liu, C.; Li, W.; Sun, J. A High-Frequency Isolation (HFI) Charging DC Port Combining a Front-End Three-Level Converter with a Back-End LLC Resonant Converter. Energies 2017, 10, 1462. [Google Scholar]

- Kim, J.; Kim, C.; Kim, J.; Lee, J.; Moon, G. Analysis on Load-Adaptive Phase-Shift Control for High Efficiency Full-Bridge LLC Resonant Converter Under Light-Load Conditions. IEEE Trans. Power Electron. 2016, 31, 4942–4955. [Google Scholar]

- Pan, H.; He, C.; Ajmal, F.; Chen, H.; Chen, G. Pulse-width modulation control strategy for high efficiency LLC resonant converter with light load applications. IET Power Electron. 2014, 7, 2887–2894. [Google Scholar] [CrossRef]

- Wang, H.; Li, Z. A PWM LLC Type Resonant Converter Adapted to Wide Output Range in PEV Charging Applications. IEEE Trans. Power Electron. 2017, 1, 1–10. [Google Scholar] [CrossRef]

- Kim, J.H.; Kim, C.E.; Kim, J.K.; Moon, G.W. Analysis for LLC resonant converter considering parasitic components at very light load condition. In Proceedings of the 8th International Conference on Power Electronics, Jeju, Korea, 30 May–3 June 2011; pp. 1863–1868. [Google Scholar]

- Yeon, C.; Kim, J.; Park, M.; Lee, L.; Moon, G. Improving the Light-Load Regulation Capability of LLC Series Resonant Converter Using Impedance Analysis. IEEE Trans. Power Electron. 2017, 32, 7056–7067. [Google Scholar] [CrossRef]

- Tsai, C.; Shen, C.; Su, J. A Power Supply System with ZVS and Current-Doubler Features for Hybrid Renewable Energy Conversion. Energies 2013, 6, 4859–4878. [Google Scholar] [CrossRef]

- Xu, W.; Chan, N.; Or, S.; Ho, S.; Chan, K. A New Control Method for a Bi-Directional Phase-Shift-Controlled DC-DC Converter with an Extended Load Range. Energies 2017, 10, 1532. [Google Scholar] [CrossRef]

- Joo, D.; Byun, J.; Lee, B.; Kim, J. Adaptive delay control for synchronous rectification phase-shifted full bridge converter with GaN HEMT. IEEE Trans. Power Electron. 2017, 53, 1541–1542. [Google Scholar] [CrossRef]

- Yang, H.; Liao, J.; Cheng, X. Zero-voltage-transition auxiliary circuit with dual resonant tank for DC–DC converters with synchronous rectification. IET Trans. Power Electron. 2017, 6, 1157–1164. [Google Scholar] [CrossRef]

- Fu, D.; Liu, Y.; Lee, F.; Xu, M. A Novel Driving Scheme for Synchronous Rectifiers in LLC Resonant Converters. IEEE Trans. Power Electron. 2009, 24, 1321–1329. [Google Scholar] [CrossRef]

- Zhang, J.; Wang, J.; Zhang, G.; Qian, Z. A Hybrid Driving Scheme for Full-Bridge Synchronous Rectifier in LLC Resonant Converter. IEEE Trans. Power Electron. 2012, 27, 4549–4561. [Google Scholar] [CrossRef]

- Duan, C.; Bai, H.; Guo, W.; Nie, Z. Design of a 2.5-kW 400/12-V High-Efficiency DC/DC Converter Using a Novel Synchronous Rectification Control for Electric Vehicles. IEEE Trans. Transp. Electr. 2015, 1, 106–114. [Google Scholar] [CrossRef]

| Component | Model/Value |

|---|---|

| Rated power | 5 kW |

| HVS DC voltage | 380–420 V |

| LVS DC voltage | 42–58 V |

| S1, S2, S3, S4 | C3M0065090D |

| S5, S6, S7, S8 | 4 IPB036N12N3G in parallel |

| D1, D2, D3, D4 | C3D30065D |

| Lm1 | 140 μH |

| n1 | 11:1 |

| Lm2 | 875 μH |

| n2 | 20:1 |

| Lr | 57 μH |

| Cr1 | 251 nF |

| Cr2 | 10 μF |

| tdt_F | 200 ns |

| tdt_B | 200 ns |

| Type | Half-Bridge | Full-Bridge |

|---|---|---|

| Forward | 87.3% | 83.0% |

| Backward | 82.1% | 70.9% |

© 2018 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).

Share and Cite

Zhang, S.-h.; Wang, Y.-f.; Chen, B.; Han, F.-q.; Wang, Q.-c. Studies on a Hybrid Full-Bridge/Half-Bridge Bidirectional CLTC Multi-Resonant DC-DC Converter with a Digital Synchronous Rectification Strategy. Energies 2018, 11, 227. https://doi.org/10.3390/en11010227

Zhang S-h, Wang Y-f, Chen B, Han F-q, Wang Q-c. Studies on a Hybrid Full-Bridge/Half-Bridge Bidirectional CLTC Multi-Resonant DC-DC Converter with a Digital Synchronous Rectification Strategy. Energies. 2018; 11(1):227. https://doi.org/10.3390/en11010227

Chicago/Turabian StyleZhang, Shu-huai, Yi-feng Wang, Bo Chen, Fu-qiang Han, and Qing-cui Wang. 2018. "Studies on a Hybrid Full-Bridge/Half-Bridge Bidirectional CLTC Multi-Resonant DC-DC Converter with a Digital Synchronous Rectification Strategy" Energies 11, no. 1: 227. https://doi.org/10.3390/en11010227