A Novel Real-Time Processing Wideband Waveform Generator of Airborne Synthetic Aperture Radar

Abstract

:1. Introduction

2. Materials and Methods

2.1. Introduction of Common LFM Generation Methods

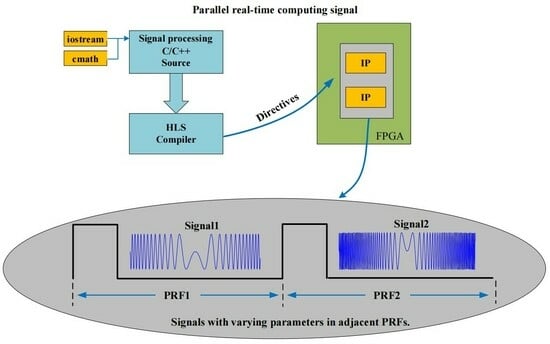

2.2. Improved Parallel Real-Time LFM Generation

2.3. Improved Parallel Polynomial Calculation Algorithm

2.4. Improved Parallel Real-Time LFM Signal Generation Method

3. Results

3.1. Results of the LFM Signal Generation

3.2. Results of Phase Compensation

3.3. Results of Signal with Compensation

3.4. Comparison of Different Methods

3.4.1. Comparison of Indicators

3.4.2. Comparison of Resource Utilization

4. Discussion

5. Conclusions

Author Contributions

Funding

Data Availability Statement

Acknowledgments

Conflicts of Interest

References

- Qiu, J.; Zhang, Z.; Wang, R.; Wang, P.; Zhang, H.; Du, J.; Wang, W.; Chen, Z.; Zhou, Y.; Jia, H.; et al. A Novel Weight Generator in Real-Time Processing Architecture of DBF-SAR. IEEE Trans. Geosci. Remote Sens. 2022, 60, 5204915. [Google Scholar] [CrossRef]

- Ding, Z.; Xiao, F.; Xie, Y.; Yu, W.; Yang, Z.; Chen, L.; Long, T. A Modified Fixed-Point Chirp Scaling Algorithm Based on Updating Phase Factors Regionally for Spaceborne SAR Real-Time Imaging. IEEE Trans. Geosci. Remote Sens. 2018, 56, 7436–7451. [Google Scholar] [CrossRef]

- Li, H.; Suo, Z.; Zheng, C.; Li, Z.; Zhang, Q. Improved Back-Projection Algorithm on Small Time Bandwidth Product SAR Imaging. IEEE Geosci. Remote Sens. Lett. 2022, 19, 4001005. [Google Scholar] [CrossRef]

- Li, B.; Chen, D.; Cao, H.; Wang, J.; Li, H.; Fu, T.; Zhang, S.; Zhao, L. Estimating the Observation Area of a Stripmap SAR via an ISAR Image Sequence. Remote Sens. 2023, 15, 5484. [Google Scholar] [CrossRef]

- Shen, W.; Jia, Y.; Wang, Y.; Lin, Y.; Li, Y.; Bai, Z.; Jiang, W. Spaceborne SAR Time-Series Images Change Detection Based on SAR-SIFT-Logarithm Background Subtraction. Remote Sens. 2023, 15, 5533. [Google Scholar] [CrossRef]

- Yang, T.; Xu, Q.; Meng, F.; Zhang, S. Distributed Real-Time Image Processing of Formation Flying SAR Based on Embedded GPUs. IEEE J. Sel. Top. Appl. Earth Obs. Remote Sens. 2022, 15, 6495–6505. [Google Scholar] [CrossRef]

- Mu, H.; Zhang, Y.; Jiang, Y.; Ding, C. CV-GMTINet: GMTI Using a Deep Complex-Valued Convolutional Neural Network for Multichannel SAR-GMTI System. IEEE Trans. Geosci. Remote Sens. 2022, 60, 5201115. [Google Scholar] [CrossRef]

- Tan, X.; Zhu, J. Window effects on the performance of matched filtering for linear frequency modulation signal. In Proceedings of the 2014 7th International Congress on Image and Signal Processing, Dalian, China, 14–16 October 2014; pp. 820–825. [Google Scholar]

- Jin, G.; Liu, K.; Deng, Y.; Sha, Y.; Wang, R.; Liu, D.; Wang, W.; Long, Y.; Zhang, Y. Nonlinear Frequency Modulation Signal Generator in LT-1. IEEE Geosci. Remote Sens. Lett. 2019, 16, 1570–1574. [Google Scholar] [CrossRef]

- Liang, Y.; Dang, Y.; Li, G.; Wu, J.; Xing, M. A Two-Step Processing Method for Diving-Mode Squint SAR Imaging With Subaperture Data. IEEE Trans. Geosci. Remote Sens. 2020, 58, 811–825. [Google Scholar] [CrossRef]

- Pallavi, N.; Anjaneyulu, P.; Reddy, P.B.; Mahendra, V.; Karthik, R. Design and implementation of linear frequency modulated waveform using DDS and FPGA. In Proceedings of the 2017 International Conference of Electronics, Communication and Aerospace Technology (ICECA), Coimbatore, India, 20–22 April 2017; pp. 237–241. [Google Scholar]

- Grabowski, A. SDR-based LFM signal generator for radar/SAR systems. In Proceedings of the 2016 17th International Radar Symposium (IRS), Krakow, Poland, 10–12 May 2016. [Google Scholar]

- Jiang, T.; Li, B.; Sun, B.; Ma, X. Research of Digital Predistortion for Ultra Wideband LFM signal. In Proceedings of the 2022 3rd International Conference on Geology, Mapping and Remote Sensing (ICGMRS), Zhoushan, China, 22–24 April 2022; pp. 154–157. [Google Scholar]

- Sheng, M.; Liu, H.; Wang, J.; Jiang, H. Direct digital generation of ultra-wideband LFM signal and its compensation technology. In Proceedings of the IET International Radar Conference 2013, Xi’an, China, 14–16 April 2013; pp. 1–4. [Google Scholar]

- Li, W.; Wang, H.; Wu, S.; Zeng, Z.; Chen, X.; Fu, Y. Research on Generation and Pre-distortion of high-frequency and wide-band signal based on FPGA/DA. In Proceedings of the 2021 2nd China International SAR Symposium (CISS), Shanghai, China, 3–5 November 2021; pp. 1–4. [Google Scholar]

- Kim, K.-R.; Kim, J.-H. Wideband Waveform Generation Using MDDS and Phase Compensation for X-Band SAR. Remote Sens. 2020, 12, 1431. [Google Scholar] [CrossRef]

- Shahin, K.; Artin, K.; Mobin, J. Novel continuous phase DDS model for linear Chirp Signal Simulation in Pulse Compression Radar. In Proceedings of the 2021 29th Iranian Conference on Electrical Engineering (ICEE), Tehran, Iran, 18–20 May 2021; pp. 798–804. [Google Scholar]

- Chen, D.; Wei, T.; Li, G.; Zeng, J.; Feng, J.; Yang, X.; Yu, Z. A novel linear frequency modulation signal generator in real-time processing of airborne synthetic aperture radar. J. Eng. 2023, 2023, e12236. [Google Scholar] [CrossRef]

- Tariq, O.B.; Shan, J.; Floros, G.; Sotiriou, C.P.; Casu, M.R.; Lazarescu, M.T.; Lavagno, L. High-Level Annotation of Routing Congestion for Xilinx Vivado HLS Designs. IEEE Access 2021, 9, 54286–54297. [Google Scholar] [CrossRef]

- Wu, N.; Xie, Y.; Hao, C. IronMan-Pro: Multiobjective Design Space Exploration in HLS via Reinforcement Learning and Graph Neural Network-Based Modeling. IEEE Trans. Comput.-Aided Des. Integr. Circuits Syst. 2023, 42, 900–913. [Google Scholar] [CrossRef]

- Zhao, J.; Feng, L.; Sinha, S.; Zhang, W.; Liang, Y.; He, B. Performance Modeling and Directives Optimization for High-Level Synthesis on FPGA. IEEE Trans. Comput.-Aided Des. Integr. Circuits Syst. 2020, 39, 1428–1441. [Google Scholar] [CrossRef]

- Kim, S.-Y.; Myung, N.-H. Wideband Linear Frequency Modulated Waveform Compensation Using System Predistortion and Phase Coefficients Extraction Method. IEEE Microw. Wirel. Compon. Lett. 2007, 17, 808–810. [Google Scholar]

- Zhao, Y.; Yang, J.; Zhang, Y.; Lin, Q.; Chen, Z. Implementation of a multi-waveband, high-precision, wideband waveform generator based on DDWS for antenna channel characteristics test. In Proceedings of the 2016 Progress in Electromagnetic Research Symposium (PIERS), Shanghai, China, 8 August–11 September 2016; pp. 444–449. [Google Scholar]

- Mohammadi Shirkolaei, M.; Ghalibafan, J. Magnetically scannable slotted waveguide antenna based on the ferrite with gain enhancement. Waves Random Complex Media 2021, 31, 1–11. [Google Scholar] [CrossRef]

- Ni, C.; Tan, H.; Liu, Q. Channel pre-distortion compensation techniques in SAR echo simulator. In Proceedings of the 2016 11th International Symposium on Antennas, Propagation and EM Theory (ISAPE), Guilin, China, 18–21 October 2016; pp. 674–677. [Google Scholar]

- Wang, W.; Wang, R.; Deng, Y.; Zhang, Z.; Wu, X.; Xu, Z. Demonstration of NLFM Waveforms with Experiments and Doppler Shift Compensation for SAR Application. IEEE Geosci. Remote Sens. Lett. 2016, 13, 1999–2003. [Google Scholar] [CrossRef]

- Kim, K.; Kim, J.-H. Polynomial Regression Predistortion for Phase Error Calibration in X-Band SAR. IEEE Geosci. Remote Sens. Lett. 2022, 19, 4002705. [Google Scholar] [CrossRef]

- Song, Y.; Wang, Y.; Xie, J.; Yang, Y.; Tian, B.; Xu, S. Ultra-Low Sidelobe Waveforms Design for LPI Radar Based on Joint Complementary Phase-Coding and Optimized Discrete Frequency-Coding. Remote Sens. 2022, 14, 2592. [Google Scholar] [CrossRef]

- Fan, Y.; Hu, X.; Xu, G. A New CCBFM/P4 RF Stealth Signal Waveform Design. In Proceedings of the 2020 IEEE International Conference on Information Technology, Big Data and Artificial Intelligence (ICIBA), Chongqing, China, 6–8 November 2020; pp. 254–258. [Google Scholar]

- Wei, T.; Wang, W.; Zhang, Y.; Wang, R. A Novel Nonlinear Frequency Modulation Waveform With Low Sidelobes Applied to Synthetic Aperture Radar. IEEE Geosci. Remote Sens. Lett. 2022, 19, 4515405. [Google Scholar] [CrossRef]

| Parameter | Value |

|---|---|

| DAC sampling frequency | 2 GHz |

| Bandwidth | 440 MHz |

| Time width | 120 µs |

| Carrier frequency | 9.6 GHz |

| Pulse repetition frequency (PRF) | 600 Hz |

| ADC sampling frequency | 2000 MHz |

| Sampling points | 81,920 |

| Method | Storage Method [15] | Serial Calculation Method [18] | Parallel Calculation Method |

|---|---|---|---|

| PSLR of ideal signal (dB) | −13.2592 | −13.2592 | −13.2592 |

| ISLR of ideal signal (dB) | −10.1038 | −10.1038 | −10.1038 |

| PSLR of signal without compensation (dB) | −10.5589 | −10.5613 | −10.6285 |

| ISLR of signal without compensation (dB) | −9.0688 | −9.0698 | −9.0096 |

| PSLR of signal with compensation (dB) | −13.0051 | −13.0138 | −13.0113 |

| ISLR of signal with compensation (dB) | −10.747 | −10.748 | −10.746 |

| Method | Storage Method | Serial Calculation Method | Parallel Calculation Method |

|---|---|---|---|

| The dedicated hardware storage resources (KB) | 937.5 | 0 | 0 |

| The dedicated BRAM cache in FPGA | 14.4% | 14.4% | 0.4% |

| The time necessary to prepare the waveform for processing | 38.5 ms | 2.5 ms | 1.7 µs |

| The utilization of DSP resources in FPGA | 0 | 33% | 39% |

| The utilization of LUT resources in FPGA | 9% | 23% | 26% |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2024 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Chen, D.; Wei, T.; Li, G.; Feng, J.; Zeng, J.; Yang, X.; Yu, Z. A Novel Real-Time Processing Wideband Waveform Generator of Airborne Synthetic Aperture Radar. Remote Sens. 2024, 16, 496. https://doi.org/10.3390/rs16030496

Chen D, Wei T, Li G, Feng J, Zeng J, Yang X, Yu Z. A Novel Real-Time Processing Wideband Waveform Generator of Airborne Synthetic Aperture Radar. Remote Sensing. 2024; 16(3):496. https://doi.org/10.3390/rs16030496

Chicago/Turabian StyleChen, Dongxu, Tingcun Wei, Gaoang Li, Jie Feng, Jialong Zeng, Xudong Yang, and Zhongjun Yu. 2024. "A Novel Real-Time Processing Wideband Waveform Generator of Airborne Synthetic Aperture Radar" Remote Sensing 16, no. 3: 496. https://doi.org/10.3390/rs16030496