Cu-Based Thermocompression Bonding and Cu/Dielectric Hybrid Bonding for Three-Dimensional Integrated Circuits (3D ICs) Application

Abstract

:1. Introduction

2. Low-Temperature Cu-Cu Bonding Schemes

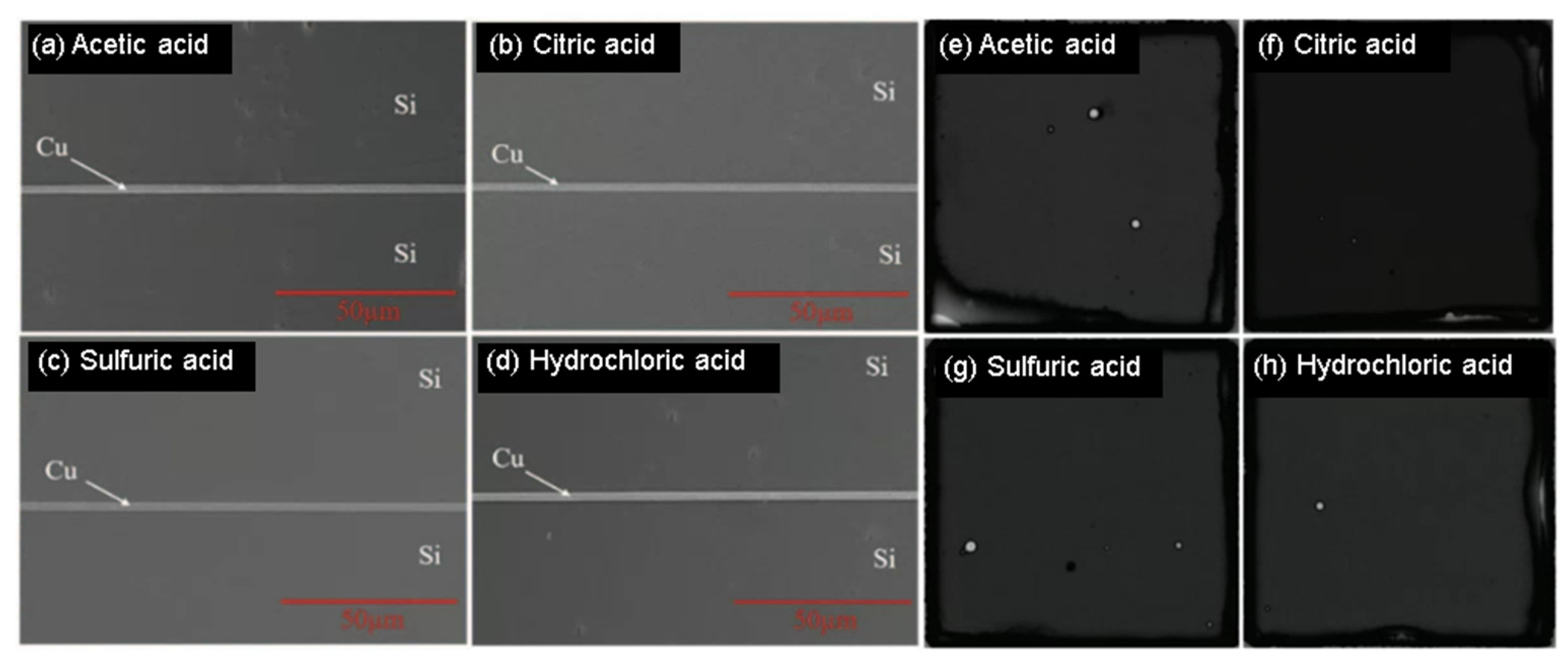

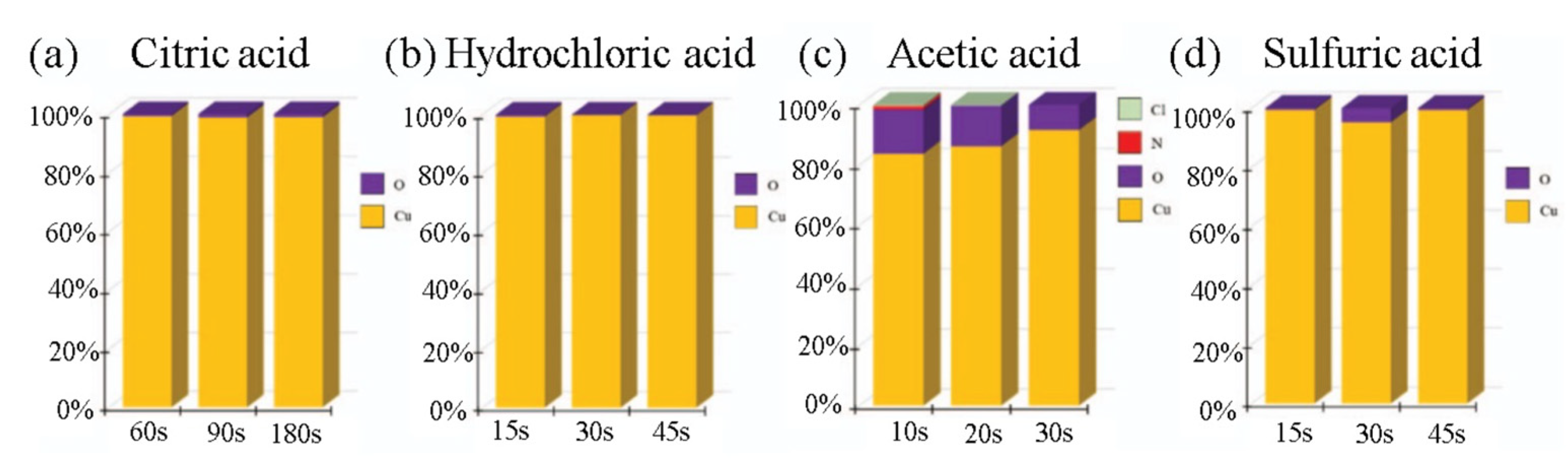

2.1. Surface Pretreatment for Cu-Cu Bonding

2.2. Surface Activation Bonding Scheme

2.3. Structure Modification with Passivation Scheme

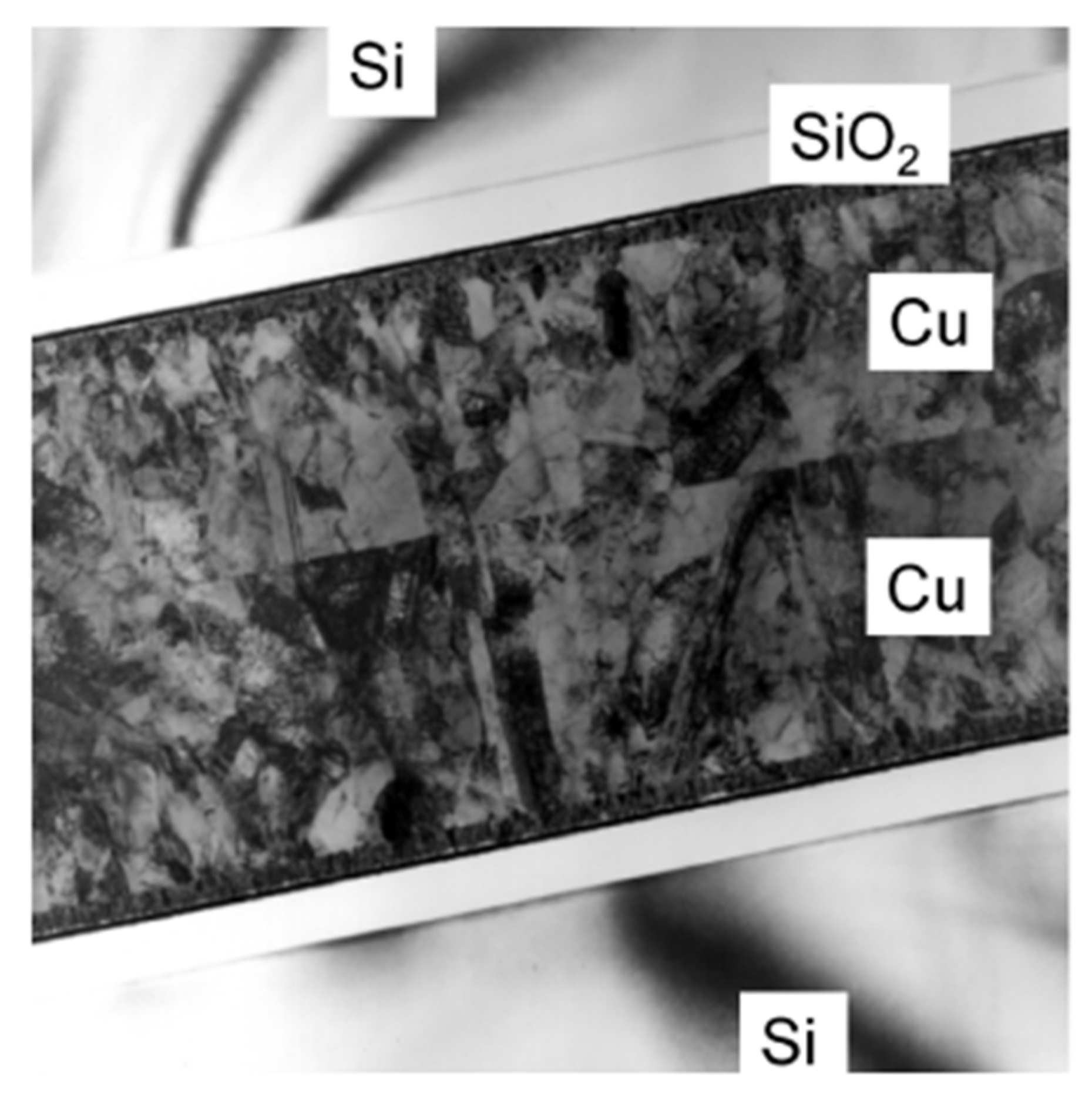

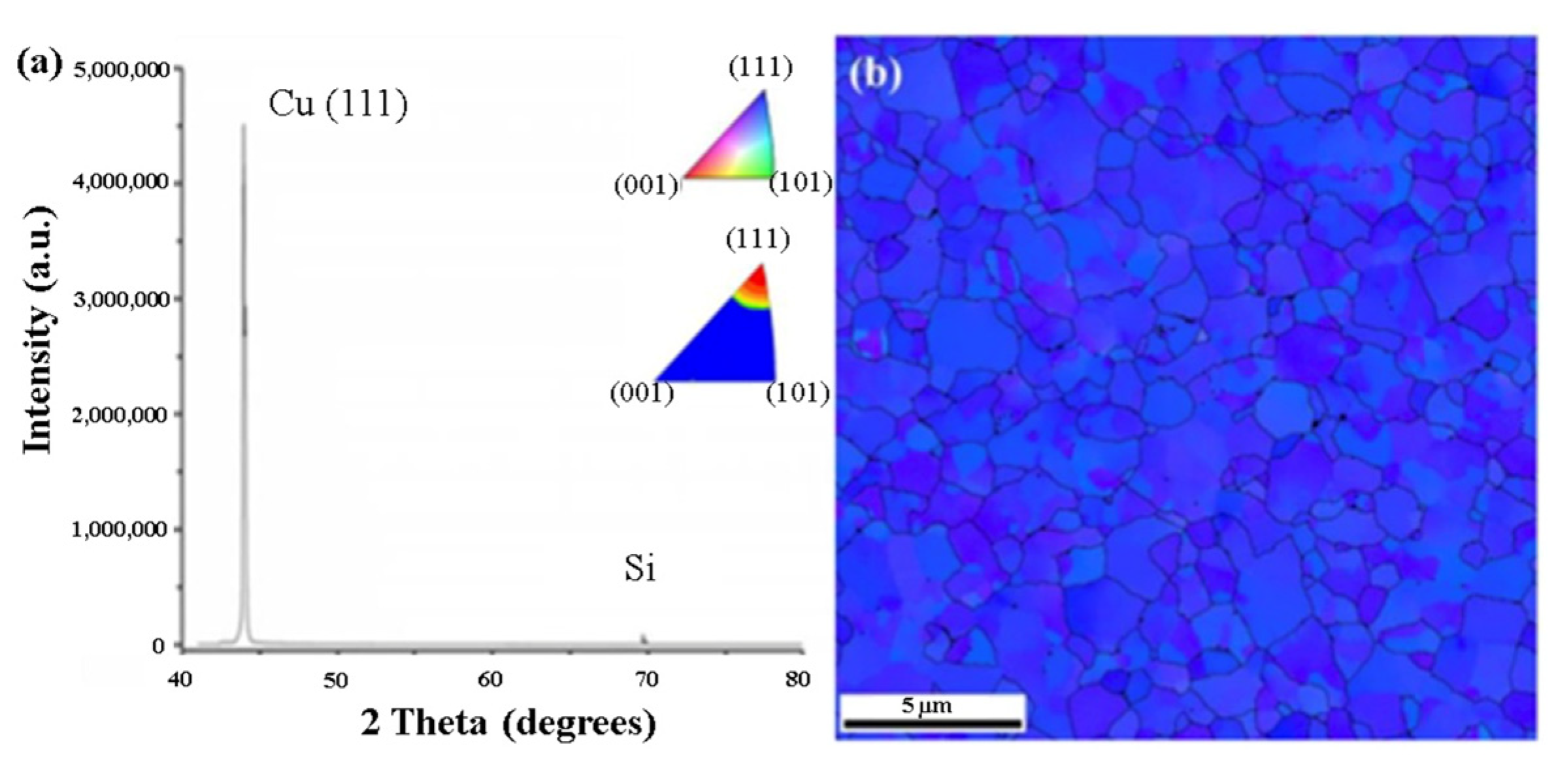

2.4. Orientation Control with (111) Surface of Nanotwinned-Cu

3. Low-Temperature Hybrid Bonding Schemes

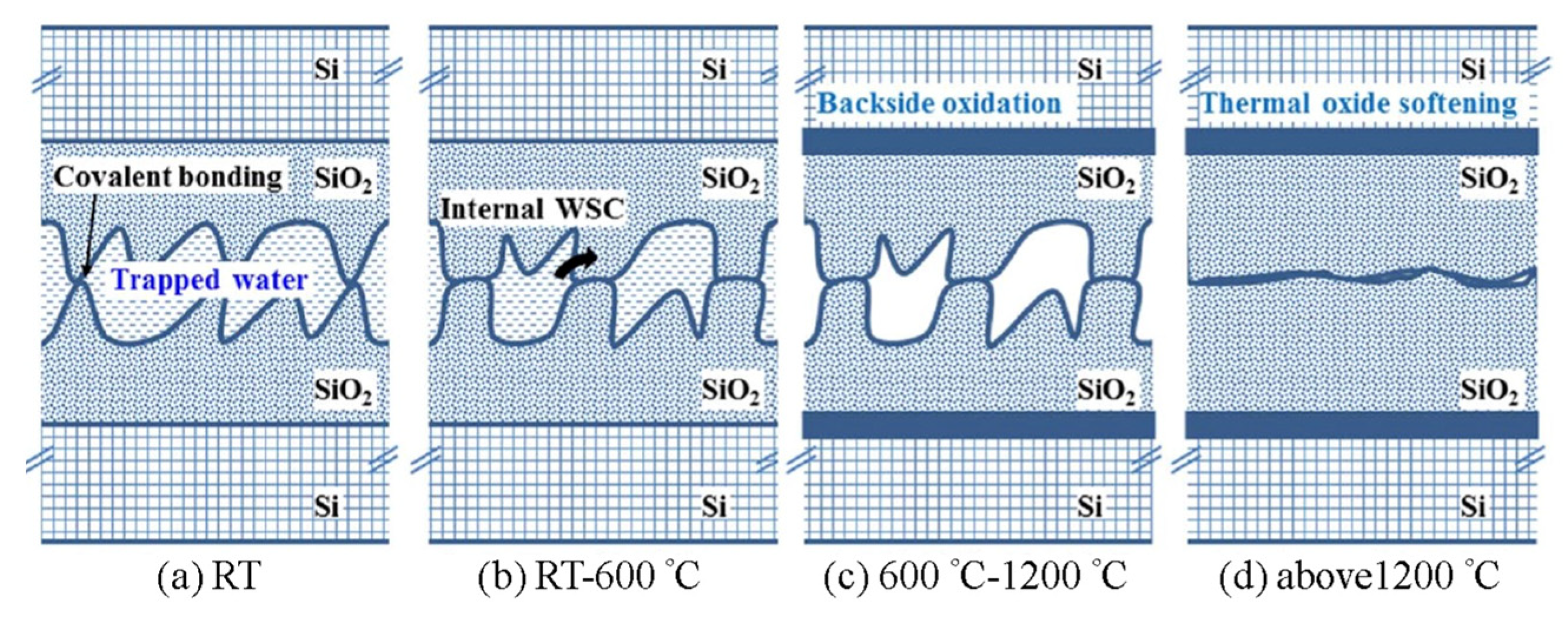

3.1. Cu/SiO2 Hybrid Bonding

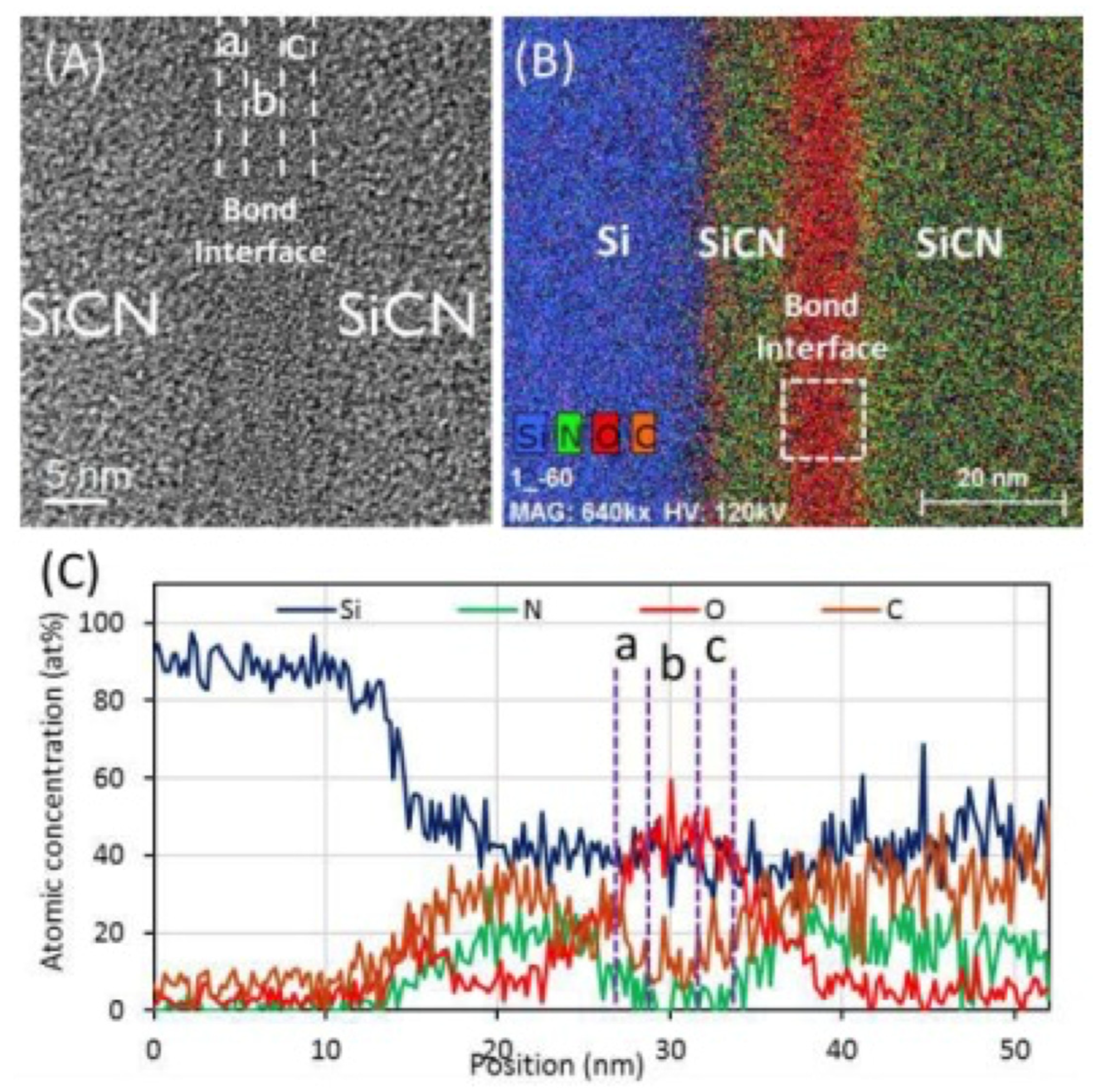

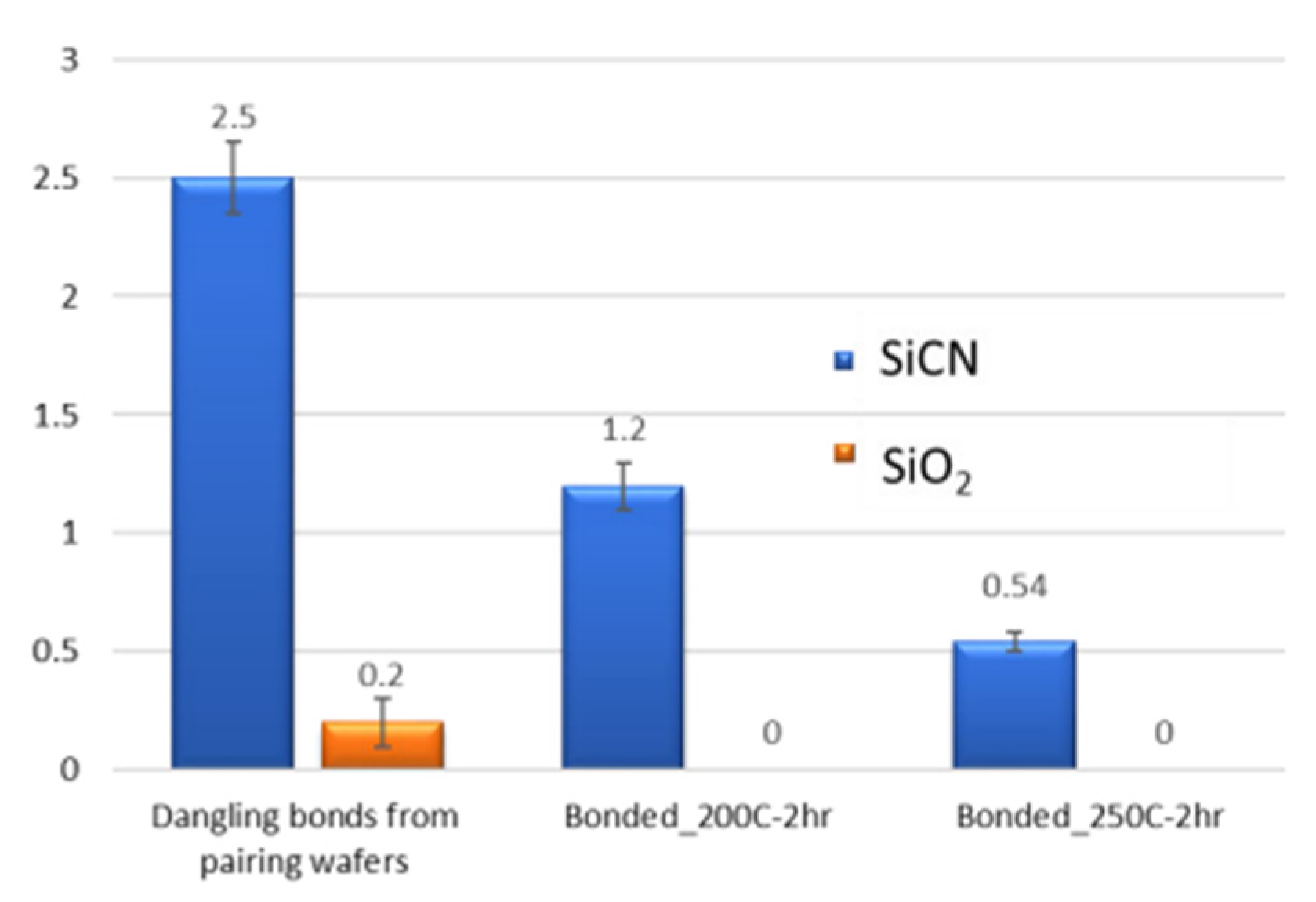

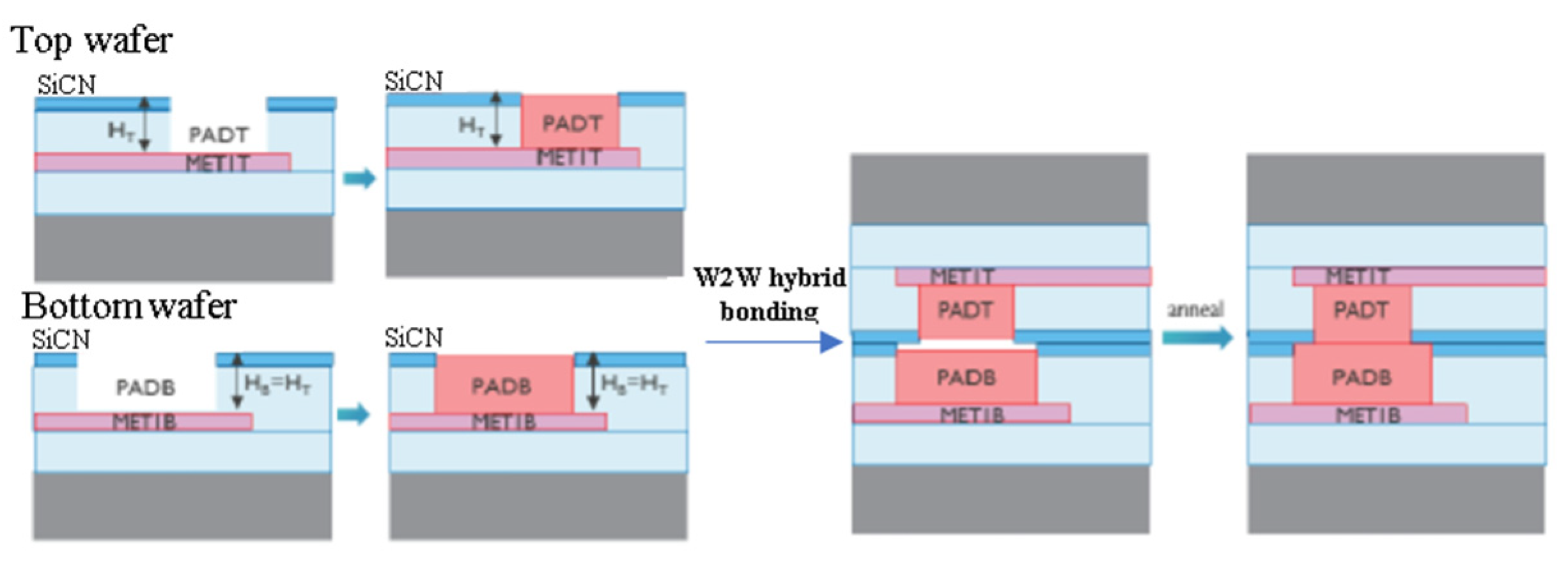

3.2. Cu/SiCN Hybrid Bonding

3.3. Cu/Polymer Hybrid Bonding

| Cu/SiO2 | Cu/SiCN | Cu/Polyimide | Reference | |

|---|---|---|---|---|

| Surface flatness requirement | Surface flatness requirement | Surface flatness requirement | Surface flatness requirement | [53,54] |

| CMP process | Needed | Needed | Optional | [58,63] |

| Dielectric constant | 3.9–4.5 | 4.8–4.9 | 2.8–3.2 | [65,66] |

| CTE (ppm/K) | 0.55–0.75 | 3.0–4.0 | Usually higher than 50 | [67,68] |

4. Conclusions

Author Contributions

Funding

Data Availability Statement

Acknowledgments

Conflicts of Interest

References

- Tummala, R.R. Moore’s Law for Packaging to Replace Moore’s Law for ICS. In Proceedings of the 2019 Pan Pacific Microelectronics Symposium (Pan Pacific), Kauai, HI, USA, 11–14 February 2019; pp. 1–6. [Google Scholar] [CrossRef]

- Kim, J.; Seo, S.-K.; Kim, H.; Kim, Y.; Jo, C.; Kim, D.-W. A Study on Bonding Pad Structure and Layout for Fine Pitch Hybrid Bonding. In Proceedings of the 2022 IEEE 72nd Electronic Components and Technology Conference (ECTC), San Diego, CA, USA, 31 May–3 June 2022; pp. 712–715. [Google Scholar] [CrossRef]

- Fisher, D.W.; Knickerbocker, S.; Smith, D.; Katz, R.; Garant, J.; Lubguban, J.; Soler, V.; Robson, N. Face to Face Hybrid Wafer Bonding for Fine Pitch Applications. In Proceedings of the 2020 IEEE 70th Electronic Components and Technology Conference (ECTC), Orlando, FL, USA, 3–30 June 2020; pp. 595–600. [Google Scholar] [CrossRef]

- Prasad, D.; Pan, C.; Naeemi, A. Impact of Interconnect Variability on Circuit Performance in Advanced Technology Nodes. In Proceedings of the 2016 17th International Symposium on Quality Electronic Design (ISQED), Santa Clara, CA, USA, 15–16 March 2016; pp. 398–404. [Google Scholar] [CrossRef]

- Prasad, D.; Ceyhan, A.; Pan, C.; Naeemi, A. Adapting Interconnect Technology to Multigate Transistors for Optimum Performance. IEEE Trans. Electron Devices 2015, 62, 3938–3944. [Google Scholar] [CrossRef]

- Lin, T.H.; Wang, R.D.; Chen, M.F.; Chiu, C.C.; Chen, S.Y.; Yeh, T.C.; Lin, L.C.; Hou, S.Y.; Lin, J.C.; Chen, K.H.; et al. Electromigration Study of Micro Bumps at Si/Si Interface in 3DIC Package for 28nm Technology and Beyond. In Proceedings of the 2011 IEEE 61st Electronic Components and Technology Conference (ECTC), Lake Buena Vista, FL, USA, 31 May–3 June 2011; pp. 346–350. [Google Scholar] [CrossRef]

- Felton, K.; Ferguson, J. Silicon-Package Co-Verification for 2.5D/3D Applications. In Proceedings of the 2016 IEEE International 3D Systems Integration Conference (3DIC), San Francisco, CA, USA, 8–11 November 2016; pp. 1–2. [Google Scholar] [CrossRef]

- Rebhan, B.; Bernauer, M.; Wagenleitner, T.; Heilig, M.; Kurz, F.; Lhostis, S.; Deloffre, E.; Jouve, A.; Balan, V.; Chitu, L. <200 Nm Wafer-to-Wafer Overlay Accuracy in Wafer Level Cu/SiO2 Hybrid Bonding for BSI CIS. In Proceedings of the 2015 IEEE 17th Electronics Packaging and Technology Conference (EPTC), Singapore, 2–4 December 2015; pp. 1–4. [Google Scholar] [CrossRef]

- Save, D.; Braud, F.; Torres, J.; Binder, F.; Müller, C.; Weidner, J.O.; Hasse, W. Electromigration Resistance of Copper Interconnects. Microelectron. Eng. 1997, 33, 75–84. [Google Scholar] [CrossRef]

- Wei, J.; Xie, H.; Nai, M.L.; Wong, C.K.; Lee, L.C. Low Temperature Wafer Anodic Bonding. J. Micromech. Microeng. 2003, 13, 217–222. [Google Scholar] [CrossRef]

- Maack, B.; Nilius, N. Impact of Granularity on the Oxidation Kinetics of Copper. Phys. Status Solidi B 2020, 257, 1900778. [Google Scholar] [CrossRef]

- De Los Santos Valladares, L.; Salinas, D.H.; Dominguez, A.B.; Najarro, D.A.; Khondaker, S.I.; Mitrelias, T.; Barnes, C.H.W.; Aguiar, J.A.; Majima, Y. Crystallization and Electrical Resistivity of Cu2O and CuO Obtained by Thermal Oxidation of Cu Thin Films on SiO2/Si Substrates. Thin Solid Films 2012, 520, 6368–6374. [Google Scholar] [CrossRef]

- Maack, B.; Nilius, N. Oxidation of Polycrystalline Copper Films—Pressure and Temperature Dependence. Thin Solid Films 2018, 651, 24–30. [Google Scholar] [CrossRef]

- Lee, S.Y.; Mettlach, N.; Nguyen, N.; Sun, Y.M.; White, J.M. Copper Oxide Reduction through Vacuum Annealing. Appl. Surf. Sci. 2003, 206, 102–109. [Google Scholar] [CrossRef]

- Jang, E.-J.; Hyun, S.; Lee, H.-J.; Park, Y.-B. Effect of Wet Pretreatment on Interfacial Adhesion Energy of Cu-Cu Thermocompression Bond for 3D IC Packages. J. Electron. Mater. 2009, 38, 2449–2454. [Google Scholar] [CrossRef]

- Swinnen, B.; Ruythooren, W.; De Moor, P.; Bogaerts, L.; Carbonell, L.; De Munck, K.; Eyckens, B.; Stoukatch, S.; Tezcan, D.S.; Tokei, Z.; et al. 3D Integration by Cu-Cu Thermo-Compression Bonding of Extremely Thinned Bulk-Si Die Containing 10 μm Pitch through-Si Vias. In Proceedings of the 2006 International Electron Devices Meeting, San Francisco, CA, USA, 11–13 December 2006; pp. 1–4. [Google Scholar] [CrossRef]

- Shin, S.; Higurashi, E.; Furuyama, K.; Suga, T. Hydrogen Radical Treatment for Surface Oxide Removal from Copper. In Proceedings of the 2017 5th International Workshop on Low Temperature Bonding for 3D Integration (LTB-3D), Tokyo, Japan, 16–18 May 2017; p. 72. [Google Scholar] [CrossRef]

- Chir, D.; Toh, J. Effect of RF Plasma Process Gas Chemistry and Electrode Configuration on the Removal of Copper Lead Frame Oxidation. In Proceedings of the 2022 IEEE 24th Electronics Packaging Technology Conference (EPTC), Singapore, 7–9 December 2022; pp. 493–497. [Google Scholar] [CrossRef]

- Hung, T.-H.; Kang, T.-C.; Mao, S.-Y.; Chou, T.-C.; Hu, H.-W.; Chiu, H.-Y.; Shih, C.-L.; Chen, K.-N. Investigation of Wet Pretreatment to Improve Cu-Cu Bonding for Hybrid Bonding Applications. In Proceedings of the 2021 IEEE 71st Electronic Components and Technology Conference (ECTC), San Diego, CA, USA, 1 June–4 July 2021; pp. 700–705. [Google Scholar] [CrossRef]

- Yamamoto, M.; Matsumae, T.; Kurashima, Y.; Takagi, H.; Miyake, T.; Suga, T.; Itoh, T.; Higurashi, E. Wafer-Scale Au-Au Surface Activated Bonding Using Atmospheric-Pressure Plasma. In Proceedings of the 2019 International Conference on Electronics Packaging (ICEP), Niigata, Japan, 17–20 April 2019; pp. 361–364. [Google Scholar] [CrossRef]

- Shigetou, A.; Itoh, T.; Suga, T. Bumpless Interconnect of Ultrafine Cu Electrodes by Surface Activated Bonding (SAB) Method. Electron. Commun. Jpn. Pt. II 2006, 89, 34–42. [Google Scholar] [CrossRef]

- Takeuchi, K.; Higurashi, E.; Wang, J.; Yamauchi, A.; Suga, T. Removal of Adsorbed Water on Si Wafers for Surface Activated Bonding. In Proceedings of the 2022 IEEE CPMT Symposium Japan (ICSJ), Kyoto, Japan, 9–11 November 2022; pp. 61–64. [Google Scholar] [CrossRef]

- Suga, T.; Mu, F. Surface Activated Bonding Method for Low Temperature Bonding. In Proceedings of the 2018 7th Electronic System-Integration Technology Conference (ESTC), Dresden, Germany, 18–21 September 2018; pp. 1–4. [Google Scholar] [CrossRef]

- Suga, T. Feasibility of Surface Activated Bonding for Ultra-Fine Pitch Interconnection-a New Concept of Bump-Less Direct Bonding for System Level Packaging. In Proceedings of the 2000 Proceedings. 50th Electronic Components and Technology Conference (Cat. No.00CH37070), Las Vegas, NV, USA, 21–24 May 2000; pp. 702–705. [Google Scholar] [CrossRef]

- Bonam, S.; Cheemalamarri, H.K.; Vanjari, S.R.K.; Singh, S.G. Diffusion Enhanced Optimized Thin Passivation Layer for Realizing Copper to Copper Wafer Bonding at Low Thermal Budget. In Proceedings of the 2022 IEEE 24th Electronics Packaging Technology Conference (EPTC), Singapore, 7–9 December 2022; pp. 344–347. [Google Scholar] [CrossRef]

- Panigrahi, A.K.; Bonam, S.; Ghosh, T.; Singh, S.G.; Vanjari, S.R.K. Ultra-Thin Ti Passivation Mediated Breakthrough in High Quality Cu-Cu Bonding at Low Temperature and Pressure. Mater. Lett. 2016, 169, 269–272. [Google Scholar] [CrossRef]

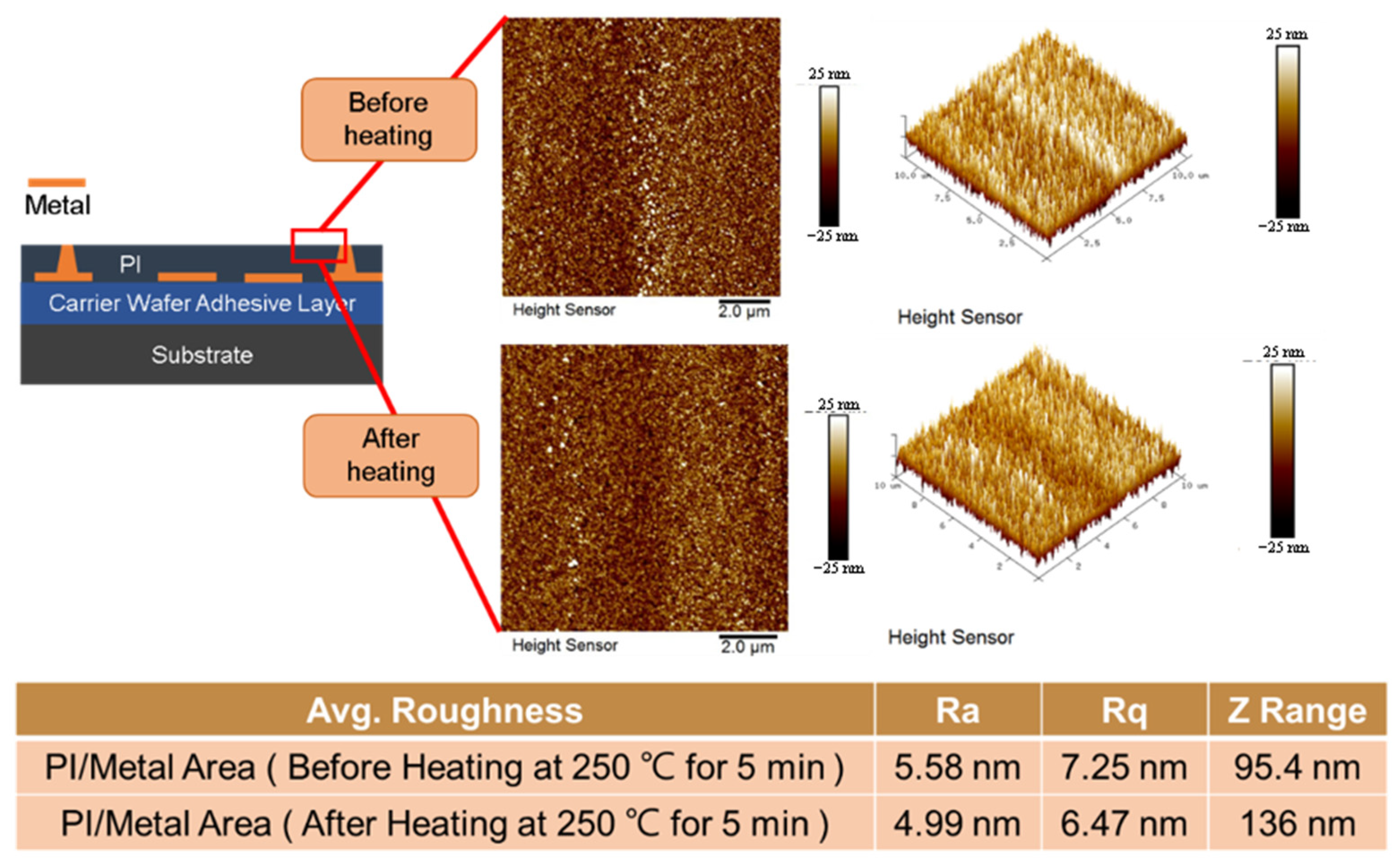

- Hong, Z.-J.; Liu, D.; Hu, H.-W.; Hsiung, C.-K.; Cho, C.-I.; Chen, C.-H.; Liu, J.-H.; Weng, M.-W.; Hsu, M.-P.; Hung, Y.-C.; et al. Low-Temperature Hybrid Bonding with High Electromigration Resistance Scheme for Application on Heterogeneous Integration. Appl. Surf. Sci. 2023, 610, 155470. [Google Scholar] [CrossRef]

- Huang, Y.-P.; Chien, Y.-S.; Tzeng, R.-N.; Shy, M.-S.; Lin, T.-H.; Chen, K.-H.; Chiu, C.-T.; Chiou, J.-C.; Chuang, C.-T.; Hwang, W.; et al. Novel Cu-to-Cu Bonding With Ti Passivation at 180 °C in 3-D Integration. IEEE Electron Device Lett. 2013, 34, 1551–1553. [Google Scholar] [CrossRef]

- Huang, Y.-P.; Chien, Y.-S.; Tzeng, R.-N.; Chen, K.-N. Demonstration and Electrical Performance of Cu–Cu Bonding at 150 °C With Pd Passivation. IEEE Trans. Electron Devices 2015, 62, 2587–2592. [Google Scholar] [CrossRef]

- Chou, T.-C.; Huang, S.-Y.; Chen, P.-J.; Hu, H.-W.; Liu, D.; Chang, C.-W.; Ni, T.-H.; Chen, C.-J.; Lin, Y.-M.; Chang, T.-C.; et al. Electrical and Reliability Investigation of Cu-to-Cu Bonding With Silver Passivation Layer in 3-D Integration. IEEE Trans. Compon. Packag. Manufact. Technol. 2021, 11, 36–42. [Google Scholar] [CrossRef]

- Liu, D.; Chen, P.-C.; Tsai, Y.-C.; Chen, K.-N. Low Temperature Cu to Cu Direct Bonding below 150 °C with Au Passivation Layer. In Proceedings of the 2019 International 3D Systems Integration Conference (3DIC), Sendai, Japan, 8–10 October 2019; pp. 1–4. [Google Scholar] [CrossRef]

- Huang, Y.-P. Development of Low Temperature Cu Bonding and Heterogeneous Integration Platform, PhD Thesis, National Chiao Tung University, Hsinchu, Taiwan, March 2017. [Google Scholar]

- Chou, T.-C. Investigation and Discussion on Passivation Bonding and Asymmetric Bonding Structure of Low Temperature Cu-Cu Direct Bonding in 3D Heterogeneous Integration, PhD Thesis, National Chiao Tung University, Hsinchu, Taiwan, December 2020. [Google Scholar]

- Liu, D. Development of Low-Temperature Cu-Cu Direct Bonding Technology Based on Passivation Scheme, PhD Thesis, National Yang Ming Chiao Tung University, Hsinchu, Taiwan, November 2021. [Google Scholar]

- Uttam, P.; Kumar, V.; Kim, K.-H.; Deep, A. Nanotwinning: Generation, Properties, and Application. Mater. Des. 2020, 192, 108752. [Google Scholar] [CrossRef]

- Zhu, T.; Gao, H. Plastic Deformation Mechanism in Nanotwinned Metals: An Insight from Molecular Dynamics and Mechanistic Modeling. Scr. Mater. 2012, 66, 843–848. [Google Scholar] [CrossRef]

- Ong, J.-J.; Chiu, W.-L.; Lee, O.-H.; Chiang, C.-W.; Chang, H.-H.; Wang, C.-H.; Shie, K.-C.; Yang, S.-C.; Tran, D.-P.; Tu, K.-N.; et al. Low-Temperature Cu/SiO2 Hybrid Bonding with Low Contact Resistance Using (111)-Oriented Cu Surfaces. Materials 2022, 15, 1888. [Google Scholar] [CrossRef]

- Agrawal, P.M.; Rice, B.M.; Thompson, D.L. Predicting Trends in Rate Parameters for Self-Diffusion on FCC Metal Surfaces. Surf. Sci. 2002, 515, 21–35. [Google Scholar] [CrossRef]

- Chen, K.N.; Fan, A.; Tan, C.S.; Reif, R.; Wen, C.Y. Microstructure Evolution and Abnormal Grain Growth during Copper Wafer Bonding. Appl. Phys. Lett. 2002, 81, 3774–3776. [Google Scholar] [CrossRef]

- Lin, P.-F.; Tran, D.-P.; Liu, H.-C.; Li, Y.-Y.; Chen, C. Interfacial Characterization of Low-Temperature Cu-to-Cu Direct Bonding with Chemical Mechanical Planarized Nanotwinned Cu Films. Materials 2022, 15, 937. [Google Scholar] [CrossRef]

- Bonam, S.; Kumar, C.H.; Vanjari, S.R.K.; Singh, S.G. Gold Passivated Cu-Cu Bonding at 140 °C For 3D IC Packaging and Heterogeneous Integration Applications. In Proceedings of the 2018 IEEE 20th Electronics Packaging Technology Conference (EPTC), Singapore, 4–7 December 2018; pp. 547–550. [Google Scholar] [CrossRef]

- Fournel, F.; Martin-Cocher, C.; Radisson, D.; Larrey, V.; Beche, E.; Morales, C.; Delean, P.A.; Rieutord, F.; Moriceau, H. Water Stress Corrosion in Bonded Structures. ECS J. Solid State Sci. Technol. 2015, 4, P124–P130. [Google Scholar] [CrossRef]

- Du, M.; Li, D.; Liu, Y. Investigation of Plasma Activated Si-Si Bonded Interface by Infrared Image Based on Combination of Spatial Domain and Morphology. Micromachines 2019, 10, 445. [Google Scholar] [CrossRef]

- Kim, Y.-S.; Nguyen, T.H.; Choa, S.-H. Enhancement of the Bond Strength and Reduction of Wafer Edge Voids in Hybrid Bonding. Micromachines 2022, 13, 537. [Google Scholar] [CrossRef]

- Wiegand, M.; Reiche, M.; Gösele, U.; Gutjahr, K.; Stolze, D.; Longwitz, R.; Hiller, E. Wafer Bonding of Silicon Wafers Covered with Various Surface Layers. Sens. Actuators A Phys. 2000, 86, 91–95. [Google Scholar] [CrossRef]

- Ko, C.-T.; Chen, K.-N. Low Temperature Bonding Technology for 3D Integration. Microelectron. Reliab. 2012, 52, 302–311. [Google Scholar] [CrossRef]

- Lhostis, S.; Farcy, A.; Deloffre, E.; Lorut, F.; Mermoz, S.; Henrion, Y.; Berthier, L.; Bailly, F.; Scevola, D.; Guyader, F.; et al. Reliable 300 Mm Wafer Level Hybrid Bonding for 3D Stacked CMOS Image Sensors. In Proceedings of the 2016 IEEE 66th Electronic Components and Technology Conference (ECTC), Las Vegas, NV, USA, 31 May–3 June 2016; pp. 869–876. [Google Scholar] [CrossRef]

- Ayoub, B.; Lhostis, S.; Moreau, S.; Souchier, E.; Deloffre, E.; Mermoz, S.; Cacho, M.G.G.; Szekely, N.; Rey, C.; Aybeke, E.; et al. Sub 1 Μm Pitch Achievement for Cu/SiO2 Hybrid Bonding. In Proceedings of the 2022 IEEE 24th Electronics Packaging Technology Conference (EPTC), Singapore, 7–9 December 2022; pp. 418–424. [Google Scholar] [CrossRef]

- Kang, Q.; Wang, C.; Li, G.; Zhou, S.; Tian, Y. Low-Temperature Cu/SiO2 Hybrid Bonding Using a Novel Two-Step Cooperative Surface Activation. In Proceedings of the 2021 22nd International Conference on Electronic Packaging Technology (ICEPT), Xiamen, China, 14–17 September 2021; pp. 1–5. [Google Scholar] [CrossRef]

- Kang, Q.; Li, G.; Li, Z.; Tian, Y.; Wang, C. Surface Co-Hydrophilization via Ammonia Inorganic Strategy for Low-Temperature Cu/SiO2 Hybrid Bonding. J. Mater. Sci. Technol. 2023, 149, 161–166. [Google Scholar] [CrossRef]

- Liu, D.; Chen, P.-C.; Chou, T.-C.; Hu, H.-W.; Chen, K.-N. Demonstration of Low-Temperature Fine-Pitch Cu/SiO2 Hybrid Bonding by Au Passivation. IEEE J. Electron Devices Soc. 2021, 9, 868–875. [Google Scholar] [CrossRef]

- Liu, D.; Chen, P.-C.; Hsiung, C.-K.; Huang, S.-Y.; Huang, Y.-P.; Verhaverbeke, S.; Mori, G.; Chen, K.-N. Low Temperature Cu/SiO2 Hybrid Bonding with Metal Passivation. In Proceedings of the 2020 IEEE Symposium on VLSI Technology, Honolulu, HI, USA, 16–19 June 2020; pp. 1–2. [Google Scholar] [CrossRef]

- Peng, L.; Kim, S.-W.; Iacovo, S.; Inoue, F.; Phommahaxay, A.; Sleeckx, E.; De Vos, J.; Miller, A.; Beyer, G.; Beyne, E.; et al. Advances in SiCN-SiCN Bonding with High Accuracy Wafer-to-Wafer (W2W) Stacking Technology. In Proceedings of the 2018 IEEE International Interconnect Technology Conference (IITC), Santa Clara, CA, USA, 4–7 June 2018; pp. 179–181. [Google Scholar] [CrossRef]

- Beyne, E.; Kim, S.-W.; Peng, L.; Heylen, N.; De Messemaeker, J.; Okudur, O.O.; Phommahaxay, A.; Kim, T.-G.; Stucchi, M.; Velenis, D.; et al. Scalable, Sub 2 μm Pitch, Cu/SiCN to Cu/SiCN Hybrid Wafer-to-Wafer Bonding Technology. In Proceedings of the 2017 IEEE International Electron Devices Meeting (IEDM), San Francisco, CA, USA, 2–6 December 2017; pp. 32.4.1–32.4.4. [Google Scholar] [CrossRef]

- Chiu, W.-L.; Lee, O.-H.; Kuo, T.-Y.; Lo, J.Y.-J.; Shih, C.-L.; Chiu, H.-Y.; Chang, H.-H. Low Temperature and Fine Pitch Nanocrystalline Cu/SiCN Wafer-to-Wafer Hybrid Bonding. In Proceedings of the 2023 IEEE 73rd Electronic Components and Technology Conference (ECTC), Orlando, FL, USA, 30 May–2 June 2023; pp. 1105–1109. [Google Scholar] [CrossRef]

- Chew, S.-A.; Iacovo, S.; Fordor, F.; Dewilde, S.; Devriendt, K.; De Vos, J.; Miller, A.; Beyer, G.; Beyne, E. 700 nm Pitch Cu/SiCN Wafer-to-Wafer Hybrid Bonding. In Proceedings of the 2022 IEEE 24th Electronics Packaging Technology Conference (EPTC), Singapore, 7–9 December 2022; pp. 334–337. [Google Scholar] [CrossRef]

- Iacovo, S.; Kim, S.-W.; Nagano, F.; Peng, L.; Inoue, F.; Phommahaxay, A.; Beyne, E. The Unique Properties of SiCN as Bonding Material for Hybrid Bonding. In Proceedings of the 2021 7th International Workshop on Low Temperature Bonding for 3D Integration (LTB-3D), Nara, Japan, 5–11 October 2021; p. 38. [Google Scholar] [CrossRef]

- Kim, S.-W.; Fodor, F.; Heylen, N.; Iacovo, S.; De Vos, J.; Miller, A.; Beyer, G.; Beyne, E. Novel Cu/SiCN Surface Topography Control for 1 Μm Pitch Hybrid Wafer-to-Wafer Bonding. In Proceedings of the 2020 IEEE 70th Electronic Components and Technology Conference (ECTC), Orlando, FL, USA, 3–30 June 2020; pp. 216–222. [Google Scholar] [CrossRef]

- Chen, Y.C.; Wan, K.; Chang, C.A.; Lee, R. Low Temperature Curable Polyimide Film Properties and WLP Reliability Performance with Various Curing Conditions. In Proceedings of the 2017 IEEE 67th Electronic Components and Technology Conference (ECTC), Orlando, FL, USA, 30 May–2 June 2017; pp. 2040–2046. [Google Scholar] [CrossRef]

- Lau, J.H. Recent Advances and Trends in Advanced Packaging. IEEE Trans. Compon. Packag. Manufact. Technol. 2022, 12, 228–252. [Google Scholar] [CrossRef]

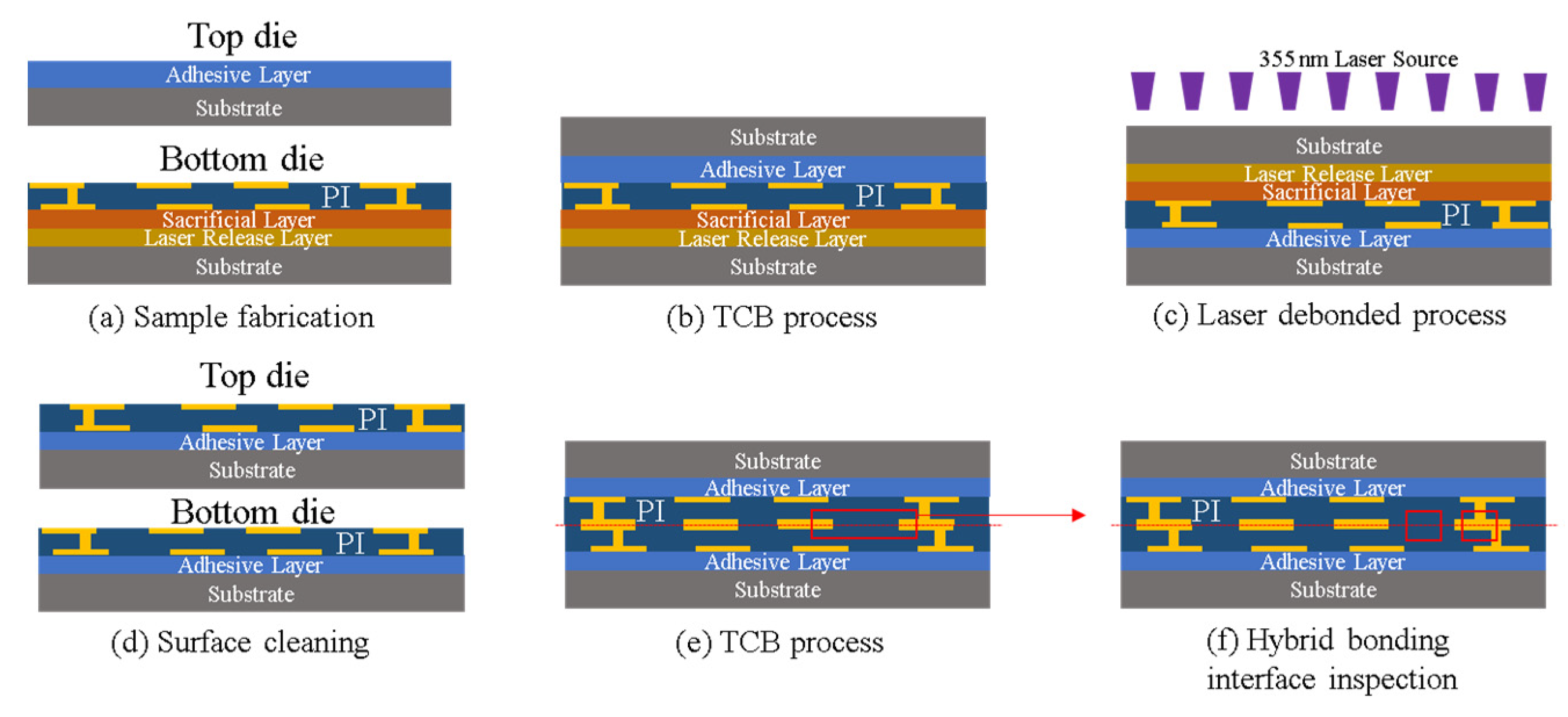

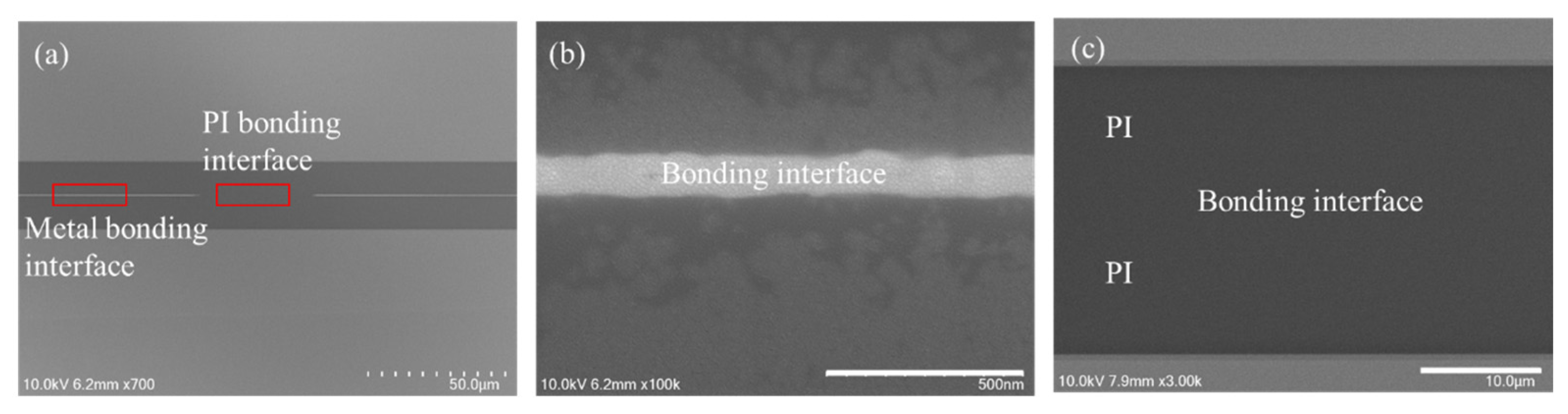

- Huang, Y.-J.; Chen, H.-C.; Yu, T.-Y.; Lai, B.-H.; Shih, Y.-C.; Chen, K.-N. Asymmetry Hybrid Bonding Using Cu/Sn Bonding with Polyimide for 3D Heterogeneous Integration Applications. In Proceedings of the 2017 12th International Microsystems, Packaging, Assembly and Circuits Technology Conference (IMPACT), Taipei, Taiwan, 25–27 October 2017; pp. 187–190. [Google Scholar] [CrossRef]

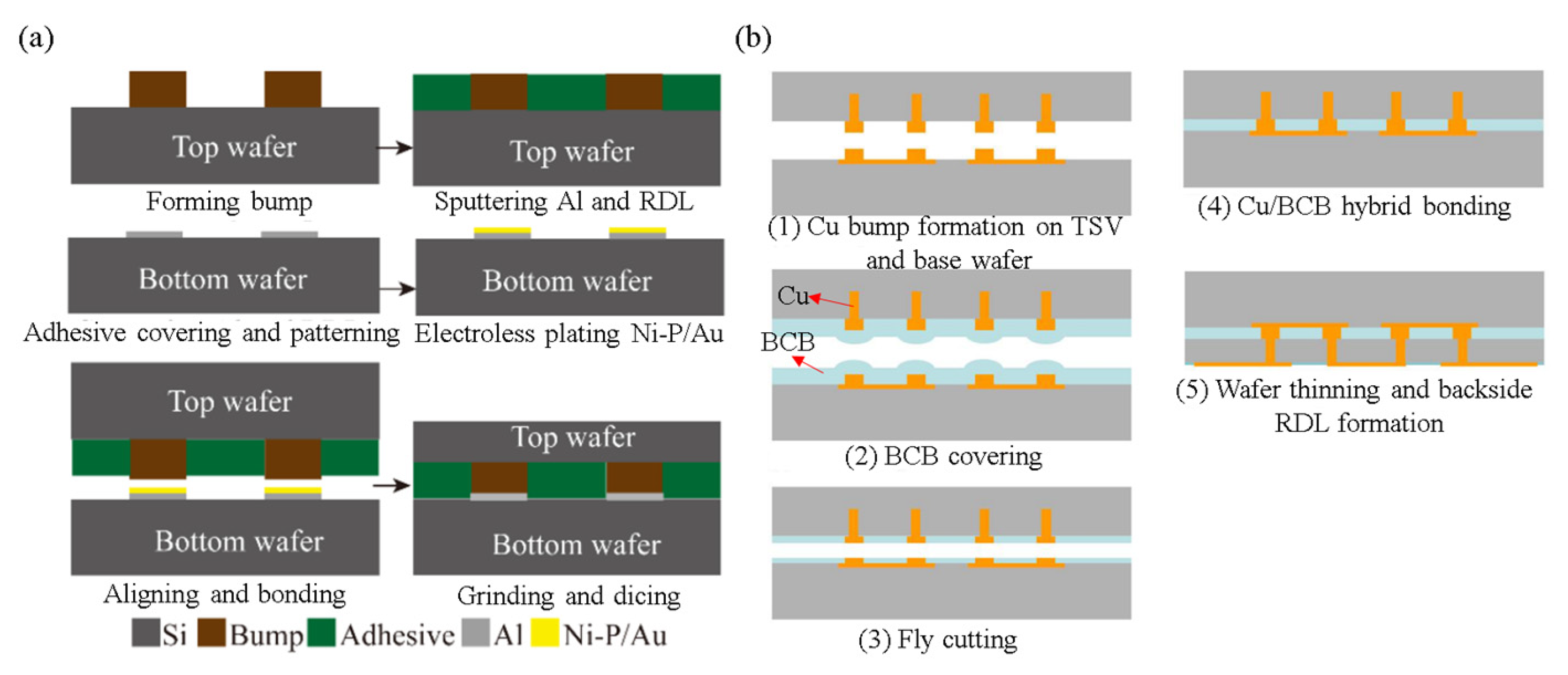

- Yao, M.; Fan, J.; Zhao, N.; Xiao, Z.; Yu, D.; Ma, H. Simplified Low-Temperature Wafer-Level Hybrid Bonding Using Pillar Bump and Photosensitive Adhesive for Three-Dimensional Integrated Circuit Integration. J. Mater. Sci. Mater. Electron. 2017, 28, 9091–9095. [Google Scholar] [CrossRef]

- Yao, M.; Yu, D.; Zhao, N.; Fan, J.; Xiao, Z.; Ma, H. Development of Wafer Level Hybrid Bonding Process Using Photosensitive Adhesive and Cu Pillar Bump. In Proceedings of the 2017 China Semiconductor Technology International Conference (CSTIC), Shanghai, China, 12–13 March 2017; pp. 1–3. [Google Scholar] [CrossRef]

- Hsiao, Z.-C.; Ko, C.-T.; Chang, H.-H.; Fu, H.-C.; Chiang, C.-W.; Hsu, C.-K.; Shen, W.-W.; Lo, W.-C. Cu/BCB Hybrid Bonding with TSV for 3D Integration by Using Fly Cutting Technology. In Proceedings of the 2015 International Conference on Electronic Packaging and iMAPS All Asia Conference (ICEP-IAAC), Kyoto, Japan, 14–17 April 2015; pp. 834–837. [Google Scholar] [CrossRef]

- Ahmad, Z. Polymer Dielectric Materials. In Dielectric Material; Silaghi, M.A., Ed.; InTech: Houston, TX, USA, 2012; ISBN 978-953-51-0764-4. [Google Scholar]

- Ahmed, S.R.A.; Naito, S.; Kobayashi, K. Characterization of Low-Dielectric Constant Silicon Carbonitride (SiCN) Dielectric Films for Charge Trapping Nonvolatile Memories. ECS Trans. 2015, 69, 99–109. [Google Scholar] [CrossRef]

- Carlotti, G.; Colpani, P.; Piccolo, D.; Santucci, S.; Senez, V.; Socino, G.; Verdini, L. Measurement of the Elastic and Viscoelastic Properties of Dielectric Films Used in Microelectronics. Thin Solid Films 2002, 414, 99–104. [Google Scholar] [CrossRef]

- Goncalves, P.D.C. Dry Sliding Behavior of Filled PDC Coatings Applied onto Surface Modified Sintered Steel. Master’s Thesis, Universidade Federal de Santa Catarina, Florianópolis, Brazil, 2016. [Google Scholar] [CrossRef]

| Bonding Temperature | Advantage | Disadvantage | Reference | |

|---|---|---|---|---|

| Surface chemical pretreatment | 250 °C to 350 °C | Low cost High throughput | High bonding temperature | [15,16,17,18,19] |

| Surface activation | Room temperature | Low thermal budget Good bonding quality (UHV environment) | High cost UHV environment needed | [20,21,22,23,24] |

| Structure modification with passivation | 70 °C to 200 °C | Low bonding temperature Low cost | An additional lithography process for passivation metal deposition | [25,26,27,28,29,30,31,32,33,34] |

| Orientation control with (111) surface | 150 °C to 250 °C | CMOS compatibility Good bonding strength | Limitation in fine-pitch RDL structure | [35,36,37,38,39,40,41] |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2023 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Huang, Y.-C.; Lin, Y.-X.; Hsiung, C.-K.; Hung, T.-H.; Chen, K.-N. Cu-Based Thermocompression Bonding and Cu/Dielectric Hybrid Bonding for Three-Dimensional Integrated Circuits (3D ICs) Application. Nanomaterials 2023, 13, 2490. https://doi.org/10.3390/nano13172490

Huang Y-C, Lin Y-X, Hsiung C-K, Hung T-H, Chen K-N. Cu-Based Thermocompression Bonding and Cu/Dielectric Hybrid Bonding for Three-Dimensional Integrated Circuits (3D ICs) Application. Nanomaterials. 2023; 13(17):2490. https://doi.org/10.3390/nano13172490

Chicago/Turabian StyleHuang, Yuan-Chiu, Yu-Xian Lin, Chien-Kang Hsiung, Tzu-Heng Hung, and Kuan-Neng Chen. 2023. "Cu-Based Thermocompression Bonding and Cu/Dielectric Hybrid Bonding for Three-Dimensional Integrated Circuits (3D ICs) Application" Nanomaterials 13, no. 17: 2490. https://doi.org/10.3390/nano13172490