Low-Voltage and Low-Power True-Single-Phase 16-Transistor Flip-Flop Design

Abstract

:1. Introduction

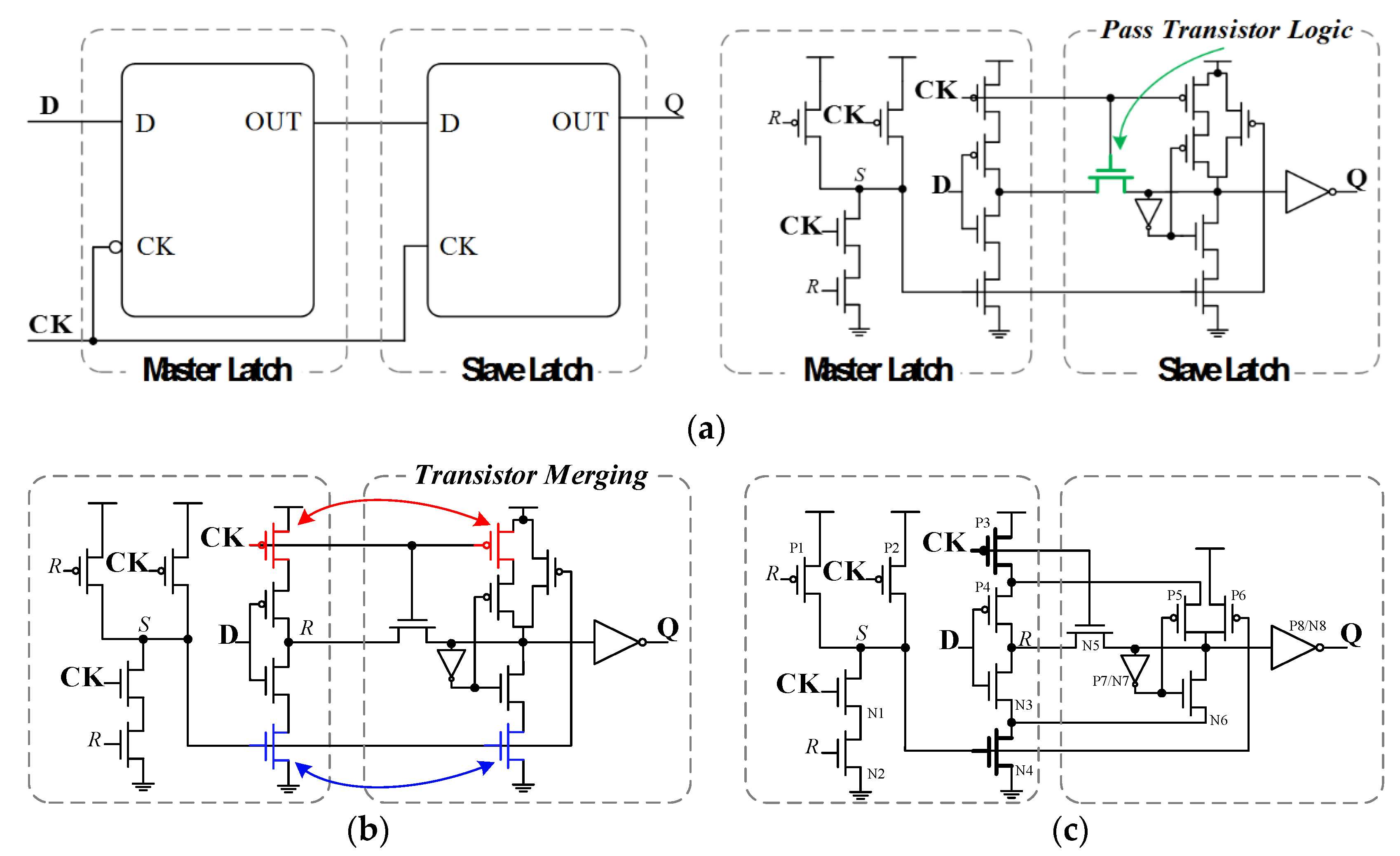

2. Proposed Low Power 16-Transistor FF Design

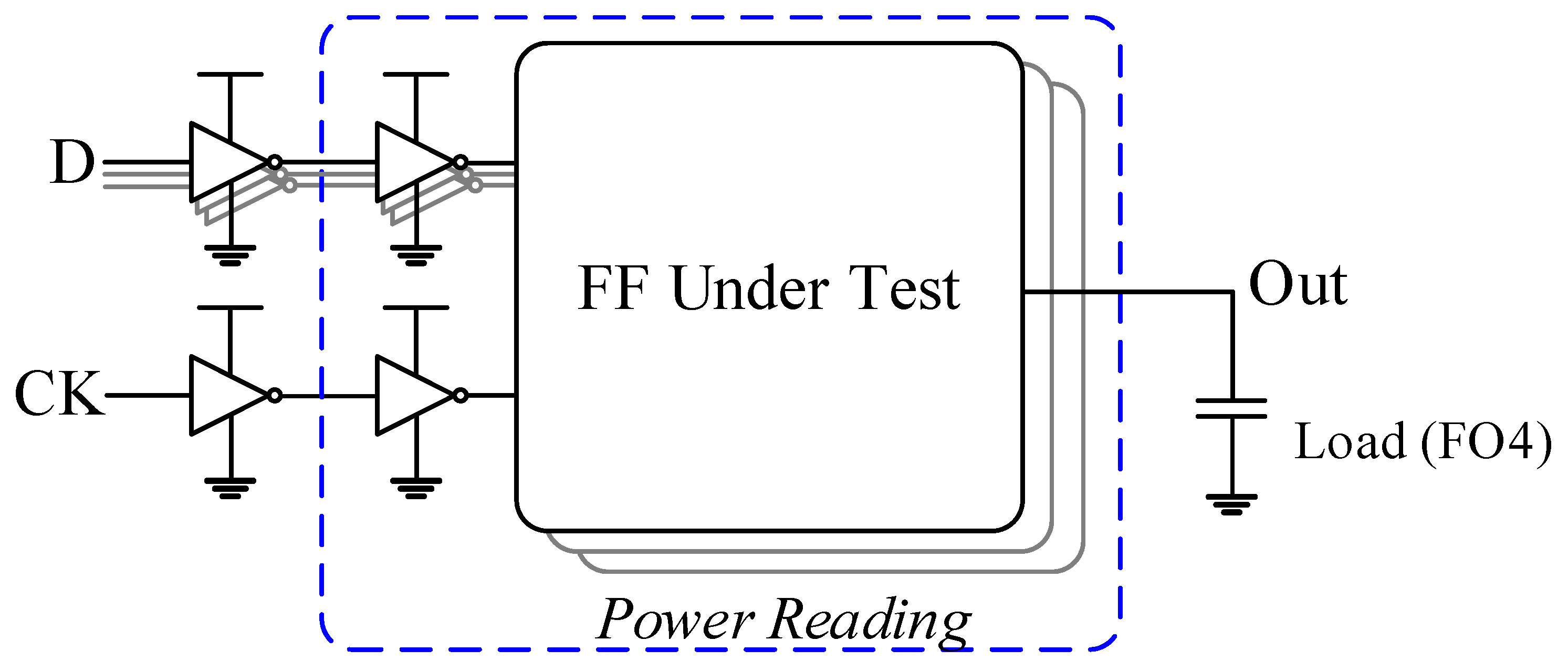

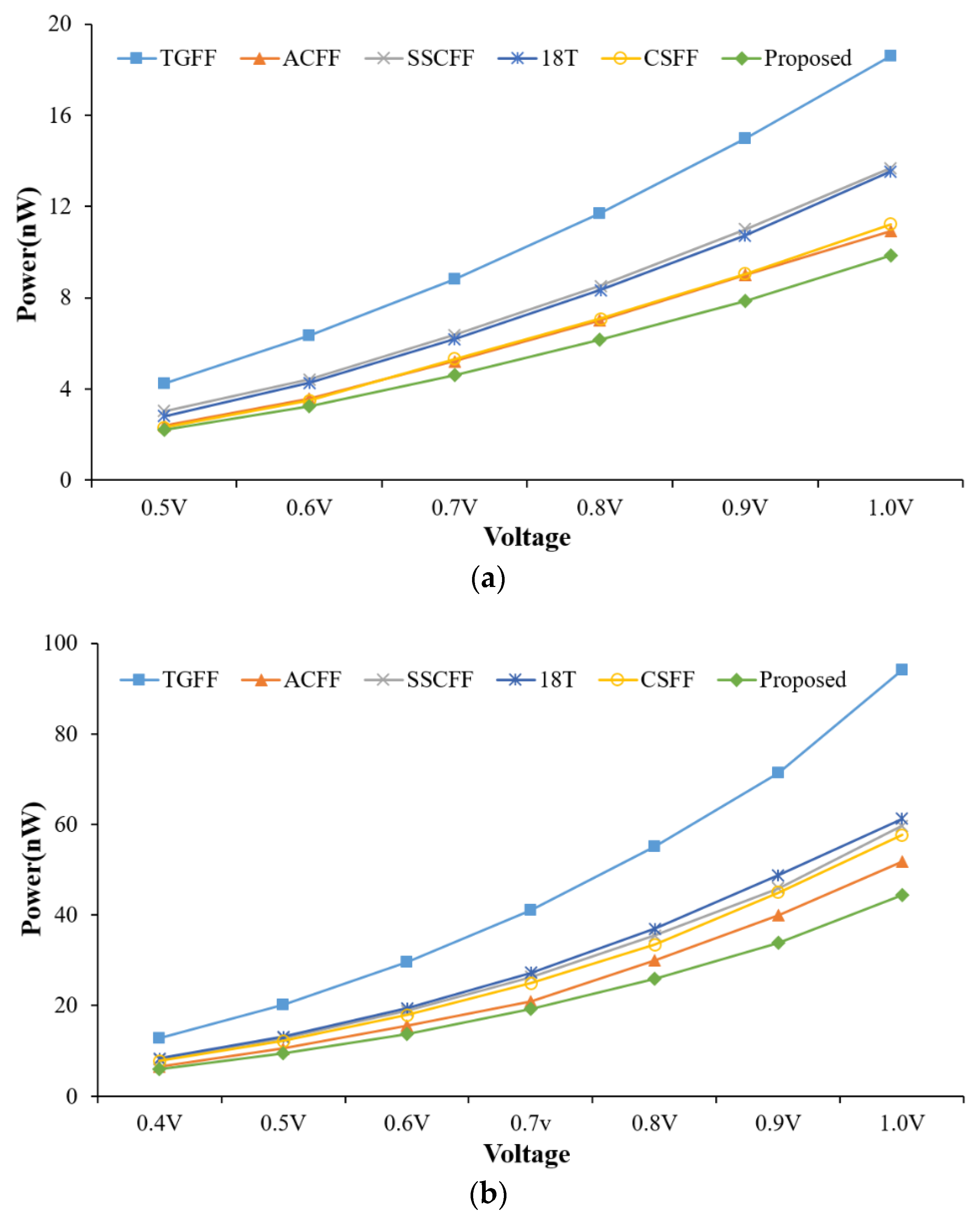

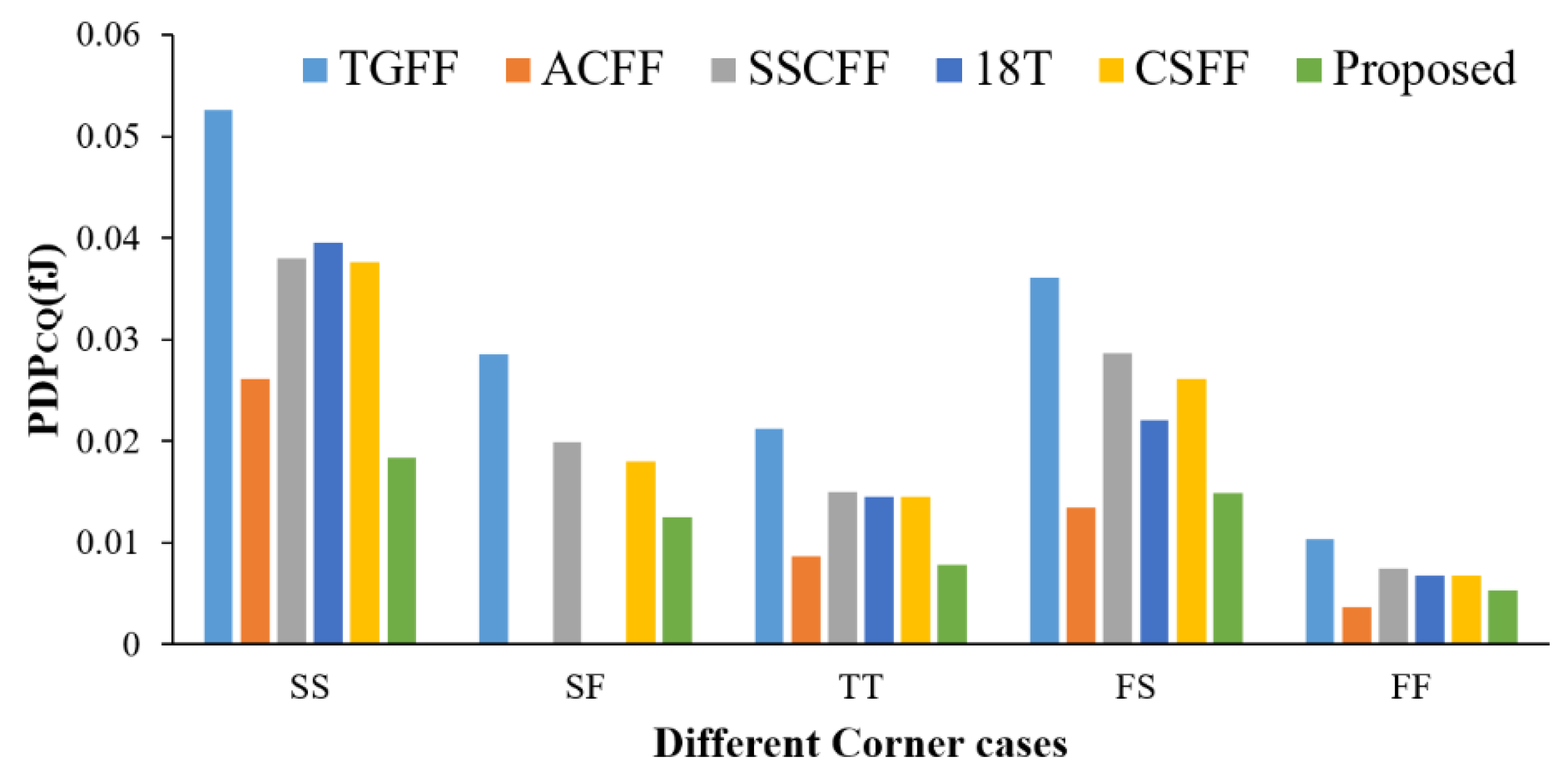

3. Simulation Results

4. Conclusions

Author Contributions

Funding

Institutional Review Board Statement

Informed Consent Statement

Data Availability Statement

Acknowledgments

Conflicts of Interest

References

- Chang, K.-L.; Gwee, B.-H.; Chang, J.S.; Chong, K.-S. Synchronous logic and asynchronous-logic 8051 microcontroller cores for realizing the Internet of Things: A comparative study on dynamic voltage scaling and variation effects. IEEE J. Emerg. Sel. Top. Circuits Syst. 2013, 3, 23–34. [Google Scholar] [CrossRef]

- Shin, J.L.; Golla, R.; Li, H.; Dash, S.; Choi, Y.; Smith, A.; Sathianathan, H.; Joshi, M.; Park, H.; Elgebaly, M.; et al. The next generation 64b SPARC core in a T4 SoC processor. IEEE J. Solid-State Circuits 2013, 48, 82–90. [Google Scholar] [CrossRef]

- Stojanovic, V.; Oklobdzija, V.G. Comparative analysis of masters-lave latches and flip-flops for high-performance and low-power systems. IEEE J. Solid-State Circuits 1999, 34, 536–548. [Google Scholar] [CrossRef]

- Moreau, L.; Rémi, D.; David, B. A 0.4 V 0.5 fJ/cycle TSPC flip-flop in 65nm LP CMOS with retention mode controlled by clock-gating cells. In Proceedings of the 2019 IEEE International Symposium on Circuits and Systems, Sapporo, Japan, 26–29 May 2019. [Google Scholar]

- Nomura, S.; Tachibana, F.; Fujita, T.; Teh, C.K.; Usui, H.; Yamane, F.; Miyamoto, Y.; Kumtornkittikul, C.; Hara, H.; Yamashita, T.; et al. A 9.7 mW AAC-decoding, 620 mW H.264 720p 60fps decoding, 8-core media processor with embedded forward body-biasing and power-gating circuit in 65 nm CMOS technology. In Proceedings of the IEEE International Solid-State Circuits Conference-Digest of Technical Papers, San Francisco, CA, USA, 3–7 February 2008; pp. 262–612. [Google Scholar]

- Teh, C.K.; Fujita, T.; Hara, H.; Hamada, M. A 77% Energy-Saving 22-Transistor Single-Phase Clocking D-Flip-Flop with AdaptiveCoupling Configuration in 40 nm CMOS. In Proceedings of the 2011 IEEE International Solid-State Circuits Conference, San Francisco, CA, USA, 20–24 February 2011; pp. 338–339. [Google Scholar]

- Consoli, E.; Alioto, M.; Palumbo, G.; Rabaey, J. Conditional push-pull pulsed latch with 726 fJ.ps energy delay product in 65nm CMOS. In Proceedings of the 2012 IEEE International Solid-State Circuits Conference, ISSCC 2012, San Francisco, CA, USA, 19–23 February 2012; pp. 482–483. [Google Scholar]

- Kim, Y.; Shin, B. A static contention-free single-phase-clocked 24T flip-flop in 45nm for low-power applications. In Proceedings of the 2014 IEEE International Solid-State Circuits Conference Digest of Technical Papers (ISSCC), San Francisco, CA, USA, 9–13 February 2014; pp. 466–467. [Google Scholar]

- Kawai, N.; Ishinura, M. A fully static topologically-compressed 21-transistor flip-flop with 75% power saving. IEEE J. Solid-State Circuits 2014, 49, 2526–2533. [Google Scholar] [CrossRef]

- Alioto, M.; Consoli, E.; Palumbo, G. Variations in nanometer CMOS flip-flops: Part I—Impact of process variations on timing. IEEE Trans. Circuits Syst. I Regul. Pap. 2015, 62, 2035–2043. [Google Scholar] [CrossRef]

- Lin, J.F.; Sheu, M.H.; Hwang, Y.T.; Wong, C.S.; Tsai, M.Y. Low-power 19-transistor true single-phase clocking flip-flop design based on logic structure reduction schemes. IEEE Trans. Very Large Scale Integr. Syst. 2017, 25, 3033–3044. [Google Scholar] [CrossRef]

- Jeong, H.; Oh, T.W.; Song, S.C.; Jung, S.-O. Sense-amplifier-based flip-flop with transition completion detection for low-voltage operation. IEEE Trans. Very Large Scale Integr. Syst. 2018, 26, 609–620. [Google Scholar] [CrossRef]

- Stas, F.; Bol, D. A 0.4-V 0.66-fJ/cycle retentive true-single-phase clock 18T flip-flop in 28-nm fully-depleted SOI CMOS. IEEE Trans. Circuits Syst. I Reg. Pap. 2018, 65, 935–945. [Google Scholar] [CrossRef]

- Kuamar, H.; Nagarajan, R. Low Power High Speed 15-Transistor Static True Single Phase Flip Flop. In Proceedings of the 2nd International Conference on Intelligent Computing, Instrumentation and Control Technologies (ICICICT), Kannur, India, 5–6 July 2019; pp. 440–444. [Google Scholar]

- Yuan, J.; Hwang, B. High-Speed CMOS Circuit Technique. IEEE J. Solid-State Circuits 1989, 24, 62–70. [Google Scholar] [CrossRef] [Green Version]

- Shin, G.; Lee, E.; Lee, J.; Lee, Y.; Lee, Y. An ultra-low-power fully-static contention-free flip-flop with complete redundant clock transition and transistor elimination. IEEE J. Solid-State Circuits 2021, 56, 3039–3048. [Google Scholar] [CrossRef]

- Lin, J.-F.; Hong, Z.-J.; Tsai, C.-M.; Wu, B.-C.; Yu, S.-W. Novel Low-Complexity and Low-Power Flip-Flop Design. Electronics 2020, 9, 783. [Google Scholar] [CrossRef]

- Le, V.L.; Li, J.; Chang, A.; Kim, T.H. An 82% energy-saving change-sensing flip-flop in 40 nm CMOS for ultra-low power applications. In Proceedings of the 2017 IEEE Asian Solid-State Circuits Conference (A-SSCC), Seoul, Korea, 6–8 November 2017; pp. 197–200. [Google Scholar]

- Le, V.L.; Li, J.; Chang, A.; Kim, T.H. A 0.4-V, 0.138-fJ/cycle single-phase-clocking redundant-transition-free 24T flip-flop with change-sensing scheme in 40-nm CMOS. IEEE J. Solid-State Circuits 2018, 53, 2806–2817. [Google Scholar] [CrossRef]

- Park, J.-Y.; Jin, M.; Kim, S.-Y.; Song, M. Design of a Dual Change-Sensing 24T Flip-Flop in 65 nm CMOS Technology for Ultra Low-Power System Chips. Electronics 2022, 11, 877. [Google Scholar] [CrossRef]

- Kuo, P.-Y.; Sheu, M.-H.; Tsai, C.-M.; Tsai, M.-Y.; Lin, J.-F. A Novel Cross-Latch Shift Register Scheme for Low Power Applications. Appl. Sci. 2021, 11, 129. [Google Scholar] [CrossRef]

- TSMC. 90 nm CMOS ASIC Process Digest; Taiwan Semiconductor Manufacturing Company: Taipei, Taiwan, 2005. [Google Scholar]

- TSMC. 180 nm CMOS ASIC Process Digest; Taiwan Semiconductor Manufacturing Company: Taipei, Taiwan, 2000. [Google Scholar]

- Mishra, K.A.; Chopra, U.; Vaithiyanathan, D. A Partially Static High Frequency 18T Hybrid Topological Flip-Flop Design for Low Power Application. IEEE Trans. Circuits Syst. II Express Briefs 2021, 69, 1592–1596. [Google Scholar] [CrossRef]

- Jeong, H.; Park, J.; Song, S.C.; Jung, S.-O. Self-Timed Pulsed Latch for Low-Voltage Operation with Reduced Hold Time. IEEE J. Solid-State Circuits 2019, 54, 2304–2315. [Google Scholar] [CrossRef]

- Lee, Y.; Shin, G.; Lee, Y. A Fully Static True-Single-Phase-Clocked Dual-Edge-Triggered Flip-Flop for Near-Threshold VoltageOperation in IoT Applications. IEEE Access 2020, 8, 40232–40245. [Google Scholar] [CrossRef]

- Huang, Y.; Jiao, H. An Ultra-Low-Voltage Single-Phase Adaptive Pulse Latch with Redundant Toggling Elimination. In Proceedings of the IEEE 15th International Conference on Solid-State & Integrated Circuit Technology (ICSICT), Kunming, China, 3–6 November 2020; pp. 1–3. [Google Scholar]

- You, H.; Yuan, J.; Tang, W.; Yu, Z.; Qiao, S. A Low-Power High-Speed Sense-Amplifier-Based Flip-Flop in 55 nm MTCMOS. Electronics 2020, 9, 802. [Google Scholar] [CrossRef]

- Lin, J.-F.; Hwang, Y.-T.; Wong, C.-S.; Shey, M.-H. Single-ended structure sense-amplifier based flip-flop for low-power systems. Electron. Lett. 2015, 51, 20–21. [Google Scholar] [CrossRef]

- Yang, B.-D. Low-Power and Area-Efficient Shift Register Using Pulsed Latches. IEEE Trans. Circuits Syst. I Regul. Pap. 2015, 62, 1564–1571. [Google Scholar] [CrossRef]

| Name | W(nm) | Name | W(nm) | Name | W(nm) | Name | W(nm) |

|---|---|---|---|---|---|---|---|

| P1 | 250 | P5 | 500 | N1 | 1000 | N5 | 500 |

| P2 | 250 | P6 | 500 | N2 | 1000 | N6 | 500 |

| P3 | 1500 | P7 | 250 | N3 | 250 | N7 | 250 |

| P4 | 1000 | P8 | 1000 | N4 | 500 | N8 | 500 |

| Name | W (nm) | Name | W (nm) | Name | W (nm) | Name | W (nm) |

|---|---|---|---|---|---|---|---|

| P1 | 200 | P5 | 300 | N1 | 450 | N5 | 300 |

| P2 | 200 | P6 | 300 | N2 | 450 | N6 | 200 |

| P3 | 600 | P7 | 200 | N3 | 200 | N7 | 200 |

| P4 | 400 | P8 | 600 | N4 | 300 | N8 | 300 |

| FF Designs | TGFF | ACFF 1 | SSCFF | 18T 1 | CSFF | Proposed |

|---|---|---|---|---|---|---|

| Transistors CK/Total | 12/24 | 4/22 | 5/24 | 4/18 | 5/24 | 4/16 |

| Cell Width(um) | 10.86 | 13.52 | 11.84 | 8.81 | 13.37 | 7.52 |

| Setup Time(nS) | 10.95 | 37.48 | 19.68 | 10.55 | 21.58 | 11.76 |

| Hold Time (nS) | −3.10 | −8.59 | 1.41 | 12.15 | 1.04 | 7.77 |

| CQ Delay(nS) | 22.44 | 18.55 | 18.23 | 24.76 | 19.85 | 16.66 |

| DQ Delay(nS) | 33.39 | 56.03 | 37.91 | 35.31 | 41.43 | 28.42 |

| Power@100% (nW) | 7.74 | 8.15 | 6.21 | 5.44 | 6.66 | 4.46 |

| Power@50% (nW) | 5.82 | 4.89 | 4.34 | 3.96 | 4.39 | 2.99 |

| Power@25% (nW) | 4.80 | 3.67 | 3.66 | 3.13 | 3.71 | 2.44 |

| [email protected]% (nW) | 4.24 | 2.57 | 3.03 | 2.79 | 2.60 | 2.21 |

| Power@0% (nW) | 3.80 | 1.56 | 2.47 | 2.28 | 2.07 | 1.95 |

| Power–Delay [email protected]% (aJ) | 95.15 | 47.67 | 55.24 | 69.08 | 51.61 | 36.82 |

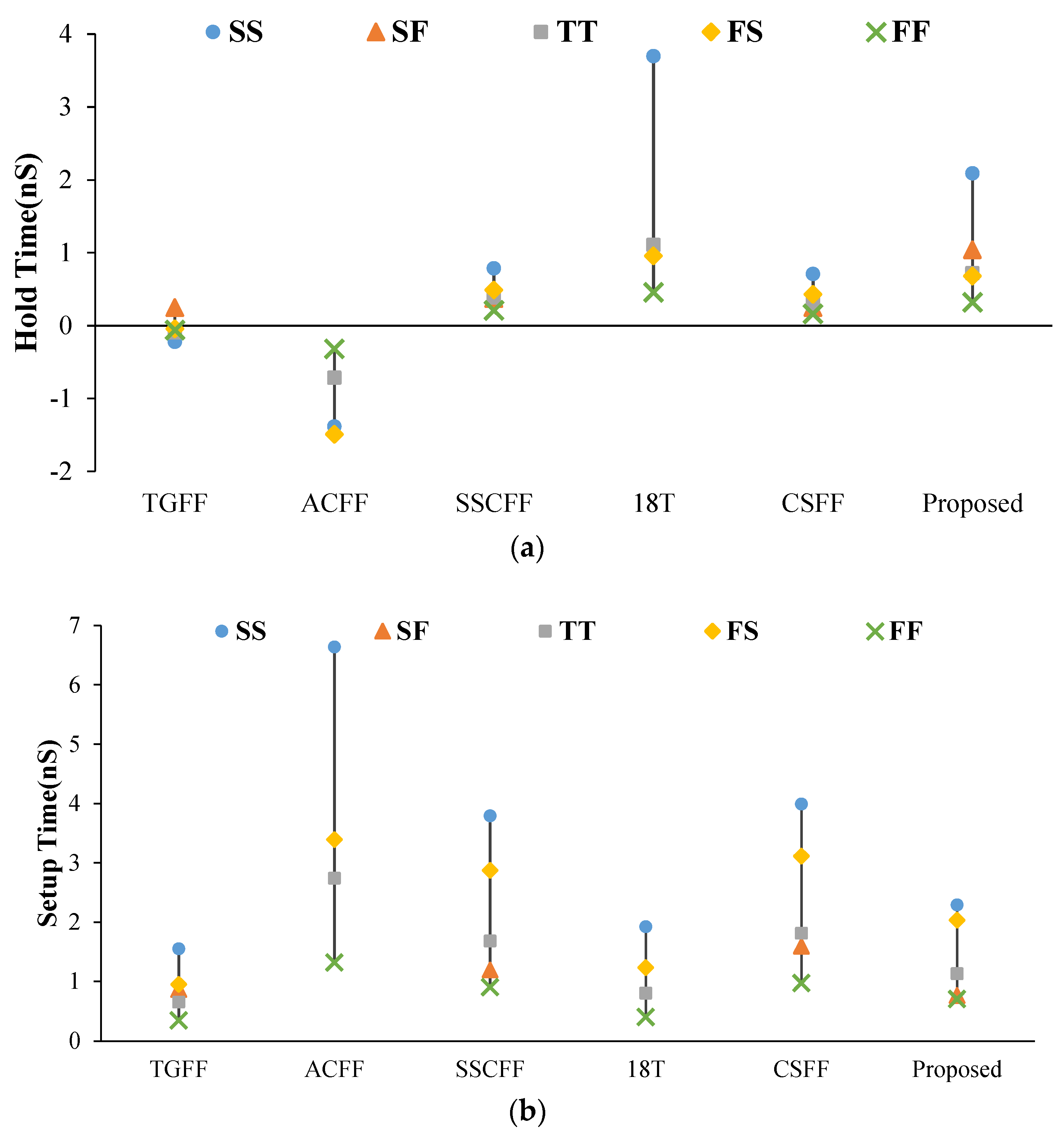

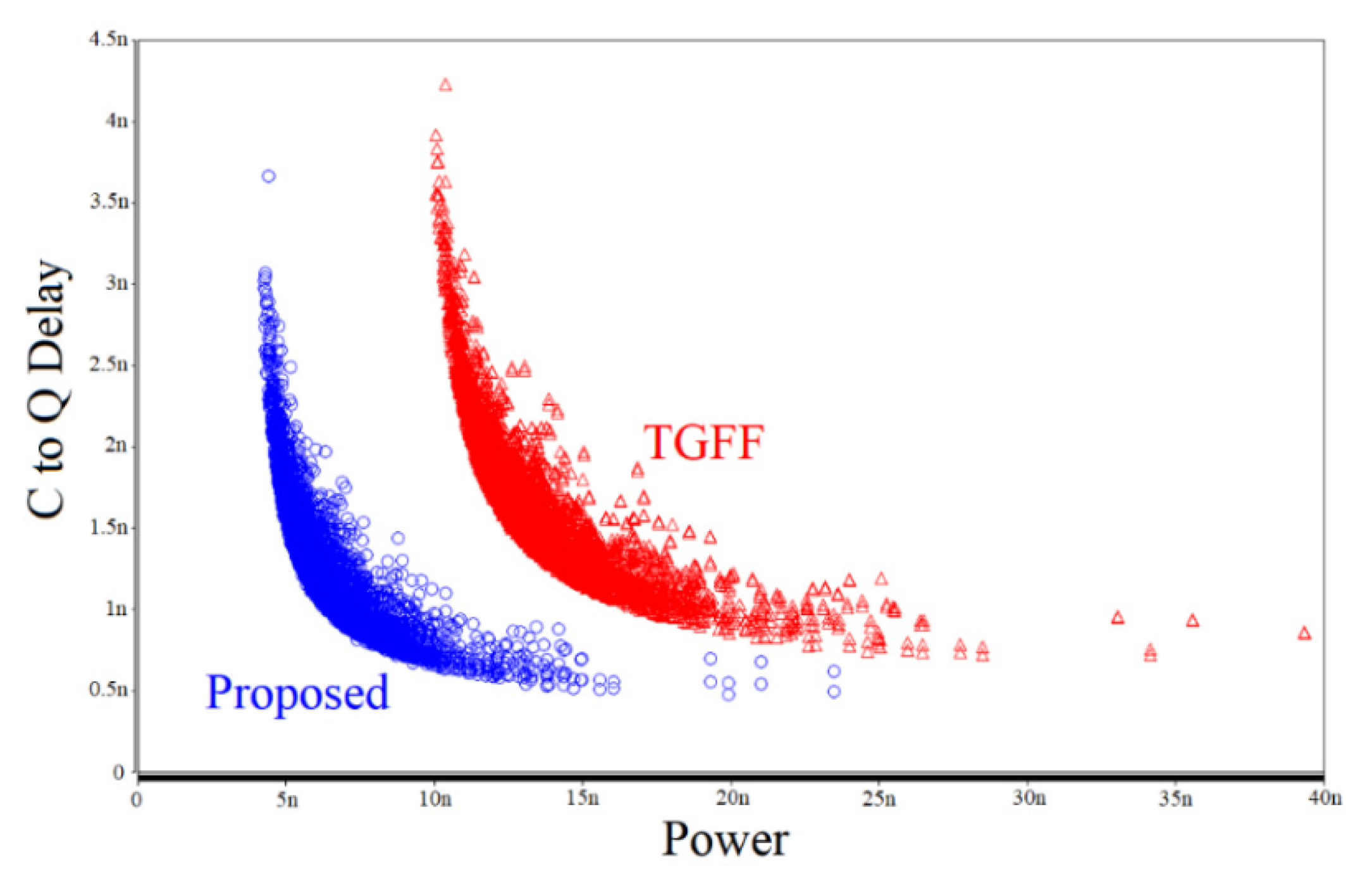

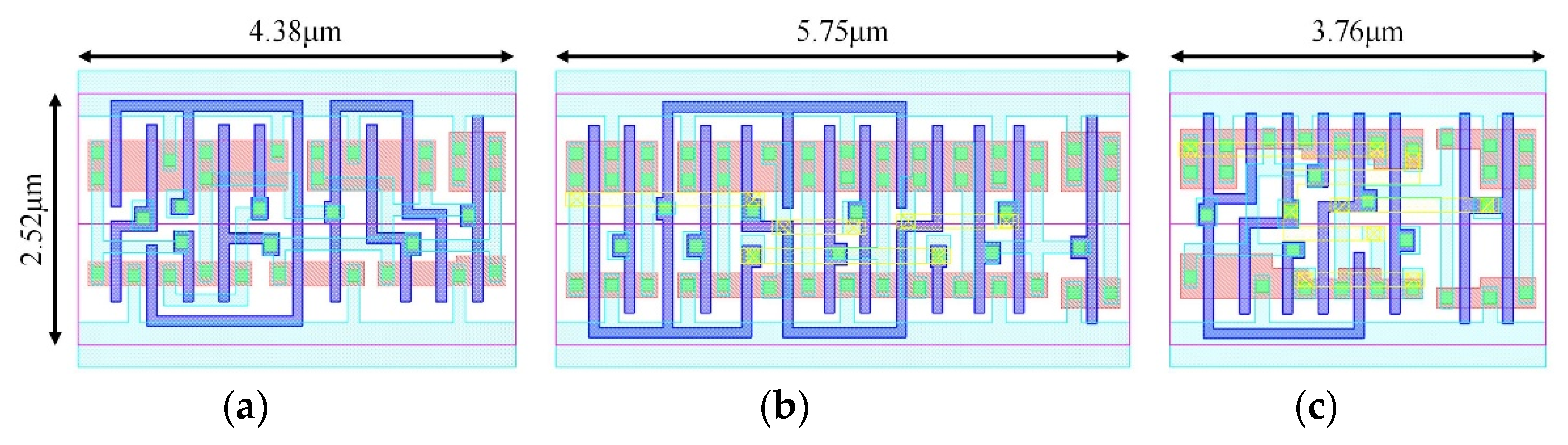

| FF Designs | TGFF | ACFF 1 | SSCFF | 18T | CSFF | Proposed |

|---|---|---|---|---|---|---|

| Cell Width(um) | 5.75 | 6.23 | 6.11 | 4.38 | 6.83 | 3.76 |

| Setup Time(nS) | 0.65 | 2.74 | 1.68 | 0.8 | 1.81 | 1.13 |

| Hold Time (nS) | −0.15 | −0.83 | 0.22 | 1.0 | 0.3 | 0.6 |

| CQ Delay(nS) | 1.67 | 1.31 | 1.85 | 1.75 | 1.86 | 1.32 |

| DQ Delay(nS) | 2.32 | 4.05 | 3.53 | 2.55 | 3.67 | 2.45 |

| Power@100% (nW) | 21.12 | 20.68 | 14.73 | 13.67 | 18.97 | 11.27 |

| Power@50% (nW) | 16.34 | 12.64 | 10.94 | 10.61 | 12.62 | 8.22 |

| Power@25% (nW) | 13.95 | 8.60 | 9.05 | 9.09 | 9.40 | 6.69 |

| [email protected]% (nW) | 12.75 | 6.58 | 8.10 | 8.32 | 7.80 | 5.92 |

| Power@0% (nW) | 11.56 | 4.61 | 7.16 | 7.56 | 6.22 | 5.16 |

| Power–Delay [email protected]% (aJ) | 21.29 | 8.62 | 14.99 | 14.56 | 14.50 | 7.84 |

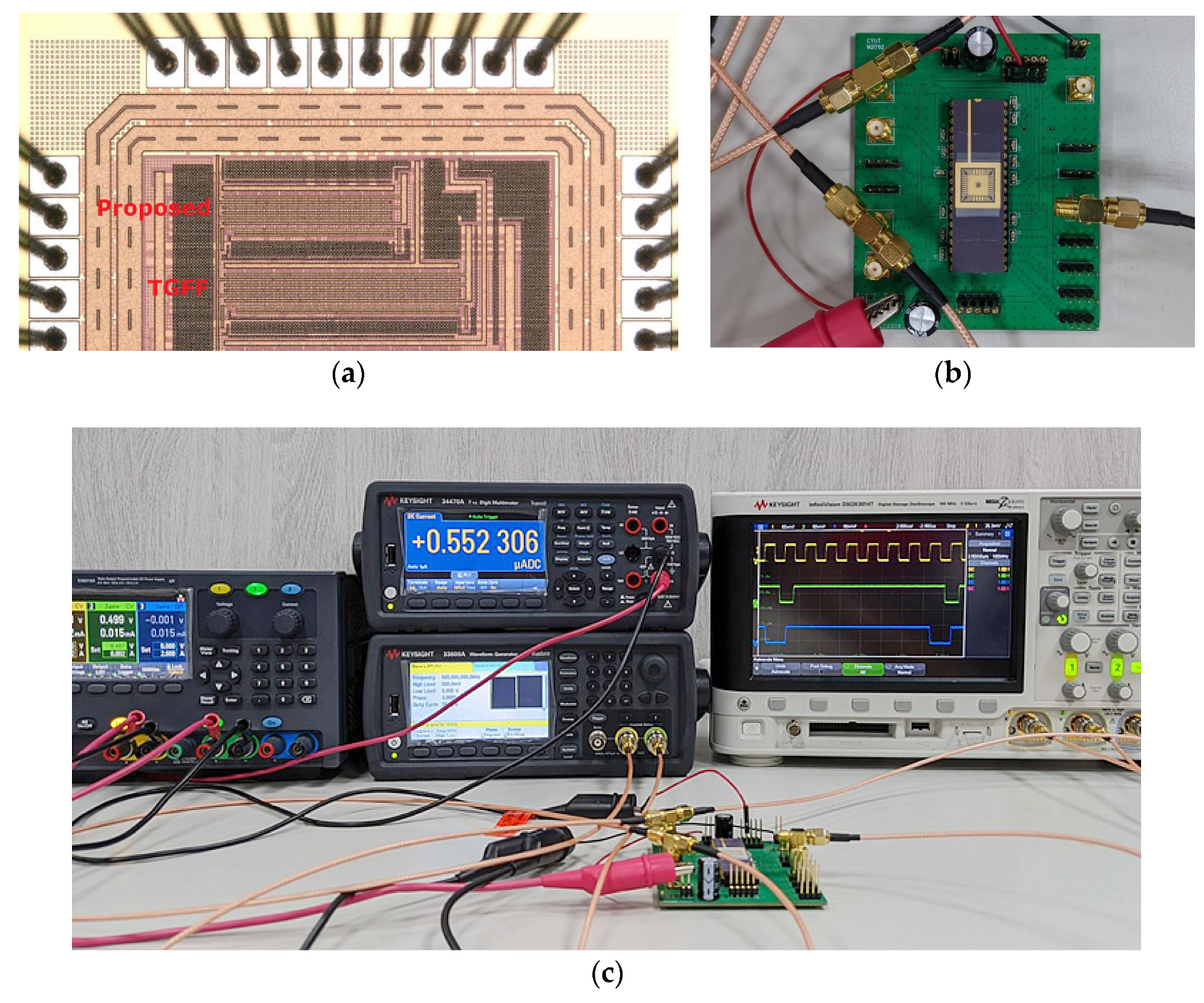

| 256-Bit Shift Registers | TGFF | Proposed |

|---|---|---|

| Layout Area (um2) | 15,979.7 | 11,104.7 |

| Average Power consumption (uW)-Simulation | 0.49 | 0.27 |

| Average Power Consumption (uW)-Measured | 0.55 | 0.29 |

Publisher’s Note: MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations. |

© 2022 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Lin, J.-F.; Hong, Z.-J.; Wu, J.-T.; Tung, X.-Y.; Yang, C.-H.; Yen, Y.-C. Low-Voltage and Low-Power True-Single-Phase 16-Transistor Flip-Flop Design. Sensors 2022, 22, 5696. https://doi.org/10.3390/s22155696

Lin J-F, Hong Z-J, Wu J-T, Tung X-Y, Yang C-H, Yen Y-C. Low-Voltage and Low-Power True-Single-Phase 16-Transistor Flip-Flop Design. Sensors. 2022; 22(15):5696. https://doi.org/10.3390/s22155696

Chicago/Turabian StyleLin, Jin-Fa, Zheng-Jie Hong, Jun-Ting Wu, Xin-You Tung, Cheng-Hsueh Yang, and Yu-Cheng Yen. 2022. "Low-Voltage and Low-Power True-Single-Phase 16-Transistor Flip-Flop Design" Sensors 22, no. 15: 5696. https://doi.org/10.3390/s22155696