## Proceeding Paper

# Effects of Electrical Stress in Solution-Processed Spin-On Glass Dielectric Films: Frequency Dependence <sup>+</sup>

Ovier Obregon, Salvador Alcantara, Susana Soto and Miguel A. Dominguez \*

Centro de Investigaciones en Dispositivos Semiconductores, Instituto de Ciencias, Benemérita Universidad Autónoma de Puebla (BUAP), Puebla 72570, Mexico; ovier.mectronica@gmail.com (O.O.); iniesta.salvador@gmail.com (S.A.); blanca.sotocruz@viep.com.mx (S.S.)

\* Correspondence: miguel.dominguezj@correo.buap.mx; Tel.: +52-(222)-229-55-00 (ext. 1043)

+ Presented at the 1st International Conference on Micromachines and Applications, 15–30 April 2021; Available online: https://micromachines2021.sciforum.net/.

**Abstract:** In this work, the effects of the frequency dependence of transparent dielectric based on Spin-on Glass (SOG) under electrical stress is presented. The SOG thin films were cured at 200 °C in ambient air. The capacitance-voltage and capacitance-frequency characteristics were measured in Metal-Oxide-Semiconductor (MOS) capacitors using the SOG thin film. In addition, electrical stress is applied to the MOS capacitors at different voltage values and during a long period of time. The results show, depending on the bias stress applied, a reversible interface charge contribution and an irreversible charge induced by interface states probably generated by the degradation of the film.

Keywords: solution-processed; electrical stress; spin-on glass

# 1. Introduction

Currently, the stability of field-effect devices based on emerging technologies is one of the most demanding research issues in terms of performance [1–5]. Since solution-processed electronic devices are attracting much attention to enable low-cost flexible electronics, the reported studies of stability seem to be conceived with arbitrary conditions. Frequently, they do not give explanation for the stress conditions used or the same values of electrical stress previously reported were considered, regardless the gate dielectric thickness and structure of the device [6–12]. Moreover, only few studies can be found in literature about this topic in solution-processed dielectric films [13].

Along with the material properties of each layer in the device, interface properties have a strong influence on the device performance. In this work, the effects of electrical stress in solution-processed dielectric film are presented. In particular, the frequency dependence of transparent dielectric based on Spin-on Glass (SOG) under electrical stress is presented. Electrical stress is applied to MOS capacitors at different voltage values and during a period of time. It is important to note that the SOG film was previously used as gate dielectric in planarized a-SiGe:H TFTs, flexible zinc nitride TFTs and flexible AZO diodes [14–16].

# 2. Materials and Methods

The SOG solution (SOG700B Filmtronics) was diluted 3:1 with Deionized Water (DI) and spin coated into the samples. The SOG/DI films were cured at 200 °C in air ambient. The complete fabrication process of the MOS capacitors is found elsewhere [17]. The capacitance-voltage and capacitance-frequency characteristics were measured using the Keithley-4200 Semiconductor Characterization System equipped with the 4200-CVU Integrated C-V, under dark conditions, ambient air and room temperature.

Citation: Obregon, O.; Alcantara, S.; Soto, S.; Dominguez, M.A. Effects of Electrical Stress in Solution-Processed Spin-On Glass Dielectric Films: Frequency Dependence. *Eng. Proc.* 2021, 4, 2. https://doi.org/ 10.3390/Micromachines2021-09543

Academic Editor: Ion Stiharu

Published: 14 May 2021

**Publisher's Note:** MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations.

**Copyright:** © 2021 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).

#### 3. Results and Discussion

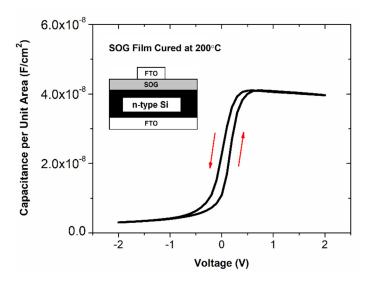

Figure 1 shows the capacitance-voltage characteristics for the n-type MOS capacitors. The characteristic shows a well-defined accumulation region when a positive voltage is applied at the top contact, as the positive voltage increases there is an accumulation of electrons at the dielectric-semiconductor interface (SOG-Si), increasing the capacitance. When a negative voltage is applied at the top contact, a depletion region is induced, then, the capacitance decreases [18].

Figure 1. Capacitance-voltage characteristics for the n-type MOS capacitors.

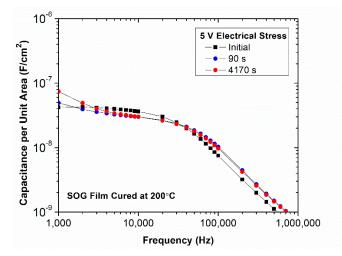

Field-effect devices, such as thin-film transistors, work in accumulation where the channel layer is formed at the dielectric-semiconductor interface. Therefore, in order to study the frequency dependence under electrical stress, the capacitance is measured in the accumulation region of the MOS capacitors (2 V). Figure 2 shows the frequency dependence of the MOS capacitors comparing the initial characteristics and after 5V electrical stress during different times. It can be observed as a frequency dependence, or also called frequency dispersion, at the initial measurement due to interface states [5,19]. On the other hand, the electrical stress induce charge trapping at the dielectric-semiconductor interface (interface charge). This interface charge causes variations in the accumulation capacitance [18–20]. It can be observed, that after a long stress time, the characteristics are very similar.

Figure 2. Frequency dependence characteristics for different stress time at 5 V electrical stress.

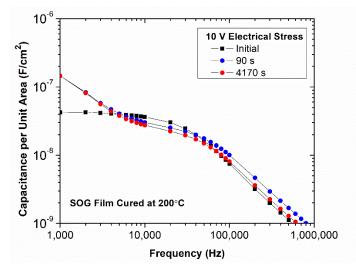

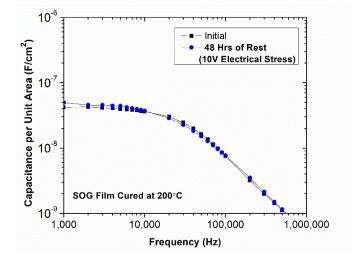

Figure 3 shows the frequency dependence characteristics for different stress times at 10 V applied. At high frequencies, the accumulation capacitance after electrical stress exhibit similar values than the initial measurement. However, it is clearly exhibited in an increase of the accumulation capacitance at 1–4 KHz due to the higher electrical stress. Some authors have reported a similar behavior in solution-processed dielectric films without electrical stress [21]. They suggest that this behavior can be due to residuals during the deposition of the films. Since our SOG dielectric films are deposited at low temperature, probably some residuals interact with the electrical stress, inducing additional charges. These induced charges can follow the low frequency contributing to the accumulation capacitance [22,23]. This behavior can be expected, since in solution-processed films the evaporation of solvents during the deposition and the low-temperature used, tends to make the films with high leakage current due to residuals [21,24]. In order to analyze these induced charges, the MOS capacitors were kept in rest for 48 h and measured again. Figure 4 shows the comparison of the initial and rested frequency dependence characteristics after the 10 V electrical stress. As can be seen, the characteristics are reestablished, indicating that most of the interface charge is reversible, as many authors suggest [25–30].

Figure 3. Frequency dependence characteristics for different stress times at 10 V electrical stress.

**Figure 4.** Comparison of the initial and 48 h rested capacitance-frequency characteristics after 10 V electrical stress.

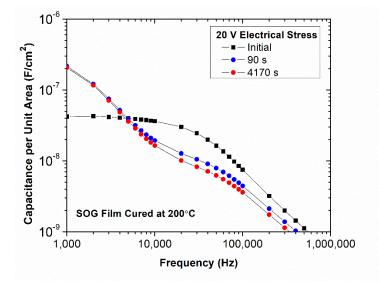

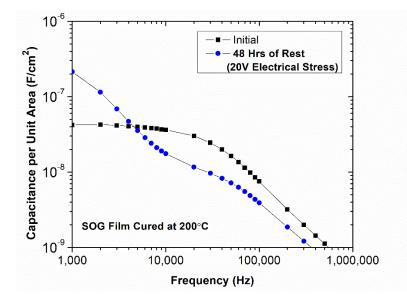

On the other hand, a higher electrical stress was induced by applying 20 V for different times (Figure 5). A clear dependence of capacitance with frequency can be appreciated. At higher frequencies, there is a decrease in the accumulation capacitance that can be related to a reduction of the accumulation charge in the MOS capacitor, due to the tunneling of electrons through the dielectric [20,31]. Additionally, the accumulation capacitance at 1–4 KHz is increased by the additional interface states. The MOS capacitors were kept in rest for 48 h and measured again. Figure 6 shows the initial and rested frequency dependence characteristics after 20 V electrical stress. It is appreciated that the characteristics are irreversible after 48 h of rest. This suggests that the higher electrical stress induce an irreversible degradation in the dielectric film by a higher tunneling rate through the dielectric, where these carriers slowly degrade the dielectric film making irreversible the effects of the electrical stress [30]. The degradation of the dielectric film by the tunneling of carriers can be correlated with the interaction of electrical stress and residuals in the film. These results can be useful to differentiate the reversible interface charge contribution and the irreversible charge induced by the degradation of the film. All these lead to find an optimum range of stability in the dielectric film to be used in the study of stability of solutionprocessed electronic devices, such as thin-film transistors.

Figure 5. Frequency dependence characteristics for different stress times at 20 V electrical stress.

**Figure 6.** Comparison of the initial and 48 h rested capacitance-frequency characteristics after 20 V electrical stress.

## 4. Conclusions

The effects of the frequency dependence in a transparent dielectric based on Spin-on Glass under electrical stress is presented. The capacitance-voltage characteristics for the n-type MOS capacitors shows a well-defined accumulation region with very low hysteresis. The low electrical stress induce charge trapping at the dielectric-semiconductor interface (interface charge) which causes variations in the accumulation capacitance. These variations in capacitance are reversible after a period of rest. The results suggest that high electrical stress induce a degradation of the film, resulted by the probable interaction of the residuals within the film with the electrical stress. This behavior is irreversible. This work presents a study to find an optimum range of stability in dielectric films under electrical stress.

**Supplementary Materials:** The following are available online at https://www.mdpi.com/2673-4591/4/1/2/s1.

**Funding:** This work was partially supported by Fondo Sectorial de Investigación para la Educación CONACYT-SEP Ciencia Basica [grant number A1-S-7888] and by VIEP-BUAP [grant number DJMA-EXC17-G].

Data Availability Statement: Data is contained within the article.

**Acknowledgments:** M. Dominguez thanks Filmtronics Inc. PA, USA for the supplies provided. O. Obregon would like to thank CONACYT-Mexico for the scholarship awarded.

**Conflicts of Interest:** The authors declare no conflict of interest. The funders had no role in the design of the study; in the collection, analyses, or interpretation of data; in the writing of the manuscript, or in the decision to publish the results.

#### References

- Karim, K.; Nathan, A.; Hack, M.; Milne, W. Drain-Bias Dependence of Threshold Voltage Stability of Amorphous Sil-icon TFTs. IEEE Electron. Device Lett. 2004, 25, 188–190.

- Takagi, K.; Nagase, T.; Kobayashi, T.; Naito, H. High operational stability of solution-processed organic field-effect transistors with top-gate configuration. Org. Electron. 2016, 32, 65–69, doi:10.1016/j.orgel.2016.02.011.

- Wahl, R.E.; Wang, F.; Chung, H.E.; Kunnen, G.R.; Yip, S.; Lee, E.H.; Pun, E.Y.B.; Raupp, G.B.; Allee, D.R.; Ho, J.C. Stability and Low-Frequency Noise in InAs NW Parallel-Array Thin-Film Transistors. *IEEE Electron. Device Lett.* 2013, 34, 765–767, doi:10.1109/led.2013.2250896.

- 4. Jeon, J.; Kim, J.; Ryu, M. Instability of an Amorphous Indium Gallium Zinc Oxide TFT under Bias and Light Illumi-nation. *J. Korean Phys. Soc.* **2011**, *58*, 158–162.

- Dominguez, M.A.; Pau, J.L.; Redondo-Cubero, A. Stability of zinc nitride thin-film transistors under positive and negative bias stress. Solid-State Electron. 2020, 171, 107841, doi:10.1016/j.sse.2020.107841.

- Jeong, Y.; Bae, C.; Kim, D.; Song, K.; Woo, K.; Shin, H.; Cao, G.; Moon, J. Bias-Stress-Stable Solution-Processed Oxide Thin Film Transistors. ACS Appl. Mater. Interfaces 2010, 2, 611–615, doi:10.1021/am900787k.

- 7. Jeng, J.-S. Improvement of transistor characteristics and stability for solution-processed ultra-thin high-valence niobium doped zinc-tin oxide thin film transistors. *J. Alloy. Compd.* **2016**, *676*, 86–90, doi:10.1016/j.jallcom.2016.03.166.

- 8. Su, B.-Y.; Chu, S.-Y.; Juang, Y.-D.; Liu, S.-Y. Effects of Mg doping on the gate bias and thermal stability of solution-processed InGaZnO thin-film transistors. *J. Alloy. Compd.* **2013**, *580*, 10–14, doi:10.1016/j.jallcom.2013.05.077.

- Oh, S.-I.; Woo, J.-M.; Jang, J.-H. Comparative Studies of Long-Term Ambiance and Electrical Stress Stability of IGZO Thin-Film Transistors Annealed Under Hydrogen and Nitrogen Ambiance. *IEEE Trans. Electron. Devices* 2016, 63, 1910–1915, doi:10.1109/ted.2016.2545742.

- 10. Zhan, R.; Dong, C.; Liu, P.-T.; Shieh, H.-P.D. Influence of channel layer and passivation layer on the stability of amorphous InGaZnO thin film transistors. *Microelectron. Reliab.* **2013**, *53*, 1879–1885, doi:10.1016/j.microrel.2013.05.007.

- Xu, H.; Xu, M.; Chen, Z.; Li, M.; Zou, J.; Tao, H.; Wang, L.; Peng, J. Improvement of Mobility and Stability in Oxide Thin-Film Transistors Using Triple-Stacked Structure. *IEEE Electron. Device Lett.* 2015, 37, 57–59, doi:10.1109/led.2015.2502990.

- 12. Kim, J.; Kim, J.; Jeong, S.; Jeong, J. Storage-period dependent bias-stress instability of solution-processed amorphous in-diumzinc-oxide thin-film transistors. *Curr. Appl. Phys.* **2015**, *15*, S64–S68.

- Kumar, A.; Mondal, S.; Kumar, S.G.; Rao, K.K. High performance sol-gel spin-coated titanium dioxide dielectric based MOS structures. *Mater. Sci. Semicond. Process.* 2015, 40, 77–83, doi:10.1016/j.mssp.2015.06.073.

- Dominguez, M.; Rosales, P.; Torres, A.; Flores, F.; Molina, J.; Moreno, M.; Luna, J.; Orduña, A. Planarized Ambipolar a-SiGe:H Thin-Film Transistors: Influence of the sequence of fabrication process. *Solid State Electron.* 2014, 99, 45–50, doi: 10.1016/j.sse.2014.06.024.

- 15. Dominguez, M.; Pau, J.; Redondo, A. Flexible Zinc Nitride Thin-Film Transistors Using Spin-On Glass as Gate Insulator. *IEEE Trans. Electron. Dev.* **2018**, *65*, 1014–1017, doi:10.1109/ted.2018.2797254.

- 16. Dominguez, M.A.; Luna-Lopez, J.A.; Ceron, S. Low-temperature ultrasonic spray deposited aluminum doped zinc oxide film and its application in flexible Metal-Insulator-Semiconductor diodes. *Thin Solid Films* **2018**, *645*, 278–281, doi:10.1016/j.tsf.2017.11.006.

- Dominguez, M.; Luna, J.; Moreno, M.; Orduña, A.; Garcia, M.; Alcantara, S.; Soto, S. Solution-processed transparent dielectric based on spin-on glass for electronic devices. *Rev. Mex. Fis.* 2016, 62, 282–284.

- 18. Neamen, D. Semiconductor Physics and Devices, 3th ed.; Mc. Graw Hill: New York, NY, USA, 2003.

- 19. Ke, M.; Yu, X.; Zhang, R.; Kang, J.; Chang, C.; Takenaka, M.; Takagi, S. Fabrication and MOS interface properties of ALD AlYO3/GeOx/Ge gate stacks with plasma post oxidation. *Microelectron. Eng.* **2015**, *147*, 244–248.

- 20. Schroder, D.K.; Rubin, L.G. Semiconductor Material and Device Characterization. *Phys. Today* **1991**, 44, 107, doi:10.1063/1.2810086.

- Yoo, Y.; Park, J.; Lee, K.; Lee, H.; Song, K.; Lee, S.; Baik, H. Solution-processed high-k HfO<sub>2</sub> gate dielectric processed under softening temperature of polymer substrates. J. Mater. Chem. C 2013, 1, 1651–1658.

- 22. Kaya, S.; Lok, R.; Aktag, A.; Seidel, J.; Yilmaz, E. Frequency dependent electrical characteristics of BiFeO<sub>3</sub> MOS capacitors. *J. Alloy. Compnd.* **2014**, *583*, 476–480.

- Zheng, C.; He, G.; Chen, X.; Liu, M.; Lv, J.; Gao, J.; Zhang, J.; Xiao, D.; Jin, P.; Jiang, S.; et al. Modification of band alignments and optimization of electrical properties of InGaZnO MOS capacitors with high-k HfOxNy gate dielectrics. *J. Alloy. Compd.* 2016, 679, 115–121, doi:10.1016/j.jallcom.2016.04.025.

- 24. Park, J.; Yoo, Y.; Lee, K.; Jang, W.; Oh, J.; Chae, S.; Baik, H. Low-Temperature, High-Performance Solution-Processed Thin-Film Transistors with Peroxo-Zirconium Oxide Dielectric. *ACS Appl. Mater. Interfaces* **2013**, *5*, 410–417.

- Subramaniam, A.; Cantley, K.D.; Stiegler, H.J.; Chapman, R.A.; Vogel, E.M. Submicron Ambipolar Nanocrystalline Silicon Thin-Film Transistors and Inverters. *IEEE Trans. Electron. Devices* 2011, 59, 359–366, doi:10.1109/ted.2011.2176737.

- Powell, M.J.; Van Berkel, C.; French, I.D.; Nicholls, D.H. Bias dependence of instability mechanisms in amorphous silicon thinfilm transistors. *Appl. Phys. Lett.* 1987, 51, 1242–1244, doi:10.1063/1.98692.

- Yang, Z.; Yang, J.; Meng, T.; Qu, M.; Zhang, Q. Influence of channel layer thickness on the stability of amorphous indium zinc oxide thin film transistors. *Mater. Lett.* 2016, 166, 46–50, doi:10.1016/j.matlet.2015.12.029.

- Cross, R.B.M.; De Souza, M.M. Investigating the stability of zinc oxide thin film transistors. *Appl. Phys. Lett.* 2006, 89, 263513, doi:10.1063/1.2425020.

- 29. John, F.; Conley, J. Instabilities in amorphous oxide semiconductor thin-film transistors. *IEEE Trans. Dev. Mater. Reliab.* 2010, 10, 460–474.

- Dominguez, M.A.; Obregon, O.; Luna-Lopez, J.A. Study of stability of solution-processed dielectric film under electrical stress. J. Alloy. Compd. 2016, 688, 893–896, doi:10.1016/j.jallcom.2016.07.126.

- Su, C.; Lietena, R.; Bakalova, P.; Tseng, W.; Dillemans, L.; Menghinia, M.; Smets, T.; Seo, J.; Locquet, J. Electrical proper-ties of magnesium oxide layers with different surface pretreatment on high mobility Ge1–xSnxand Ge MOS capacitors. *Appl. Surf. Sci.* 2014, 291, 31–34.