# Proceeding Paper FPGA Implementation of ECG Signal Processing for Use in a Neonatal Heart Rate Monitoring System <sup>†</sup>

Henry Dore <sup>(b)</sup>, Rodrigo Aviles-Espinosa and Elizabeth Rendon-Morales \*

Robotics and Mechatronics Systems Research Group, School of Engineering and Informatics, University of Sussex, Falmer BN1 9RH, UK

\* Correspondence: er241@sussex.ac.uk

+ Presented at the 9th International Electronic Conference on Sensors and Applications, 1–15 November 2022; Available online: https://ecsa-9.sciforum.net.

Abstract: A field-programmable gate array (FPGA) based system for digital filtering in a neonatal heart rate monitoring system is presented. The system employs electric potential sensors (EPS) and contains a single hardware filter stage for antialiasing. The remaining digital signal processing required to provide a clinical standard electrocardiogram (ECG) is performed on the FPGA (myRIO 1900, National Instruments Corporation of Austin, Austin, TX, USA). This is compared with a previous microprocessor version (Raspberry Pi 3, BCM2837 processor, Raspberry Pi Ltd, Cambridge, UK) containing a dual hardware/software filtering scheme, with the aim of simplifying the analog front end and allowing for reconfigurable filtering in the digital domain. A custom neonate phantom was employed to emulate real world conditions and ambient noise. The developed FPGA system was shown to have a signal quality comparable with the microprocessor implementation, with an average signal-to-noise ratio loss of 2%. A 12 dB increase in the attenuation of the predominant 50 Hz noise was shown, indicating filter effectiveness gains. The phantom was used to broadcast data from the preterm infant cardio-respiratory signals database (PICSDB) and the FPGA filtering scheme was shown to remove the majority of the ambient 50 Hz noise with an average reduction of 30 dB, and provided a clean ECG signal. These results demonstrate that FPGA-filtered EPS ECGs have comparable signal quality to the combined HW/SW filtering implementation, with a reduction in complexity and power consumption.

Keywords: heart rate; FPGA; ECG; newborn; medical devices; DSP; electric potential sensor

## 1. Introduction

The need for rapid and accurate heart rate (HR) measurement in the delivery room is well established, as it is the predominant quantitative indicator of a newborn's health and is monitored in the delivery room to guide clinical intervention and resuscitation efforts [1]. Our previous work describes a prototype microprocessor-based neonatal HR monitor [2] integrating novel electric potential sensors (EPS) into a standard delivery room neonatal mattress. EPS sensors do not require galvanic contact with the skin; therefore, high-resolution ECGs can be recorded without the need for a sensor attachment, allowing for rapid and accurate infant HR calculation. EPS sensors are highly susceptible to ambient noise however, predominantly 50/60 Hz power line interference. The requirement for high levels of filtering with EPS devices can be fulfilled by the use of hardware accelerators in place of traditional digital signal processing.

Field programmable gate-arrays (FPGAs) are reprogrammable logic devices, capable of parallel process execution and reconfiguration. FPGA based bio-signal filtering has been successfully applied to the ECG signal for powerline noise reduction [3] with efficiency savings over traditional digital signal processing (DSP), and FPGA implementations of beat detection algorithms used to measure heart rates have shown a 98% accuracy and real-time beat classification [4].

Citation: Dore, H.; Aviles-Espinosa, R.; Rendon-Morales, E. FPGA Implementation of ECG Signal Processing for Use in a Neonatal Heart Rate Monitoring System. *Eng. Proc.* 2022, *27*, 70. https://doi.org/ 10.3390/ecsa-9-13258

Academic Editor: Francisco Falcone

Published: 1 November 2022

**Publisher's Note:** MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations.

**Copyright:** © 2022 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https:// creativecommons.org/licenses/by/ 4.0/). FPGA system-on-chip (FPSoC) architectures provide dynamic partial reconfiguration (DPS) for runtime reconfiguration of the FPGA [5] which can replace static analog frontend elements such as analog hardware filters. This allows for adaptation to changing or intermittent noise sources.

This work considers the implementation of an FPGA-based digital filtering system for electrocardiogram reading using EPS sensors. Two platforms were tested: a microprocessorbased system with both hardware and software filters; and an FPGA-based system with a single-hardware low-pass filter stage for anti-aliasing, and software filtering. Both systems were characterised using a custom infant ECG phantom tailored for EPS sensor experimentation. Evaluation metrics for signal quality were defined including signal quality, noise rejection, and HR calculation accuracy. The end goal is to investigate whether the hardware filtering section can be removed and replaced with a purely digital filtering scheme implemented in FPGA hardware.

#### 2. Materials and Methods

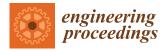

This work compares two neonatal HR monitoring platforms, these being the frontend for the EPS sensors: a traditional microprocessor-based system and a field-programmable gate array-based system, hereafter referred to as the  $\mu$ PU and FPGA systems, respectively. Both systems were connected to a pair of EPS sensors, with a textile reference electrode connected to each system ground. A subtraction is performed by a precision instrumentation amplifier (AD623, Analog Devices Inc., Wilmington MA, USA) to remove common mode noise and produce a single signal which is processed by the system front ends. Figure 1 shows a block system diagram of the EPS sensor connections to the frontend and system architecture elements.

Figure 1. EPS sensor connection and system architecture overviews for FPGA and µPU systems.

The  $\mu$ PU system is based on the Raspberry Pi 3 A+ with built-in hardware filtering, a 12-bit analog-to-digital converter (ADC) sampling at 1 kHz. A C++ DSP filtering runs on Raspbian Linux using the Broadcom 2837 Cortex-A53 (Raspberry Pi Ltd, Cambridge, UK). The resulting data were displayed on an integrated 7" touchscreen and graphical user interface. The FPGA system is based on a National Instruments myRIO 1900 platform with a front end for signal conditioning and alias filtering. A 12-bit ADC at a sample rate of 1 kHz matches that of the  $\mu$ PU system. Digital software filters were implemented in the FPGA portion of the Xilinx Z-7010 chip. Data storage and display is programmed in National Instruments LabVIEW.

## 2.1. Filtering

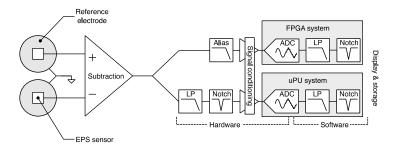

A 50 Hz notch filter to remove the dominant noise from powerline interference and a 200 Hz low-pass (LP) filter to remove any higher frequencies and harmonics of the fundamental 50 Hz noise were employed. These standard ECG filter specifications were chosen to avoid any alteration of the ECG signal [6], and allow the R peak of the ECG to be extracted accurately, enabling heartbeat interval and therefore HR calculation. Figure 2 shows the frequency response of the hardware and software filter stages.

Figure 2. (a) Hardware, (b) software low pass, and (c) software notch filter FRA.

Hardware filtering for the  $\mu$ PU system consists of a 2nd-order active twin-T Notch filter (corner frequency, fc = 50 Hz) and a 2nd-order active low pass filter (fc = 200 Hz) and the FPGA system contains a single 1st-order active low pass filter (fc = 500 Hz) for anti-aliasing, as shown in Figure 2a.

Both systems have the same software filters implemented in the FPGA or C++, respectively. To compare different levels of software filtering, 3 predefined filtering settings were chosen: Low/Medium/High. The level of high frequency (>200 Hz) attenuation for the LP filters is controlled by varying the filter order, thus creating a steeper roll-off as seen in Figure 2b. The level of 50 Hz attenuation is varied by varying the stopband frequencies either side of 50 Hz resulting in a deeper notch (Figure 2c).

#### 2.2. Neonate Phantom

A cardiac phantom was developed to mimic the interference layer of tissue between signal source and sensor, and to provide a signal ground path with similar conductivity to human tissue. It consists of a stack of layers modelling the voltage of the neonate heart and signal propagation through the human tissue, the cotton and foam material of the mattress.

Pharmaceutical-grade agar powder (Intralabs UK) used at 2% concentration (to reflect the elastic behaviour of skin) was mixed with a saline solution to increase the conductivity. A total of 1 mg NaCl per 100 mL was selected for an approximate conductivity of  $\approx 0.5$ Siemens/m to emulate the skin as described in [7]. Agar castings were then placed on top of an insulating base with a copper ground loop and voltage source emitter for signal generation.

The EPS sensors and ground reference electrodes (CuNi MOS Titan conductive fabric) were attached to a cotton substrate to mimic the top layer of a delivery room mattress. Electrodes were selected for biocompatibility, low electrical resistance and an impedance comparable with traditional ECG electrodes [8] of 100 k $\Omega$  at 50 Hz. To reproduce the compression due to an average birth weight infant (~3.4 kg), a weight of 140 g was placed on top of the phantom stack to achieve a realistic contact pressure of 260 Pa for the 5 cm × 10 cm stack.

#### 2.3. Signal Analysis

Signal to noise ratio (SNR) was calculated using the signal matching method [9]. A 2 Hz sine wave with amplitudes of Vpp = 25 mV, 50 mV, and 75 mV was transmitted to the phantom. EPS sensor voltages drop linearly with distance from the source, representing EPS voltages of 3.3, 6.7, and 10 mV, respectively, comparable to infant ECG voltage levels. Five 60 s recordings of the test signal were taken with both systems, then an idealised input sine wave was then generated, and cross-correlated with the recorded signal in MatLab. This was used to produce a noise estimate by subtracting the idealised sine wave from the recorded EPS output. The signal-to-noise ratio (SNR) in decibels of the signal is then derived by computing the ratio of its summed squared magnitude to that of the noise.

The phantom was used to transmit a generated neonate biosignal to the EPS sensors at an amplitude of 75 mVpp at 1, 2, and 3 Hz corresponding to 60, 120, and 180 bpm. This serves to examine the frequency components of the received signal, and to examine

the calculated HR and any system-induced heart rate variability. The Pan Tompkins HR detection algorithm [10] was applied to validate accurate HR calculation, and the heart rate variation (HRV) metric rrHRV [11] (computing the difference of consecutive RR intervals weighted by their mean) was also applied to the signals.

Finally, to test the filtering effectiveness of the proposed FPGA system with real world signals, the neonate phantom was used to broadcast 60 s samples of waveforms from the Preterm Infant Cardio-Respiratory Signals Database [12].

Data were recorded and processed in MatLab, and recordings were made simultaneously on both devices in a residential setting with no attempt to shield the devices from ambient interference that may be present.

## 3. Results

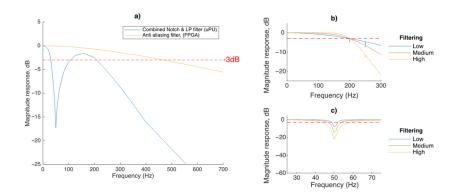

Figure 3 shows the results comparing the SNR of the DSP filtering of the FPGA system to the combined DSP and hardware filtering of the  $\mu$ PU at a range of signal amplitudes:

Figure 3. Signal-to-noise ratio for both systems at a range of signal amplitude and DSP filtering levels.

SNR is proportional to the signal amplitude as the predominant 50 Hz noise (external to the system) is fixed, so increasing signal amplitude increases the SNR. For the High filtering case (ideal scenario) the FPGA has a 15% reduction in SNR compared to the  $\mu$ PU system at the 25 mV signal level, but a 3% and 5% increase for the 50 mV and 75 mV signal levels, respectively. This gives the FPGA system an average SNR loss of 2% compared to the  $\mu$ PU system, indicating that the signal quality is comparable. The effect of increasing the level of filtering is modest, and for all the cases across both devices the High filtering level only generates a maximum 7% increase in SNR compared to the Low level. Comparing the unfiltered  $\mu$ PU cases, the effect of the hardware filtering stage is clear, accounting an average increase of 3 dB SNR compared to the unfiltered FPGA system.

Figure 4 shows the power spectral density (PSD) using the Welch estimate method for a generated neonate biosignal transmitted to the phantom with an amplitude of 75 mVpp at 120 Hz.

Figure 4. PSD of a generated neonate biosignal for (a)  $\mu$ PU system, (b) FPGA system.

For both cases, without DSP filtering, the 50 Hz noise peak can be seen clearly, although it has a lower amplitude for the  $\mu$ PU system given that the signal has already been prefiltered using the hardware filtering. The varied levels of DSP filtering provide greater 50 Hz attenuation for the FPGA system at 29.2, 33.8, and 40.4 dB for low/medium/high, respectively, and just 28 dB for the  $\mu$ PU across all 3 DSP filtered cases. The effect of the increased DSP filtering levels is clear for all the LP filters, with increasing roll-off visible for both systems above 200 Hz, closely matching the frequency response analysis in Figure 2b,c. The results of the HR validation and HR variation analysis are presented in Table 1, to quantify the temporal accuracy of both systems.

Table 1. HR and HRV analysis at a range of heart rates.

| Generated HR [bpm]   | μ <b>PU</b> |      |      | FPGA |      |      |

|----------------------|-------------|------|------|------|------|------|

|                      | 60          | 120  | 180  | 60   | 120  | 180  |

| Calculated HR, [bpm] | 60          | 120  | 180  | 60   | 120  | 179  |

| rrHRV, median        | 0.22        | 0.62 | 0.81 | 0.14 | 0.28 | 0.42 |

In this test, the two systems produced HRs within 1 bpm of the generated signals, confirming the accuracy of the signal reproduction. The HRV analysis showed increasing RR interval deviation for increasing bpm due to the fixed 1 kHz sample rate of the devices, where higher frequency input samples become less temporally accurate due to sample timing errors in discretisation.

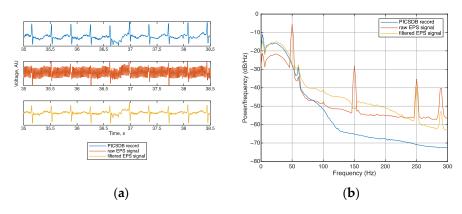

A sample of the results of the PICSDB waveform testing of the FPGA system is shown in Figure 5:

**Figure 5.** A sample illustrating filtering of the PICSDB data record ecg8, showing (**a**) sample waveforms and (**b**) power spectral density.

Figure 5a shows the original signal, the effect of the addition of ambient 50 Hz noise in the raw EPS signal, and the filtered EPS signal showing the removal of noise and return to original waveform morphology. The R peak of the ECG is clearly visible in the filtered signal, albeit with some reduction in amplitude. Features of the ECG such the baseline wander just after the 36.5 s mark were preserved in the filtered signal, showing that no major morphological changes occur in the waveform. In Figure 5b the PSD of PICSDB record, raw signal, and filtered signal are shown. The susceptibility of EPS sensors to 50 Hz noise is clear in the peaks at 50 Hz and also 150 Hz harmonic. The FPGA-based filtering scheme removed an average of 30 dB of 50 Hz noise via the notch filter, and the steep roll-off of the 200 Hz LP filter removed the higher-order harmonics.

### 4. Discussion & Conclusions

Signal quality for the proposed FPGA DSP system is broadly equivalent to the  $\mu$ PU with hardware and software filtering, with an average SNR loss of just 2%. The frequency response of the FPGA is shown to have up to twice as much 50 Hz noise attenuation for the highest filtering setting compared with the  $\mu$ PU system. Heart rate variability measurements using a HR detection algorithm and analysis of detected RR interval changes show that both systems produce ECGs suitable for the accurate calculation of heart rates (within 1 bpm of the generated signal).

This work has introduced an FPGA-based DSP filtering system for the monitoring of newborn ECG signal using electric potential sensors, validating its performance using a neonate phantom with a high resolution, low amplitude bio-signals, and a human tissue phantom. The system is characterised and compared to a previous prototype with microprocessor-based software DSP. The FPGA system is shown to have the same filtering capabilities compared to the  $\mu$ PU system, despite the lack of hardware filtering stage, and consuming up to 90% less energy per sample filtered. The FPGA system recorded ECGs suitable for the accurate calculation of HR, and with less HR variation than the  $\mu$ PU system. This work contains strong evidence that sufficient filtering capacity is available purely in the digital domain by harnessing FPGA technology.

**Author Contributions:** Conceptualization, E.R.-M.; investigation, H.D.; methodology, R.A.-E. and E.R.-M.; software, H.D.; supervision, R.A.-E. and E.R.-M.; writing—original draft, H.D.; writing—review and editing, R.A.-E. and E.R.-M. All authors have read and agreed to the published version of the manuscript.

**Funding:** Henry Dore would like to acknowledge the University of Sussex scholarship for the financial support provided/Higher Education Innovation fund 2020/EPSRC-Engineering and Physical Sciences Research Council E-futures Sandpit award number RES/0560/7386/004.

Institutional Review Board Statement: Not applicable.

Conflicts of Interest: The authors declare no conflict of interest.

# References

- Wyllie, J.; Bruinenberg, J.; Roehr, C.C.; Rüdiger, M.; Trevisanuto, D.; Urlesberger, B. European Resuscitation Council Guidelines for Resuscitation 2015: Section 7. Resuscitation and support of transition of babies at birth. *Resuscitation* 2015, 95, 249–263. [CrossRef] [PubMed]

- Dore, H.; Aviles-Espinosa, R.; Luo, Z.; Anton, O.; Rabe, H.; Rendon-Morales, E. Characterisation of Textile Embedded Electrodes for Use in a Neonatal Smart Mattress Electrocardiography System. Sensors 2021, 21, 999. [CrossRef] [PubMed]

- 3. Bhaskar, P.; Uplane, M. FPGA based notch filter to remove PLI noise from ECG. *Int. J. Recent Innov. Trends Comput. Commun* 2015, 3, 2246–2250. [CrossRef]

- Alhelal, D.; Aboalayon, K.A.I.; Daneshzand, M.; Faezipour, M. FPGA-based denoising and beat detection of the ECG signal. In Proceedings of the 2015 Long Island Systems, Applications and Technology, Farmingdale, NY, USA, 1 May 2015; pp. 1–5. [CrossRef]

- Abdelkrim; Othman, S.B.H.; Saoud, S.B. Reconfigurable SoC FPGA based: Overview and trends. In Proceedings of the 2015 2017 International Conference on Advanced Systems and Electric Technologies (IC\_ASET), Hammamet, Tunisia, 14–17 January 2017; pp. 378–383.

- 6. Fedotov, A.A. Selection of Parameters of Bandpass Filtering of the ECG Signal for Heart Rhythm Monitoring Systems. *Biomed. Eng.* **2016**, *50*, 114–118. [CrossRef]

- Gabriel, S.; Lau, R.; Gabriel, C. The dielectric properties of biological tissues: II. Measurements in the frequency range 10 Hz to 20 GHz. *Phys. Med. Biol.* 1996, 41, 2251. [CrossRef] [PubMed]

- Rattfält, L.; Lindén, M.; Hult, P.; Berglin, L.; Ask, P. Electrical characteristics of conductive yarns and textile electrodes for medical applications. *Med. Biol. Eng. Comput* 2007, 45, 1251–1257. [CrossRef] [PubMed]

- Wang, T.; Zhang, H.; Lin, S. Influence of Capacitive Coupling on High-Fidelity Non-contact ECG Measurement. *IEEE Sens. J.* 2020, 20, 9265–9273. [CrossRef]

- Pan, J.; Tompkins, W.J. A Real-Time QRS Detection Algorithm. *IEEE Trans. Biomed. Eng.* **1985**, *32*, 230–236. [CrossRef] [PubMed]

Vollmer, M. A Robust, Simple and Reliable Measure of Heart Rate Variability using Relative RR Intervals. In Proceedings of the 2015 Computing in Cardiology Conference (CinC), Nice, France, 6–9 September 2015.

- 12. Gee, A.H.; Barbieri, R.; Paydarfar, D.; Indic, P. Predicting Bradycardia in Preterm Infants Using Point Process Analysis of Heart Rate. *IEEE Trans. Biomed. Eng.* 2017, 64, 2300–2308. [CrossRef] [PubMed]