Proceedings

# A Tunable CMOS Image Sensor with High Fill-Factor for High Dynamic Range Applications †

Fernando de Souza Campos 1,\*, Bruno Albuquerque de Castro 1 and Jacobus W. Swart 2

- <sup>1</sup> Electrical Engineering Department, Sao Paulo State University, 01049-010 Sao Paulo, Brazil; bruno.castro@unesp.br

- <sup>2</sup> Center of Semiconductor Components and Nanotechnologies, 6101 São Paulo, Brazil; jacobus@fee.unicamp.br

- \* Correspondence: fernando.campos@unesp.br

- † Presented at the 7th International Electronic Conference on Sensors and Applications, 15–30 November 2020; Available online: https://ecsa-7.sciforum.net/.

Published: 14 November 2020

**Abstract:** Several CMOS imager sensors were proposed to obtain high dynamic range imager (>100 dB). However, as drawback these imagers implement a large number of transistors per pixel resulting in a low fill factor, high power consumption and high complexity CMOS image sensors. In this work, a new operation mode for 3 T CMOS image sensors is presented for high dynamic range (HDR) applications. The operation mode consists of biasing the conventional reset transistor as active load to photodiode generating a reference current. The output voltage achieves a steady state when the photocurrent becomes equal to the reference current, similar to the inverter operation in the transition region. At a specific bias voltage, the output swings from o to Vdd in a small light intensity range; however, high dynamic range is achieve using multiple readout at different bias voltage. For high dynamic range operation different values of bias voltage can be applied from each one, and the signal can be captured to compose a high dynamic range image. Compared to other high dynamic range architectures this proposed CMOS image pixel show as advantage high fillfactor (3 T) and lower complexity. Moreover, as the CMOS pixel does not operate in integration mode, de readout can be performed at higher speed. A prototype was fabricated at  $3.3~V~0.35~\mu m$ CMOS technology. Experimental results are shown by applying five different control voltage from 0.65 to 1.2 V is possible to obtain a dynamic range of about 100 dB.

**Keywords:** CMOS; dynamic range; image sensor; photodetector

## 1. Introduction

Several image sensor applications, such as in the biomedical, robotics and surveillance areas, require imaging systems with a high dynamic range. Typically, imagers for these applications are required to capture scenes with dynamic ranges ~100 dB. However, conventional CMOS image sensors possess dynamic ranges of only ~60 dB. Therefore, many techniques were proposed to achieve high dynamic ranges using CMOS image sensors [1–6]. In [2], by integrating a comparator and a dynamic flip-flop in each pixel, a multi-sampling technique was proposed. In [3], a self-reset technique using one comparator per pixel was described. In general, these techniques are effective as they achieved a dynamic range >100 dB. However, they both require a large number of transistors per pixel, resulting in a low fill factor, high power consumption and high complexity.

More recently, techniques using analog-to-digital converters have been proposed as methods to obtain high dynamic range with high fill-factor and low pixel complexity [7–12]. However, these approaches achieve dynamic ranges of 70–80 dB, which is too low for some applications. Therefore,

there is still a need to improve the performance of CMOS active pixel sensors with respect to high dynamic ranges, high fill-factors and low complexity [13,14].

In this work, we propose a new control method of 3 T CMOS active pixel sensors for high dynamic range applications. It maintains a high fill-factor and low complexity compared to main topologies of high dynamic range CMOS image sensors. The main different concept is to keep the reset transistor biased, generating a reference current. The steady-stated of pixel occurs when the photocurrent equal to the charge transistor current. The output voltage varies from 0 to  $V_{\rm dd}$  as a quadratic function of the photocurrent generated (light intensity). The prototype was design at 3.3 V 0.35  $\mu$ m CMOS technology. Measurement results are presented for voltage biased of 0.65, 0.74, 0.84, 1 and 1.2 V. In general, our measurements results show that for reset transistor operating at moderate inversion (0.65, 0.74 and 0.84 V) the output voltage range is about one decade of light intensity. For operation at strong inversion (1 and 1.2 V) the output voltage range covers 0.5 decades or less. By combining the five different measurements it is possible to assemble a 100 dB dynamic range image.

### 2. Operation Mode

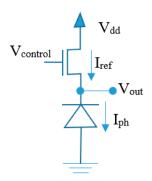

Figure 1 shows the typical 1T pixel architecture. It is composed of a charge transistor (M<sub>1</sub>) and a photodiode. A source follower and a select transistor must be also implemented to connect to the output bus; however, for only a pixel analysis purpose they were not implemented. An external ultralow bias input buffer was implemented. The charge transistor is biased at a constant voltage ( $V_{control}$ ), establishing a reference current ( $I_{ref}$ ) that defines the maximum photocurrent measured in the pixel.

Figure 1. Pixel architecture.

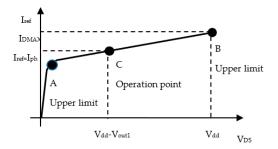

Considering that the operation starts at  $V_{out} = 0$  V (see point A—Figure 2) and assuming that the reset transistor's current is higher than the photocurrent, the photodiode's capacitance voltage ( $V_{out}$ ) starts to increase due to the difference between the photocurrent and the charge transistor current through the photodiode's capacitance. As the photodiode's voltage increases, the reset transistor  $V_{DS}$  starts to decrease. Being initially in the saturation region (see point A—Figure 2a), the charging transistor's drain current  $I_{ref}$  reduces accordingly as  $V_{DS}$  reduces. A steady state is achieved when the photocurrent  $I_{PH}$  becomes equals to the charging drain current  $I_{ref}$  (see point B in Figure 2).

Figure 2. Operation points.

Basically, the output voltage swings from  $V_{dd}$  to  $V_{DSSAT}$  while the related photocurrent swings from  $I_{ref}(V_{dd})$  to  $I_{refsat}(V_{DSSat})$ . Therefore, the current variation of the reset transistor over the saturation region defines the photocurrent range measured. Considering the typical V-I relationship of MOSFET

$$I_{D} = \mu C_{ox} \frac{W}{L} (V_{GS} - V_{T})^{2} (1 - \lambda V_{DS})$$

(1)

and knowing that  $V_{DS} = V_{OUT} - V_{dd}$  and  $I_D = I_{PH}$ , Equation (1) can be written as:

$$V_{OUT} = -\frac{L}{W} \frac{1}{\lambda \mu C_{ox} (V_{GS} - V_T)^2} I_{PH} + V_{dd} + \frac{1}{\lambda}$$

(2)

Equation (2) shows how the output voltage changes with photocurrent for reset transistor operating at saturation region and  $V_{GS} > V_T$ .

#### 3. Material and Methods

A light source Spectra Physics with a tungsten halogen lamp illuminates the IC pixel a 550nm filter. An external low bias buffer (femtoamperes) was used to connect the pixel output to a Tektronix oscilloscope. The optical power is varied by changing current lamp. A power meter with a calibrated photodetector (Newport) was used to measure the optical power at the same position as where the chip was placed. For a fixed  $V_{control}$  value, the light intensity was increased until the output voltage swung from 0 to  $V_{dd}$ .

#### 4. Results and Discussion

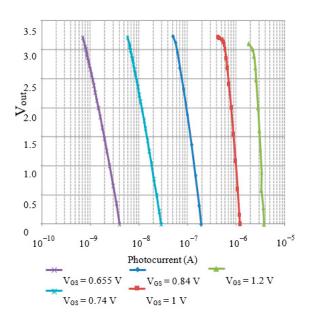

A prototype was fabricated at 0.35  $\mu$ m 3.3 V AMS CMOS technology. The pixel comprised a 10  $\mu$ m × 10  $\mu$ m Nwell-Psub photodiode and a W/L = (0.4  $\mu$ m/0.4  $\mu$ m) presenting fill-factor about 80%. Figure 3 shows the output voltage of the pixel obtained from measurements at five different control voltages. As one can see, the pixel photoresponse curves at  $V_{GS}$  = 1.2 V and  $V_{GS}$  = 1.0 V the output voltage range is about 3 V and the dynamic range is very small, less than 20 dB. This biasing condition and photoresponse is characterized by the pixel operating at strong inversion. The pixel photoresponse curves at  $V_{GS}$  = 0.84 V,  $V_{GS}$  = 0.74 V and  $V_{GS}$  = 0.65 V the output voltage range is about 3 V, and the dynamic range is small but is higher increasing toward 20 dB as  $V_{GS}$  reduces.

Figure 3. Pixel photoresponse: output voltage versus light intensity at five different control voltages.

Although the photoresponse shows small dynamic range, by using multiples captures from the five control voltages it is possible to achieve five decades of photocurrent values or images with a 100 dB dynamic range. Moreover, the new operation mode with small dynamic range allows us to see small contrasting image parts at conventional pixels become a full N bits image. Therefore, the small dynamic tunned photoresponse gives us a unique characteristic to offer an enhanced image of small contrasting images, which has been very attractive for surveillance and medical camera applications.

Compared to most linear CMOS active pixels with high dynamic ranges [1–6], the main advantage of our proposed pixel is to integrate a small number of transistors per pixel, thus achieving a higher fill-factor and small pixel complexity. In general, the fill factor of HDR architecture in the literature [1–6] varies from 15 to 50% in while our 4T pixel has a fill-factor of ~80% using a 10  $\mu$ m × 10  $\mu$ m photodiode. The main drawback of low fill-factor is the reduction of the global quantum efficiency 15.

## 3. Conclusions

A new operation mode for a 3 T CMOS image sensor prototype fabricated at 0.35 µm 3.3 V AMS CMOS technology for high dynamic range is presented. The pixel output voltage is related to photocurrent and it is controlled (tunned) by a voltage. For operation at only one bias voltage the output shows less 10 decades of dynamic range. This application allows a typical low contrast image portion at full N bits image, providing image enhancement. Multiples captures using multiples bias voltages allows us to achieve a dynamic range image equal to or greater than 100 dB. The fill-factor is about only 80% and it is very much higher than typical high dynamic range imager architectures. As an overall characteristic, this new control method comprises a conventional 3 T pixel architecture offering a simultaneously high dynamic range, high fill-factor, low pixel complexity and wide output swing range. Moreover, for a small dynamic range this pixel can be used for tuned image enhanced cameras.

#### References

- 1. Belenky, A.; Fish, A.; Spivak, A.; Yadid-Pecht, O. A snapshot CMOS image sensor with extended dynamic range. *IEEE Sens. J.* **2009**, *9*, 103–111.

- 2. Campos, F.S.; Marinov, O.; Faramarzpour, N.; Saffih, F.; Deen, M.J.; Swart, J.W. A multisampling time-domain CMOS imager with synchronous readout circuit. *Analog Int. Circuits Signal Proc.* **2008**, *57*, 151–159.

- 3. Park, D.; Rhee, J.; Joo, Y. A wide dynamic-range CMOS image sensor using self-reset technique. *IEEE Dev. Lett.* **2007**, *28*, 890–892.

- 4. McIlrath, L.G. A low-power low-noise ultrawide-dynamic range CMOS imager with pixel-parallel A/D conversion. *IEEE J. Solid-State Circuits* **2001**, *36*, 846–853.

- 5. Yang, D.; El Gamal, A.; Fowler, B.; Tian, H. A 640 × 512 CMOS image sensor with ultra wide dynamic range floating point pixel level ADC. *IEEE J. Solid-State Circuits* **1999**, *34*, 1821–1834.

- 6. Decker, S.; McGrath, R.D.; Brehmer, K.; Sodini, G. A 256 × 256 CMOS imaging array with wide dynamic range pixels and column parallel digital output. *IEEE J. Solid-State Circuits* **1998**, 33, 2081–2091.

- 7. Seo, M.-W.; Sawamoto, T.; Akahori, T.; Liu, Z.; Iida, T.; Takasawa, T.; Kosugi, T.; Watanabe, T.; Isobe, K.; Kawahito, S. A low-noise high-dynamic-range 17b 1.3-Megapixel 30-fps CMOS image sensor with column-parallel two-stage folding-integration/cyclic ADC. *IEEE Trans. Electron. Devices* **2012**, *59*, 3396–3400.

- 8. Ignjatovic, Z.; Maricic, D.; Bocko, M.F. Low power, high dynamic range CMOS image sensor employing pixel-level oversampling  $\Sigma\Delta$  analog-to-digital conversion. *IEEE Sens. J.* **2012**, *12*, 737–746.

- 9. Seo, M.W.; Suh, S.-H.; Iida, T.; Takasawa, T.; Isobe, K.; Watanabe, T.; Itoh, S.; Yasutomi, K.; Kawahito, S. A low-noise high intrascene dynamic range CMOS image sensor with a 13 to 19b variable-resolution column-parallel folding-integration/cyclic ADC. *IEEE J. Solid-State Circuits* **2012**, *47*, 272–283.

- Chae, Y.C.; Cheon, J.M.; Lim, S.H.; Kwon, M.H.; Yoo, K.S.; Jung, W.K.; Lee, D.H.; Ham, S.H.; Han, G.H. A

2.1 M pixels, 120frames/s CMOS image sensor with column-parallel ΔΣ ADC architecture. *IEEE J. Solid-State Circuits* 2011, 46, 236–247.

- 11. Park, J.H.; Ayoama, S.; Watanabe, T.; Isobe, K.; Kawahito, S. A high-speed low noise CMOS image sensor with 13-b column-parallel single-ended cyclic ADCs. *IEEE Trans. Electron. Devices* **2009**, *56*, 2414–2422.

12. Furuta, M.; Nishikawa, Y.; Kawahito, S. A high-speed, high-sensitivity digital CMOS image sensor with a global shutter and 12-bit column-parallel cyclic A/D converter. *IEEE J. Solid-State Circuits* **2007**, 42, 766–774.

- 13. El-Desouki, M.M.; Palubiak, D.; Deen, M.J.; Fang, Q.; Marinov, O. A Novel, High Dynamic Range, High Speed and High Sensitivity CMOS Imager Using Time-Domain Single Photon Counting and Avalanche Photodiodes. *IEEE Sens. J.* **2011**, *11*, 1078–1083.

- 14. Campos, F.S.; Faramarzpour, N.; Marinov, O.; Deen, M.J.; Swart, J.W. Photodetection with Gate-Controlled Lateral BJTs from Standard CMOS Technology. *IEEE Sens. J.* **2013**, *13*, 1554–1563.

- 15. Faramarzpour, N.; El-Desouki, M.M.; Deen, M.J.; Shirani, S.; Fang, Q. CMOS Photodetector Systems for Low-Level Light Applications. *J. Mater. Sci. Mater. Electron.* **2009**, 20, S87–S93.

**Publisher's Note:** MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations.

© 2020 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).