# Article Fabrication Process for On-Board Geometries Using a Polymer Composite-Based Selective Metallization for Next-Generation Electronics Packaging

Sarthak Acharya <sup>1,2,\*</sup>, Shailesh Singh Chouhan <sup>1</sup> and Jerker Delsing <sup>1</sup>

- <sup>1</sup> Embedded Internet System Laboratory, Department of Computer Science, Electrical & Space Engineering, Luleå University of Technology, 971 87 Luleå, Sweden; Shailesh.chouhan@ltu.se (S.S.C.); Jerker.Delsing@ltu.se (J.D.)

- <sup>2</sup> Department of Information Technology & Electrical Engineering, University of Oulu, 90570 Oulu, Finland

- \* Correspondence: acharya.sarthak@ltu.se or sarthak.acharya@oulu.fi

Abstract: Advancements in production techniques in PCB manufacturing industries are still required as compared to silicon-ICs fabrications. One of the concerned areas in PCBs fabrication is the use of conventional methodologies for metallization. Most of the manufacturers are still using the traditional Copper (Cu) laminates on the base substrate and patterning the structures using lithography processes. As a result, significant amounts of metallic parts are etched away during any mass production process, causing unnecessary disposables leading to pollution. In this work, a new approach for Cu metallization is demonstrated with considerable step-reducing pattern-transfer mechanism. In the fabrication steps, a seed layer of covalent bonded metallization (CBM) chemistry on top of a dielectric epoxy resin is polymerized using actinic radiation intensity of a 375 nm UV laser source. The proposed method is capable of patterning any desirable geometries using the above-mentioned surface modification followed by metallization. To metallize the patterns, a proprietary electroless bath has been used. The metallic layer grows only on the selective polymer-activated locations and thus is called selective metallization. The highlight of this production technique is its occurrence at a low temperature (20-45 °C). In this paper, FR-4 as a base substrate and polyurethane (PU) as epoxy resin were used to achieve various geometries, useful in electronics packaging. In addition, analysis of the process parameters and some challenges witnessed during the process development are also outlined. As a use case, a planar inductor is fabricated to demonstrate the application of the proposed technique.

**Keywords:** surface modification; functionalization; selective metallization; laser assisted fabrication; CBM chemistry; electronics packaging; polymerization; UV laser; polyurethane; challenges

# 1. Introduction

Modern electronics products are becoming thinner, lighter, and more functional day by day. The scaling of geometries in silicon-based fabrications (ICs) has been inexorable during the last two decades. Meanwhile, the Printed Circuit Boards (PCBs), which hold those ICs, continue to struggle to find an appropriate production technique in terms of flexibility, scalability, and environmental friendliness. With the growing demand for reduced packaging factor, multilayered PCBs are being used [1,2]. In general, any multilayered PCB consists of on-board conducting lines embedded on a dielectric medium, which reliably connects various electrical components such as resistors, capacitors, inductors, ICs, etc. For the conducting lines, copper (Cu) is the first choice for metallization because of its low resistivity, minimal electromigration, and high reliability [3,4].

Most of the leading manufacturers in mass production are still using a blanket of Cu on an insulating epoxy resin and pattern it using subtractive etch-and-print techniques to build circuit interconnects. There have been some variations witnessed in the lithography

Citation: Acharya, S.; Chouhan, S.S.; Delsing, J. Fabrication Process for On-Board Geometries Using a Polymer Composite-Based Selective Metallization for Next-Generation Electronics Packaging. *Processes* 2021, 9, 1634. https://doi.org/10.3390/ pr9091634

Academic Editor: Yan Wang

Received: 10 August 2021 Accepted: 6 September 2021 Published: 10 September 2021

**Publisher's Note:** MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations.

**Copyright:** © 2021 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https:// creativecommons.org/licenses/by/ 4.0/). techniques over the years, but the patterning methodologies still use the conventional etching steps [5,6]. Some of the most commonly used laminates in the PCB industries are epoxide resins, cyanate ester, polyimides, phenolic resins, polytetrafluroethylene (PTFE), polyphenyl ether (PPE), polyesters, etc. for non-flexible implementation [7,8].

The requirements of modern PCB fabrication technologies are scalability, high dynamic range of structures, heterogeneous integration of various components, robustness in yield, and cost-saving potential. As a choice of material, polymers qualify all of these essentials and are widely accepted in production units [9]. One of the strongest assets of polymers is the capability of producing large numbers of devices by replicating a master structure. For device-level applications, lithography-based micro-fabrication technologies are widely adapted, particularly when the feature sizes and choice of geometries are the point of interest [10,11]. Polymers have been used in electronics packaging applications especially in flexible printed boards due to their material properties such as high electrical insulation, improved chemical and moisture resistance, lower weight or volume, and low dielectric constant [12].

Out of many PCB manufacturing techniques, the Sequential Build-Up (SBU) method using the polymeric materials has been adopted by all leading electronics manufacturers [13]. Few techniques such as plasma etching, photo-imageable permanent dielectric, and laser-assisted patterning and drilling are constantly in use for board-level fabrications [12,14–16]. However, in all of these processes, the Cu patterning is performed by removing most of the metallic part from the board.

A sudden surge in the electronics market for modern gadgets during the fourth industrial revolution has also seen a rapid growth in the research and development sectors related to various manufacturing processes. There are proposed fabrication methods, beyond the conventional pattern transfer lithography processes, for making cheaper and more reliable display units (vertical thin LED) using glass substrates [17]. Laboratory-based research in interface engineering and chemically modified techniques is providing new production recipes for industries on regular intervals. Taking the advantages of laser-assisted methods and properties of certain materials, various micro-tools, full-color displays, and color conversion tools are being manufactured every day [18,19]. Laser direct writing (LDW) incorporated with a mask-free pattern transfer method is also one of the flexible electronics technologies for micro-structure printing [20–22]. In recent years, some of the direct laser patterning with dual damascene metallization process were also proposed for ultra-thin advanced packaging [23,24]. However, such processes still involve metal removal methods. A mask-free laser patterning process is demonstrated in this work as well for electronics packaging applications.

In the era of "More than Moore", the scaling of feature sizes is one of the primary concerns related to production techniques. There is a clear gap in adaptation of production approaches in silicon-based fabrications and PCB manufacturing. Regarding the scaling on the board level, some laser-assisted SBU processes also achieve significant minimum feature size on PCBs but again using the subtractive etch-and-print methods [25–27]. Therefore, with the advancement of certain technologies, the PCB manufacturing units are shifting towards Semi-Additive Processes (SAPs) or modified additive approaches. In SAP or modified-SAP (mSAP) techniques, due to the additive nature of the process, a Cu layer is deposited on a dielectric with an etched pattern. Then, the extra Cu is removed from the surface by etching [28]. For example, the fabrication of Cu interconnects on silicon wafers using mSAPs techniques is accepted and has been a trend for a decade [29].

Recently, an electroplating technique was demonstrated using Cu selective metallization on silicon wafer [30]. Such technologies are vital because of the cost reduction of metallization in advanced packaging. However, the process still uses Chemical Mechanical Planarization (CMP) to remove the extra Cu from the target field. However, such processes are very common in IC-substrate fabrication, but such fabrication in the PCB segment is an emerging technology. So far, most of the methods to metallize the non-metallic surfaces rely on mechanical engineering techniques. However, the CBM technology by Cuptronics Technology AB, Roserberg, Sweden has shown a potential chemical surface modification process to plate metals on plastics. In this work, this technology is adapted with laser activation of surfaces to show its application in PCBs fabrication. In another study [31], this fully additive-selective metallization process was shown on the PCB substrate with smallest feature size possible at the board level.

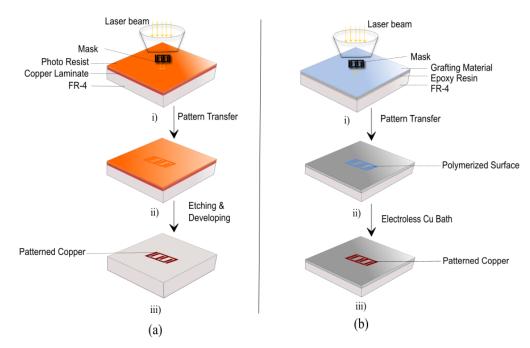

The main steps in this pattern-transferring techniques in PCBs are illustrated in Figure 1. In Figure 1a, a conventional etch-and-print method is shown where the Cu foil has been laminated onto an FR-4 substrate, and with the use of mask, any designed structure can be made. During the etching stage, a large part of the unwanted Cu (except the pattern) goes into the drain. This wastage is even significant while handling smaller feature size patterns. Meanwhile, in Figure 1b, an additive process is shown, which supports the selective metallization. The metallization of the desired pattern is controlled during the laser exposure and pattern transfer stage. Such techniques in mass production will reduce the amount of discarded metallic parts and the cost of the production, as the metal will only be deposited on the activated area.

In this paper, the usage of the fully additive fabrication technique has been demonstrated by creating different structures, generally used in electronics. The main highlights of the work are as follows:

- To demonstrate a fully additive process using exopy resins and polymer-based CBM technology to procure any desirable geometries on the FR-4 substrate.

- To show the selective metallization capability of the process by eliminating the etching process significantly (especially during the metallization), i.e., adapting an environmentally friendlier production approach.

- To present the feasibility of the fabrication technique at lower temperature (20–45 °C).

- To show the possibility of process implementation for the PCB fabrication segment of the industry towards miniaturization.

**Figure 1.** Main patterning and metallization steps in the PCB fabrication: (**a**) A conventional Subtractive etch-and-print Technology. (**b**) A fully additive technology named SBU-CBM approach with selective metallization.

Section 2 outlines the information about the materials and fabrication steps. Section 3 covers the analysis of the production techniques, characterization of the geometries, and process parameters in the fabrication. A planar inductor is fabricated using the proposed

production approach as a use case. The final section summarizes the entire process and its application in electronics packaging, including future work.

## 2. Materials and Methods

# 2.1. Sample Preparation

For the fabrication process, FR-4 was used as a base substrate because it has nice dimensional stability and good electrical properties. FR-4 is a well-known material in the PCB manufacturing industry and the same industrial standard commercially available FR-4 is used for this work. However, other materials such as FR-2, FR-3, XPC, CEM-3, etc. can also be used [32]. There should be two important considerations while choosing the base substrate: one is adhesion of the prepreg (PU/PA resins) on the base substrate's surface and the second one is the hydrophobic nature of the base material (as the electroless plating baths contain solvents). Polyurethane (PU) was used as dielectric epoxy resin due to its strong bonding properties, good insulating properties, resistance to solvents, tear resistance nature, and cost-friendliness [33]. For the surface modification technology from Cuptronic Technology, AB was used, i.e., covalent bonded metallization (CBM). Materials used in the experimentation, such as polyurethane solution (PU) and CBM substance (HP-14), were procured from Cuptronic Technology AB. An electroless Cu bath (PEC-660 series) was purchased from J-KEM International, Stockholm, Sweden [34]. A Gallium-Nitride (GaN) laser source (LW405B laser machine by MICROTECH, Italy) with a wavelength of 375 nm has been used to make the geometries.

## 2.2. Fabrication Steps

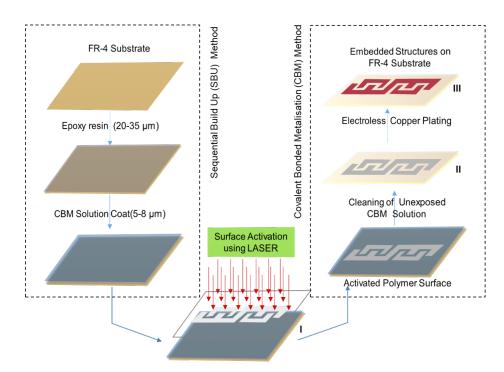

The fabrication steps to draw the patterns are shown in Figure 2. The steps were almost identical to that in [35] with a few modifications in the controlling parameters for both laser exposure and electroless bath. The sequential steps are as follows:

- Step 1: Ultrasonic cleaning of the FR-4 substrate using deionized water (DIW).

- Step 2: Drying of the FR-4 substrate at room temperature.

- Step 3: Spin coating of the PU layer on top of FR-4.

- Step 4: UV soft baking for 1 min followed by surface hardening at room temperature.

- Step 5: Spin coating of HP-14 on PU.

- Step 6: Selective polymerization of the surface using actinic radiation and pattern file (optional in case of bulk Cu deposition).

- Step 7: Proper cleaning using DIW of the sample to remove the unexposed HP-14 solution from the sample surface before the Cu bath.

- Step 8: Electroless Cu bath (Predip, Activator, Reducer and Cu bath).

- Step 9: Final cleaning of the surface and characterization.

The fabrication process is named Sequential Build Up-Covalent Bonded Metallization (SBU-CBM), as the layers were sequentially built on each other, and there is covalent bonding among the layers. A process flow chart of the proposed technique is shown in Figure 2, where each layer of polymer is subsequently grown, and the pattern is finally metallized with Cu.

## 2.3. Characterization

To characterize the fabricated samples, both optical microscopy and Scanning Electron Microscopy (SEM) were used. The samples were first checked using an optical microscope by FLIR pvt. and subsequently examined in a high-resolution SEM (JSM-IT300) by JEOL Inc. (Akishima, Japan). There are various critical parameters in this fabrication method. Thus, the process parameters were analyzed using  $2^k$  factorial design in the DESIGN EXPERT 12.0 <sup>®</sup> software to obtain the individual contribution and effect of the parametric sweep on the process. The results of different geometries and description of the important steps in fabrication are outlined in the following section.

Figure 2. Process flow diagram of the fabrication steps to pattern the geometries.

## 3. Results and Discussion

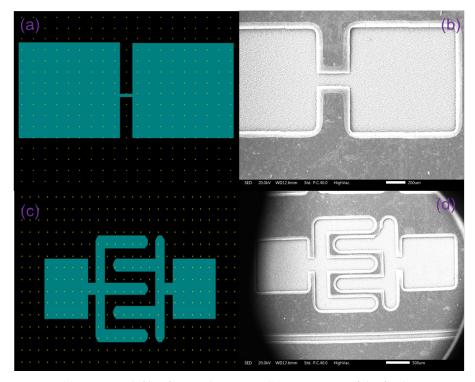

In this section, the selected geometries are shown in Figure 3, which were fabricated using the above production strategy. The surface modification and involvement of various process parameters are discussed in detail. The statistical analysis of the parameters, challenges in the fabrication steps, and potential application of the fabrication techniques are stated in the subsections.

**Figure 3.** (a) CAD-mask file of a simple pattern. (b) SEM image of the final structure on FR-4 using the fabrication steps. (c) Pattern file of another geometry. (d) SEM image of the pattern in panel (c) procured on the substrate.

#### 3.1. Surface Mechanism of the Polymerization

Following the steps of the SBU-CBM process, any planar structure can be achieved. First, the polyurethane was uniformly coated over the FR-4 substrate and properly cured to ensure the adhesion of the CBM solution (HP-14 in this work) on top of it. This process has the flexibility to use any other epoxy resin instead. Next, a seed layer of the HP-14 was uniformly spin coated. In general, HP-14 consists of monomers, initiators, catalysts, and solvents. Upon proper exposure to the UV laser, the polymerizable units undergo a chemical reaction with the unsaturated groups of polyurethane and form covalent bonding at the interface. The roles of the initiators are to start the polymerization reaction and provide anchor structures to the polymers that form on the substrate with the covalent bonds [36].

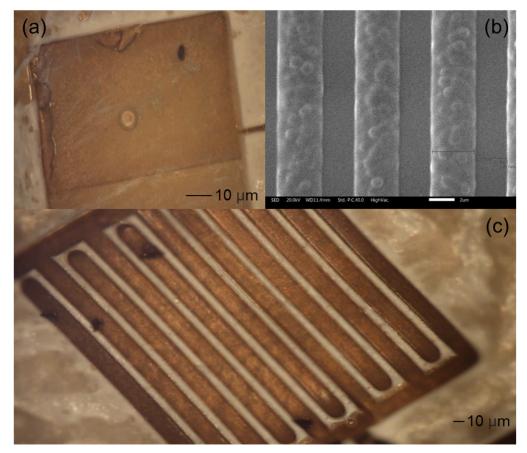

Figure 3a,c shows CAD-files with simple geometry and comparatively large geometry, respectively. Such pattern files of any desired geometry can be designed and used for laser exposure as shown in Figure 2 (step I). In Figure 3b,d, SEM images of the final structures, which were made using the pattern files in (a,c), are shown, respectively. The bright outline to the patterns in Figure 3b,d is the surface of the polyurethane on which Cu adhered due to the reflections from the imaging medium.

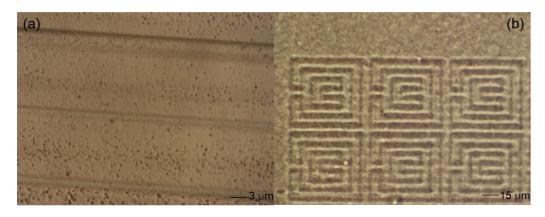

#### 3.1.1. Selective Polymerization with Patterns

As stated above, the surface phenomena of forming covalent bonds between the CBM solution and epoxy resin, is easy to handle with the large surface of the substrate, whereas the critical steps is to confined these mechanism to some specific regions (patterns). The concerning part in this step is to set the parameters for laser exposure of HP-14 chemistry in accordance to different feature sizes in the pattern files. Each CBM solution varies in composition; thus, the activation energy of the constituents requires a proper setting of laser exposure. The major variations in CBM solutions are the chemical constituents (monomers/initiators/catalysts) and their stoichiometry ratios. Therefore, a proper amount of actinic radiation is needed to form the covalent bonds. An overview of the surface immediately after the laser activation and selective polymerization is shown in Figure 4a,b. Figure 4a shows the lines of width 10  $\mu$ m; Figure 4b shows a complex pattern of a square-shaped split-ring resonator structure was achieved. In these implementations, computer-aided design (CAD) files were incorporated to achieve different structures unlike the physical masks in photolithography processes. This step corresponds to part 2 in Figure 2.

**Figure 4.** (a) Optical microscopic view of the surface immediately after the laser patterning and selective polymerization with a line pattern of width 10  $\mu$ m. (b) Image of the selective polymerized surface with a complex structure of the resonators.

#### 3.1.2. Selective Metallization

Once the surface has been properly activated, the polymers bound to the surface with covalent binding and the sample further undergo the metallization steps. Before the metallization step, the sample should be cleaned and rinsed with deionized water (DIW). This

7 of 13

step removes the extra and unexposed polymerizing units from the surface to ensure the proper adhesion of metallic ions onto the patterns. An electroless Cu bath, which consisted of four subsequent baths, was used to metallize the geometries as shown in Table 1. In the first bath, which is often known as the Predip, the polymerized surface is treated in an alkaline base to enhance the interface for the next bath. The Activator bath is the second bath, which metallizes the polymeric base with Palladium (Pd) as a first metallic coat. The third bath is the Reducer bath, where the metallic ions become reduced and form a suitable nucleation site for Cu to adhere. The final step in the electroless bath is the Cu bath, where bulk copper is deposited on the polymers by forming strong binding. The thickness of the Cu deposited on the patterns are in the range of 0.3 to 3  $\mu$ m, which is excellent for the electrical applications.The sample surface after the selective metallization is shown in Figure 5. Figure 5a,c shows the optical microscopic images of a simple structure and a complex structure, respectively. Figure 5b shows an SEM image of lines with a feature size of 3  $\mu$ m.

**Figure 5.** (a) Optical microscopic image of a pad structure after the final bath, i.e., Cu metallization. (b) SEM image of lines and spaces of 3 μm on FR-4 using the fabrication steps. (c) A complex geometry achieved using the SBU-CBM fabrication method [26].

The proposed SBU-CBM process also has great potential in making vias on polyurethane and metalizing the via with the above technique. Other possibilities include the fabrication of multilayered PCBs with different layers of PU and Cu. Multilayered metallization using nickel or gold or silver on top of Cu is also possible using this method.

## 3.2. Parameter Optimization

As previously mentioned, the most critical step in selective patterning and metallizing the surface is the control over parameters. Parameter optimization is required in two main steps: laser activation and electroless Cu bath of the samples. Laser exposure has three parameters: Gain, Exposure duration (no. of repetition), and Scanning rate (D-step). A brief description of these parameters is presented in [17]. The setting of these parameters require continuous inspection to optimize for different CBM solutions. With the proposed fabrication approach, the smallest possible feature size in any pattern using HP-14 so far is 2.5  $\mu$ m. The optimized values of the laser parameters to achieve the smallest feature size are gain = 6.5 mW, no. of repetition = 3 (11 min) and scanning rate = 160  $\mu$ /s (with D-step: 2), indicated in Table 2. Similarly, for Cu adhesion, the important parameters are the concentration of each bath, immersion time and temperature of the bath. Table 1 shows the optimized parameters of the Cu bath adjusted for HP-14. The adjusted laser parameters with various feature sizes in a pattern are shown in Table 2.

|     | Electroless Copper Bath Parameters |                       |                                                                                  |                   |                  |  |  |

|-----|------------------------------------|-----------------------|----------------------------------------------------------------------------------|-------------------|------------------|--|--|

|     | Type                               | Name                  | Concentration                                                                    | Time (in Minutes) | Temperature (°C) |  |  |

| Ι   | Predip                             | Precup-128            | 55.5 mL in 200 mL of DIW                                                         | 1                 | 25               |  |  |

| II  | Activator                          | Catcup-207            | 55.5 mL in 200 mL of DIW                                                         | 6                 | 42               |  |  |

| III | Reducer                            | Boric acid + ACS-2075 | 2.4 g in 100 mL of DIW +<br>1.5 mL of ACS-2075                                   | 6                 | 27               |  |  |

| IV  | Cu Bath                            | PEC-660<br>(A/M/B)    | 9.25 mL of PEC-A +<br>6.75 mL of PEC-M +<br>9.75 mL of PEC-B in<br>100 mL of DIW | 4–6               | 25               |  |  |

Table 1. Process parameter of the electroless Cu Bath for perfect metallization.

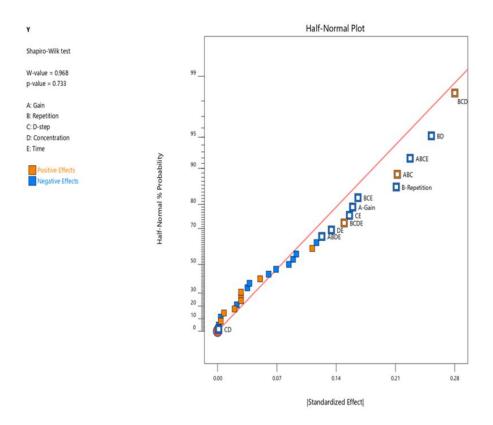

## Significance Level of Parameters

To observe the significance of different parameters, a statistical analysis of the parameters was performed using Design-Exert Version12<sup>®</sup>. For this analysis, 5 parameters were considered with respect to the minimum feature size in a pattern with 32 different samples. A  $2^k$  factorial design was used for the analysis. The parameters in the model are laser gain (A), no. of repetition (B), D-step (C), concentration of bath 4 (D), and immersion time of bath 4 (E). The thickness of the Cu layer on the patterns is a function of the parameters related to only the fourth bath. The significance level of all parameters and their combined effect with respect to the minimum feature size in the geometry are shown in Figure 6. This analysis helps to optimize individual parameters to achieve fine lines on the board. The proposed production technique has great potential in achieving the minimum feature size interconnects on PCB [31].

Due to the experimental nature of the work and involvement of numerous parameters, each sample after any parametric sweep undergoes an optical inspection. The values of the parameters also varies for different CBM solutions. In this case, the parameters for HP-14 were analyzed. In general, parameters A–C are responsible for proper surface activation and writing of the geometry on the surface. Parameters D and E are responsible for the deposition of metal ions onto the laser activated surface. The width and depth of the Cu is controllable by tuning parameters D and E. In Figure 6, the strongest effect is the combined effect of parameters B–D, which reflects the connectivity of laser activation and electroless bath to achieve the smallest structures on the board. The term 'positive effect' in the Figure 6, which combination of changes at a time are acceptable for obtaining the smallest feature size in the geometry. For instance, in this analysis, any change in parameters B–D at a time, is feasible. This is a simple analysis of the process to modify the parameters in a correct direction instead of adapting trial-and-error runs.

#### 3.3. Challenges in Fabrication

In this section, some challenges associated with the fabrication methodology are presented. Most challenges were due to the poor selection of process parameters.

## 3.3.1. Inadequate Laser Exposure

The CBM solution on the PU surface requires an adequate amount of actinic radiation to polymerize and form bonds. Therefore, the proper setup of laser parameters plays a crucial role in patterning the structures. Table 2 shows some of the parameters adjusted with respect to HP-14. Some of the shortcomings witnessed during the surface activation were due to the formation of cross-linked or branched polymerization while drawing complex patterns. High laser gain and excess number of repetitions are the primary reasons for such effects, which results in broadening of the structures.

| Feature Size in the Pattern (in $\mu$ m) | Laser Gain (mW) | D-Step (80 µm/s) | No. of Repetition |

|------------------------------------------|-----------------|------------------|-------------------|

| 30 and above                             | 6.6             | 4.0              | 6.0               |

| 10                                       | 6.5             | 4.0              | 6.0               |

| 7.5                                      | 6.4             | 4.0              | 5.0               |

| 5                                        | 6.5             | 2.0              | 3.0               |

| 2.5                                      | 6.5             | 2.0              | 3.0               |

Table 2. Laser parameters optimized for HP-14.

## 3.3.2. Improper Metallization

Poor metallization is another factor to consider in this production approach. As shown in part II in Figure 2, surface cleaning of the samples before the electroless bath and after the laser exposure is mandatory, as the extra polymer chains remain on the patterns and affect the Cu adhesion. Proper rinsing of the activated regions remained intact to the surface as it due to the formation of covalent bonds. Two related issues that we witnessed were overand under-metallization. Sometimes, the reason behind the poor Cu plating is substandard laser modification of the substrate surface.

Figure 6. Significance of the individual and combined effects of the parameters on the fabrication process.

#### 3.4. Fabrication of Planar Inductor: A Use-Case

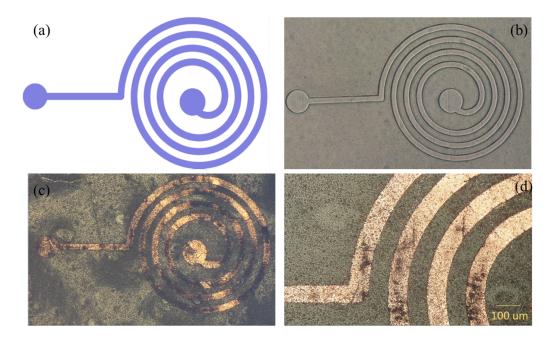

Miniaturization in electronics packaging is the call of the day. Use of bulky passive components in PCBs, such as resistors, capacitors, inductors, and so on, cause area penalty, which restricts the overall packaging density of the system. In a typical PCB, more than 80% components are passives, which take more than 40% of the area [37]. As a result, in modern packaging, embedded passives are used in abundant to accommodate large number of components in lesser space. Embedded passives are fabricated using the dielectric materials and metallic layer patterning on PCB base substrates. Such techniques are in high demand as they eliminate solder joints and reduce parasitic wastage [38]. As discussed in the introduction, most of the manufacturing processes use subtractive etch and print method or Semi-Additive Production (SAP) approaches to embed such passives in the inner layers of PCBs. However, in this work, it is achieved through a fully additive method. Using the above SBU-CBM method, a planar circular-spiral inductor is fabricated with a feature size of 75  $\mu$ m.

## 3.4.1. Objectives

Fabrication of on-board inductors is one of difficult tasks for any new fabrication technique due to their complex structures. In this work, the aim was to design a high inductance and high Q-factor embedded inductor using the available technology. The initial challenge was to decide the dimensions of the geometry which can exhibit the high inductance and Q-factor. The second challenge was to depict the geometry on board by adjusting the process parameters.

Out of three different planar inductors, spiral type of structure withstands highest inductance due to its positive mutual inductance property [39]. Similarly, out of four different spiral type designs, the circular type has highest Q-factor [40].

#### 3.4.2. Materials and Methods

For the fabrication of the inductor, the FR-4 substrate was used with a dimension of  $25 \times 25 \times 0.4$  mm. The same steps were followed as shown in Figure 2. However, these steps are also valid for other commercially available substrates such as PA-6, glass, FR-3, etc. The final laser parameters used to activate the pattern are 6.5, 4, and 5 (laser gain, D-step, and no.of repetition, respectively) as defined in Table 2. The final Cu bath parameters followed, are shown in Table 1.

#### 3.4.3. Results

The design and final fabrication results are shown in Figure 7. Figure 7a shows the design of the inductor considering the feature sizes required for an optimum inductance and Q-factor. Figure 7b is obtained after laser patterning and cleaning of the sample. Then, the sample was processed in the Cu bath to metallize the tracks and the result is shown in Figure 7c. The black regions in the figure are due to the rapid oxidation of Cu and can be prevented by storing the samples in an inert atmosphere. However, the target was achieved by building the planar spiral tracks precisely, shown in Figure 7d.

Finally, a planar circular spiral inductor with a feature size of 75  $\mu$ m was successfully fabricated using the Sequential Build-Up-Covalent Bonded Metallization (SBU-CBM) process. Further work can be done to optimize the parameters. This work shows that it is possible to fabricate these kinds of structures and that they can be incorporated into electrical circuits with smaller feature sizes.

**Figure 7.** (a) The final optimized design for the planar inductor. (b) The pattern obtained after laser surface modification and cleaning of the surface as shown in step-II in Figure 2. (c) Planar inductor pattern after the Cu bath as shown in step-III in Figure 2. (d) An image of the fine spiral tracks made by SBU-CBM method.

#### 4. Summary and Conclusions

In this work, a fully additive fabrication approach using polymer-based selective surface modification followed by metallization was demonstrated by patterning desired geometries on a 2D surface. Experimental evidence of a successful 2.5D process is in progress. Polyurethane was used as the dielectric coat, and HP-14 was used as the nanocomposite polymer layer with adequate surface activation to grow Cu at the desired locations. The process parameters and their role in patterning the geometries were analyzed. These selective metallization approaches will help to completely eliminate the etching process. Thus, this fabrication technique is environmentally friendly, cost-effective, and has great potential for industrialization. In the paper, a planar inductor is fabricated to show the feasibility of the process for complex geometries as well. Future development of this work will be the electrical and reliability assessment with different patterns. In the next step, we will realize two or more layers of epoxy resin and Cu to accommodate high-density interconnects and fabricate a multilayered PCB core. Furthermore, a simulation model of the fabrication steps to understand the surface mechanism will be developed using the finite element analysis method.

**Author Contributions:** Conceptualization was done by S.A. and S.S.C. designed the experiments; S.A. performed the experiments; S.A. analyzed the data; S.A. wrote the paper; J.D. and S.S.C. reviewed and edited the paper; J.D. supervised the process. All authors have read and agreed to the published version of the manuscript.

**Funding:** This research was funded by the Interreg Nord, European Regional Development Fund (ERDF) at https://www.interregnord.com/ (accessed on 25 August 2021).

Institutional Review Board Statement: Not applicable.

Informed Consent Statement: Not applicable.

Data Availability Statement: This can be excluded.

Acknowledgments: The authors would like to acknowledge the European Project: Productive 4.0 and InterregNord-COMPACT for the financial support. The entire work has done in the Clean Room, EISLAB, in the Department of Computer Science, Electrical and Space Engineering, LUT. The authors are thankful to the Master thesis student Linus Karlquist for his support in fabrication of embedded inductor. The authors also thankful to Cuptronic Technology AB, Rosersberg, Sweden for providing the proprietary CBM chemistry and the Copper bath.

Conflicts of Interest: The authors declare no conflict of interest.

Sample Availability: Samples of the fabricated specimen are available from the authors.

## References

- 1. Lee, H.J.; Yu, J. Method of Manufacturing Printed Circuit Board and Multi-Layered PCB. U.S. Patent 6,902,660, 7 June 2005.

- Kobayashi, T.; Kawasaki, J.; Mihara, K.; Honma, H. Via-filling using electroplating for build-up PCBs. *Electrochim. Acta* 2001, 47, 85–89. [CrossRef]

- 3. Cheng, Y.L.; Lee, C.Y.; Huang, Y.L. Copper Metal for Semiconductor Interconnects. In *Noble and Precious Metals—Properties, Nanoscale Effects and Applications*; Intechopen: London, UK, 2018; Chapter 10.

- 4. Frater, M.S. Copper/Steel Laminated Sheet for Use in Manufacturing Printed Circuit Boards. U.S. Patent 6,129,990, 10 October 2000.

- 5. Betancourt, T.; Brannon-Peppas, L. Micro-and nanofabrication methods in nanotechnological medical and pharmaceutical devices. *Int. J. Nanomed.* **2006**, *1*, 483. [CrossRef] [PubMed]

- 6. Ra, S.; Lee, C.; Cho, J.; Lee, S.; Lee, J.; Hong, M.; Kwak, J. Micro via and line patterning for PCB using imprint technique. *Curr. Appl. Phys.* **2008**, *8*, 675–678. [CrossRef]

- Murphy, O.J.; Hitchens, G.D.; Hodko, D.; Clarke, E.T.; Miller, D.L.; Parker, D.L. Method of Using Conductive Polymers to Manufacture Printed Circuit Boards. U.S. Patent 5,545,308, 13 August 1996.

- 8. Tamm, W.; Olbrich, W.; Dippon, S.; Weitmann, M.; Lam, S. Method of Manufacturing Printed Circuit Boards. U.S. Patent 5,666,722, 16 September 1997.

- Plovie, B.; Yang, Y.; Guillaume, J.; Dunphy, S.; Dhaenens, K.; Van Put, S.; Vandecasteele, B.; Vervust, T.; Bossuyt, F.; Vanfleteren, J. Arbitrarily shaped 2.5 d circuits using stretchable interconnects embedded in thermoplastic polymers. *Adv. Eng. Mater.* 2017, 19, 1700032. [CrossRef]

- 10. Rötting, O.; Röpke, W.; Becker, H.; Gärtner, C. Polymer microfabrication technologies. *Microsyst. Technol.* 2002, *8*, 32–36. [CrossRef]

- 11. Becker, H.; Gärtner, C. Polymer microfabrication technologies for microfluidic systems. *Anal. Bioanal. Chem.* **2008**, 390, 89–111. [CrossRef] [PubMed]

- 12. Goosey, M.T. Plastics for Electronics, 2nd ed.; Springer: Dordrecht, The Netherlands, 1999.

- 13. Varadarajan, M.G.; Lee, K.J.; Bhattacharya, S.K.; Pucha, R.; Tummala, R.R.; Sitaraman, S. Printed circuit board (PCB) miniaturization by embedded passives and sequential build-up (SBU) process methodology. *J. Indian Inst. Sci.* **2013**, *86*, 639.

- 14. Knudsen, P.; Brainard, R.; Schell, K. A photoimageable dielectric for sequential PWB fabrication. *Circuit World* **1995**, *21*, 5–9. [CrossRef]

- 15. Fierro, L.; Getty, J.D. Plasma processes for printed circuit board manufacturing. Circuitree-Campbell 2003, 16, 28–33.

- 16. Yung, K.; Liem, H.; Choy, H.; Yue, T. Impact of plasma etching on fabrication technology of liquid crystal polymer printed circuit board. *J. Mater. Sci. Mater. Electron.* 2010, *21*, 954–962. [CrossRef]

- Shin, J.H.; Park, J.H.; Seo, J.; Im, T.H.; Kim, J.C.; Lee, H.E.; Kim, D.H.; Woo, K.Y.; Jeong, H.Y.; Cho, Y.H.; et al. A Flash-Induced Robust Cu Electrode on Glass Substrates and Its Application for Thin-Film μLEDs. *Adv. Mater.* 2021, 33, 2007186. [CrossRef] [PubMed]

- 18. Weng, Y.; Chen, S.; Zhang, Y.; Sun, L.; Wu, Y.; Yan, Q.; Guo, T.; Zhou, X.; Wu, C. Fabrication and color conversion of patterned InP/ZnS quantum dots photoresist film via a laser-assisted route. *Opt. Laser Technol.* **2021**, *140*, 107026. [CrossRef]

- 19. Zhao, Y.; Liu, H.; Yu, T.; Hong, M. Fabrication of high hardness microarray diamond tools by femtosecond laser ablation. *Opt. Laser Technol.* **2021**, *140*, 107014. [CrossRef]

- 20. Zhang, Q.; Huang, D.; Qi, D.; Zhou, W.; Wang, L.; Zhang, Z.; Chen, S.; Dai, S.; Zheng, H. Mask-free patterning of Cu mesh as smart windows by spatially modulated nanosecond laser pulses. *Opt. Laser Technol.* **2021**, *140*, 107056. [CrossRef]

- 21. Trantidou, T.; Friddin, M.S.; Gan, K.B.; Han, L.; Bolognesi, G.; Brooks, N.J.; Ces, O. Mask-free laser lithography for rapid and low-cost microfluidic device fabrication. *Anal. Chem.* **2018**, *90*, 13915–13921. [CrossRef] [PubMed]

- 22. Miao, Y.; Wan, L.; Ling, X.; Chen, B.; Pan, L.; Gao, Y. Mask-free preparation of patterned carbonized carboxymethyl cellulose on fabrics for flexible electronics. *ACS Appl. Electron. Mater.* **2020**, *2*, 855–862. [CrossRef]

- Hollman, R.; Dimov, O.; Malik, S.; Hichri, H.; Arendt, M. Ultra fine RDL structure fabrication using alternative patterning and bottom-up plating processes. In Proceedings of the 2018 IEEE 68th Electronic Components and Technology Conference (ECTC), San Diego, CA, USA, 29 May–1 June 2018; pp. 58–63.

- 24. Woehrmann, M.; Wuensch, O.; Lang, K.D.; Gernhard, R.; Hauck, K.; Kroehnert, K.; Zoschke, K.; Juergensen, N.; Toepper, M.; Braun, T.; et al. New Excimer Laser-Based Dual Damacene Process For High I/O Applications with Ultra-Fine Line Routing. *Süss Rep.* **2016**, 2016, 4–10.

- Acharya, S.; Chouhan, S.S.; Delsing, J. Scalability of Copper-Interconnects down to 3 μm on Printed Boards by Laser-assistedsubtractive process. In Nordic Conference on Microelectronics Packaging, NORDPAC (Device Packaging, HiTEC, HiTEN, & CI-CMT); International Microelectronics Assembly and Packaging Society (IMAPs): Copenhagen, Denmark, 2019; Volume 2019, pp. 000017–000020.

- 26. Çakır, O. Review of etchants for copper and its alloys in wet etching processes. In *Key Engineering Materials*; Trans Tech Publications Ltd.: Stafa-Zurich, Switzerland, 2008; Volume 364, pp. 460–465. [CrossRef]

- 27. Cakir, O. Copper etching with cupric chloride and regeneration of waste etchant. *J. Mater. Process. Technol.* **2006**, 175, 63–68. [CrossRef]

- Dunn, T. Additive Electronics: PCB Scale to IC Scale. Available online: http://www.magazines007.com/pdf/PCB007-Sept2018.pdf (accessed on 24 August 2021).

- Dharmarathna, S.; Clark, T.; Bae, C.; Kil, E.; Bang, A.; Sy, M.; Yeh, R.; Feng, K. Copper Electroplating Processes for Advanced HDI Applications. In Proceedings of the 2019 14th International Microsystems, Packaging, Assembly and Circuits Technology Conference (IMPACT), Taipei, Taiwan, 23–25 October 2019; pp. 84–87.

- Mavliev, R.; Gottfried, K.; Rhoades, R. Advanced Packaging Cost Reduction by Selective Copper Metallization. In Proceedings of the 2020 IEEE 70th Electronic Components and Technology Conference (ECTC), Orlando, FL, USA, 3–30 June 2020; pp. 327–332.

- Acharya, S.; Chouhan, S.S.; Delsing, J. An Additive Production approach for Microvias and Multilayered polymer substrate patterning of 2.5 μm feature sizes. In Proceedings of the 2020 IEEE 70th Electronic Components and Technology Conference (ECTC), Orlando, FL, USA, 3–30 June 2020; pp. 1304–1308.

- 32. Stojanovic, G.; Zivanov, L. Comparison of optimal design of different spiral inductors. In Proceedings of the 2004 24th International Conference on Microelectronics (IEEE Cat. No. 04TH8716), Nis, Serbia, 16–19 May 2004; Volume 2, pp. 613–616.

- 33. Multi-cb Printed Circuit Boards/Data Sheet. Available online: https://www.multi-circuitboards.eu (accessed on 24 August 2021).

- 34. Precision Urethane & Machine, Inc. Available online: https://www.precisionurethane.com/urethane-advantage.html (accessed on 24 August 2021).

- 35. Johan Lundqvist, F.V. J-KEM International. Available online: http://jkem.se (accessed on 24 August 2021).

- Acharya, S.; Chouhan, S.S.; Delsing, J. Realization of Embedded Passives using an additive Covalent bonded metallization approach. In Proceedings of the 2019 22nd European Microelectronics and Packaging Conference & Exhibition (EMPC), Pisa, Italy, 16–19 September 2019; pp. 1–6.

- 37. Atthoff B.; Göthe S. Metalization of Surfaces. U.S. Patent 10,822,702, 16 February 2017.

- Chammas, H. Embedded Passive Technology. 2012. Available online: https://docplayer.net/29645317-Embedded-passivetechnology.html (accessed on 24 August 2021).

- 39. Gerke, R.D. Embedded passives technology. Resistor 2005, 146, 635.

- 40. Stalf, S. Printed inductors in RF consumer applications. IEEE Trans. Consum. Electron. 2001, 47, 426–435. [CrossRef]