# Article A Sub-THz Wireless Power Transfer for Non-Contact Wafer-Level Testing

# Hanh Dang-ba and Gyung-su Byun \*

School of Information and Communication Engineering, Inha University, Incheon 22212, Korea; 22192288@inha.edu

\* Correspondence: gsbyun@inha.ac.kr; Tel.: +82-32-860-7435

Received: 12 June 2020; Accepted: 23 July 2020; Published: 28 July 2020

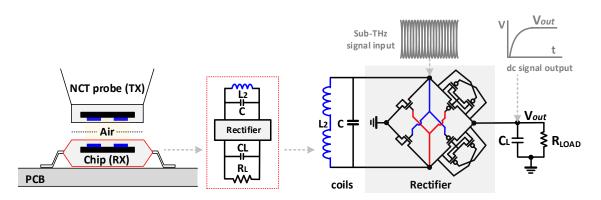

**Abstract:** In this paper, a sub-THz wireless power transfer (WPT) interface for non-contact wafer-level testing is proposed. The on-chip sub-THz couplers, which have been designed and analyzed with 3-D EM simulations, could be integrated into the WPT to transfer power through an air media. By using the sub-THz coils, the WPT occupies an extremely small chip size, which is suitable for future wafer-testing applications. In the best power transfer efficiency (PTE) condition of the WPT, the maximum power delivery is limited to 2.5 mW per channel. However, multi-channel sub-THz WPT could be a good solution to provide enough power for testing purposes while remaining high PTE. Simulated on a standard 28-nm CMOS technology, the proposed eight-channel WPT could provide 20 mW power with the PTE of 16%. The layouts of the eight-channel WPT transmitter and receiver occupy only 0.12 mm<sup>2</sup>, 0.098 mm<sup>2</sup>, respectively.

Keywords: wireless power transfer (WPT); non-contact testing; sub-THz WPT; wafer-level testing

# 1. Introduction

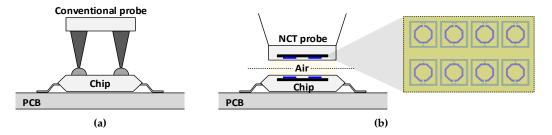

Wafer-level testing is an essential process for semiconductor device fabrication. The traditional wafer testing technique utilizes a probe card that directly connects to pads or bumps of a device under test (DUT) [1], as shown in Figure 1a. The probe card is required to be accurately placed on top of the DUTs because any misalignment between the probe card and the DUTs could lead to unreliable testing results. To overcome the misalignment risk, a complex probe card is required and testing cost could be increased [2]. Moreover, direct contact causes severe damage to both the probe card and the DUT. In simultaneous on-wafer test technique, as demonstrated in [2], all DUTs on a given wafer are tested at the same time for the maximum testing speed. Each pad of the DUTs generally suffers from an approximate pressure of three grams during the wafer test [2]. If 2000 DUTs are fabricated in a wafer and each DUTs has 60 pads, the total pressure on the pad is 350 kg, which could break any wafer used in recent semiconductor technology [2]. Therefore, the traditional wafer testing technique encounters challenges from high-cost testing, low-reliability, and limited testing speed.

**Figure 1.** (**a**) The traditional wafer-level testing interface; (**b**) Non-contact wafer-level testing interface with inductive coupling link.

The challenges of the contact testing technique lead to the studies of non-contact testing (NCT) interface [3–8] where the wired link has been replaced by the inductive coupling link. Compared to the complex probe card of the wired testing interface, the NCT probe card has a simpler architecture, therefore, the testing cost could be significantly reduced [3–5]. The NCT interface provides a more reliable testing result because the performance of the inductive coupling link remains more stable than the performance of the direct contact link when the misalignment risk happens [6,7]. Additionally, when the pressure on the wafer has been removed, the testing speed could be improved because more DUTs could be tested at the same time [3,6,8]. However, increasing the number of DUTs on a single wafer leads to a new challenge, the NCT chip size needs to be very small. An NCT system usually requires both wireless data transfer (WDT) and wireless power transfer (WPT) chips [9–12], which occupy a very large chip size due to the bulky inductive couplers. Therefore, NCT in the advanced wafer-level testing technique requires a new task: reduce WDT and WPT chip size.

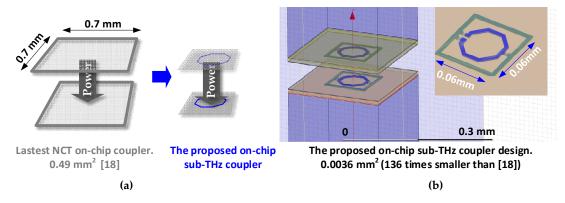

Recent research on WPT [2,13–18] has been reported in terms of scaling down chip size and improving power transfer efficiency (PTE). Aiming to the biomedical applications, the conventional WPTs in [13–17] only focus on optimizing the receiver (RX) chip size. The transmitter (TX) chip size is usually very large to provide enough power to the RX because the transfer distance is required to be larger than a certain value (i.e., TX area: 900 mm<sup>2</sup>, distance: 10 mm [14]). To be designed for the applications with much shorter distance, the conventional WPTs in [2,18,19] provide both optimized TX and RX chip size (i.e., TX area: 0.49 mm<sup>2</sup>, RX area: 0.49 mm<sup>2</sup>, distance: 0.02 mm [18]). When the TX chip size and the transfer distance could be considered as a trade-off, the RX chip size of the conventional WPTs is expected to be as small as possible. However, the scaling down RX chip size in the conventional method is limited by the bulky couplers, which are designed for low-frequency operation (i.e., 144 MHz [2]).

In this paper, we propose an extremely small form factor WPT by utilizing the sub-THz band for the inductive-coupling link. Figure 1b shows the principle of the proposed WPT where multiple sub-THz couplers could easily fit into a single WPT link because the sub-THz band provides much scaled inductive coils (i.e., 300 MHz as  $0.7 \times 0.7$  mm [18], 200 GHz as  $0.06 \times 0.06$  mm). Furthermore, from the advanced design techniques that have been reported for the conventional WPTs, the proposed WPT transmitter and receiver have been upgraded for the higher PTE in the desired sub-THz frequency operation. The proposed multi-channel WPT could be a good solution for the power coupling scalability (i.e., when more THz coils for WPT is added, more transfer power is achieved).

#### 2. The Proposed Sub-THz WPT Design

#### 2.1. The Proposed Sub-THz Transmitter Design

Figure 2 shows the architecture and schematic of the proposed sub-THz WPT TX. In the TX, an LC tank voltage-controlled oscillator (VCO) generates the sub-THz carrier. To provide higher power transmission, the sub-THz VCO output signal goes into a power amplifier (PA), which drives the gate voltage of  $M_3$  and  $M_4$  to change the current flow on an inductor (L<sub>1</sub>). The higher current fluctuation causes a stronger magnetic field on the L<sub>1</sub>, which enhances the efficiency of WPT. Furthermore, the network impedance of the PA is matched to our WPT load impedance for maximum power transfer. The LC-tank VCO consists of active transistors (M<sub>1</sub> and M<sub>2</sub>) and an LC tank. The cross-coupled NMOS transistors are utilized to provide the negative resistances and overcome the loss due to the parasitic resistance of the LC tank. Passive circuit elements such as inductor (L) and capacitor (C) are usually very large in on-chip CMOS implementation, especially if the inductor is bulky. For our WPT, the sub-THz inductors are used to implement smaller form factor VCO and PA. Moreover, to achieve a high power gain at the sub-THz frequency operation, the PA is designed as two symmetric class E amplifiers. These amplifiers are made of two NMOS transistors and the L<sub>1</sub>. The output impedance of

the PA is a combination of the inductance on the  $L_1$ , the parasitic capacitance ( $C_{p)}$ , and resistance ( $R_p$ ) of the NMOS transistors and the inductor. The transfer function of the PA (A(s)) is given by

$$A(s) = \frac{sR_{p}L_{1}g_{m}}{s^{2}R_{p}L_{1}C_{p} + sL_{1} + R_{p}}$$

(1)

or

$$A(s) = A_0 \frac{s}{\left(1 + \frac{s}{\omega_{p1}}\right)\left(1 + \frac{s}{\omega_{p2}}\right)}$$

(2)

where  $g_m$  is the trans-conductance of  $M_3$  and  $M_4$ ,  $A_0 = L_1 g_m$  is the mid-band gain of the PA. As shown in Equations (1) and (2), the A(s) is a form of a band-pass filter transfer function with two poles frequency,  $\omega_{p1}$  and  $\omega_{p2}$  satisfy

$$\omega_{p1} + \omega_{p2} = \frac{1}{R_p C_p} \tag{3}$$

$$\omega_{p1} \times \omega_{p2} = \frac{1}{L_1 C_p} \tag{4}$$

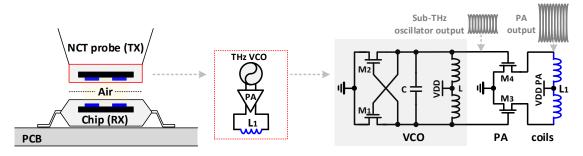

**Figure 2.** The architecture and schematic of the proposed sub-THz wireless power transfer (WPT) transmitter.

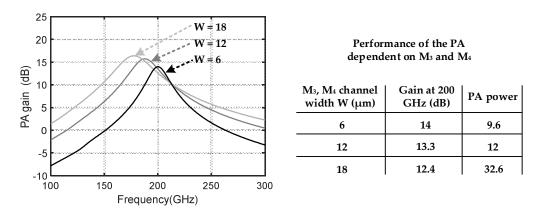

When the channel width of M3 and M4 is increased, the  $g_m$  and the  $C_p$  are both increased. The mid-band gain  $A_0$  increases when  $g_m$  is increased. However, Equations (1) and (2) show that increasing  $C_p$  causes the reduction in poles-frequency of the A(s), reduces the gain in higher frequency operation. Therefore, the sizes of the PA NMOS transistors need to be carefully optimized to obtain the highest gain in the desired frequency. Figure 3 shows the performance of the PA dependent on the channel width ( $W_{PA}$ ) of  $M_3$  and  $M_4$ . When  $W_{PA} = 6 \ \mu m$ , the PA achieves approximately 14 dB gain when consumes 9.6 mW power. When  $W_{PA}$  increases, the power consumption of PA is dramatically increased while the gain starts decreased at 200 GHz frequency operation.

Figure 3. The performance of power amplifier (PA) according to the channel width of M<sub>3</sub> and M<sub>4</sub>.

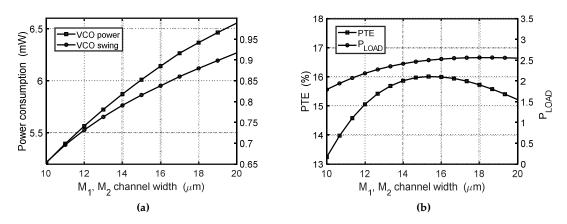

To increase the delivered power ( $P_L$ ) for the WPT, the output voltage swing on the PA need to be increased. When the PA has been optimized at the desired frequency operation, we can increase the PA output voltage swing by providing more power to the VCO. Higher power consumption on VCO provides a higher gate voltage driver on  $M_3$  and  $M_4$ . Figure 4a shows the power consumption and output voltage swing of the VCO dependent on the channel width of  $M_1$  and  $M_2$ . However, the PA performs the best efficiency with a limited range of the VCO output voltage swing. When the limitation voltage range has been reached, increasing the channel width of  $M_1$  and  $M_2$  only increases the power consumption but not improves the  $P_L$ . The maximum PTE of the proposed WPT is achieved when the channel width of  $M_1$ ,  $M_2$  is 15 µm, as shown in Figure 4b.

**Figure 4.** (a) Power consumption and output voltage swing of the voltage-controlled oscillator (VCO) according to the channel width of  $M_1$  and  $M_2$ ; (b) power transfer efficiency (PTE) and  $P_L$  of the proposed WPT according to the channel width of  $M_1$ ,  $M_2$ .

#### 2.2. The Proposed Sub-THz Receiver Design

The architecture and schematic of the sub-THz WPT RX are shown in Figure 5. The changing magnetic field produced on the  $L_1$  generates a current flow in the primary coil of the receiver ( $L_2$ ). The sub-THz rectifier converts the ac current signal to the dc voltage signal ( $V_{OUT}$ ). The key task of designing a sub-THz WPT RX is to design a sub-THz rectifier with high power conversion efficiency (PCE).

Figure 5. The architecture and schematic of the proposed sub-THz WPT receiver.

The PCE is calculated as what the percentage of ac power can be converted to dc output power. The most fundamental rectifier is a full bridge rectifier, which uses four Schottky diodes arranged in series pairs [20]. Each pair is active in each half cycle of the supply to convert the ac signal into the dc signal. However, due to the forward voltage drop on each Schottky diodes, this architecture performs very low PCE, especially when the ac input swing is low. There are state-of-the artworks to overcome PCE limitations [6,21,22]. The [21] presented an NMOS cross-connected gate rectifier for the V<sub>TH</sub> cancellation, leading to eliminate the voltage drop on the NMOS transistor. In [6], a SiP PMOS bridge rectifier was proposed, which uses two auxiliary PMOSs to connect the N-well to V<sub>OUT</sub> or V<sub>IN</sub>. This helps to control the body of the transistors by eliminating the substrate leakage and risk of latch-up. The [22] utilized an active NMOS rectifier with two integrated comparators and a cross-connected PMOS pair. When the cross-connection cancels the V<sub>TH</sub> drop on the PMOS pairs, the comparators could provide a wide bias voltage swing for the NMOSs, leading to the better PCE when the ac input signal swing is small. However, at the sub-THz frequency operation, the PCE of prior works degrades significantly because of the increased parasitic capacitance of bulky NMOS and PMOS transistors of the rectifier.

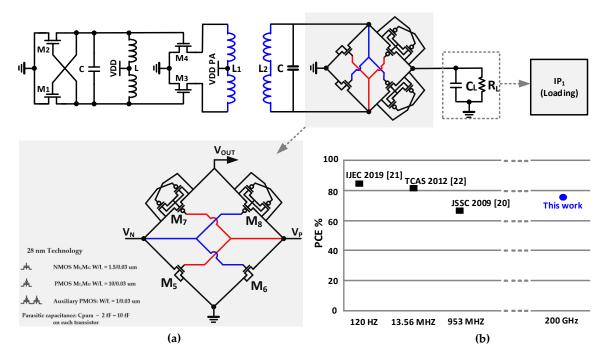

As shown in Figure 6a, our proposed sub-THz rectifier utilizes the cross-connection to both NMOS ( $M_5$ ,  $M_6$ ) and PMOS ( $M_7$ ,  $M_8$ ) pairs to achieve the V<sub>TH</sub> self-cancellation, which improve the PCE of the rectifier at sub-THz frequency range. Additionally, the body dynamic control topology is also employed on the PMOS pair. The inevitable trade-off between parasitic capacitance and transconductance of each transistor results in the compromise between frequency limitation and power conversion efficiency of the rectifier. The channel width of all the transistors in the rectifier should be less than 10  $\mu$ m to reduce the parasitic capacitance, which dramatically decreases the sub-THz current signal on L<sub>2</sub>. For the best PCE achievement, the channel width of the NMOS pair should be 6–10 times smaller than the channel width of the PMOS pair. Figure 6b shows the performance comparison among the proposed rectifier with the state-of-art rectifiers. Although the PCE of [22] (i.e., 84%) is higher than others [21,23] the PCE starts degrading in higher frequency and achieves 82 and 67.5% respectively at 13 MHz and 330 MHz. However, our proposed rectifier maintains the PCE up to 78% from low frequency to higher sub-THz frequency.

**Figure 6.** (**a**) The upgraded rectifier for the sub-THz frequency operation; (**b**) Performance comparison among the conventional rectifiers and the sub-THz rectifier.

## 2.3. The Proposed Sub-THz Coupling Coils Design

The on-chip sub-THz coupling inductors  $L_1$  and  $L_2$  are the most important components that influence the performance of the proposed sub-THz WPT. The coupling factor between  $L_1$  and  $L_2$ is the most critical factor that decides the power transfer efficiency (PTE) of the WPT [24–26]. The quality factor of the on-chip inductors is limited by considerable parasitic resistance and capacitance. The parasitic resistance of  $L_1$  on the TX chip must be as small as few Ohms to allow the maximum output power of the PA. The parasitic resistance of inductor  $L_2$  on the RX chip should be relatively small, compared with the load and on-state resistance of the rectifier [27].

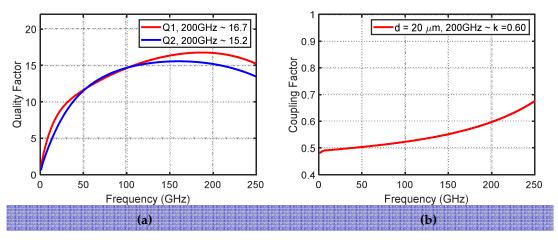

A typical inductor design process usually requires a 3-D electromagnetic (EM) field simulator such as HFSS. In this section, multiple case studies for the sub-THz coupling inductors (couplers) are presented. By using the HFSS EM simulator, the couplers have been designed and verified by the most accurate 3D EM model extraction for the sub-THz WPT PTE. Figure 7a shows an on-chip coupler for a conventional WPT [18], which operates at 300 MHz. The low-frequency inductor occupies a 0.49-mm<sup>2</sup> footprint, which is a huge area and not suitable for wafer-level testing in deep sub-micron technologies. Figure 7b shows the proposed on-chip sub-THz coupling inductors that are implemented on two silicon dies. To be designed for the 200 GHz frequency operation, the proposed coupler occupies only 0.0036 mm<sup>2</sup>, which is 136 times smaller than the state-of-the-art NDT [13]. Therefore, the proposed WPT can significantly reduce the overall size of the non-contact wafer-level probes. Figure 8a shows the simulated quality factors Q<sub>1</sub> and Q<sub>2</sub> of the coupler, which are 16.7 and 15.2, respectively at 200 GHz frequency. Figure 8b shows the coupling factor (*k*) of the proposed WPT coupler with a 0.02-mm air gap distance. When the coupler operates at a higher frequency, *k* is higher. At the desired frequency operation (200 GHz), the coupling factor *k* = 0.6.

**Figure 7.** (a) A comparison between a conventional on-chip coupler and the proposed on-chip sub-THz coupler; (b) The proposed on-chip sub-THz coupler design.

**Figure 8.** (a) Quality factors Q1 and Q2 of the proposed sub-THz coupler; (b) coupling factor of the proposed sub-THz coupler.

In the non-contact wafer-level testing, it is not always available to place the testing probe exactly alight with the DUT. Therefore, there are always an *offset distance* ( $\Delta$ ) and a *distance* (d) between the inductors of the sub-THz coupler. Those offsets yield a big impact on the coupling factor. To evaluate

the critical impacts on the coupling factor accurately, the key case studies are executed as shown in Figure 9. The *k* decreases from 0.6 to 0.36 when *d* increases from 20 to 50  $\mu$ m and decreases from 0.6 to 0.25 when  $\Delta$  increases from 0 to 20  $\mu$ m. Therefore, in the proposed non-contact wafer-level testing system, any misalignment between the sub-THz NCT probe and DUTs causes a reduction for the *k*, leading to decreasing the PTE.

**Figure 9.** Simulation results of the proposed coupler at 200 GHz according to (**a**) various distance (*d*); (**b**) various offset distance ( $\Delta$ ).

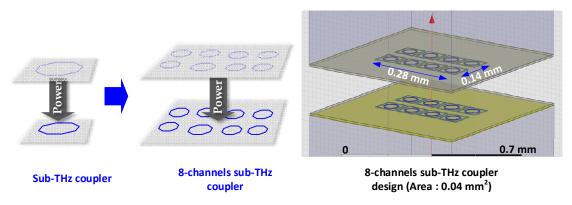

An important specification of a WPT is the maximum power that it could provide to the load [28–30]. In the proposed sub-THz WPT, the maximum power transfer is limited by the specification of the sub-THz PA and rectifier (i.e., 200 GHz as 2.5 mW maximum). However, if multiple parallel channels are integrated into a single WPT, the desirable transfer power could be achieved while the total footprint remains much smaller than the conventional WPT (i.e., 8 channels as 20 mW, 0.04 mm<sup>2</sup>). When higher PTE is required, the number of WPT channels could be simply increased along with the number of sub-THz couplers. Figure 10 shows a sub-THz multi-channel WPT system using a high-performance 8-channels coupler. On each chip die, 8 sub-THz inductors are arranged into a  $2 \times 4$  rectangle. The total area of the 8-channels coupler is only 0.04 mm<sup>2</sup>.

Figure 10. An 8-channels sub-THz coupler design.

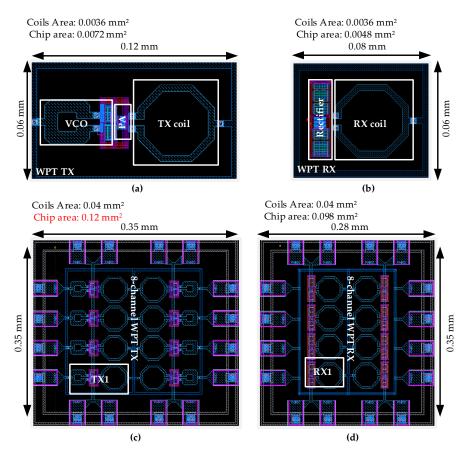

The proposed sub-THz WPTs has been implemented in 28-nm CMOS technology. Figure 11a,b show the layout of the single-channel WPT transmitter and receiver, respectively. In the single-channel WPT, the coupling coils occupy a 0.0036 mm<sup>2</sup> area while the total chip area is 0.0072 mm<sup>2</sup> for TX and 0.0048 mm<sup>2</sup> for RX. Figure 11c,d show the layout of the 8-channels WPT where the total area of the coupler is 0.04 mm<sup>2</sup> for both TX and RX. In the 8-channels WPT, the sizes of the TX and the RX are still only 0.12 mm<sup>2</sup> and 0.098 mm<sup>2</sup> respectively.

**Figure 11.** (**a**) Layout of the single-channel WPT TX; (**b**) Layout of the single-channel WPT RX; (**c**) Layout of the 8-channels WPT TX; (**d**) Layout of the 8-channels WPT RX.

## 3. Results

#### 3.1. Simulation Results of a Single Channel Sub-THz WPT Interface

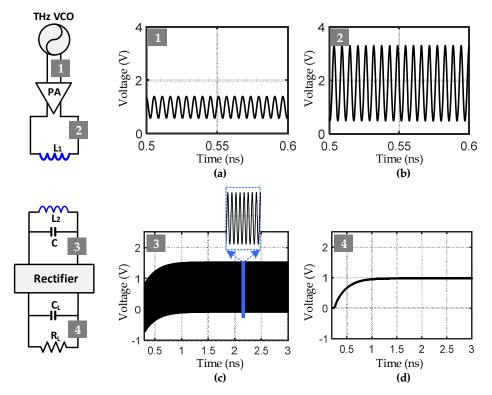

The post-layout-extracted simulation for a single channel WPT TX and RX is performed to evaluate the maximum and worst-case performance of the proposed WPTs. For an accurate WPT coupler modeling including wire bonds and parasitic capacitance, the 3-D EM solver tool (HFSS) is used to generate s-parameters. The worst-case simulated signal-flow (SS/0.9/100°) of the proposed single-channel sub-THz WPT at 200 GHz frequency operation is shown in Figure 12. The VCO consumes 6 mW power to generate a 200 GHz signal with 0.8 V voltage output swing as shown in Figure 12a. The PA is applied to magnify the signal amplitude to 3.9 V as shown in Figure 12b. The power consumption of the PA is 9.6 mW. The total power consumption of the single-channel WPT TX ( $P_{TX}$ ) is 15.6 mW. Figure 12c shows the input voltage signal of the rectifier which has a 1.5 V ac output swing. When a 400  $\Omega$  load resistance is applied for the RX, the dc voltage output on the load is 1 V, as shown in Figure 12d. As a result, the power delivered to the load could be calculated as

$P_L = V_{OUT}^2/R_L = 2.5$  mW. The PTE of the proposed single-channel WPT is  $P_{L/}P_{TX} = 16\%$  at 200 GHz frequency operation.

**Figure 12.** The simulated signal-follow of the proposed single-channel sub-THz WPT at 200 GHz frequency operation (SS/0.9/100°). (a) VCO output; (b) PA output; (c) rectifier input; (d) rectifier output ( $V_{OUT}$ ).

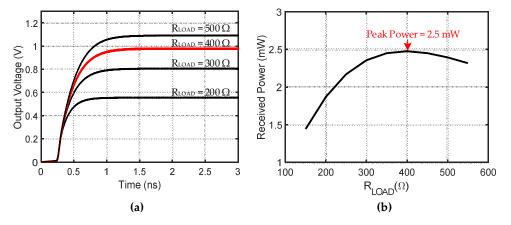

The output voltage ( $V_{OUT}$ ) and the power transfer of the proposed WPTs depend on the loading resistance value ( $R_L$ ). Figure 13a shows the output voltage ( $V_{OUT}$ ) when the  $R_L$  increases from 200 to 500  $\Omega$ . The  $V_{OUT}$  keeps increasing when the  $R_L$  increases. However, the maximum received power is 2.5 mW when the loading resistance  $R_L = 400 \Omega$ , as shown in Figure 13b. This is because the performance of the proposed rectifier depends on the output loading condition. Therefore, with a specific power delivery requirement, the sub-THz rectifier should be carefully optimized for the best PTE achievement.

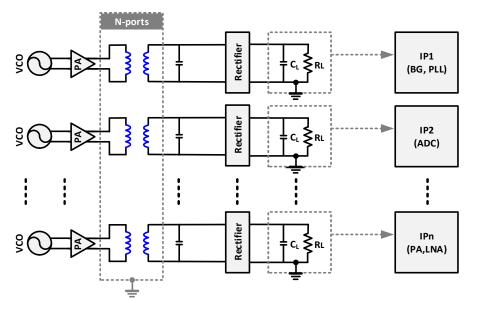

## 3.2. Simulation Results of a Multi-Channel Sub-THz WPT Interface

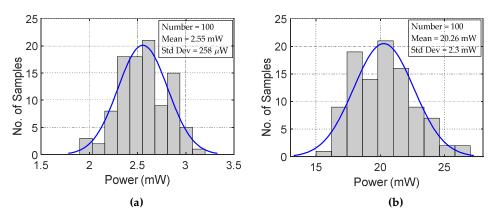

Based on the design of the single-channel WPT with the maximum PTE, the optimal multi-channel WPT has been designed, shown in Figure 14. The 8-channels sub-THz coupler is modeled by an N-ports with the s-parameter generated from the HFSS model to consider crosstalk between multiple channels. As the number of the WPT channels is added, the maximum overall power transfer efficiency could be significantly improved because the sub-THz WPT can provide enough space. To evaluate the power offset of the proposed WPTs depending on the process, voltage, and temperature (PVT) variation accurately, the Monte Carlo simulation has been performed for both single-channel and multi-channel cases. Figure 15 shows that the power transfer distortion is 0.77 mW and 6.9 mW at the 3-sigma of single-channel and multi-channel WPT, respectively. To achieve better power transfer for the proposed WPT, the accurate alignment between WPT coupling inductors is needed. In terms of multi-channel WPT case with the worst-case scenario, the max power mismatch is 6.9 mW. Therefore, when the proposed WPT provides the max power transfer for various intertextual properties (IPs)

such as bandgap, PLL/DLL, ADC, and PA/LNA blocks, the optimal number of WPT channels should be considered.

**Figure 13.** (a) The simulated output voltage  $V_{OUT}$  versus variation in  $R_L$  at 200 GHz (SS/0.9/100°). (b) The simulated output power  $P_L$  versus variation in  $R_L$  at 200 GHz.

Figure 14. The architecture of the 8 parallel channels sub-THz WPT.

**Figure 15.** The Monte Carlo simulation results. (**a**) Power transferred of single-channel WPT; (**b**) Power transferred of 8-parallel channels WPT.

Table 1 shows the performance comparison of the prior works and the proposed work. To the best if the authors' knowledge, the proposed sub-THz WPT design has not been reported.

|                                 | Unit            | This Work | JSSC<br>2012<br>[18] | TBCS<br>2016<br>[13] | TMTT<br>2017<br>[14] | JSSC<br>2017<br>[15] | TIM<br>2017<br>[2] | TCAS<br>2018<br>[19] | TSWMCS<br>2019<br>[16] | TMTT<br>2020<br>[17] |

|---------------------------------|-----------------|-----------|----------------------|----------------------|----------------------|----------------------|--------------------|----------------------|------------------------|----------------------|

| Received Power, P <sub>RX</sub> | mW              | 20        | 10                   | 0.224                | 18                   | 0.16                 | 5.29               | N/A                  | 79.43                  | N/A                  |

| RX Area, $A_{RX}$               | mm <sup>2</sup> | 0.098     | 0.49                 | 1                    | 25                   | 9                    | 0.87               | 0.45                 | 36                     | 33.6                 |

| TX Area, $A_{TX}$               | mm <sup>2</sup> | 0.12      | 0.49                 | 576                  | 900                  | 625                  | 0.93               | N/A                  | 784                    | 2500                 |

| Distance, d                     | mm              | 0.02      | 0.02                 | 12                   | 10                   | 10                   | 0.1                | 2.5                  | 10                     | 20                   |

| Efficiency, η                   | %               | 16        | 10                   | 1.02                 | 19.1                 | 1.23                 | 37.5               | N/A                  | 21                     | 5.1                  |

| Carrier Frequency, $f_c$        | GHz             | 200       | 0.3                  | 0.2                  | 0.0136               | 0.144                | 0.144              | 0.865                | 0.025                  | 1.9                  |

| Supply Voltage, V <sub>DD</sub> | V               | 1.0/1.8 * | 1.2                  | N/A                  | 2                    | 1.5                  | 1.9                | N/A                  | N/A                    | N/A                  |

| CMOS Technology                 | nm              | 28        | 350                  | N/A                  | 180                  | 180                  | 180                | 180                  | 65                     | N/A                  |

Table 1. Performance of the proposed sub-THz wireless power transfer.

\* 28 nm: two devices used (standard CMOS: 1V, I/O device: 1.8V for PA)

The conventional WPTs shown in Table 1 are designed for two practical applications. The biomedical related WPTs [13–17] could transfer the power through a greater distance with a very large TX chip size. The wafer-level testing related WPTs [2,18,19] performs the power delivery in a much shorter distance, but the TX chip area is much smaller. When the trade-off between the TX chip size and the delivered distance is eliminated, small RX chip size and maximum power delivery are the most critical factors required for both biomedical WPTs and wafer-level testing WPTs. The proposed WPT RX chip occupies only 0.098 mm<sup>2</sup> area (5 times smaller than the smallest one [19]). The maximum power delivery of the proposed WPT is 20 mW (only [16] could provide 4 times more power, but the RX chip size is 367 times larger). To be designed for the wafer-level testing applications, the proposed WPT could significantly reduce the chip size and improve power delivery. Therefore, more DUTs on a single wafer could be tested at the same time, the testing speed could be improved.

#### 4. Conclusions

In this paper, we presented a sub-THz wireless power transfer interface for non-contact wafer-level testing. Multiple case studies of the sub-THz WPTs have been designed in a 28-nm CMOS RF process. To enhance the PTE, the PA has been designed and analyzed to obtain the highest gain at 200 GHz frequency operation. The VCO has been well designed for reasonable output voltage range, allowing the best performance operation of the PA. From the advance rectifier design techniques that have been reported, the upgraded rectifier could achieve 78% PCE at the desired sub-THz frequency operation. The simulated proposed single-channel WPT could transfer 2.5 mW power to the load with the PTE of 16%. To enhance the power delivery, the 8-channels sub-THz WPT has been simulated, which could provide up to 20 mW power to the DUT while the total chip size is only 0.12 mm<sup>2</sup> and 0.098 mm<sup>2</sup> for TX and RX, respectively.

**Author Contributions:** Conceptualization, G.-s.B.; formal analysis, investigation, the layout design, the writing, simulations, H.D.-b.; supervision, G.-s.B. Both authors have read and agreed to the published version of the manuscript.

Funding: This work was supported by the Inha University Research Grant under Grant INHA-00000.

**Acknowledgments:** This work was supported by the Inha University Research Grant under Grant INHA-00000. The prototype design is implemented in a 28-nm CMOS process provided by Samsung Foundry.

Conflicts of Interest: The authors declare no conflicts of interest.

#### References

Radecki, A.; Chung, H.; Yoshida, Y.; Miura, N.; Shidei, T.; Ishikuro, H.; Kuroda, T. 6W/25mm 2 inductive power transfer for non-contact wafer-level testing. In Proceedings of the 2011 IEEE International Solid-State Circuits Conference, San Francisco, CA, USA, 20–24 February 2011. [CrossRef]

- 2. Lee, M.; Lee, C.; Park, C. Transceiver for wireless power transfer using a cross-coupled oscillator for a wireless on-wafer test. *IEEE Trans. Instrum. Meas.* **2017**, *66*, 2097–2105. [CrossRef]

- Sellathamby, C.V.; Reja, M.M.; Fu, L.; Bai, B.; Reid, E.; Slupsky, S.H.; Filanovsky, I.M.; Iniewski, K. Noncontact wafer probe using wireless probe cards. In Proceedings of the IEEE International Conference on Test, Charlotte, NC, USA, 6 February 2006; pp. 6–452.

- Sasaki, M.; Iwata, A. A 0.95 mW/1.0 Gbps spiral-inductor based wireless chip-interconnect with asynchronous communication scheme. In Proceedings of the Digest of Technical Papers. 2005 Symposium on VLSI Circuits, Kyoto, Japan, 16–18 June 2005; pp. 348–351.

- Miura, N.; Kohama, Y.; Sugimori, Y.; Ishikuro, H.; Sakurai, T.; Kuroda, T. An 11Gb/s Inductive-Coupling Link with Burst Transmission. Available online: https://xueshu.baidu.com/usercenter/paper/show?paperid= 200853f11db15627204c3fd6a2c6391a&site=xueshu\_se (accessed on 17 July 2020).

- Onizuka, K.; Kawaguchi, H.; Takamiya, M.; Kuroda, T.; Sakurai, T. Chip-to-Chip Inductive Wireless Power Transmission System for SiP Applications. Available online: https://www.researchgate.net/publication/ 224060141\_Chip-to-Chip\_Inductive\_Wireless\_Power\_Transmission\_System\_for\_SiP\_Applications (accessed on 17 July 2020).

- Yuan, Y.; Radecki, A.; Miura, N.; Aikawa, I.; Take, Y.; Ishikuro, H.; Kuroda, T. Simultaneous 6Gb/s data and 10mW power transmission using nested clover coils for non-contact memory card. In Proceedings of the 2010 Symposium on VLSI Circuits, Honolulu, HI, USA, 16–18 June 2010; pp. 199–200.

- Kawai, S.; Ishikuro, H.; Kuroda, T. A 2.5 Gb/s/ch 4PAM Inductive-Coupling Transceiver for Non-Contact Memory Card. Available online: https://xueshu.baidu.com/usercenter/paper/show?paperid= 0595d91182b2c1e235023b4450f5d276&site=xueshu\_se (accessed on 17 July 2020).

- Yuxiang, Y.; Miura, N.; Imai, S.; Ochi, H.; Kuroda, T. Digital Rosetta Stone: A Sealed Permanent Memory with Inductive-Coupling Power and Data Link. Available online: https://xueshu.baidu.com/usercenter/ paper/show?paperid=5ce9c34bf40c18f4b7e95e485db7afcb&site=xueshu\_se (accessed on 17 July 2020).

- Niitsu, K.; Kawai, S.; Miura, N.; Ishikuro, H.; Kuroda, T. A 65 fJ/b inductive-coupling inter-chip transceiver using charge recycling technique for power-aware 3D system integration. In Proceedings of the 2008 IEEE Asian Solid-State Circuits Conference, Fukuoka, Japan, 5 December 2008; pp. 97–100.

- Miura, N.; Kasuga, K.; Saito, M.; Kuroda, T. An 8Tb/s 1pJ/b 0.8 mm 2/Tb/s QDR Inductive-Coupling Interface between 65nm CMOS GPU and 0.1 μm DRAM. Available online: https://www.researchgate.net/publication/238733942\_Tbs\_QDR\_Inductive-Coupling\_Interface\_ Between\_65nm\_CMOS\_GPU\_and\_01m\_DRAM (accessed on 17 July 2020).

- 12. Miura, N.; Shidei, T.; Yuan, Y.; Kawai, S.; Takatsu, K.; Kiyota, Y.; Asano, Y.; Kuroda, T. A 0.55 V 10 fJ/bit inductive-coupling data link and 0.7 V 135 fJ/cycle clock link with dual-coil transmission scheme. *IEEE J. Solid-State Circuits* **2011**, *46*, 965–973. [CrossRef]

- 13. Ahn, D.; Ghovanloo, M. Optimal design of wireless power transmission links for millimeter-sized biomedical implants. *IEEE Trans. Biomed. Circuits Syst.* **2015**, *10*, 125–137. [CrossRef] [PubMed]

- 14. Yang, C.L.; Chang, C.K.; Lee, S.Y.; Chang, S.J.; Chiou, L.Y. Efficient four-coil wireless power transfer for deep brain stimulation. *IEEE Trans. Microwave Theory Tech.* **2017**, *65*, 2496–2507. [CrossRef]

- Kim, C.; Ha, S.; Park, J.; Akinin, A.; Mercier, P.P.; Cauwenberghs, G. A 144-MHz fully integrated resonant regulating rectifier with hybrid pulse modulation for mm-sized implants. *IEEE J. Solid-State Circuits* 2017, 52, 3043–3055. [CrossRef]

- 16. Biswas, D.K.; Tasneem, N.T.; Mahbub, I. Optimization of Miniaturized Wireless Power Transfer System to Maximize Efficiency for Implant Biomedical Devices. Available online: https://www.researchgate.net/publication/332261113\_Optimization\_of\_Miniaturized\_Wireless\_Power\_ Transfer\_System\_to\_Maximize\_Efficiency\_for\_Implantable\_Biomedical\_Devices (accessed on 17 July 2020).

- Shah, S.A.A.; Yoo, H. Radiative Near-Field Wireless Power Transfer to Scalp-Implantable Biotelemetric Device. *IEEE Trans. Microwave Theory Tech.* 2020, 68, 2944–2953. [CrossRef]

- Radecki, A.; Yuan, Y.; Miura, N.; Aikawa, I.; Take, Y.; Ishikuro, H.; Kuroda, T. Simultaneous 6-Gb/s data and 10-mW power transmission using nested clover coils for noncontact memory card. *IEEE J. Solid-State Circuits* 2012, 47, 2484–2495. [CrossRef]

- Finocchiaro, A.; Girlando, G.; Motta, A.; Pagani, A.; Ragonese, E.; Palmisano, G. Wafer-Level Contactless Testing Based on UHF RFID Tags With Post-Process On-Chip Antennas. *IEEE Trans. Circuits Syst. Express Briefs* 2018, 65, 1355–1359. [CrossRef]

- 20. Ghovanloo, M.; Najafi, K. Fully integrated wideband high-current rectifiers for inductively powered devices. *IEEE J. Solid-State Circuits* **2004**, *39*, 1976–1984. [CrossRef]

- 21. Kotani, K.; Sasaki, A.; Ito, T. High-efficiency differential-drive CMOS rectifier for UHF RFIDs. *IEEE J. Solid-State Circuits* **2009**, *44*, 3011–3018. [CrossRef]

- 22. Yuen, P.W.; Chong, G.; Ramiah, H. A high efficient dual-output rectifier for piezoelectric energy harvesting. *AEU Int. J. Electron. Commun.* **2019**, *111*, 152922. [CrossRef]

- 23. Cha, H.-K.; Park, W.-T.; Je, M. A CMOS rectifier with a cross-coupled latched comparator for wireless power transfer in biomedical applications. *IEEE Trans. Circuits Syst. Express Briefs* **2012**, *59*, 409–413. [CrossRef]

- 24. Hui, S.Y.R.; Zhong, W.; Lee, C.K. A critical review of recent progress in mid-range wireless power transfer. *IEEE Trans. Power Electron.* **2013**, *29*, 4500–4511. [CrossRef]

- 25. Lu, F.; Zhang, H.; Hofmann, H.; Mi, C.C. An inductive and capacitive combined wireless power transfer system withLC-compensated topology. *IEEE Trans. Power Electron.* **2016**, *31*, 8471–8482. [CrossRef]

- 26. Narayanamoorthi, R. Modeling of Capacitive Resonant Wireless Power and Data Transfer to Deep Biomedical Implants. *IEEE Trans. Compon. Packag. Manuf. Technol.* **2019**, *9*, 1253–1263. [CrossRef]

- 27. Yuxiang, Y.; Yoshida, Y.; Kuroda, T. Non-Contact 10% Efficient 36mW Power Delivery Using on-Chip Inductor in 0.18-μm CMOS. Available online: https://xueshu.baidu.com/usercenter/paper/show?paperid= ad93f441519ed74e64469a5c60f7f5d8&site=xueshu\_se (accessed on 17 July 2020).

- 28. Miller, J.M.; Onar, O.C.; Chinthavali, M. Primary-side power flow control of wireless power transfer for electric vehicle charging. *IEEE J. Emerg. Sel. Top. Power Electron.* **2014**, *3*, 147–162. [CrossRef]

- Lu, F.; Zhang, Y.; Zhang, H.; Zhu, C.; Diao, L.; Gong, M.; Zhang, W.; Mi, C. A low-voltage and high-current inductive power transfer system with low harmonics for automatic guided vehicles. *IEEE Trans. Veh. Technol.* 2019, *68*, 3351–3360. [CrossRef]

- 30. Halim, M.A.; Smith, S.E.; Samman, J.M.; Arnold, D.P. A High-Performance Electrodynamic Micro-Receiver for Low-Frequency Wireless Power Transfer. Available online: https://xueshu.baidu.com/usercenter/paper/show? paperid=126v0e20x37d0010rd2k0r10b7595652&site=xueshu\_se&hitarticle=1 (accessed on 17 July 2020).

© 2020 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).