# Article Subthreshold Characteristics of AlGaN/GaN MIS-FinFETs with Controlling Threshold Voltages

## Quan Dai and Jung-Hee Lee \*

School of Electronic and Electrical Engineering, Kyungpook National University, Daegu 41566, Korea; quanshiduan@knu.ac.kr

\* Correspondence: jlee@ee.knu.ac.kr

Received: 12 October 2020; Accepted: 19 November 2020; Published: 21 November 2020

**Abstract:** AlGaN/GaN metal-insulator-semiconductor field-effect transistors with fin structures (AlGaN/GaN MIS-FinFETs) were fabricated and characterized by changing fin width and using different dielectric layers. The FinFET with 20 nm-thick SiO<sub>2</sub> dielectric layer exhibits a very small subthreshold swing (SS) of 56 mV/decade. However, the threshold voltage of the device is too low to ensure low off-state leakage current (at the gate voltage of 0 V), even though the fin width of the device is reduced to 30 nm, which would not meet the requirement for low standby power consumption. On the other hand, the FinFET with a 10 nm-thick Al<sub>2</sub>O<sub>3</sub> dielectric layer and a much wider fin width of 100 nm shows normally-off operation with a threshold voltage of 0.8 V, SS of 63 mV/dec, and very low off-state current of 1 nA/mm. When the fin width is reduced to 40 nm, the threshold voltage of the FinFET is increased to 2.3 V and the SS is decreased to 52 mV/decade. These excellent switching performances convince us that the FinFETs might be promising either for low voltage logic or for efficient power switching applications. The observed SS values, which are smaller than the theoretical Boltzmann limit (60 mV/decade), can be explained by the concept of the voltage-dependent effective channel width.

Keywords: AlGaN/GaN; FinFET; Sub-60 mV/decade

## 1. Introduction

AlGaN/GaN-based high electron mobility transistors (HEMTs) are very promising for high power and high-frequency applications due to their wide bandgap, large critical electric field, and high saturation velocity [1–4]. Recently, AlGaN/GaN metal-insulator-semiconductor field-effect transistors with fin structures (MIS-FinFETs) have been widely investigated to achieve better gate controllability and higher device linearity, compared with conventional planar HEMTs, which results in a great reduction of off-state leakage current ( $I_{OFF}$ ), suppression of drain induced barrier lowering (DIBL), and improvement of subthreshold swing (SS) [5–10]. It is worth noting that the threshold voltage ( $V_{TH}$ ) of the MIS-FinFET increases as the fin width ( $W_{fin}$ ) decreases due to the lateral depletion of 2-dimensional electron gas (2DEG) channel by sidewall gate and eventually the device can show a normally-off operation when the  $W_{fin}$  is reduced to a few tenths of a nanometer [11,12], without adapting additional process methods, such as recessed gate, P-GaN gate, thin AlGaN barrier layer, and cascode structure, usually applied to conventional planar HEMTs [13–16].

Our previous work demonstrated that AlGaN/GaN MIS-FinFETs with  $W_{fin}$  of around 30 nm can show not only normally-off operation, but also extremely low I<sub>OFF</sub> as well as small SS (smaller than theoretical Boltzmann limit of < 60 mV/decade) [17]. These excellent performances of the AlGaN/GaN MIS-FinFETs suggest that the GaN-based materials, combined with novel nano-structure such as fin or nanowire, can offer an opportunity for a new possible low power logic device application [18–20], in addition to conventional efficient power switching device application which requires a relatively large positive  $V_{TH}$  to ensure safe device operation as well as low standby power consumption. For low-power logic applications, however, it is better to keep the  $V_{TH}$  of the device low as long as the off-state leakage current ( $I_{OFF}$ ; at gate voltage,  $V_G = 0$  V) is low, which can be achieved with very steep SS.

In this work, two different AlGaN/GaN MIS-FinFETs with either 20 nm-thick  $SiO_2$  or 10 nm-thick  $Al_2O_3$  dielectric layers were characterized to investigate the effects of the fixed oxide charge and the surface trap at the GaN/dielectric interface on the device performances with varying the  $W_{fin}$ . In addition, the MIS-FinFETs with different sidewall planes, either steep m-plane or sloped plane (12° off-angle to m-plane), were also characterized for the same purpose.

#### 2. Device Fabrication

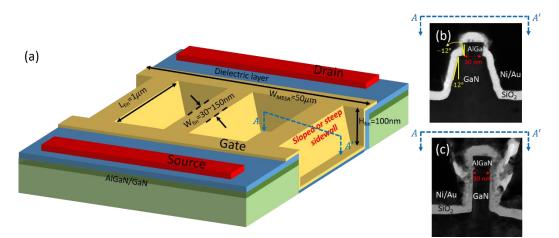

Epitaxial layers of 2  $\mu$ m-thick highly resistive undoped GaN, 50 nm-thick GaN channel layer and 25 nm-thick Al<sub>0.25</sub>Ga<sub>0.75</sub>N barriers were sequentially grown on the sapphire substrate by using metal-organic chemical vapor deposition (MOCVD). The 2DEG density of 8.83×10<sup>12</sup> cm<sup>-2</sup> and the electron mobility of 1800 cm<sup>2</sup>·V<sup>-1</sup>·s<sup>-1</sup> were estimated by Hall measurement. Figure 1a shows the schematic image of AlGaN/GaN MIS-FinFET. The fabrication processes of the FinFETs were similar to our previous work [17]. Figure 1b,c exhibit the cross-sectional TEM images for the fin with sloped and steep sidewall surface, respectively. It was found that the formation of fin shape depends on the etching time in anisotropic lateral etching tetramethylammonium hydroxide (TMAH: 25% solution at 85 °C) solution. It was also found the slope of the dry-etched fin, prior to the TMAH wet etching, is important in determining the fin shape. However, the exact etching mechanism for the fin shape still remains unclear and further study is required. It is worth noting that, as shown Figure 1b, the sloped sidewall surface has ~12° off-angle to the m-plane, while the top AlGaN layer has a negatively sloped shape with almost the same off-angle as shown in both Figure 1b,c. This negative slope might be due to the existence of stress induced by lattice mismatch between AlGaN and GaN layers, which increases the etch rate at the interface during TAMH wet etching.

**Figure 1.** (**a**) Schematic image of AlGaN/GaN-based FinFET with either sloped sidewall surface or steep sidewall surface; (**b**) Cross-sectional TEM image of fin with sloped sidewall surface; (**c**) Cross-sectional TEM image of fin with steep sidewall surface.

The dielectrics, 20 nm-thick plasma enhanced chemical vapor deposited (PECVD) SiO<sub>2</sub> layer and 10 nm-thick atomic layer deposited (ALD) Al<sub>2</sub>O<sub>3</sub> layer, were used to investigate the influence of different dielectric layer on device performance. The gate length (L<sub>G</sub>), which corresponds to fin length (L<sub>fin</sub>), and the mesa width for all devices are 1 and 50  $\mu$ m, respectively. Both of the gate to drain spacing L<sub>GD</sub> and the gate to source spacing L<sub>GS</sub> are 5  $\mu$ m. The fin height (H<sub>fin</sub>) is 100 nm and the W<sub>fin</sub> varies from 30 to 150 nm. All the devices have a fin number (N<sub>fin</sub>) of 45. Drain current (I<sub>D</sub>) and transconductance (g<sub>m</sub>) are normalized by gate width ( $W_G$ ) = [ $W_{fin}$  + width of GaN channel (50 nm) × 2] ×  $N_{fin}$ , and  $V_{TH}$  is defined as the  $V_G$  when drain current  $I_D$  equals to 0.1  $\mu A \times \frac{W_G}{L_C}$ .

#### 3. Results and Discussion

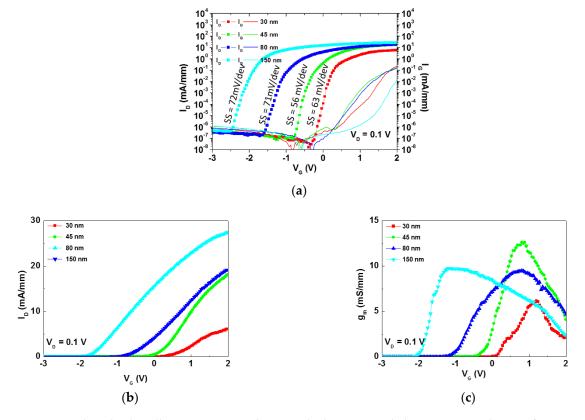

Figure 2a,b show the logarithmic and linear transfer curves, respectively, for the sloped sidewall AlGaN/GaN MIS-FinFETs with 20 nm-thick SiO<sub>2</sub> gate dielectric varying the W<sub>fin</sub> from 150 to 30 nm. The key parameters such as  $V_{TH}$ , SS,  $g_m$  peak value, full width at half maximum (FWHM) of  $g_m$ , and hysteresis of all the devices are summarized and shown in Table 1. The V<sub>TH</sub> of the sloped FinFET with  $W_{fin}$  is 150 nm is -1.9 V and it shifts to a positive direction as the  $W_{fin}$  narrows, showing the  $V_{TH}$ of 0.3 V when  $W_{fin}$  is reduced to 30 nm. This positive shift of the  $V_{TH}$  is due to lateral depletion of the 2DEG channel from the sidewall. The SS values for all devices are smaller than 72 mV/dec, which are relatively low compared to those of conventional AlGaN/GaN-based HEMTs [21-23]. For the wide FinFETs with  $W_{fin}$  of 150 and 80 nm, the  $V_{TH}$  of the 2DEG channel is much lower than that of the MOS channel at sidewall surface and hence the 2DEG channel current dominates the subthreshold current of the device. In this case, the SS (~ 70 mV/dec) for the device can be mainly determined from the trap capacitance at AlGaN/GaN interface (Cit,AlGaN/GaN) and the existence of the depletion capacitance  $(C_{dep})$  in wide bottom fin body below the 2DEG channel, which is not completely depleted by the lateral electric field from the sidewall gate. Besides, the V<sub>TH</sub> difference between the 2DEG channel and MOS channel of these FinFETs with wide W<sub>fin</sub> are relatively large and the two-channel currents become merged as the gate voltage increases to have the broad gm curves as shown in Figure 2c, which is important in improving the device linearity [8,24].

**Figure 2.** Sloped sidewall MIS-FinFETs with 20 nm-thick  $SiO_2$  gate dielectric varying the  $W_{fin}$  from 150 to 30 nm. (a) Logarithmic transfer curves; (b) Linear transfer curves; (c) Transconductance curves.

| W <sub>fin</sub> (nm) | V <sub>TH</sub> (V) | SS (mV/dec) | g <sub>m</sub> Peak (mS/mm) | FWHM of g <sub>m</sub> (V) | Hysteresis (mV) |

|-----------------------|---------------------|-------------|-----------------------------|----------------------------|-----------------|

| 30                    | 0.3                 | 63          | 6.1                         | 0.92                       | 400             |

| 45                    | -0.2                | 54          | 12.6                        | 1.52                       | 320             |

| 80                    | -0.9                | 71          | 9.5                         | 2.40                       | 240             |

| 150                   | -1.9                | 72          | 9.8                         | 3.12                       | 120             |

Table 1. Key parameters for each device exhibited in Figure 2.

On the other hand, the narrow FinFET with  $W_{fin}$  of 45 nm has a sharper and higher  $g_m$  peak as can be seen in Figure 2c, which means that the  $V_{TH}$  of the 2DEG channel and MOS channel are almost the same and hence both channels simultaneously turn on/off and the effective channel width of the device can be modulated with the gate voltage, which results in very small SS as low as 56 mV/dec, smaller than the theoretical Boltzmann limit of 60 mV/dec. As discussed in our previous work [17], the 2DEG channel will be generated at the center of the 2DEG channel and laterally spread until occupying the whole 2DEG channel as  $V_G$  increases from the  $V_{TH}$  of the 2DEG channel to just above it. Then, the MOS channel will instantaneously turn on because there is only a tiny  $V_{TH}$  difference between the top 2DEG channel and the sidewall MOS channel. In other words, the channel width first spread laterally within the 2DEG channel and then immediately spread vertically into the MOS channel, which makes the concept of gate-dependent effective channel width modulation reasonable. This sub-60 mV/dec SS can be understood by considering the expression for new  $SS_{W(V_G)}$  which includes the gate voltage-dependent channel width modulation [17] as shown below,

$$SS_{W(V_G)} = \frac{1}{\frac{d(logI_{D,sub})}{dV_G}} = \frac{1}{A + \frac{1}{SS_{con}}} = \frac{SS_{con}}{A \cdot \frac{1}{SS_{con}} + 1}$$

(1)

where  $\frac{d(logI_{D,sub})}{dV_G} = \frac{d[logW(\varphi_s)]}{dV_G} + \frac{d\left[\int_0^{V_D} Q_{ch}(V,\varphi_s)dV\right]}{dV_G} + \frac{d(log\mu)}{dV_G}$ ,  $I_{D,sub} = \mu \frac{W(\varphi_s)}{L} \int_0^{V_D} Q_{ch}(V,\varphi_s)dV$ . In these equations,  $\varphi_s$  and  $Q_{ch}(V,\varphi_s)$  are the surface potential and the channel charges in the subthreshold region, respectively.  $W_{(\varphi_s)}$  is the surface potential-dependent effective channel width which is constant in conventional devices.  $I_{D,sub}$  is the channel current in the subthreshold region and  $\frac{d(logI_{D,sub})}{dV_G}$  is the channel current. The first term  $\frac{d[logW(\varphi_s)]}{dV_G}$  in  $\frac{d(logI_{D,sub})}{dV_G}$  is the channel width modulation and expressed as A in Equation (1). The third term is related to electron mobility and can be neglected. The inverse of the second term is  $SS_{con}$  for conventional devices without channel width modulation.  $SS_{con}$  can be expressed as,

$$SS_{con} = 2.3 \frac{kT}{q} \left( 1 + \frac{C_{dep} + C_{it}}{C_{ox}} \right)$$

<sup>(2)</sup>

where *k* is the Boltzmann's constant, *T* is temperature, *q* is electronic charge,  $C_{ox}$  is the capacitance for gate oxide, and  $C_{it}$  is the trap capacitance either for the interface of AlGaN/GaN or dielectric/GaN. Normally,  $SS_{con}$  is larger than 60 mV/dec and cannot explain the sub-60 mV/dec characteristic observed in this work.

When  $W_{fin}$  is further reduced to 30 nm, the SS of the device increases slightly above 60 mV/dec again. This is because the  $V_{TH}$  of the 2DEG channel increases and hence the simultaneous turning on of these two channels tends to break to make the channel width modulation less effective. The  $V_{TH}$  of the 2DEG channel becomes higher than that of the MOS channel and becomes positive to show normally-off operation with  $V_{TH}$  of 0.3 V. In this case, the MOS channel current at sidewall surface dominates the subthreshold characteristics of the device and the SS can be determined mainly from the trap capacitance ( $C_{it, SiO_2/GaN}$ ) at SiO<sub>2</sub>/GaN interface, which leads to increased SS of 63 mV/dec. As a result, Figure 2c indicates that the g<sub>m</sub> of the FinFET with  $W_{fin}$  of 30 nm becomes slightly broader and the peak value becomes lower again compared with that of FinFET with  $W_{fin}$  of 45 nm. As can be seen in

Figure 2a, SS first decreases below 60 mV/dec when  $W_{fin}$  is reduced to 45 nm and then increases again above 60 mV/dec with further decreasing  $W_{fin}$ , which depends on whether the 2DEG channel and MOS channel turn on at the same time or not as has already been discussed above. Correspondingly, with decreasing  $W_{fin}$ , as shown in Figure 2c,  $g_m$  curve becomes sharper as  $W_{fin}$  decreases to 45 nm, but becomes broad again when  $W_{fin}$  is reduced to 30 nm. Based on the tendency of SS and  $g_m$  curves as decreasing  $W_{fin}$  as shown in Figure 2a,b, it can be concluded that the  $g_m$  peak becomes sharp showing excellent subthreshold characteristics with SS of sub-60 mV/dec, if 2DEG channel and MOS channel of a FinFET are simultaneously turned on/off. However, most of the FinFETs with SiO<sub>2</sub> dielectric layer investigated in this work exhibits normally-on operation, thus they are not adequate to be used as efficient power switching or low power logic application due to large I<sub>OFF</sub>, even though they exhibited excellent SS. A similar argument can be addressed even for the normally-off FinFET with  $W_{fin}$  of 30 nm, because I<sub>OFF</sub> of the FinFET is still very high due to its low V<sub>TH</sub>.

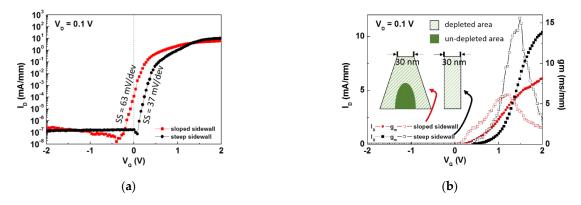

Figure 3a shows the comparison of the logarithmic transfer curves obtained from the FinFETs with sloped and steep sidewall surfaces. It is observed that the steep sidewall surface is m-plane and very smooth and uniform and has the lowest surface trap density, while the sloped sidewall has a rather rough and nonuniform surface, as shown in Figure 1b. The key parameters such as  $V_{TH}$ , SS,  $g_m$  peak value, and FWHM of  $g_m$  of all the devices are summarized and shown in Table 2. Both devices, which have the same W<sub>fin</sub> of 30 nm and 20 nm-thick SiO<sub>2</sub> gate dielectric layer, exhibit normally-off operation, but the sloped sidewall device exhibits much higher IOFF of 100 nA/mm, measured at  $V_{G} = 0 V_{c}$  compared with that of steep sidewall device. The high  $I_{OFF}$  of the sloped sidewall device is due to its lower V<sub>TH</sub> of 0.3 V, compared to V<sub>TH</sub> of 0.6 V of the steep sidewall device. The lower V<sub>TH</sub> of the sloped device is probably because the sidewall surface has a higher density of positive effective oxide charge at the  $GaN/SiO_2$  interface as well as higher surface trap density caused by a relatively rough surface, compared to the steep m-plane sidewall surface [25]. This high positive oxide charge density in the sloped device lowers V<sub>TH</sub> of the sidewall MOS channel to increase I<sub>OFF</sub>. The SS of steep sidewall device is as low as 37 mV/dec due to the simultaneous turning on of 2DEG channel and MOS channel and the effective channel width modulation as discussed before [17]. On the other hand, the sloped sidewall device exhibits a relatively larger SS of 63 mV/dec, which could be explained by the existence of non-negligible  $C_{dep}$  caused by the undepleted part at the wide fin bottom and relatively large  $C_{it, SiO_2/GaN}$  due to a rough sidewall surface [25], which increases both SS<sub>con</sub> and  $SS_{W(V_G)}$ , while the  $C_{dep}$  can be ignored for the device with a steep sidewall because the entire fin is narrow and completely depleted from the electric field of the sidewall gate at off-state. The schematic images of both sloped and steep sidewall fin structures with un-depleted/depleted areas are shown in Figure 3b. The steep sidewall device exhibits a sharper and higher  $g_m$  peak, as shown in Figure 3b, which indicates that both the 2DEG channel and the MOS channel of the device simultaneously turn on almost at the same time.

**Figure 3.** (a) Logarithmic transfer curves of sloped sidewall FinFETs (red line) in this work and steep sidewall FinFETs (black line) in our previous work; (b) Transfer curves of the two devices in (a). The schematic images of sloped and steep sidewall fin structures are shown in the insert of (b).

Table 2. Key parameters for each device exhibited in Figure 3.

| W <sub>fin</sub> (nm) | Sidewall Type | V <sub>TH</sub> (V) | SS (mV/dec) | g <sub>m</sub> Peak (mS/mm) | FWHM of g <sub>m</sub> (V) |

|-----------------------|---------------|---------------------|-------------|-----------------------------|----------------------------|

| 30                    | sloped        | 0.3                 | 63          | 6.1                         | 0.92                       |

| 30                    | steep         | 0.6                 | 37          | 15.6                        | 0.60                       |

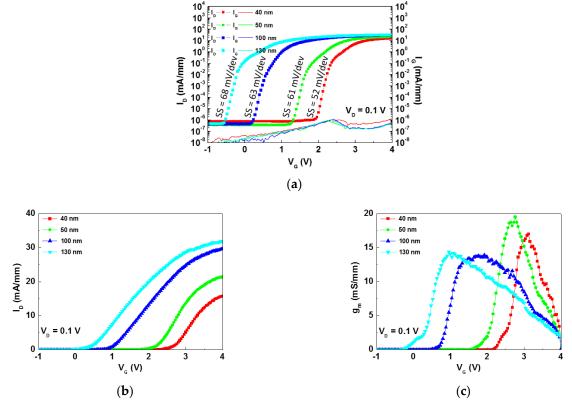

To investigate the effect of the gate dielectric on the device performances, the SiO<sub>2</sub> layer was replaced with 10 nm-thick  $Al_2O_3$  layers on the sloped sidewall FinFETs. All FinFETs with  $W_{fin}$  varied from 130 to 40 nm exhibit normally-off operation as shown in Figure 4a,b. The key parameters such as  $V_{TH}$ , SS,  $g_m$  peak value, FWHM of  $g_m$ , and hysteresis of all the devices are summarized and shown in Table 3. Similarly,  $V_{TH}$  of the FinFET shifts to a positive direction as  $W_{fin}$  decreases, but it increases up to a much higher value of 2.5 V for the FinFET with  $W_{fin}$  of 40 nm, which is probably due to the existence of the negative effective oxide charge at the interface between the  $Al_2O_3$  dielectric layer and GaN [5,26,27].

**Figure 4.** Sloped sidewall MIS-FinFETs with 10 nm-thick  $Al_2O_3$  gate dielectric varying the  $W_{fin}$  from 130 to 40 nm. (a) Logarithmic transfer curves; (b) Linear transfer curves; (c) Transconductance curves.

| <b>Table 3.</b> Key parameters for each device exhibited in Figure 4. |

|-----------------------------------------------------------------------|

|-----------------------------------------------------------------------|

| W <sub>fin</sub> (nm) | $V_{TH}$ (V) | SS (mV/dec) | g <sub>m</sub> Peak (mS/mm) | FWHM of g <sub>m</sub> (V) | Hysteresis (mV) |

|-----------------------|--------------|-------------|-----------------------------|----------------------------|-----------------|

| 40                    | 2.3          | 52          | 17                          | 0.88                       | 400             |

| 50                    | 1.8          | 61          | 19.5                        | 1.04                       | 480             |

| 100                   | 0.8          | 63          | 13.9                        | 2.12                       | 400             |

| 130                   | 0            | 68          | 14.4                        | 2.44                       | 400             |

It is also observed that the FinFETs show considerably low  $I_{OFF}$  of ~0.1 nA/mm, except the FinFET with  $W_{fin}$  of 130 nm, which is essential for reducing the standby power consumption. Especially, the FinFET with  $W_{fin}$  of 40 nm exhibits excellent SS of 52 mV/dec, also smaller than the theoretically limited value of 60 mV/dec, which can be explained by the concept of effective channel width

modulation and the simultaneous turn-on of 2DEG channel and MOS channel as discussed before. This fast switching characteristics of the device with its relatively high  $V_{TH}$  of 2.5 V and low off-state leakage current would lead to improvement of efficiency and ensure the safety of power switching devices [28]. The g<sub>m</sub> peak becomes sharper as the  $W_{fin}$  of the FinFET decreases, as shown in Figure 4b, which is similar to the case of the FinFETs with SiO<sub>2</sub> gate dielectric layer and a similar argument can be also addressed for the reason.

According to the discussion above, it can be seen that it is a possible method to realize relatively high  $V_{TH}$ , small SS, and low  $I_{OFF}$  in AlGaN/GaN MIS-FinFETs by carefully adjusting  $W_{fin}$  as well as choosing the sidewall plane, which corresponds to the controlling of threshold voltages. As  $W_{fin}$  varies, the shape of  $g_m$  curve becomes sharper as the  $V_{TH}$  difference between the 2DEG channel and the MOS channel becomes closer.

### 4. Conclusions

In this work, AlGaN/GaN MIS-FinFETs were fabricated and characterized using 20 nm-thick SiO<sub>2</sub> and 10 nm-thick Al<sub>2</sub>O<sub>3</sub> as dielectric layers, respectively. The effects of the sidewall plane on device performance were also investigated. The sloped sidewall FinFET with 20 nm-thick SiO<sub>2</sub> dielectric layers and W<sub>fin</sub> of 45 nm shows the lowest SS of 56 mV/dec among the FinFETs which can be explained by the concept of effective channel width modulation and the simultaneous turn-on of 2DEG channel and sidewall MOS channel. The SS is further decreased to 37 mV/dec for the steep sidewall FinFET with W<sub>fin</sub> of 30 nm. However, the sloped sidewall FinFET with the same W<sub>fin</sub> of 30 nm, which has a relatively rough sidewall surface, show low V<sub>TH</sub>, large SS, and high I<sub>OFF</sub> probably due to the high density of positive effective fixed oxide charges and trap charges at the SiO<sub>2</sub>/GaN interface. On the other hand, the sloped sidewall FinFETs with 10 nm-thick Al<sub>2</sub>O<sub>3</sub> dielectric layer show normally-off operation with relatively high V<sub>TH</sub>, small SS, and low I<sub>OFF</sub>. In our opinion, these performances are probably due to the existence of negative effective fixed oxide charge at the Al<sub>2</sub>O<sub>3</sub>/GaN interface, even though the FinFETs have sloped sidewalls. The device with W<sub>fin</sub> of 40 nm exhibits SS of 52 mV/dec with V<sub>th</sub> of 2.3 V, which might be promising for efficient power switching application.

**Author Contributions:** Conceptualization, Q.D.; Formal analysis, Q.D. and J.-H.L.; Investigation, J.-H.L.; Methodology, Q.D.; Supervision, J.-H.L.; Writing—original draft, Q.D.; Writing—review & editing, J.-H.L. All authors have read and agreed to the published version of the manuscript.

**Funding:** This work was partly supported by the BK21 Plus funded by the Ministry of Education (21A20131600011) and this investigation was financially supported by Samsung Research Funding & Incubation Center of Samsung Electronics under Project Number SRFC-TA1703-08.

**Conflicts of Interest:** The authors declare no conflict of interest. The funders had no role in the design of the study; in the collection, analyses, or interpretation of data; in the writing of the manuscript, or in the decision to publish the results.

#### References

- Chen, K.J.; Häberlen, O.; Lidow, A.; Tsai, C.L.; Ueda, T.; Uemoto, Y.; Wu, Y. GaN-on-Si power technology: Devices and applications. *IEEE Trans. Electron Devices* 2017, 64, 779–795. [CrossRef]

- Khandelwal, S.; Chauhan, Y.S.; Fjeldly, T.A.; Ghosh, S.; Pampori, A.; Mahajan, D.; Dangi, R.; Ahsan, S.A. ASM GaN: Industry Standard Model for GaN RF and Power Devices—Part 1: DC, CV, and RF Model. *IEEE Trans. Electron Devices* 2019, *66*, 80–86. [CrossRef]

- 3. Flack, T.J.; Pushpakaran, B.N.; Bayne, S.B. GaN Technology for Power Electronic Applications: A Review. *J. Electron Mater.* **2016**, *45*, 2673–2682. [CrossRef]

- Tang, Z.; Jiang, Q.; Lu, Y.; Huang, S.; Yang, S.; Tang, X.; Chen, K.J. 600-V Normally off SiNx/AlGaN/GaN MIS-HEMT with large gate swing and low current collapse. *IEEE Electron Device Lett.* 2013, 34, 1373–1375. [CrossRef]

- 5. Im, K.S.; Kim, R.H.; Kim, K.W.; Kim, D.S.; Lee, C.S.; Cristoloveanu, S.; Lee, J.H. Normally off single-nanoribbon Al<sub>2</sub>O<sub>3</sub>/GaN MISFET. *IEEE Electron Device Lett.* **2013**, *34*, 27–29. [CrossRef]

- Zhang, H.S.; Ma, X.H.; Zhang, M.; Lu, Y.; Zhu, Q.; Zhao, Z.Y.; Yi, C.P.; Yang, L.A.; Ma, P.J.; Hao, Y. Influence of Different Fin Configurations on Small-Signal Performance and Linearity for AlGaN/GaN Fin-HEMTs. *IEEE Trans. Electron Devices* 2019, 66, 3302–3309. [CrossRef]

- 7. Zhu, M.; Ma, J.; Nela, L.; Erine, C.; Matioli, E. High-Voltage Normally-off Recessed Tri-Gate GaN Power MOSFETs with Low on-Resistance. *IEEE Electron Device Lett.* **2019**, *40*, 1289–1292. [CrossRef]

- 8. Jo, Y.W.; Son, D.H.; Won, C.H.; Im, K.S.; Seo, J.W.; Kang, I.M.; Lee, J.H. AlGaN/GaN FinFET with Extremely Broad Transconductance by Side-Wall Wet Etch. *IEEE Electron Device Lett.* **2015**, *36*, 1008–1010. [CrossRef]

- Tamura, T.; Kotani, J.; Kasai, S.; Hashizume, T. Nearly Temperature-Independent Saturation Drain Current in a Multi-Mesa-Channel AlGaN/GaN High Electron Mobility Transistor. *Appl. Phys. Express* 2008, 1, 023001. [CrossRef]

- 10. Ohi, K.; Asubar, J.T.; Nishiguchi, K.; Hashizume, T. Current Stability in Multi-Mesa-Channel AlGaN/GaN HEMTs. *IEEE Trans. Electron Devices* **2013**, *60*, 2997–3004. [CrossRef]

- Ohi, K.; Hashizume, T. Drain Current Stability and Controllability of Threshold Voltage and Subthreshold Current in a Multi-Mesa-Channel AlGaN/GaN High Electron Mobility Transistor. *Jpn. J. Appl. Phys.* 2009, 48, 081002. [CrossRef]

- Im, K.S.; Won, C.H.; Jo, Y.W.; Lee, J.H.; Bawedin, M.; Cristoloveanu, S.; Lee, J.H. High-performance GaN-based nanochannel FinFETs With/Without AlGaN/GaN heterostructure. *IEEE Trans. Electron Devices* 2013, 60, 3012–3018. [CrossRef]

- Choi, W.; Seok, O.; Ryu, H.; Cha, H.Y.; Seo, K.S. High-voltage and low-leakage-current gate recessed normally-Off GaN MIS-HEMTs with dual gate insulator employing PEALD-SiN<sub>x</sub>/RF-Sputtered-HfO<sub>2</sub>. *IEEE Electron Device Lett.* 2014, 35, 175–177. [CrossRef]

- Uemoto, Y.; Hikita, M.; Ueno, H.; Matsuo, H.; Ishida, H.; Yanagihara, M.; Ueda, T.; Tanaka, T.; Ueda, D. Gate Injection Transistor (GIT)—A Normally-Off Conductivity Modulation. *IEEE Trans. Electron Devices* 2007, 54, 3393–3399. [CrossRef]

- Ohmaki, Y.; Tanimoto, M.; Akamatsu, S.; Mukai, T. Enhancement-mode AlGaN/AlN/GaN high electron mobility transistor with low on-state resistance and high breakdown voltage. *Jpn. J. Appl. Phys.* 2006, 45, 1168–1170. [CrossRef]

- 16. Huang, X.; Liu, Z.; Li, Q.; Lee, F.C. Evaluation and application of 600 V GaN HEMT in cascode structure. *IEEE Trans. Power Electron.* **2014**, *29*, 2453–2461. [CrossRef]

- Dai, Q.; Son, D.H.; Yoon, Y.J.; Kim, J.G.; Jin, X.; Kang, I.M.; Kim, D.H.; Xu, Y.; Cristoloveanu, S.; Lee, J.H. Deep Sub-60 mV/decade Subthreshold Swing in AlGaN/GaN FinMISHFETs with M-Plane Sidewall Channel. *IEEE Trans. Electron Devices* 2019, 66, 1699–1703. [CrossRef]

- Chu, Y.; Lu, S.C.; Chowdhury, N.; Povolotskyi, M.; Klimeck, G.; Mohamed, M.; Palacios, T. Superior Performance of 5-nm Gate Length GaN Nanowire nFET for Digital Logic Applications. *IEEE Electron Device Lett.* 2019, 40, 874–877. [CrossRef]

- 19. Son, D.H.; Jo, Y.W.; Seo, J.H.; Won, C.H.; Im, K.S.; Lee, Y.S.; Jang, H.S.; Kim, D.H.; Kang, I.M.; Lee, J.H. Low voltage operation of GaN vertical nanowire MOSFET. *Solid-State Electron.* **2018**, *145*, 1–7. [CrossRef]

- Xu, Y.; Cristoloveanu, S.; Bawedin, M.; Im, K.S.; Lee, J.H. Performance Improvement and Sub-60 mV/Decade Swing in AlGaN/GaN FinFETs by Simultaneous Activation of 2DEG and Sidewall MOS Channels. *IEEE Trans. Electron Devices* 2018, 65, 915–920. [CrossRef]

- Hao, R.; Fu, K.; Yu, G.; Li, W.; Yuan, J.; Song, L.; Zhang, Z.; Sun, S.; Li, X.; Cai, Y.; et al. Normally-off p-GaN/AlGaN/GaN high electron mobility transistors using hydrogen plasma treatment. *Appl. Phys. Lett.* 2016, 109, 152106. [CrossRef]

- 22. Song, B.; Zhu, M.; Hu, Z.; Qi, M.; Nomoto, K.; Yan, X.; Cao, Y.; Jena, D.; Xing, H.G. Ultralow-Leakage AlGaN/GaN High Electron Mobility Transistors on Si With Non-Alloyed Regrown Ohmic Contacts. *IEEE Electron Device Lett.* **2016**, *37*, 16–19. [CrossRef]

- 23. Ahn, H.K.; Kim, H.C.; Kang, D.M.; Kim, S.L.; Lee, J.M.; Lee, S.H.; Min, B.G.; Yoon, H.S.; Kim, D.Y.; Lim, J.W.; et al. Effect of Fluoride-based Plasma Treatment on the Performance of AlGaN/GaN MISHFET. *ETRI J.* **2016**, *38*, 675–684.

- 24. Zhang, K.; Kong, Y.; Zhu, G.; Zhou, J.; Yu, X.; Kong, C.; Li, Z.; Chen, T. High-Linearity AlGaN/GaN FinFETs for Microwave Power Applications. *IEEE Electron Device Lett.* **2017**, *38*, 615–618. [CrossRef]

- 25. Matocha, K.; Tilak, V.; Dunne, G. Comparison of metal-oxide-semiconductor capacitors on c- and m-plane gallium nitride. *Appl. Phys. Lett.* **2007**, *90*, 123511. [CrossRef]

- Son, D.H.; Jo, Y.W.; Sindhuri, V.; Im, K.S.; Seo, J.H.; Kim, Y.T.; Kang, I.M.; Cristoloveanu, S.; Bawedin, M.; Lee, J.H. Effects of sidewall MOS channel on performance of AlGaN/GaN FinFET. *Microelectron. Eng.* 2015, 147, 155–158. [CrossRef]

- 27. Jo, Y.W.; Son, D.H.; Won, C.H.; Sindhuri, V.; Kim, J.H.; Seo, J.H.; Kang, I.M.; Lee, J.H. Control of Transconductance in High Performance AlGaN/GaN FinFETs. In Proceedings of the IEEE 11th International Conference on Power Electronics and Drive Systems, Sydney, Australia, 9–12 June 2015.

- 28. Lu, B. AlGaN/GaN-Based Power Semiconductor Switches. Ph.D. Thesis, Massachusetts Institute of Technology, Cambridge, MA, USA, June 2013.

**Publisher's Note:** MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations.

© 2020 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).