# Communication Design Techniques for L-C-L T-Type Wideband CMOS Phase Shifter with Suppressed Phase Error

Seongjin Jang<sup>1</sup> and Changkun Park<sup>1,2,\*</sup>

- <sup>1</sup> Department of Electric Engineering, Soongsil University, 369, Sangdo-ro, Dongjak-gu, Seoul 06978, Republic of Korea; jsj0613@soongsil.ac.kr

- <sup>2</sup> Department of Intelligent Semiconductors, Soongsil University, 369, Sangdo-ro, Dongjak-gu, Seoul 06978, Republic of Korea

- \* Correspondence: pck77@ssu.ac.kr; Tel.: +82-828-7166

**Abstract:** In this study, we designed a K-band CMOS switch-type phase shifter. Equivalent circuits of shift and pass modes were analyzed to minimize phase errors in a wide frequency range. In particular, the impedance inside the equivalent circuit of the pass mode was analyzed to derive a frequency region in which the equivalent circuit of the pass mode becomes an L-C-L structure. Based on the fact that equivalent circuits in shift and pass modes can be regarded as L-C-L structures beyond a specific frequency, a design methodology of the wideband phase shifter was proposed through slope adjustment of the phase according to the frequency of each of the two modes. To verify the feasibility of the proposed design methodology, a 20°-bit phase shifter was designed through a 65 nm RFCMOS process. As a result of the measurement at 21.5 GHz to 40.0 GHz, the phase error was within 0.87°.

Keywords: CMOS; phase error; phase shifter; wideband

# 1. Introduction

With the introduction of 5G mobile communication, research related to beamforming systems has recently been actively conducted [1–4]. Accordingly, millimeter-wave (mm-Wave) circuits constituting the beamforming system are also developing. Recently, research has been active in securing more frequency bands with one beamforming system by securing wideband characteristics as well as improving the performance of mm-Wave circuits that make up the beamforming system [5–10].

With the development of such a beamforming system, research on a phase shifter for antenna beam control is also attracting attention [11–13]. Such a phase shifter is divided into an active type using a vector sum and a passive type using a filter consisting of a passive device and switch. Active phase shifters have the advantage of fine-tuning the phase and amplifying the signal, while only one-way signal paths are possible [14–21]. On the other hand, in the case of a passive phase shifter, there is a disadvantage that insertion loss occurs due to power loss caused by passive devices, but there is an advantage that a bidirectional signal path is possible [22–25]. The passive phase shifter consists of several bits that can control the phase, and each bit has a different amount of phase control function. The advantages and disadvantages of each phase shift structure have been summarized in previous studies [26]. These phase shifters, like other mm-Wave circuits [5,9], require wideband characteristics to be secured for the application of beamforming systems that can support multiple frequency bands [11,25].

In this study, a method of designing a unit bit of a phase shifter that can secure wideband characteristics in a passive phase shifter consisting of several bits and suppress phase error at the same time was proposed. The proposed design methodology relates to the L-C-L T-type structure, and a method of maintaining phase differences in a wide range of frequency bands through impedance analysis in pass and shift modes was proposed. The

Citation: Jang, S.; Park, C. Design Techniques for L-C-L T-Type Wideband CMOS Phase Shifter with Suppressed Phase Error. *Electronics* 2023, *12*, 4368. https://doi.org/ 10.3390/electronics12204368

Academic Editor: Reza K. Amineh

Received: 16 September 2023 Revised: 7 October 2023 Accepted: 20 October 2023 Published: 21 October 2023

**Copyright:** © 2023 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https:// creativecommons.org/licenses/by/ 4.0/). proposed design methodology was applied to the phase shifter fabricated with the 65 nm RFCMOS process, and its feasibility was confirmed through the measurement results.

### 2. Proposed Design Method of the Wideband L-C-L T-Type Unit Bit for Phase Shifters

Here, in order to explain the proposed design methodology of a wideband phase shifter with a suppressed phase error, the equivalent circuits in shift and pass mode were first analyzed. After considering the simplified equivalent circuit for each mode, a design technique for a wideband phase shifter with suppressed phase errors was presented using the derived equivalent circuits.

## 2.1. Analysis of Equivalent Circuits by Mode in T-Type Structure

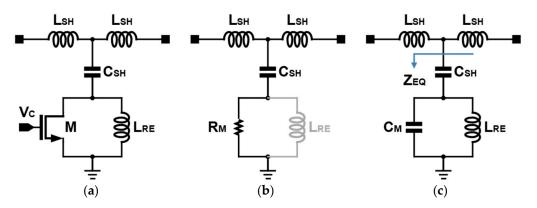

Figure 1 shows the schematic and its equivalent circuits of the unit bit of a wideband phase shifter for the application of the proposed design methodology. The unit bit of the phase shifter operates in shift and pass modes, respectively, depending on the on- and off-states of the transistor acting as a switch. Figure 1b,c show equivalent circuits in shift and pass modes of the unit bit, respectively.

**Figure 1.** L-C-L T-type structure of unit bit for phase shifter: (**a**) schematic of the used T-type structure, and equivalent circuits for the (**b**) shift and (**c**) pass modes.

In the shift mode shown in Figure 1b, the transistor M is turned on, and for convenience of analysis, it is assumed equivalent to the on-resistance,  $R_M$  of the transistor. Assuming that the impedance of  $R_M$  is small enough, the impedance by  $L_{RE}$  connected in parallel with  $R_M$  can be ignored. In this case, the equivalent circuit of the shift mode is in the form of a low-pass filter composed of a T-type  $L_{SH}$ - $C_{SH}$ - $L_{SH}$ .

On the other hand, in the case of the pass mode, M is turned off, and for the convenience of analysis, it is assumed equivalent to  $C_M$  due to parasitic capacitances of the transistor M, as shown in Figure 1c. In this case, unlike the shift mode, direct equalization with the L-C-L structure is difficult. Therefore, the  $Z_{EQ}$  of Figure 1c was developed as follows.

$$Z_{EQ} = \frac{1 - \omega^2 L_{RE} (C_{SH} + C_M)}{j \omega C_{SH} (1 - \omega^2 L_{RE} C_M)}$$

(1)

Here, for convenience of analysis, it was assumed that the parasitic resistance was small enough to be negligible. The frequencies at which  $Z_{EQ}$  becomes 0 and infinite using Equation (1) are calculated as follows.

2

$$\omega_{Z_{EQ}=0} = \frac{1}{\sqrt{L_{RE}(C_{SH}+C_M)}},$$

$$\omega_{Z_{EQ}=\infty} = \frac{1}{\sqrt{L_{RE}C_M}}$$

(2)

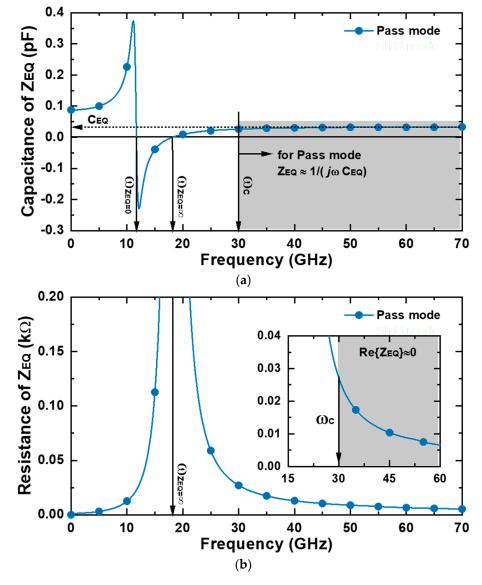

Here,  $\omega_{Z_{EQ}=0}$  and  $\omega_{Z_{EQ}=\infty}$  denote frequencies at which  $Z_{EQ}$  becomes 0 and infinity, respectively. Figure 2 shows the simulation results of the resistance and capacitance of  $Z_{EQ}$  according to frequency. Since the simulation was performed using models of actual devices,

there is a slight difference from the results of the analyzed equations, but the tendency is the same as that of the equations. The main difference between equations and simulation is that parasitic resistances were ignored in equations, but were considered in simulation.

**Figure 2.** Simulated conceptual  $Z_{EQ}$  according to operating frequency: (a) capacitance and (b) resistance.

The capacitance of  $Z_{EQ}$  shown in Figure 2a has a value of 0 at  $\omega_{Z_{EQ}=0}$  and  $\omega_{Z_{EQ}=\infty}$ . As the operating frequency gradually increases from  $\omega_{Z_{EQ}=0}$ , the capacitance of  $Z_{EQ}$  converges to a specific value, and the converging capacitance is expressed as  $C_{EQ}$ . At this time, the frequency at which the capacitance of  $Z_{EQ}$  begins to be regarded as  $C_{EQ}$  was defined as  $\omega_C$ . On the other hand, the resistance shown in Figure 2b has the highest value at  $\omega_{Z_{EQ}=\infty}$ , which is determined by the  $L_{RE}$  and  $C_M$  as shown in Equation (2). As the operating frequency increases from  $\omega_{Z_{EQ}=\infty}$ , the resistance gradually decreases, and eventually approaches 0  $\Omega$ . In addition, even near  $\omega_C$  set from Figure 2a, the resistance of  $Z_{EQ}$  can be considered 0  $\Omega$ . As a result, in the frequency region higher than  $\omega_C$ , the resistance and capacitance of  $Z_{EQ}$ are 0  $\Omega$  and  $C_{EQ}$ , respectively, so  $Z_{EQ}$  can be expressed as follows.

$$Z_{EQ} \cong \frac{1}{j\omega C_{EQ}} \quad for \quad \omega > \omega_C \tag{3}$$

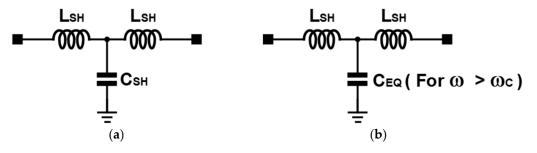

Therefore, in the case of pass-mode, a circuit consisting of  $C_{SH}$ ,  $C_M$ , and  $L_{RE}$  may be represented by  $C_{EQ}$  in the frequency region higher than  $\omega_C$ . This allows an equivalent circuit in pass mode to be T-type  $L_{SH}$ - $C_{EQ}$ - $L_{SH}$ , similar to shift mode, in frequency regions higher than  $\omega_C$ . Figure 3 shows equivalent circuits of shift and pass modes in frequency regions higher than  $\omega_C$ .

**Figure 3.** Equivalent circuits in frequency regions above  $\omega_C$ : (a) shift and (b) pass modes.

## 2.2. Proposed Design Methodology for Wideband Phase Shifter with Suppressed Phase Error

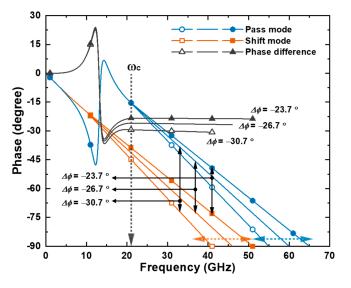

Figure 4 is a conceptual diagram for explaining the proposed design methodology of a wideband phase shifter with suppressed phase errors using the previously derived equivalent circuit for each mode. In the case of an equivalent circuit in shift mode, it has a structure of  $L_{SH}$ - $C_{SH}$ - $L_{SH}$  regardless of the operating frequency, so the phase in shift mode in Figure 4 shows linear characteristics according to the frequency. On the other hand, in the case of an equivalent circuit in pass mode, it can only be regarded as the structure of  $L_{SH}$ - $C_{EQ}$ - $L_{SH}$  in the higher operating frequency region than  $\omega_C$ , so the phase in pass mode in Figure 4 shows linear characteristics according to the frequency after  $\omega_C$ .

Figure 4. Conceptual diagram for securing wideband characteristics with suppressed phase error.

That is, in the frequency regions after  $\omega_C$ , for both shift and pass modes, the phase according to the frequency maintains a linear characteristic. Therefore, in the frequency region after  $\omega_C$ , if the slopes of the phases according to the frequency in the shift and pass modes are set to be the same, the phase difference between shift and pass modes can be maintained to be the same in the frequency region after  $\omega_C$ . When the slopes of the shift and pass modes are set the same as each other, the phase difference between the two modes also increases as the absolute value of the slope in the two modes increases.

As a result of qualitative analysis, wideband characteristics can be secured by equalizing the phase slopes according to the frequency of the two modes. In addition, the desired phase difference can be secured by adjusting the equalized slope. In order to quantify such a qualitative analysis, the phase of each mode in the frequency region after  $\omega_C$  can be calculated as follows.

$$\varphi_{Shift} = \tan^{-1} \left( -\frac{2\omega L_{SH} - \omega^3 L_{SH}^2 C_{SH}}{Z_0 (1 - \omega^2 L_{SH} C_{SH})} \right)$$

(4)

$$\varphi_{Pass} = \tan^{-1} \left( -\frac{2\omega L_{SH} - \omega^3 L_{SH}^2 C_{EQ}}{Z_0 \left(1 - \omega^2 L_{SH} C_{EQ}\right)} \right)$$

(5)

where  $\varphi_{Shift}$  and  $\varphi_{Pass}$  are phases of the shift and pass modes, respectively. In addition, we assumed that the termination impedance  $Z_0$  is 50  $\Omega$ . Here, for convenience of analysis through equations, it was assumed that parasitic resistances including  $R_M$  were small enough to be negligible. In this study, instead of directly setting the phase slope according to the frequency, the desired slope for each mode was secured by adjusting the frequency at which the phase in each mode becomes  $-90^\circ$ . In order to set the slope of the phase in this manner, the frequency at which the phase becomes  $-90^\circ$  for each mode is considered as follows.

$$\omega_{Shift-90} = \frac{1}{\sqrt{L_{SH}C_{SH}}}$$

$$\omega_{Pass-90} = \frac{1}{\sqrt{L_{SH}C_{EO}}}$$

(6)

where  $\omega_{Shift-90}$  and  $\omega_{Pass-90}$  are frequencies when the phase becomes  $-90^{\circ}$  in shift and pass modes, respectively.

As a result of quantitative analysis of the proposed design methodology, if the frequency with a phase of  $-90^{\circ}$  in each mode is adjusted through Equation (6), a wideband phase shifter with a suppressed phase error can be secured.

## 3. Design Examples of the Phase Shifter Using Proposed Design Methodology

In this study, in order to verify the effectiveness of the proposed design methodology, several unit bits of the phase shifter were first designed through simulation.

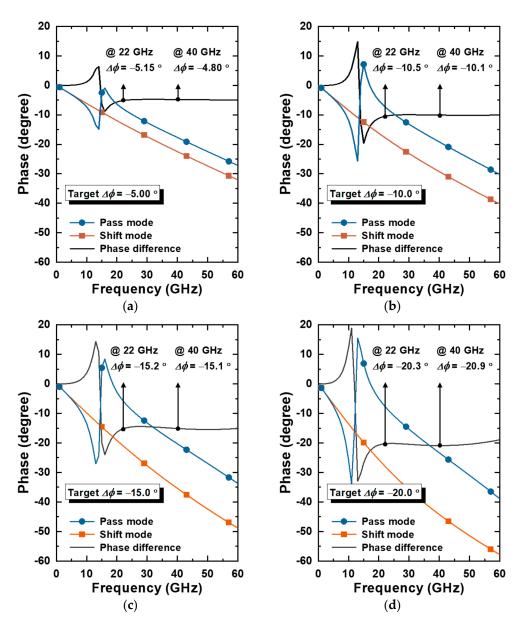

Here, if Equation (6) and Figure 4 are analyzed again, in the case of the unit bit of the L-C-L structure of a wideband phase shifter with a large phase difference, the absolute value of the phase slope according to frequency must increase. This means that  $\omega_{Shift-90}$  and  $\omega_{Pass-90}$  of Equation (6) should decrease, and  $L_{SH}C_{SH}$  and  $L_{SH}C_{EQ}$  should increase. As such, when the required inductance and capacitance increase for a large phase difference, the power loss and the size of the integrated circuit also increase accordingly. Therefore, the wideband unit bit with suppressed phase error using the T-type L-C-L structure proposed in this study is relatively more suitable for securing a small phase difference. For this reason, in this study, as shown in Figure 5, unit bits for phase shifters of 5°, 10°, 15°, and 20° were designed to verify the proposed structure through simulation.

In this study, the 65 nm RFCMOS process which provides eight metal layers was used to design the phase shifter. The schematics for the simulation results of Figure 5 are all the same as Figure 1a. The device values used for each bit to obtain the phase shift of  $5^{\circ}$ ,  $10^{\circ}$ ,  $15^{\circ}$ , and  $20^{\circ}$  shown in Figure 5 are summarized in Table 1. When designing for each bit to obtain simulation results, the effects of metal lines, inductors, and test pads were all considered through electromagnetic (EM) simulation to secure the accuracy of the simulation results. Spiral inductors are designed using the top metal layer to minimize loss due to the Silicon substrate. In addition, the gate voltages of the transistor were 1 V and 0 V, respectively, for the on and off states of the transistor. The simulation results in Figure 5 were conducted at a temperature of 25 °C in a typical corner.

**Figure 5.** Simulation results of design examples of the wideband phase shifter: (**a**)  $5^{\circ}$ , (**b**)  $10^{\circ}$ , (**c**)  $15^{\circ}$ , and (**d**)  $20^{\circ}$ .

| Table 1. Size of the used | l transistors, inductors | , and capacitors. |

|---------------------------|--------------------------|-------------------|

|---------------------------|--------------------------|-------------------|

| Bits                | $5^{\circ}$ | <b>10</b> ° | $15^{\circ}$ | <b>20</b> ° |

|---------------------|-------------|-------------|--------------|-------------|

| M (μm) <sup>1</sup> | 4.8         | 6.8         | 10.5         | 12.0        |

| $C_M$ (fF)          | 5.0         | 7.4         | 10.5         | 12.4        |

| $C_{SH}$ (fF)       | 29.1        | 47.6        | 80.5         | 106.2       |

| $L_{SH}$ (pH)       | 220         | 220         | 220          | 220         |

| $L_{RE}$ (nH)       | 1.73        | 1.44        | 1.44         | 1.13        |

<sup>1</sup> Total gate width.

Among the simulation results of the four designed phase shifters, the phase shifter of 20° was actually fabricated, measured, and analyzed. Accordingly, the phase shifter of 20° was investigated in more detail. As shown in Figure 5d, the simulation results of the phase difference of  $-20.9^{\circ}$  were obtained at the 25 °C typical corner with the operating frequency of 40 GHz. In addition, simulation results at -40 °C, 25 °C, and 80 °C were examined in fast, typical, and slow corners to confirm the impact of process and temperature variations.

For the 20° phase shifter with the operating frequency of 40 GHz, simulation results of the phase difference of  $-19.2^{\circ}$  and  $-22.3^{\circ}$  were obtained in the  $-40 \,^{\circ}$ C fast corner and 80  $^{\circ}$ C slow corner, respectively. It was confirmed as a simulation result that there was a deviation of approximately 3.1° by process and temperature variations with the operating frequency of 40 GHz.

As described above, in order to ensure wideband characteristics with suppressed phase errors, the slopes of the phase according to the frequency of shift and pass modes for each bit were designed to be the same. For all  $5^{\circ}$ -,  $10^{\circ}$ -,  $15^{\circ}$ -, and  $20^{\circ}$ -bits, the phase error from the operating frequency of 22 GHz to 40 GHz was within  $0.6^{\circ}$  under 25 °C typical corner conditions. If the operating frequency was expanded from 22 GHz to 60 GHz, the phase error was less than  $0.97^{\circ}$ . Such a frequency range includes all of the frequency ranges for 5G applications in the mm-Wave band. As a result, from the simulation results shown in Figure 5, it can be seen that the proposed design methodology is effective in securing wideband characteristics and suppressing phase errors in the phase shifter.

#### 4. Measurement Results of the Designed Wideband Phase Shifter

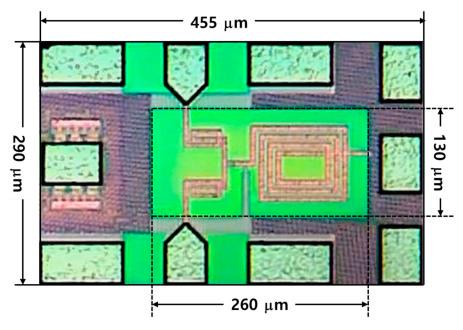

In order to verify the effectiveness of the proposed design methodology through measurement, a phase shifter of the unit bit of the T-type L-C-L structure was designed using the 65-nm RFCMOS process. The phase shift target of the designed unit bit was set to 20°. For shift- and pass-modes, the gate voltages of the transistor were 1 V and 0 V, respectively. The measurement was carried out at room temperature. Figure 6 shows a chip photograph of the designed 20°-bit phase shifter. The chip and core sizes are  $0.290 \times 0.455 \text{ mm}^2$  and  $0.130 \times 0.260 \text{ mm}^2$ . The designed phase shifter of the unit bit is actually integrated and used in the transceiver for the beamforming system. Therefore, although test pads were implemented in this study to verify the feasibility of the phase shifter itself, these test pads are removed when applied to the actual transceiver. On-wafer probes were used to measure RF input and output signals, and gate voltage was applied through a bonding wire.

Figure 6. Chip photograph of the designed unit bit phase shifter.

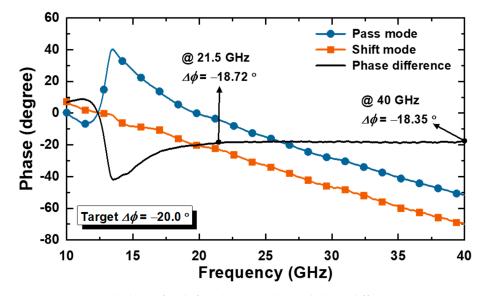

Figure 5d shows the simulated phase characteristics according to the frequency of the designed unit bit phase shifter, and Figure 7 shows the measured phase characteristics. Due to the limitation of the measurement environment, the operating frequency of the designed unit bit phase shifter was measured up to 40 GHz. The target phase was 20°, but the measured phase was slightly reduced. One of the causes of the difference between

measurement and simulation results may be the accuracy of EM simulation. In addition, as described in the previous section, process–voltage–temperature (PVT) variation can also be one of the important causes of the difference.

Figure 7. Measured phases for shift and pass modes and phase difference.

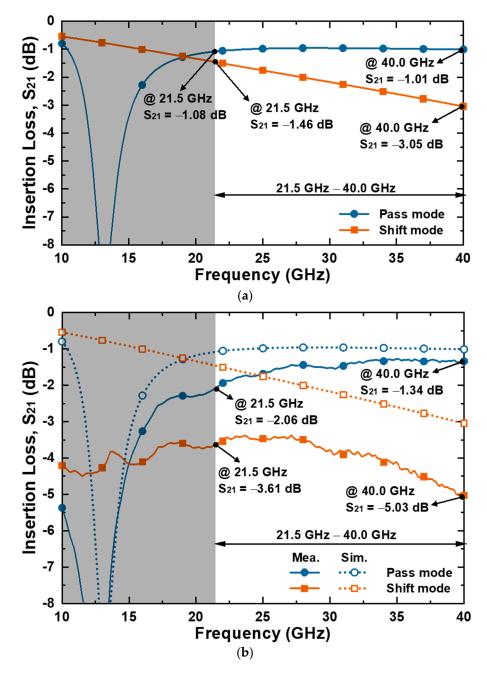

The measured phase differences of the shift and pass modes were 18.72° and 18.35° at 21.5 GHz and 40.0 GHz, respectively. In the operating frequency range of 21.5 GHz to 40.0 GHz, the measured phase difference was in the range of 17.85° to 18.72°. Therefore, based on the target phase difference of 20°, the phase error was less than 2.15°. However, considering the wideband characteristics of the proposed designed technique, the deviation of the phase difference in the operating frequency range from 21.5 GHz to 40.0 GHz was less than  $\pm 0.5^{\circ}$ . Figure 8 shows the measured and simulated insertion losses of the designed unit bit phase shifter.

In Table 2, the performance of CMOS-based wideband phase shifters was compared. While phase shifters in most previous studies consist of several bits, the phase shift in this study consists of a unit bit. Therefore, accurate comparative evaluation is somewhat difficult. However, it can be seen that the phase shifter of this study generally has a low phase error in a wide frequency range.

| Ref.      | Tech.<br>(nm) | Type<br>/Bits          | Freq.<br>(GHz) | BW<br>(%) | IL <sup>1</sup><br>(dB) | RMS Phase<br>Error (°) | P <sub>DC</sub><br>(mW) | Core Size<br>(mm <sup>2</sup> ) |

|-----------|---------------|------------------------|----------------|-----------|-------------------------|------------------------|-------------------------|---------------------------------|

| [27]      | 28            | VSPS/2.8° <sup>2</sup> | 22–44          | 66.7      | <5.81                   | <2.6                   | 25                      | 0.19                            |

| [28]      | 180           | VSPS/22.5° 2           | 27-33          | 20.0      | <10.0                   | <4.0                   | 6.6                     | 0.44                            |

| [29]      | 65            | RTPS/>360° 3           | 27.8-31.2      | 11.5      | <9.0                    | -                      | 0                       | 0.08                            |

| [30]      | 65            | RTPS/>180° 3           | 25-43          | 53.0      | <9.1                    | -                      | 0                       | 0.15                            |

| [31]      | 65            | STPS/5-bits            | 27-42          | 43.5      | <14.5                   | <3.8 4                 | 0                       | 0.40                            |

| [32]      | 28            | STPS/4-bits            | 29-37          | 24.2      | <15.3                   | <8.8                   | 0                       | 0.07                            |

| This work | 65            | STPS/1-bits            | 21.5-40.0      | 63        | <5.0                    | <0.5                   | 0                       | 0.03                            |

Table 2. Performance comparison of CMOS phase shifters.

<sup>1</sup> Insertion loss, <sup>2</sup> resolution, <sup>3</sup> phase-shift range, <sup>4</sup> controlled by bi-phase modulator.

Figure 8. Insertion loss: (a) simulation and (b) measurement results.

#### 5. Conclusions

In this study, we propose a design methodology for a wideband phase shifter with suppressed phase errors. To this end, the equivalent circuits in shift and pass modes of the phase shifter were analyzed. Through internal impedance analysis of equivalent circuits, it was shown using mathematical and simulation results that both modes can be represented by equivalent circuits of the L-C-L structure beyond a specific frequency. In shift and pass modes represented by equivalent circuits of L-C-L structure, it was confirmed that phase errors can be minimized in a wide range of frequency bands when the slope of the phase according to frequency is adjusted. Adjustment of the slope can be achieved by adjusting the frequency of  $-90^{\circ}$  in each mode, which can be achieved by adjusting the inductance and capacitance in the equivalent circuit for each mode. The proposed design methodology was applied to a  $20^{\circ}$ -bit phase shifter designed with a 65 nm RFCMOS process. As a result of the measurement, at 21.5 GHz to 40.0 GHz, the phase error was within  $0.87^{\circ}$ .

**Author Contributions:** Conceptualization, S.J. and C.P.; methodology, S.J. and C.P.; investigation, S.J.; supervision, C.P.; writing—original draft, S.J.; review and editing C.P. All authors have read and agreed to the published version of the manuscript.

**Funding:** This work was supported in part by the National Research Foundation of Korea (NRF) through the Korean Government (MSIT) under Grant NRF-2021R1A2C1013666 and in part by the National Research Foundation of Korea (NRF) through the Korean Government (MSIT) under Grant NRF-2021R1A4A1032580.

Data Availability Statement: All the material conducted in the study is mentioned in the article.

**Conflicts of Interest:** The authors declare no conflict of interest.

## References

- 1. Park, J.; Lee, S.; Chun, J.; Jeon, L.; Hong, S. A 28-GHz Four-Channel Beamforming Front-End IC with Dual-Vector Variable Gain Phase Shifters for 64-Element Phased Array Antenna Module. *IEEE J. Solid State Circuits* **2023**, *58*, 1142–1159. [CrossRef]

- 2. Mondal, S.; Carley, L.R.; Paramesh, J. Dual-Band, Two-Layer Millimeter-Wave Transceiver for Hybrid MIMO Systems. *IEEE J. Solid State Circuits* 2022, *57*, 339–355. [CrossRef]

- Al-Yasir, Y.I.A.; Abdulkhaleq, A.M.; Parchin, N.O.; Elfergani, I.T.; Rodriguez, J.; Noras, J.M.; Abd-Alhameed, R.A.; Rayit, A.; Qahwaji, R. Green and Highly Efficient MIMO Transceiver System for 5G Heterogenous Networks. *IEEE Trans. Green Commun. Netw.* 2022, 6, 500–511. [CrossRef]

- 4. Khan, B.; Tervo, N.; Jokinen, M.; Pärssinen, A.; Juntti, M. Statistical Digital Predistortion of 5G Millimeter-Wave RF Beamforming Transmitter under Random Amplitude Variations. *IEEE Trans. Microw. Theory Tech.* **2022**, *70*, 4284–4296. [CrossRef]

- Chang, Y.-T.; Lin, K.-Y.; Wu, T.-L. Wideband Reconfigurable Power Divider/Combiner in 40-nm CMOS for 5G mmW Beamforming System. *IEEE Trans. Microw. Theory Tech.* 2022, 70, 1410–1422. [CrossRef]

- Lee, S.; Hong, S. Frequency-Reconfigurable Dual-Band Low-Noise Amplifier with Interstage Gm-Boosting for Millimeter-Wave 5G Communication. *IEEE Microw. Wirel. Technol. Lett.* 2023, 33, 463–466. [CrossRef]

- Lee, S.; Park, J.; Hong, S. Millimeter-Wave Multi-Band Reconfigurable Differential Power Divider for 5G Communication. *IEEE Trans. Microw. Theory Tech.* 2022, 70, 886–894. [CrossRef]

- Capelli-Mouvand, T.; Deltimple, N.; Cathelin, P.; Ghiotto, A. Third-Order Intermodulations Phase Shifting in Power Amplifiers for Spatial Filtering in Multi-Beam 5G mmW Phased Array. *IEEE Trans. Circuits Syst. II Express Briefs* 2023, 70, 3363–3367. [CrossRef]

- 9. Wang, Z.; Wang, X.; Liu, Y. A Wideband Power Amplifier in 65 nm CMOS Covering 25.8 GHz–36.9 GHz by Staggering Tuned MCRs. *Electronics* 2023, *12*, 3566. [CrossRef]

- Chiou, H.-K.; Lin, H.-C.; Chang, D.-C. High-Efficiency and Cost-Effective 10 W Broadband Continuous Class-J Mode Quasi-MMIC Power Amplifier Design Utilizing 0.25 μm GaN/SiC and GaAs IPD Technology for 5G NR n77 and n78 Bands. *Electronics* 2023, 12, 3494. [CrossRef]

- 11. Ghaedi Bardeh, M.; Fu, J.; Naseh, N.; Paramesh, J.; Entesari, K. A Wideband Low RMS Phase/Gain Error mm-Wave Phase Shifter in 22-nm CMOS FDSOI. *IEEE Microw. Wirel. Technol. Lett.* **2023**, *33*, 739–742. [CrossRef]

- 12. Liao, Y.; Tang, M.; Pang, J.; Shirane, A.; Okada, K. A 19–34-GHz Bridged-T Phase Shifter with High-Pass Phase Compensation Achieving 3.9° RMS Phase Error for 5G NR. *IEEE Solid State Circuits Lett.* **2023**, *6*, 233–236. [CrossRef]

- 13. Singhal, N.; Hasan, S.M.R. A 25–30-GHz RMS Error-Minimized 360° Continuous Analog Phase Shifter Using Closed-Loop Self-Tuning I/Q Generator. *IEEE Trans. Very Large Scale Integr. (VLSI) Syst.* 2022, 30, 720–731. [CrossRef]

- 14. Park, G.-H.; Byeon, C.W.; Park, C.S. 60 GHz 7-Bit Passive Vector-Sum Phase Shifter with an X-Type Attenuator. *IEEE Trans. Circuits Syst. II Express Briefs* 2023, 70, 2355–2359. [CrossRef]

- 15. Akbar, F.; Mortazawi, A. An Integrated Compact Phase Shifter with a Single Analog Control. *IEEE Microw. Wirel. Technol. Lett.* **2022**, *32*, 410–413. [CrossRef]

- Zhu, X.; Yang, T.; Chi, P.-L.; Xu, R. Novel Passive Vector-Sum Reconfigurable Filtering Phase Shifter with Continuous Phase-Control and Tunable Center Frequency. *IEEE Trans. Microw. Theory Tech.* 2022, 70, 1188–1197. [CrossRef]

- 17. Qiu, F.; Zhu, H.; Che, W.; Xue, Q. A K-Band Full 360° Phase Shifter Using Novel Non-Orthogonal Vector Summing Method. *IEEE J. Solid State Circuits* 2023, *58*, 1299–1309. [CrossRef]

- 18. Dou, B.; Duan, Z.; Li, Y.; Ding, N.; Xiao, D.; Liao, B.; Yao, X. A 4–10 GHz Programmable CMOS Vector-Sum Phase Shifter for a Two-Channel Transmitter. *IEEE Trans. Circuits Syst. II Express Briefs* **2022**, *69*, 3699–3703. [CrossRef]

- 19. Qiu, F.; Zhu, H.; Che, W.; Xue, Q. A Simplified Vector-Sum Phase Shifter Topology with Low Noise Figure and High Voltage Gain. *IEEE Trans. Very Large Scale Integr. (VLSI) Syst.* **2022**, *30*, 966–974. [CrossRef]

- 20. Sung, E.-T.; So, C.; Hong, S. A 60-GHz Variable-Gain Phase Shifter with Particular-Sized Digital-RF Cells. *IEEE Trans. Microw. Theory Tech.* **2022**, *70*, 1302–1313. [CrossRef]

- So, C.; Sung, E.-T.; Hong, S. A 60-GHz Variable-Gain Phase Shifter with an Active RL Poly-Phase Filter. *IEEE Trans. Microw. Theory Tech.* 2022, 71, 593–601. [CrossRef]

- 22. Li, X.; Liu, B.; Fu, H.; Ma, K. A 30–36 GHz Passive Hybrid Phase Shifter with a Transformer-Based High-Resolution Reflect-Type Phase Shifting Technique. *IEEE Trans. Circuits Syst. II Express Briefs* **2021**, *68*, 2419–2423. [CrossRef]

- Meng, F.; Ma, K.; Yeo, K.S.; Xu, S. A 57-to-64-GHz 0.094-mm<sup>2</sup> 5-bit Passive Phase Shifter in 65-nm CMOS. IEEE Trans. Very Large Scale Integr. (VLSI) Syst. 2016, 24, 1917–1925. [CrossRef]

- 24. Jang, S.; Kim, C.-Y.; Park, C. Design Technique of K-Band CMOS Phase Shifter with L-C-L T-Type Low Pass Structure. *Electronics* 2023, 12, 3678. [CrossRef]

- 25. Li, X.; Fu, H.; Ma, K.; Hu, J. A 2.4–4-GHz Wideband 7-Bit Phase Shifter with Low RMS Phase/Amplitude Error in 0.5-μm GaAs Technology. *IEEE Trans. Microw. Theory Tech.* **2022**, *70*, 1292–1301. [CrossRef]

- Guan, P.; Jia, H.; Deng, W.; Dong, S.; Huang, X.; Wang, Z.; Chi, B. A 33.5–37.5-GHz Four-Element Phased-Array Transceiver Front-End with Hybrid Architecture Phase Shifters and Gain Controllers. *IEEE Trans. Microw. Theory Tech.* 2023, 71, 4129–4143. [CrossRef]

- 27. Zhou, J.; Qian, H.J.; Luo, X. High-Resolution Wideband Vector-Sum Digital Phase Shifter with On-Chip Phase Linearity Enhancement Technology. *IEEE Trans. Circuits Syst. I Regul. Pap.* **2021**, *68*, 2457–2469. [CrossRef]

- Chang, Y.-T.; Ou, Z.-W.; Alsuraisry, H.; Sayed, A.; Lu, H.-C. A 28-GHz Low-Power Vector-Sum Phase Shifter Using Biphase Modulator and Current Reused Technique. *IEEE Microw. Wirel. Compon. Lett.* 2018, 28, 1014–1016. [CrossRef]

- Gu, P.; Zhao, D. Ka-band CMOS 360° Reflective-Type Phase Shifter with ±0.2 dB Insertion Loss Variation Using Triple-Resonating Load and Dual-Voltage Control Techniques. In Proceedings of the IEEE Radio Frequency Integrated Circuits Symposium (RFIC), Philadelphia, PA, USA, 10–12 June 2018; pp. 140–143.

- 30. Lim, J.-T.; Choi, S.; Lee, E.-G.; Choi, H.-W.; Song, J.-H.; Kim, S.-H.; Kim, C.-Y. 25–40 GHz 180° Reflective-Type Phase Shifter using 65-nm CMOS Technology. In Proceedings of the European Microwave Conference (EuMC), Paris, France, 1–3 October 2019.

- Tsai, J.-H.; Tung, Y.-L.; Lin, Y.-H. A 27–42-GHz Low Phase Error 5-Bit Passive Phase Shifter in 65-nm CMOS Technology. IEEE Microw. Wirel. Compon. Lett. 2020, 30, 900–903. [CrossRef]

- Jung, M.; Min, B.-W. A Compact Ka-Band 4-bit Phase Shifter with Low Group Delay Deviation. *IEEE Microw. Wirel. Compon. Lett.* 2020, 30, 414–416. [CrossRef]

**Disclaimer/Publisher's Note:** The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content.