Article

# A New Gate Driver for Suppressing Crosstalk of SiC MOSFET

Mei Liang \*, Jiwen Chen \*, Jinchao Bai, Pengyu Jia and Yuzhe Jiao

School of Electrical and Control Engineering, North China University of Technology, Beijing 100144, China \* Correspondence: liangmei@ncut.edu.cn (M.L.); chenjiwen@ncut.edu.cn (J.C.)

Abstract: High switching-speed Silicon Carbide Metal-Oxide-Semiconductor Field-Effect Transistor (SiC MOSFET) has serious crosstalk issues. During the turn-ON transition and turn-OFF transition of the active switch in a phase-leg configuration, the voltage drops across the common-source inductor and the displacement current of the gate-drain capacitor of the OFF-state switch induce a spurious pulse on its gate-source voltage. This paper proposes a new gate driver using two Bipolar Junction Transistors (BJTs) and one diode to connect the gate terminal of SiC MOSFET and the negative driver voltage, which provides a low impedance path to bypass the displacement current of the gate-drain capacitor when crosstalk issues occur. The simulation results prove the proposed driver is valid on suppressing the crosstalk issue. The comparisons between the prior drivers and the proposed driver show the superiority of the proposed driver. Finally, the proposed gate driver is successfully implemented and experimentally verified on a 1.1 kW synchronous buck prototype.

Keywords: crosstalk; SiC MOSFET; driver

#### 1. Introduction

The next generation power device, SiC MOSFET, is a promising candidate for many applications, because the SiC material properties are superior to a conventional Silicon (Si) material [1–6]. SiC MOSFET has faster switching speeds (shorter switching time), higher switching frequencies, higher voltage blocking capabilities and higher temperature performance. The converter based SiC MOSFET in trains and electric vehicles [7,8], battery chargers for electric vehicles [9], renewable energy [10,11] and industrial automation [12] have excellent performance, such as higher efficiency, higher power density and lighter weight, etc. However, due to the high speed of SiC MOSFET, parasitic parameters cannot be overlooked, although they are not considered in Si device applications [13–15].

Crosstalk issues matter in the reliability of electronic equipment. Independent of SiC or Si device applications, crosstalk issues exist in a phase-leg configuration. However, the high switching speed of SiC MOSFET makes crosstalk issues more acute. Crosstalk issues are the spurious pulses induced on the gate-source voltage of the OFF-state switch during the active switch turn-ON or turn-OFF transition [16–21]. If the positive spurious pulse exceeds threshold voltage  $V_{th}$  of the OFF-state switch, this switch can be partially turned ON; if the negative spurious pulse exceeds the maximum allowable negative driver voltage  $V_{GS\_MAX(-)}$  of the OFF-state switch, gate overstresses of this switch can occur, which damage the device and may impose serious reliability problems [22,23]. Thus, it is necessary to investigate in more detail the mechanisms of crosstalk issues of SiC MOSFET.

For solutions suppressing the crosstalk issue, several have been done. First, decreasing the switching speed of the active switch is an easy solution. However, the efficiency and the density may be affected. Second, setting an appropriate negative driver voltage to avoid the spurious pulse exceeding the safety value is a common solution [23]. However, the safety allowance ( $V_{th} - V_{GS\_MAX(-)}$ ) of SiC MOSFET is small, so selecting a suitable negative driver voltage is difficult. The most studied solution is to add an assistant circuit to the conventional driver, which is recommended by several SiC power device

Citation: Liang, M.; Chen, J.; Bai, J.; Jia, P.; Jiao, Y. A New Gate Driver for Suppressing Crosstalk of SiC MOSFET. *Electronics* **2022**, *11*, 3268. https://doi.org/10.3390/ electronics11203268

Academic Editor: Toshishige Yamada

Received: 20 September 2022 Accepted: 8 October 2022 Published: 11 October 2022

**Publisher's Note:** MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Copyright: © 2022 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

manufacturers [21,24,25]. In [26], the added assistant circuit can change the negative driver voltage of the OFF-state switch, which makes the spurious pulse within the safety allowance. However, it may occur that the spurious pulse is so high that shifting the negative driver voltage cannot guarantee that the spurious pulse is within the safety allowance. In [25,27], shifting negative driver voltage and clamping the gate-source voltage to negative driver voltage are realized together, but the implementation of the assistant circuit is complex and needs MOSFETs and control circuits. The authors in [28] propose a capacitor paralleling with the gate-source terminal to bypass a proportion of displacement current of the gate-drain capacitor C<sub>GD</sub>. However, the performance of SiC MOSFET will be reduced. In [29], a bipolar junction transistor (BJT) and a capacitor are paralleling with the gate-source terminal to avoid affecting the switching speed of SiC MOSFET. However, this assistant circuit can only suppress the negative spurious pulse. In [30], the BJT is replaced by a MOSFET, but this MOSFET needs an accurate control signal and the control circuit. In [31], only two capacitors are added. One capacitor is in parallel with the turn-OFF gate resistor, another capacitor connects the terminal of the negative driver voltage and the common source inductors, and one switch which connects the turn-OFF gate resistor in the driver chip is reused to replace BJT in [29] or MOSFET in [30]. This assistant circuit is simple and has no transistors. However, the driver chip must use split output which separates the turn-ON gate resistor and the turn-OFF gate resistor [32], because the reusable switch guarantees that the added capacitor does not affect the performance of SiC MOSFET during the tun-ON transition. In [33–35], some manufacturers also use the active miller clamping in the driver chip. The operating principle is to sense the gatesource voltage of the OFF-state switch and to compare it with the clamping threshold (typically, 2 V) in the chip. Thus, the crosstalk issue is identified by the measured gatesource voltage. However, due to the parasitic gate inductor, the common source inductor and the inner gate resistor, the measured gate-source voltage is inaccurate and always smaller than the actual value. Moreover, the threshold voltage of SiC MOSFET is low and the switching speed is fast, so it is very possible that the positive spurious pulse exceeds the threshold voltage before the clamping transistor turns ON. These kinds of driver chips with the active miller clamping can only detect the positive spurious pulse; the negative spurious pulse is also needed suppression for limiting it smaller than the maximum negative driver voltage (*V*<sub>GS\_MAX(-)</sub>) of SiC MOSFET.

Therefore, this paper focuses on a suppressing solution for the crosstalk issue of SiC MOSFET. First, the crosstalk mechanisms of SiC MOSFET are analyzed in this paper. The voltage drops across the common-source inductors and the displacement current of the gate-drain capacitor of the OFF-state switch cause the crosstalk issue. Second, a new gate driver for suppressing crosstalk issue is proposed, which adds two BJTs and one diode to the gate terminal of SiC MOSFET and the negative driver voltage. This assistant circuit provides a low impedance path to bypass the displacement current of the gate-drain capacitor. The operating principle and simulation results of the proposed driver are presented in the paper. The prior drivers and the proposed driver are compared based on the simulation results. Finally, the proposed gate driver is successfully implemented and effectively verified on a 1.1 kW synchronous buck prototype.

## 2. Crosstalk Mechanisms of SiC MOSFET

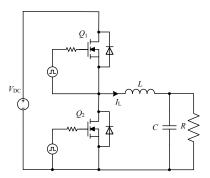

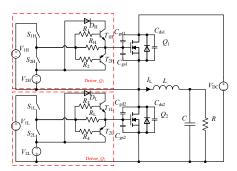

In a phase-leg configuration, such as synchronous boost, synchronous buck, half bridge and full bridge, a crosstalk issue is likely to occur on the OFF-state switch. Figure 1 shows a synchronous buck converter. In this figure,  $Q_1$  is the upper switch and  $Q_2$  is the lower switch. Crosstalk issue occurs on the gate-source voltage of  $Q_2$  during  $Q_1$  switching transitions.

Electronics 2022, 11, 3268 3 of 13

Figure 1. Synchronous buck converter.

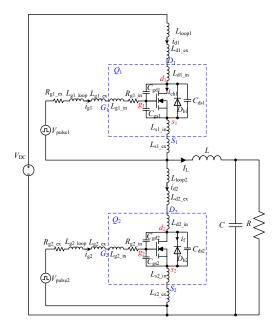

In Figure 2, the parasitic parameters existing on the device and loop are considered, which cannot be overlooked in SiC device applications due to their high-speed switching. The junction capacitors of  $Q_1$  and  $Q_2$  are the gate-source capacitor  $C_{gs1}$  and  $C_{gs2}$ , the gate-drain capacitor  $C_{gd1}$  and  $C_{gd2}$ , and the drain-source capacitor  $C_{ds1}$  and  $C_{ds2}$ . The parasitic inductors in the package of  $Q_1$  and  $Q_2$  are the gate inductor  $L_{g1\_in}$  and  $L_{g2\_in}$ , the drain inductor  $L_{d1\_in}$  and  $L_{d2\_in}$ , the source inductor  $L_{s1\_in}$  and  $L_{s2\_in}$ . The internal gate drive resistors of  $Q_1$  and  $Q_2$  are  $R_{g1\_in}$  and  $R_{g2\_in}$ .  $L_{g1\_ex}$ ,  $L_{d1\_ex}$ ,  $L_{s1\_ex}$ ,  $L_{d2\_ex}$ ,  $L_{d2\_ex}$ , and  $L_{s2\_ex}$  represent the parasitic inductors of the package leads.  $L_{g1\_loop}$ ,  $L_{g2\_loop}$ ,  $L_{loop1}$ , and  $L_{loop2}$  represent the interconnection parasitic inductors of PCB traces. In addition,  $L_{s1\_in}$ ,  $L_{s1\_ex}$ ,  $L_{s2\_in}$  and  $L_{s2\_ex}$  are the common source inductors [31].  $R_{g1\_ex}$  and  $R_{g2\_ex}$  are external gate resistor.  $v_{pulse1}$  and  $v_{pulse2}$  are gate signals, the voltages of which are from  $v_{g1}$  to  $v_{g2}$ , and  $v_{g2}$  is negative. The input voltage source  $v_{g2}$  and the current  $v_{g3}$  shows the switching waveforms of  $v_{g3}$  and  $v_{g2}$  during  $v_{g3}$  turn-ON and turn-OFF transition.

Figure 2. Synchronous buck considering the parasitic parameters.

Electronics **2022**, 11, 3268 4 of 13

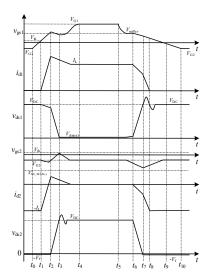

**Figure 3.** Theoretical waveforms during  $Q_1$  turn-ON and turn-OFF transition.

# 2.1. Crosstalk Issue during Q1 Turn-ON Transition

$v_{\rm gs1}$  is the gate-source voltage of  $Q_1$ ,  $i_{\rm d1}$  is the drain current of  $Q_1$ .  $v_{\rm ds1}$  is the drain-source voltage of  $Q_1$ .  $v_{\rm gs2}$  is the gate-source voltage of  $Q_2$ ,  $i_{\rm d2}$  is the drain current of  $Q_2$ .  $v_{\rm ds2}$  is the drain-source voltage of  $Q_2$ . Before  $Q_1$  is turned ON, the current  $I_L$  flows through  $D_2$ ,  $Q_1$  and  $Q_2$  are OFF-state.

Stage 1 [ $t_0 \sim t_1$ ], at  $t_0$ ,  $Q_1$  is turned ON. Since the gate-source voltage  $v_{gs1}$  does not reach the threshold voltage  $V_{th}$ , the channel of  $Q_1$  is OFF and the crosstalk issue does not occur in this stage.

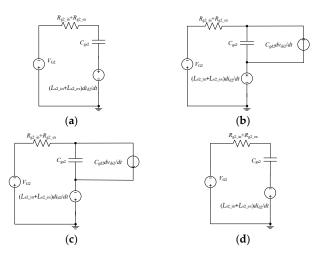

Stage 2 [ $t_1 \sim t_2$ ], when the gate-source voltage  $v_{\rm gs1}$  reaches the threshold voltage  $V_{\rm th}$ , the current  $I_{\rm L}$  commutates from  $D_2$  to  $Q_1$ . This stage ends when  $D_2$  begins to block the voltage. The equivalent circuit of this stage is shown in Figure 4a. Figure 4a neglects the gate inductors due to their less obvious effects on crosstalk issue. The spurious pulse on the gate-source voltage of  $Q_2$  during this stage is given by Equation (1). The falling drain current  $i_{\rm d2}$  brings the voltage drops across the common source inductors  $L_{\rm s2\_in}$  and  $L_{\rm s2\_ex}$ , which results in charging the gate-source capacitor  $C_{\rm gs2}$ .

$$\Delta v_{gs2} = V_1 \left( 1 - e^{\frac{-t}{\tau}} \right) \tag{1}$$

where  $\tau = (R_{g2\_in} + R_{g2\_ex})C_{gs2}$ , and  $V_1 = -(L_{s2\_in} + L_{s2\_ex})di_{d2}/dt$ .  $V_1$  decides the change trend of the gate-source voltage  $v_{gs2}$  during this stage.

At Stage 3 [ $t_2$ – $t_3$ ], when  $D_2$  is able to block the voltage, the drain-source voltage  $v_{\rm ds2}$  of  $Q_2$  increases. The drain current  $i_{\rm d2}$  charges the gate-drain capacitor  $C_{\rm gd2}$  and the drain-source capacitor  $C_{\rm ds2}$ . This stage ends when the drain-source voltage  $v_{\rm ds1}$  decreases to the ON-state voltage of SiC MOSFET. The equivalent circuit of this stage is shown in Figure 4b. The spurious pulse on the gate-source voltage of  $Q_2$  during this stage is given by Equation (2). The drain current  $i_{\rm d2}$  still induces the voltage drops across the common source inductors  $L_{\rm s2\_in}$  and  $L_{\rm s2\_ex}$ . In addition, the displacement current of the gate-drain capacitor  $C_{\rm gd2}$  also passes through the gate-source capacitor  $C_{\rm gs2}$ .

$$\Delta v_{gs2} = V_2 \left( 1 - e^{\frac{-t}{\tau}} \right) \tag{2}$$

where  $V_2 = (R_{g2\_in} + R_{g2\_ex})C_{gd2}dv_{ds2}/dt - (L_{s2\_in} + L_{s2\_ex})di_{d2}/dt$ .  $V_2$  decides the change trend of the gate-source voltage  $v_{gs2}$  during this stage.

Stage 4 [ $t_3 \sim t_4$ ], during this stage, the drain-source voltage  $v_{ds2}$  and the drain current  $i_{d2}$  of  $Q_2$  may have the ringing. Therefore, the ringing also exists on the gate voltage  $v_{gs2}$ .

After  $t_4$ , the circuit is steady after the  $Q_1$  turn-ON transition.

Electronics 2022, 11, 3268 5 of 13

**Figure 4.** Equivalent circuit during  $Q_1$  turn-ON and turn-OFF transition. (a) Stage 2, (b) Stage 3, (c) Stage 7 and (d) Stage 8.

# 2.2. Crosstalk Issue during Q1 Turn-OFF Transition

Before  $Q_1$  is turned OFF, the current  $I_L$  flows through  $Q_1$ , and  $Q_2$  are OFF-state.

Stage 6 [ $t_5 \sim t_6$ ], at  $t_5$ ,  $Q_1$  is turned OFF. Since the gate-source voltage  $v_{gs1}$  does not reach the miller voltage  $V_{mil}$ ,  $Q_1$  is still in the ON-state and the crosstalk issue does not occur in this stage.

Stage 7 [ $t_6$ - $t_7$ ], when the gate-source voltage  $v_{\rm gs1}$  reaches the miller voltage  $V_{\rm mil}$ , the drain-source voltage  $v_{\rm ds1}$  of  $Q_1$  increases and the drain-source voltage  $v_{\rm ds2}$  of  $Q_2$  declines. When the drain-source voltage  $v_{\rm ds2}$  reaches to the forward voltage of  $D_2$ , this stage ends. The equivalent circuit of this stage is shown in Figure 4c. The spurious pulse on the gate-source voltage of  $Q_2$  during this stage can be also expressed as Equation (2). The drain current  $i_{\rm d2}$  discharges the gate-drain capacitor  $C_{\rm gd2}$  and the drain-source capacitor  $C_{\rm ds2}$ . Therefore, the voltage drops across the common source inductors  $L_{\rm s2\_in}$  and  $L_{\rm s2\_ex}$  and the displacement current of the gate-drain capacitor  $C_{\rm gd2}$  induce the crosstalk issue of  $Q_2$  in this stage.

At Stage 8 [ $t_7$ ~ $t_8$ ], when  $D_2$  is on state, the current  $I_L$  commutates from  $Q_1$  to  $D_2$ . This stage ends when the channel of  $Q_1$  is OFF. The equivalent circuit of this stage is shown in Figure 4d. The spurious pulse on the gate-source voltage of  $Q_2$  during this stage can be also expressed as Equation (1). The falling drain current  $i_{d2}$  brings the voltage drops across the common source inductors  $L_{s2\_in}$  and  $L_{s2\_ex}$ , which makes the gate voltage change  $v_{gs2}$  of  $Q_2$  fluctuate.

At Stage 9 [ $t_8 \sim t_9$ ], the drain-source voltage  $v_{ds2}$  and the drain current  $i_{d2}$  of  $Q_2$  may have ringing. Therefore, the ringing also exists on the gate voltage  $v_{gs2}$ .

After *t*9, the circuit is steady after *Q*1 turn-OFF transition.

Based on the previous discussions, the voltage drops across the common-source inductors and the displacement current of the gate-drain capacitor cause the crosstalk issue of SiC MOSFET.

## 3. A New Gate Driver for Suppressing Crosstalk Issue of SiC MOSFET

The common source inductors  $L_{s2\_in}$  and  $L_{s2\_ex}$  are the parasitic inductors of the bonding wires and leads of the package. The common source inductor  $L_{s2\_in}$  is immutable. Nevertheless, the common source inductor  $L_{s2\_ex}$  can be decoupled from the driver loop by adding a capacitor to the negative driver voltage and node S1 (or node S2) in Figure 2, like in [31]. In addition, the common source inductor  $L_{s2\_ex}$  can also be reduced by shortening the length of package leads connected into circuit. In this paper, the solution of making the driver board connect to the nodes G1 and S1 (or nodes G2 and S2) in Figure 2 is adopted, like in [36]. This solution makes the leads connected into driver loop much less.

The effects of common source inductors on the crosstalk issue are reduced. A new gate driver is proposed to bypass the injected current into the gate-source capacitor from the gate-drain capacitor. The proposed driver is shown as Driver\_ $Q_1$  or Driver\_ $Q_2$  in Figure 5. Driver\_ $Q_1$  is composed of the power supply  $V_{1H}$  and  $V_{2H}$ , two switches  $S_{1H}$  and  $S_{2H}$ , the gate resistor  $R_{1H}$ , two BJTs  $T_{1H}$  and  $T_{2H}$ , diode  $D_{1H}$  and resistor  $R_{1H}$  and  $R_{2H}$ . Driver\_ $R_{2H}$  is composed of the power supply  $V_{1L}$  and  $V_{2L}$ , two switches  $S_{1L}$  and  $S_{2L}$ , the gate resistor  $R_{1L}$ , two BJTs  $T_{1L}$  and  $T_{2L}$ , diode  $D_{1L}$  and resistors  $R_{3H}$  and  $R_{4H}$ .

Figure 5. Proposed driver for suppressing the crosstalk issue.

#### 3.1. Operating Principle

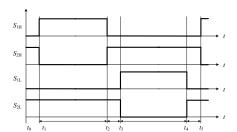

Figure 6 shows the logic signals of switches  $S_{1H}$ ,  $S_{2H}$ ,  $S_{1L}$  and  $S_{2L}$ . The proposed driver has four operating modes. Before  $t_0$ , Switches  $S_{2H}$  and  $S_{2L}$  are ON-state, switches  $S_{1H}$  and  $S_{1L}$  are OFF-state,  $T_{1H}$ ,  $T_{2H}$ ,  $T_{1L}$  and  $T_{2L}$  are OFF-state.  $Q_1$  and  $Q_2$  are OFF-state, and the current  $I_L$  flows through  $D_2$ .

**Figure 6.** Logic signals of *S*<sub>1</sub>H, *S*<sub>2</sub>H, *S*<sub>1</sub>L and *S*<sub>2</sub>L in the proposed driver.

Mode 1 [ $t_1 \sim t_2$ ]:  $S_{1H}$  is turned ON,  $S_{2H}$  is turned OFF.  $S_{1L}$  is still OFF-state and  $S_{2L}$  is still ON-state.  $Q_1$  is turned ON and  $Q_2$  remains OFF-state. The current  $I_L$  commutates from  $D_2$  to  $Q_1$ . The displacement current of the gate-drain capacitor  $C_{gd2}$  of  $Q_2$  flows through the gate resistor  $R_L$  and the gate-source capacitor  $C_{gs2}$ . Then, the voltage drop on the gate resistor  $R_L$  turns ON the BJT  $T_{2L}$ , which clamps the gate-source voltage  $v_{gs2}$  as the negative driver voltage  $V_{2L}$ . When the displacement current of the gate-drain capacitor  $C_{gd2}$  is zero, the BJT  $T_{2L}$  is turned OFF. The impedance of the BJT  $T_{2L}$  is small, most of the displacement current of the gate-drain capacitor  $C_{gd2}$  is bypassed. Therefore, the effect of the displacement current of the gate-drain capacitor  $C_{gd2}$  on the crosstalk issue of  $Q_2$  is suppressed during  $Q_1$  turn-ON transition.

Mode 2 [ $t_2\sim t_3$ ]:  $S_{1H}$  is turned OFF,  $S_{2H}$  is turned ON.  $S_{1L}$  is still OFF-state and  $S_{2L}$  is still ON-state.  $Q_1$  is turned OFF and  $Q_2$  remain OFF-state. The current  $I_L$  commutates from  $Q_1$  to  $D_2$ . The displacement current of the gate-drain capacitor  $C_{gd2}$  flows through gate resistor  $R_L$  and gate-source capacitor  $C_{gs2}$ . The voltage drop on the gate resistor  $R_L$  turns ON the BJT  $T_{1L}$  and diode  $D_L$  is ON-state, which clamps the gate-source voltage  $v_{gs2}$  as the negative driver voltage  $V_{2L}$ . When the displacement current of the gate-drain capacitor  $C_{gd2}$  is zero, the BJT  $T_{1L}$  is turned OFF as same with Mode 1. Most of the displacement current of the gate-drain capacitor  $C_{gd2}$  is also bypassed by  $T_{1L}$  and  $D_L$ . Therefore, the effect of the

displacement current of the gate-drain capacitor  $C_{gd2}$  on the crosstalk issue of  $Q_2$  is also suppressed during  $Q_1$  turn-OFF transition.

Mode 3 [ $t_3$ ~ $t_4$ ]:  $S_{1L}$  is turned ON, and  $S_{2L}$  is turned OFF.  $S_{1H}$  remains OFF-state, and  $S_{2H}$  remains ON-state. During this mode,  $Q_2$  is turned ON, and  $Q_1$  remains OFF-state. The current  $I_L$  commutates from  $D_2$  to  $Q_2$ , so the drain-source voltage  $v_{ds2}$  and the drain current  $i_{d2}$  scarcely change and no crosstalk issues occur for  $Q_2$ .

Mode 4 [ $t_4 \sim t_5$ ]:  $S_{1L}$  is turned OFF, and  $S_{2L}$  is turned ON.  $S_{1H}$  remains OFF-state, and  $S_{2H}$  remains ON-state. During this mode,  $Q_2$  is turned OFF, and  $Q_1$  remains OFF-state. The discharging current of the gate-source capacitor  $C_{g^{s_2}}$  of  $Q_2$  flows through the gate resistor  $R_L$ . The voltage drop on the gate resistor  $R_L$  turns ON the BJT  $T_{2L}$ . When the discharging current of the gate-source capacitor  $C_{g^{s_2}}$  is zero,  $T_{2L}$  is turned OFF. The current  $I_L$  commutates from  $Q_2$  to  $D_2$ , so the drain-source voltage  $v_{d^{s_2}}$  and the drain current  $i_{d^2}$  also scarcely change and no crosstalk issue occurs for  $Q_2$ .

#### 3.2. Simulation Results

In order to verify the operating principle of the proposed driver, the simulation model of the proposed driver based on the synchronous buck is made in LTspice. In the simulation model, the spice model of C2M0080120D by Cree Inc. is used, the parameters of which are shown in Table 1. The parameters in the simulation model are presented in Table 2. Considering that the gate voltage oscillation should be avoided, the gate resistor needs to meet the limitation condition [37] shown in Equation (3). Calculated based on Tables 1 and 2, the gate resistor selected  $10\,\Omega$ .

$$R_{g_{in}} + R_{g_{ex}} \ge 2\sqrt{\frac{L_{g_{in}} + L_{g_{ex}} + L_{g_{loop}} + L_{s_{in}} + L_{s_{ex}}}{C_{gs}}}$$

(3)

Table 1. Parameters of C2M0080120D.

| Parameter                                            | Value        | Parameter                                 | Value   |

|------------------------------------------------------|--------------|-------------------------------------------|---------|

| Inner gate resistor ( $R_{g_in}$ )                   | $3.9 \Omega$ | Threshold voltage ( $V_{\text{th}}$ )     | 2.9 V   |

| Gate inductors ( $L_{g_{in}} + L_{g_{ex}}$ )         | 15 nH        | Gate-source capacitor ( $C_{gs}$ )        | 1122 pF |

| Common source inductors ( $L_{s_in} + L_{s_ex}$ )    | 9 nH         | Gate-drain capacitor ( $C_{gd}$ )         | 8 pF    |

| Drain inductors $(L_{d_{in}} + L_{d_{ex}})$          | 6 nH         | Drain-source capacitor (C <sub>ds</sub> ) | 92 pF   |

| Maximum negative driver voltage ( $V_{GS\_MAX(-)}$ ) | -10 V        |                                           |         |

Table 2. Parameters of the simulation model based on synchronous buck and proposed driver.

| Parameter                | Value   | Parameter                                         | Value       |

|--------------------------|---------|---------------------------------------------------|-------------|

| Input voltage            | 400 V   | Power loop inductor                               | 25 nH       |

| Output current           | 21 A    | Power loop inductor                               | 25 nH       |

| Switching frequency      | 500 kHz | Positive driver voltage ( $V_{1H}$ and $V_{1L}$ ) | 18 V        |

| Width of the gate signal | 500 ns  | Negative driver voltage ( $V_{2H}$ and $V_{2L}$ ) | -5 V        |

| Dead time                | 500 ns  | Gate resistor ( $R_H$ and $R_L$ )                 | $10 \Omega$ |

| Gate loop inductor       | 10 nH   | Base resistor of BJT( $R_1 \sim R_4$ )            | 1 Ω         |

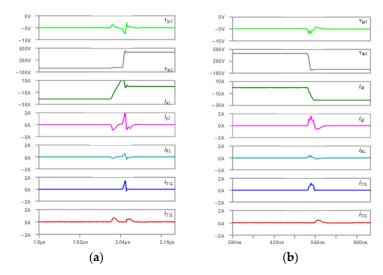

Figure 7 shows the waveforms of the simulation model, which include the gate-source voltage  $v_{\rm gs2}$ , the drain-source voltage  $v_{\rm ds2}$ , the drain current  $i_{\rm d2}$ , the gate current  $i_{\rm g2}$ , the  $R_{\rm L}$  current  $i_{\rm RL}$ , the  $T_{\rm 1L}$  current  $i_{\rm TL}$  and the  $T_{\rm 2L}$  current  $i_{\rm T2L}$ . From Figure 7a, when the current passes through the gate, resistor  $R_{\rm L}$  is positive, the voltage drop on  $R_{\rm L}$  makes  $T_{\rm 1L}$  turn ON; when the current passes through the gate, resistor  $R_{\rm L}$  is negative, the voltage drop on  $R_{\rm L}$  makes  $T_{\rm 2L}$  turn ON. Therefore, the displacement current of the gate-drain capacitor  $C_{\rm gd2}$  is shunted by the gate-source capacitor  $C_{\rm gs2}$ , the gate resistor  $R_{\rm L}$ , the BJTs  $T_{\rm 1L}$  and  $T_{\rm 2L}$ . Due to the impedance of  $T_{\rm 1L}$  and  $T_{\rm 2L}$  being lower, much of the displacement

current passes through  $T_{1L}$  and  $T_{2L}$ . From Figure 7b, it is the same with Figure 7a that  $T_{1L}$  is turned ON when the current passes through the gate, resistor  $R_L$  is positive and  $T_{2L}$  is turned ON when the current passes through the gate, resistor  $R_L$  is negative. On basis of the simulation results, it is proved that the proposed driver is valid for suppressing the crosstalk issue.

**Figure 7.** Simulation waveforms of the proposed driver. (a) during  $Q_1$  turn-ON transition and (b) during  $Q_1$  turn-OFF transition.

# 3.3. Comparisons

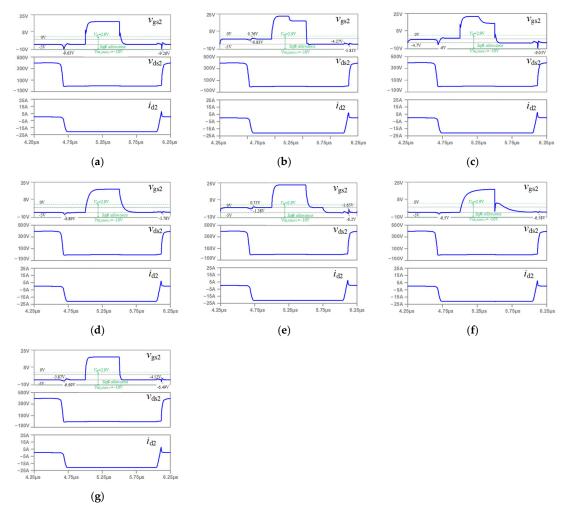

The comparisons between the prior drivers in [24-27,30,31] and the proposed driver are presented in this section. The driver in [24] is the conventional driver, which is a simple and generally-used SiC device application. Drivers in [25–27,30,31] add assistant circuits to the conventional driver in [18]. The simulation waveforms of  $Q_2$  based on the prior drivers in [24–27,30,31] and the proposed driver are shown in Figure 8, which is obtained under the same switching performance of Q<sub>1</sub>. The parameters of the prior drivers in [24– 27,30,31] and the proposed driver are shown in Table 3. In addition, the suppression method, assistant components, implementation and suppression effectiveness of the prior drivers and the proposed driver are compared in Table 4. Drivers in [25-27] shift the driver voltage to make a spurious pulse in the safety allowance. Drivers, except in [19], provide a low impedance path for the displacement current of the gate-drain capacitor. From simulation results, it is observed that drivers with the low impedance path have lower spikes of the spurious pulse than the conventional driver in [24] and the driver in [26]. The driver in [25] has the lowest spikes of the spurious pulse on the gate voltage but the assistant circuit is complex. The driver in [31] has the simplest circuit structure because of no added transistor. However, the driver chip in [31] needs split output because the switch  $S_{2L}$  is reusable to connect the turn-OFF gate resistor and the capacitor  $C_{a1}$ , which guarantees no effect on the turn-ON performance of SiC MOSFET. Comparing drivers in [25–27,30], which do not need to use the driver chip with split output, the proposed driver is easier to implement owing to no MOSFET and no driver circuit. Therefore, considering the suppression effectiveness and the implementation, the proposed driver is a good choice.

|                 | Parameter                                                                                                                                           |

|-----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|

| Driver in [24]  | $V_{1L} = 18 \text{ V}, V_{2L} = 5 \text{ V}, R_{L} = 10 \Omega$                                                                                    |

| Driver in [25]  | $V_{1L}=23 \text{ V}, V_{2L}=5 \text{ V}, R_{L}=10 \Omega$                                                                                          |

| Driver in [26]  | $V_{1L} = 18 \text{ V}, V_{Z} = 4.7 \text{ V}, R_{L\_ON} = 10 \Omega, R_{L\_OFF} = 10 \Omega, R_{C} = 1 \Omega, R_{M} = 0.1 \Omega, C_{Z} = 100 nF$ |

| Driver in [27]  | $V_{1L} = 18 \text{ V}, V_{2L} = 5 \text{ V}, R_{L} = 10 \Omega$                                                                                    |

| Driver in [30]  | $V_{1L} = 18 \text{ V}, V_{2L} = 5 \text{ V}, R_{L} = 10 \Omega, C_{a} = 5 \text{ nF}$                                                              |

| Driver in [31]  | $V_{1L} = 18 \text{ V}, V_{2L} = 5 \text{ V}, R_{L\_ON} = 10 \Omega, R_{L\_OFF} = 10 \Omega, C_{a1} = 5 \text{ nF}$                                 |

| Proposed driver | $V_{1L} = 18 \text{ V}, V_{2L} = 5 \text{ V}, R_{L} = 10 \Omega$                                                                                    |

**Figure 8.** Simulation results of the prior drivers in [24–27,30,31] and the proposed driver. (a) the conventional driver in [24], (b) driver in [25], (c) driver in [26], (d) driver in [27], (e) driver in [30], (f) driver in [31] and (g) the proposed driver.

|                 | Suppression Method                                    | Assistant Components                                      | Implementation | Suppression Effectiveness |

|-----------------|-------------------------------------------------------|-----------------------------------------------------------|----------------|---------------------------|

| Driver in [25]  | Shift driver voltage and provide a low impedance path | One diode, two MOSFETs and drivers for MOSFETs            | hard           | Good                      |

| Driver in [26]  | Shift driver voltage                                  | One resistor, one MOSFET and driver for MOSFET            | Medium         | Bad                       |

| Driver in [27]  | Shift driver voltage and provide a low impedance path | Two diodes, two switches (if MOSFETs, drivers are needed) | hard           | Medium                    |

| Driver in [30]  | provide a low impedance path                          | One capacitor, one MOSFET and driver for MOSFET           | Medium         | Good                      |

| Driver in [31]  | provide a low impedance path                          | Two capacitors                                            | Easy           | Good                      |

| Proposed driver | provide a low impedance path                          | Two BJTs and one diode                                    | Easy           | Good                      |

**Table 4.** Comparisons between the prior drivers in [25–27,30,31] and proposed driver.

#### 4. Verification

Comparison experiments are implemented between the conventional driver and the proposed driver to verify the proposed driver. C2M0080120D by Cree Inc. is tested in this paper and the related parameters of C2M0080120D are shown in Table 1. The Parameters of synchronous buck and driver are the same with the simulation model shown in Table 2. The driver PCB boards must be mounted as close as the plastic package of SiC MOSFET, and the leads connected into the driver loop are shortest which reduces the common source inductors.

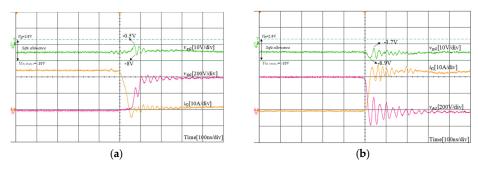

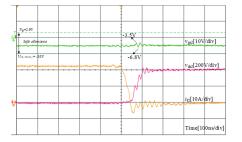

Figure 9 presents the switching waveforms with the conventional driver. Figure 10 presents the switching waveforms with the proposed driver. The conventional driver is realized by removing the assistant circuit in the proposed driver. The forward current  $i_{12}$  of  $D_2$ , the drain-source voltage  $v_{ds2}$  of  $Q_2$  and the gate-source voltage  $v_{gs2}$  of  $Q_2$  are tested. From Figure 9, the spikes of the spurious pulse on the gate-source voltage of  $Q_2$  with conventional drivers are tested as -0.5 V and -8 V during  $Q_1$  turn-ON transition, and -1.7 V and -8.9 V during  $Q_1$  turn-OFF transition, respectively. From Figure 10, the spikes of the spurious pulse on the gate-source voltage of  $Q_2$  with the proposed driver are tested as -3.5 Vand-6.8 V during  $Q_1$  turn-ON transition, and -3.3 V and -7 V during  $Q_1$  turn-OFF transition, respectively. Comparing Figures 9 and 10, the spikes of the spurious pulse on the gate-source voltage of  $Q_2$  are obviously decreased by using the proposed driver.

**Figure 9.** Experimental results with the conventional driver. (a) during  $Q_1$  turn-ON transition, and (b) during  $Q_1$  turn-OFF transition.

(a) (b)

**Figure 10.** Experimental results with the proposed driver. (a) during  $Q_1$  turn-ON transition, and (b) during  $Q_1$  turn-OFF transition.

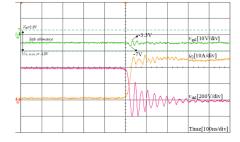

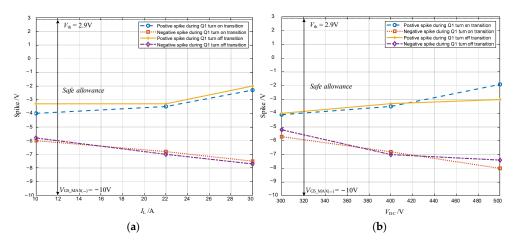

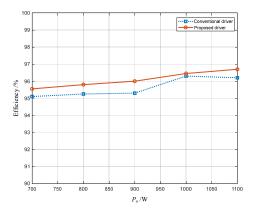

Figure 11a,b show the spikes of the spurious pulses under different currents IL and different voltages VDC. As shown in Figure 11, the higher operating current or voltage makes the crosstalk issue more severe. However, it is observed that the proposed driver is effective to suppress crosstalk issues and guarantees the spikes of the spurious pulses within safe allowance. Figure 12 presents the efficiency of 1.1 kW synchronous buck with the conventional driver or the proposed driver. The tested conditions of synchronous buck are presented in Table 5 and the efficiency is tested under open-loop control. From Figure 12, it is observed that the efficiency of synchronous buck converter is higher than with the proposed driver, and the maximum efficiency is 96.7%.

Table 5. Efficiency tested conditions of synchronous buck.

| Parameter           | Value      | Parameter        | Value  |

|---------------------|------------|------------------|--------|

| Input voltage       | 400 V      | Dead time        | 500 ns |

| Output voltage      | 100 V      | Output inductor  | 100 μΗ |

| Output power        | 700~1100 W | Output capacitor | 220 μF |

| Switching frequency | 50 kHz     |                  | ·      |

**Figure 11.** Spikes of spurious pulses at different working conditions, (a) *I*L and (b) *V*DC.

Figure 12. Efficiency of synchronous buck with the conventional driver and the proposed driver.

#### 5. Conclusions

Crosstalk issues impact the reliability of SiC MOSFET applications. The crosstalk mechanisms of SiC MOSFET are analyzed in this paper, which can be divided into two perspectives: the voltage drops across the common-source inductors and the displacement current of the gate—drain capacitor. A new gate driver for suppressing crosstalk issues is proposed in this paper. Two BJTs and one diode are used to connect the gate terminal of SiC MOSFET and the negative driver voltage, which provides a low impedance path to bypass the displacement current of the gate-drain capacitor. The operating principle and simulation results show the proposed driver is valid on suppressing crosstalk. In addition, the comparisons between the prior drivers and the proposed driver show the proposed driver is a good choice when trading off the suppression effectiveness and circuit complexity. The experiments also prove the proposed driver is effective on suppressing crosstalk issues. In addition, the efficiency of 1.1 kW synchronous buck with the proposed driver is higher than with the conventional driver, which can reach 96.7%.

**Author Contributions:** Conceptualization, M.L.; methodology, M.L.; validation, M.L.; writing—original draft preparation, M.L.; writing—review and editing, J.B. and Y.J.; supervision, J.C. and P.J.; funding acquisition, J.C. and P.J. All authors have read and agreed to the published version of the manuscript.

**Funding:** This research was funded by National Key R&D Program of China, grant number 2021YFF0700102.

Data Availability Statement: Not applicable.

**Conflicts of Interest:** The authors declare no conflict of interest. The funders had no role in the design of the study; in the collection, analyses, or interpretation of data; in the writing of the manuscript; or in the decision to publish the results.

#### References

- 1. Zhang, L.; Zheng, Z.; Lou, X. A review of WBG and Si devices hybrid applications. Chin. J. Electr. Eng. 2021, 7, 1–20.

- Narasipuram, R.P.; Mopidevi, S. A technological overview & design considerations for developing electric vehicle charging stations. J. Energy Storage 2021, 43, 103225.

- 3. Oliveira, J.; Alhoussen, A.; Loiselay, F.; Morel, H.; Planson, D. Switching Behavior and Comparison of Wide Bandgap Devices for Automotive Applications. In Proceedings of the 2021 23rd European Conference on Power Electronics and Applications (EPE'21 ECCE Europe), Ghent, Belgium, 6–10 September 2021; pp. 1–10.

- 4. Shah, S.S.; Narwal, R.; Bhattacharya, S.; Kanale, A.; Cheng, T.H.; Mehrotra, U.; Agarwal, A.; Baliga, B.J.; Hopkins, D.C. Optimized AC/DC Dual Active Bridge Converter using Monolithic SiC Bidirectional FET (BiDFET) for Solar PV Applications. In Proceedings of the 2021 IEEE Energy Conversion Congress and Exposition (ECCE), Vancouver, BC, Canada, 10–14 October 2021; pp. 568–575.

- 5. Iannaccone, G.; Sbrana, C.; Morelli, I.; Strangio, S. Power Electronics Based on Wide-Bandgap Semiconductors: Opportunities and Challenges. *IEEE Access* **2021**, *9*, 139446–139456.

- 6. Xu, Y.; Yuan, X.; Ye, F.; Wang, Z.; Zhang, Y.; Diab, M.; Zhou, W. Impact of High Switching Speed and High Switching Frequency of Wide-Bandgap Motor Drives on Electric Machines. *IEEE Access* **2021**, *9*, 82866–82880.

- 7. Yu, S.; Wang, J.; Zhang, X.; Liu, Y.; Jiang, N.; Wang, W. The potential impact of using traction inverters with SiC MOSFETs for electric buses. *IEEE Access* **2021**, *9*, 51561–51572.

- 8. Zhang, C.; Srdic, S.; Lukic, S.; YKang Choi, E.; Tafti, E. A SiCbased 100 kW high-power-density (34 kW/L) electric vehicle traction inverter. In Proceedings of the 2018 IEEE Energy Conversion Congress and Exposition (ECCE), Portland, OR, USA, 23–27 September 2018.

- 9. Nguyen, H.V.; Lee, D.C.; Blaabjerg, F. A novel SiC-based multifunctional onboard battery charger for plug-in electric vehicles. *IEEE Trans. Power Electron.* **2021**, *36*, 5635–5646.

- 10. Abbasi, M.; Emamalipour, R.; Cheema, M.A.M.; Lam, J. A new fully magnetically coupled SiC-based DC/DC step-up LLC resonant converter with inherent balanced voltage sharing for renewable energy systems with a medium voltage DC grid. In Proceedings of the 2019 IEEE Energy Conversion Congress and Exposition (ECCE), Baltimore, MD, USA, 29 September–3 October 2019; pp. 5542–5547.

- 11. Schwarzer, G.U.; Buschhorn, S.; Vogel, K. System benefits for solar inverters using SiC semiconductor modules. In Proceedings of the International Exhibition and Conference for Power Electronics, Intelligent Motion, Renewable Energy and Energy Management, Nuremberg, Germany, 20–22 May 2014; 787–794.

- 12. She, X.; Huang, A.Q.; Lucía, Ó.; Ozpineci, B. Review of silicon carbide power devices and their applications. *IEEE Trans. Ind. Electron.* **2017**, *64*, 8193–8205.

13. Lemmon, A.; Mazzola, M.; Gaord, J.; Parker, C. Stability considerations for silicon carbide field-effect transistors. *IEEE Trans. Power Electron.* **2013**, *28*, 4453–4459.

- 14. Mohan, N.; Undeland, T.M. Power Electronics: Converters, Applications, and Design; John Wiley & Sons: Hoboken, NJ, USA, 2007.

- 15. Zhang, Z.; Guo, B.; Wang, F.; Tolbert, L.M.; Blalock, B.J.; Liang, Z. Impact of ringing on switching losses of wide band-gap devices in a phase-leg configuration. In Proceedings of the 2014 IEEE Applied Power Electronics Conference and Exposition—APEC, Fort Worth, TX, USA, 16–20 March 2014; pp. 2542–2549.

- 16. Jahdi, S.; Alatise, O.; Gonzalez, J.A.; Bonyadi, R.; Ran, L.; Mawby, P. Temperature and switching rate dependence of crosstalk in Si-IGBT and SiC power modules. *IEEE Trans. Ind. Electron.* **2015**, *63*, 849–863.

- 17. Nishigaki, A.; Umegami, H.; Hattori, F.; Martinez, W.; Yamamoto, M. An analysis of false turn-on mechanism on power devices. In Proceedings of the 2014 IEEE Energy Conversion Congress and Exposition (ECCE), Pittsburgh, PA, USA, 14–18 September 2014; pp. 2988–2993.

- 18. Wang, J.; Chung, H.S. Impact of parasitic elements on the spurious pulse in synchronous buck converter. *IEEE Trans. Power Electron.* **2014**, *29*, 6672–6685.

- 19. Xu, S.; Liu, X.; Sun, W. Modelling of power metal-oxide semiconductor field-effect transistor for the analysis of switching characteristics in half-bridge converters. *IET Circuits Devices Syst.* **2010**, *4*, 327–336.

- 20. Xu, S.; Sun, W.; Sun, D. Analysis and design optimization of brushless DC motor's driving circuit considering the Cdv/dt induced effect. In Proceedings of the 2010 IEEE Energy Conversion Congress and Exposition, Atlanta, GA, USA, 12–16 September 2010; pp. 2091–2095.

- 21. Yang, B.; Zhang, J. Effect and utilization of common source inductance in synchronous rectification. In Proceedings of the 2005 IEEE Applied Power Electronics Conference and Exposition, Austin, TX, USA, 6–10 March 2005; pp. 1407–1411.

- 22. Yin, S.; Tseng, K.J.; Tong, C.F.; Simanjorang, R.; Gajanayake, C.J.; Nawawi, A.; Liu, Y.; Liu, Y.; See, K.Y.; Sakanova, A.; et al. Gate driver optimization to mitigate shoot-through in high-speed switching SiC half bridge module. In Proceedings of the 2015 IEEE 11th International Conference on Power Electronics and Drive Systems, Sydney, NSW, Australia, 9–12 June 2015; pp. 484–491.

- 23. Wang, J.; Chung, H.S. A novel RCD level shifter for elimination of spurious turn-on in the bridge-leg configuration. *IEEE Trans. Power Electron.* **2014**, *30*, 976–984.

- 24. Cree. SiC MOSFET Isolated Gate Driver. 2018. Available online: https://assets.wolfspeed.com/uploads/2020/12/CPWRAN21.pdf (accessed on 01 April 2018).

- 25. Zhang, Z.; Wang, F.; Tolbert, L.M.; Blalock, B.J.; Costinett, D.J. Active gate driver for fast switching and cross-talk suppression of SiC devices in a phase-leg configuration. In Proceedings of the 2015 IEEE Applied Power Electronics Conference and Exposition (APEC), Charlotte, NC, USA, 15–19 March 2015; pp. 774–781.

- 26. Wu, X.; Zaman, H.; Wu, P.; Jia, R.; Zhao, X.; Wu, X. A quasi-multilevel gate driver for fast switching and crosstalk suppression of SiC devices. *IEEE Access* **2020**, *8*, 191403–191412.

- 27. Zhang, Z.; Wang, F.; Tolbert, L.M.; Blalock, B.J. A gate assist circuit for cross talk suppression of SiC devices in a phase-leg configuration. In Proceedings of the 2013 IEEE Energy Conversion Congress and Exposition (ECCE), Denver, CO, USA, 15–19 September 2013; pp. 2536–2543.

- 28. Zhou, Q.; Gao, F.; Jiang, T. A gate driver of SiC MOSFET with passive triggered auxiliary transistor in a phase-leg configuration. In Proceedings of the 2015 IEEE Energy Conversion Congress and Exposition (ECCE), Montreal, QC, Canada, 20–24 September 2015; pp. 7023–7030.

- Gao, F.; Zhou, Q.; Wang, P.; Zhang, C. A gate driver of SiC MOSFET for suppressing the negative voltage spikes in a bridge circuit. IEEE Trans. Power Electron. 2017, 33, 2339–2353.

- 30. Zhang, Z.; Wang, F.; Tolbert, L.M.; Blalock, B.J. Active gate driver for crosstalk suppression of SiC devices in a phase-leg configuration. *IEEE Trans. Power Electron.* **2013**, 29, 1986–1997.

- 31. Li, Y.; Liang, M.; Chen, J.; Zheng, T.Q.; Guo, H. A low gate turn-off impedance driver for suppressing crosstalk of SiC MOSFET based on different discrete packages. *IEEE J. Emerg. Sel. Top. Power Electron.* **2018**, *7*, 353–365.

- 32. Texas Instruments. IGBT & SiC Gate Driver Fundamentals. 2019. Available online: https://www.ti.com/lit/eb/slyy169/slyy169.pdf (accessed on 1 July 2019).

- 33. Texas Instruments. ISO5852S Datasheet. 2017. Available online: https://www.ti.com (accessed on 1 January 2017).

- 34. BROADCOM. ACPL-337J-000E Datasheet. 2014. Available online: https://docs.broadcom.com/doc/AV02-4390EN (accessed on 9 May 2014).

- 35. Analog Devices. ADUM4135BRWZ Datasheet. 2020. Available online: https://www.analog.com/media/en/technical-documentation/data-sheets/ADuM4135.pdf (accessed on 1 July 2015).

- 36. Zhang, Z.; Wang, F.; Tolbert, L.M.; Blalock, B.J.; Costinett, D.J. Realization of high speed switching of SiC power devices in voltage source converters. In Proceedings of the 2015 IEEE 3rd Workshop on Wide Bandgap Power Devices and Applications (WiPDA), Blacksburg, VA, USA, 2–4 November 2015; pp. 28–33.

- Chen, J.; Li, Y.; Liang, M. A gate driver based on variable voltage and resistance for suppressing overcurrent and overvoltage of SiC MOSFETs. Energies 2019, 12, 1640.