# Article A 6-Bit 20 GS/s Time-Interleaved Two-Step Flash ADC in 40 nm CMOS

Dong-Ryeol Oh 🕕

Citation: Oh, D.-R. A 6-Bit 20 GS/s Time-Interleaved Two-Step Flash ADC in 40 nm CMOS. *Electronics* 2022, *11*, 3052. https://doi.org/ 10.3390/electronics11193052

Academic Editor: Gaetano Palumbo

Received: 2 September 2022 Accepted: 21 September 2022 Published: 25 September 2022

**Publisher's Note:** MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations.

**Copyright:** © 2022 by the author. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https:// creativecommons.org/licenses/by/ 4.0/). School of Electrical Engineering, Korea Advanced Institute of Science and Technology (KAIST), Daejeon 34141, Korea; droh@kaist.ac.kr; Tel.: +82-42-350-7525

**Abstract:** A 6-bit 20 GS/s 16-channel time-interleaved (TI) analog-to-digital converter (ADC) using a two-step flash ADC with a sample-and-hold (S/H) sharing technique and a gain-boosted voltage-to-time converter (VTC) is presented for high-speed wireline communication systems. By sharing one S/H between coarse and fine stages in the two-step flash ADC, the input bandwidth as well as area and power efficiency can be improved without a gain error between coarse and fine ADCs. Thanks to an eight-time interpolation using the gain-boosted VTC, the fine ADC has a small gate capacitance without a speed penalty, even in a small input voltage range. A prototype ADC implemented in a 40 nm CMOS process occupies a 0.1 mm<sup>2</sup> active area. The measured differential non-linearity (DNL) and integral non-linearity (INL) after offset and gain calibrations were 0.45 and 0.39 least significant bit (LSB), respectively. With a 9.042 GHz input, the measured signal-to-noise and distortion ratio (SNDR) and the spurious-free dynamic range (SFDR) were 30.12 and 40.23 dB, respectively. The small input capacitance of the sub-ADC enables a power-efficient track-and-hold amplifier (THA), resulting in a power consumption of 56.2 mW under a supply voltage of 0.9 V. The prototype ADC achieves a figure of merit (FoM) of 107.4 fJ/conversion-step at 20 GS/s.

**Keywords:** two-step; time-interleaving; time-domain; interpolation; voltage-to-time converter; sample-and-hold; flash; reference embedding; clock generation

# 1. Introduction

The demand for wired input/output bandwidth within data center networks is steadily increasing, driven by significant increases in data generation on wireline communication systems, such as cloud computing, mobile devices, and the Internet of things (IoT). In order to meet the demand, high-speed wireline communication systems applied with a multilevel signal modulation format, such as a pulse amplitude modulation 4-level (PAM-4), are required. In these wideband data communication systems, DSP-based high-speed serial links using an analog-to-digital converter (ADC) enable more complex and flexible applications of back-end digital signal processing. However, due to the addition of high-speed ADCs, the characteristics of input bandwidth, sampling rate, effective resolution, area, and power consumption of the ADC have a significant impact on the performance of the systems [1–7]. Recent studies show that a time-interleaving (TI) architecture is essential to convert the data above 10 GHz, and the performance of sub-ADC is a large portion of the TI ADC. At a medium resolution and a 20 GS/s conversion rate, sub-ADC types for the TI ADCs are generally divided into the flash and successive approximation register (SAR). Due to the fastest conversion speed of the flash ADC, the flash-based TI ADCs have the advantage of reducing the number of interleaving channels, which can reduce the hardware burden, such as a clock distribution and channel mismatch calibration on the TI ADC. However, many comparators required in the flash ADC and the burden on the offset calibration circuits for them directly affect the area and power consumption of the flash-based TI ADCs [6-10]. Recent studies on tens of GS/s TI ADCs have shown that the conversion speed of the SAR ADCs, used as the sub-ADC of the TI ADC, has been improved to the GHz level thanks to the advanced CMOS process [11-14]. However, the SAR

ADC requires not only the high-speed design for the comparator and logic corresponding to the number of conversion cycles, but also the management of internal clock signals for the comparator.

On the other hand, single-channel two-step flash ADCs have often been utilized to maximize the aforementioned advantages of the flash and SAR ADCs [15–21]. However, it was previously reported that the two-step flash ADCs have drawbacks, which are as follows: (1) settling time required to select the reference voltage ranges for the fine ADC (FADC) [15–17]; (2) large input capacitance and offset calibration complexity due to the full flash hardware in the FADC [18–20]; (3) bandwidth mismatch due to an additional input sampler [21]. Because of these limitations, SAR and flash architectures have been preferred over the two-step flash architecture as a sub-ADC for the TI ADC. With these reasons as a motivation, in this paper, a competitive TI two-step flash ADC suitable for a high-speed data conversion was proposed by improving the drawbacks of the existing two-step structures and applying them to the TI ADC.

The two-step flash ADC architecture used in this proposed TI ADC could be implemented with a low power, small area, and wide input bandwidth thanks to sample-andhold (S/H) sharing and reference-embedding eight-time interpolation techniques [22]. The two-step flash ADC could guarantee inherent gain matching between the coarse and fine stage and could reduce the sampling capacitance as well by utilizing the S/H sharing technique. In addition, thanks to the reference-embedded interpolation technique, only one capacitive digital-to-analog converter (C-DAC) is required for the coarse stage, and a reference resistor-string (R-string) for the FADC and its settling speed burden are eliminated. As a result, the two-step flash ADC could be designed with a low-power and wide input bandwidth. The small input capacitance of the sub-ADC leads the input sampling network of the TI architecture, such as a track-and-hold amplifier (THA), to be fast and power efficient. Therefore, in this design, only four-channel THAs, each operating at 5 GHz, are used for the 20 GS/s sampling rate, which realize the wide input bandwidth and reduce the complexity of the channel mismatch calibration.

This paper is organized as follows. The overall ADC with an input network and sub-ADC is described in Section 2. Detailed circuit implementations of a pseudo-differential comparator for a coarse ADC (CADC) with an offset calibration capability, a gain-boosted voltage-to-time converter (VTC) for an FADC, and a high-speed clock generation scheme with a digitally-controlled delay line (DCDL) are explained in Section 3. Section 4 shows the measurement results and Section 5 concludes the paper.

#### 2. Proposed ADC Architecture

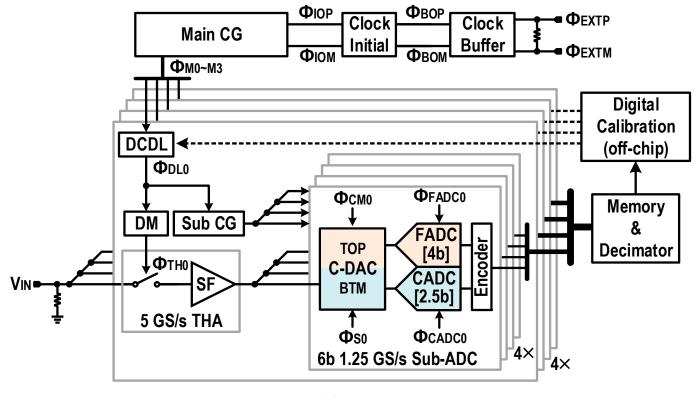

A block diagram of the proposed 6-bit 20 GS/s TI two-step flash ADC is shown in Figure 1a. The TI ADC consists of 4-channel 5 GS/s input samplers with a source follower (SF) buffer (i.e., THA), 16-channel 6-bit 1.25 GS/s two-step flash ADCs with one S/H shared by 2.5b CADC and 4b FADC, multi-phase clock generators (CG) for 5 GHz main sampling clocks ( $\Phi_{TH}$ ) and 1.25 GHz sub sampling clocks ( $\Phi_S$  and  $\Phi_{CM}$ ), memory for digital calibration, and a decimator for real-time measurement. Ten-gigahertz differential clocks ( $\Phi_{BOP}$  and  $\Phi_{BOM}$ ) are applied to the clock initial logic through the clock buffer based on the low-voltage differential signaling (LVDS) I/O [23]. As shown in Figure 1b, the clock initial logic ensures that the first rising edge of the positive output clock ( $\Phi_{IOP}$ ) always precedes the first rising edge of the negative output clock ( $\Phi_{IOM}$ ) whenever the ADC is enabled. In this way, the order of the output clocks ( $\Phi_{M0\sim M3}$ ) of the main clock generator (Main CG), which generates multi-phase clocks based on a ring-counter, can always be guaranteed. The sub-clock generator (Sub CG) makes the input and common voltage sampling clocks ( $\Phi_{50.4.8.12}$  and  $\Phi_{CM0.4.8.12}$ ) of the 4-channel sub-ADCs using the 5 GHz clock ( $\Phi_{DL0}$ ). The delay matching (DM) logic is added to generate a delay corresponding to the gate delay of the sub-clock generator. Each sampling time skew of the THAs (i.e., the falling edge of  $\Phi_{TH0\sim TH3}$ ) is controlled by the DCDL, and the digital input codes of the DCDL are obtained by the digital calibration engine implemented with the off-chip.

The details of the circuit implementations related to the clock generation will be covered in Section 3.3.

# (a)

Figure 1. Proposed 6-bit 20 GS/s TI two-step flash ADC. (a) Block and (b) timing diagrams.

### 2.1. Input Network

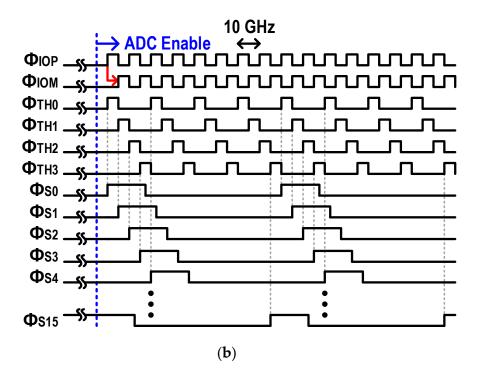

Figure 2 shows the input sampling network of the proposed 20 GS/s TI ADC. In this design, 4-channel THAs are used to achieve a wide input bandwidth over the Nyquist input and to reduce sampling errors, such as a charge injection and clock feed-through, induced by the interference between the sub-ADCs. As shown in Figure 2, the THA consists of NMOS sampling switches ( $M_1$  and  $M_2$ ) with dummy switches ( $M_3$ – $M_6$ ) and PMOSbased SF buffers. The cross-coupled dummy switches (M<sub>3</sub> and M<sub>4</sub>) prevent the signal feed-through during the hold time (i.e.,  $\Phi_{TH}$  is low), and the dummy switches (M<sub>5</sub> and M<sub>6</sub>) with the source and drain nodes shorted compensate for the clock feed-through, which changes the input common voltage of the SF buffers [24,25]. Since the differential swing range of the input voltage and the input common mode voltage of the TI ADC are 400 mV and 200 mV, respectively, the clock boosting circuit for the NMOS sampling switches is not required. The tracking times for the track-and-hold (T/H) of the THA and the S/H of the sub-ADC are approximately 50 ps and 150 ps, respectively, at a sampling rate of 20 GS/s. At the falling edge of  $\Phi_{TH}$ , the input voltage is sampled to the parasitic capacitance (C<sub>P</sub>), which is approximately 28 fF, formed by the SF buffer, dummy switches, and routing metal. Note that the sampling switches for the 4-channel THAs are not turned on at the same time. That is, the input bandwidth is defined by the resistance of the sampling switch and the parasitic capacitance for only one THA. Therefore, the input network of the proposed TI ADC is suitable for a wide input bandwidth [11]. Similar to the sampling method of the THA, the sampling switches of the 4-channel sub-ADCs driven by one SF buffer are not turned on at the same time. Moreover, due to the S/H sharing and reference-embedding techniques, the sampling capacitance of the sub-ADC was designed to be approximately 18 fF. As a result, the THA could be designed to be very compact, consuming 3.6 mW at a 0.9 V supply voltage.

**Figure 2.** Input network of the proposed 20 GS/s TI ADC composed of 4-channel 5 GS/s SF-based THAs.

#### 2.2. Two-Step Flash ADC

The small input capacitance, compact area, and low offset calibration burden of the sub-ADC are high priority factors for the realization of a power-efficient TI ADC with a wide input bandwidth. For this reason, in this design, the two-step flash architecture, considering the aforementioned factors, was applied to the sub-ADC for the TI ADC. The two-step flash ADC has been applied to the 7-bit 3 GS/s two-channel TI architecture in [22], and the advantages of the low-power, small area, and wide input bandwidth obtained by the S/H sharing and reference-embedding techniques have already been verified based on the measurement results. In this design, compared to [22], the two-step flash ADC was modified to be more suitable for the 20 GS/s TI ADC under the changed design conditions, such as the number of channels, input voltage range, and resolution.

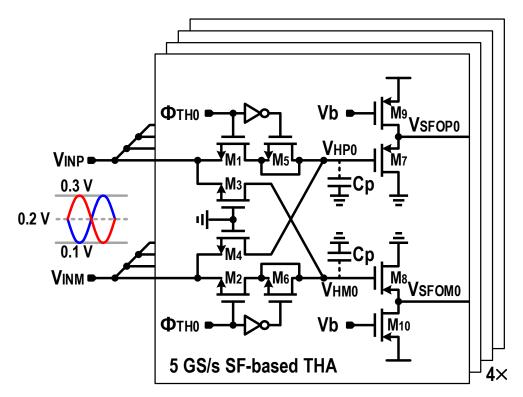

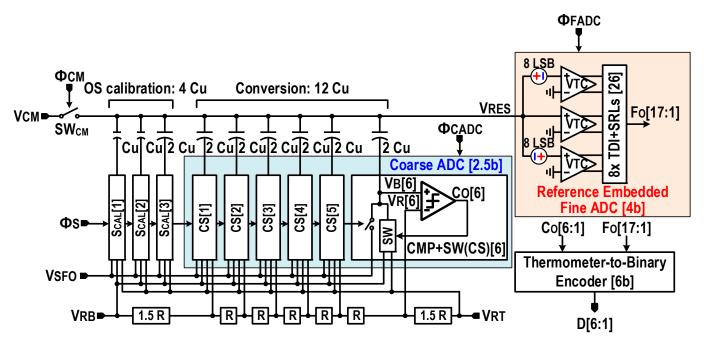

The block diagram of the single-channel 6-bit 1.25 GS/s two-step flash ADC is shown in Figure 3. The ADC consists of a 2.5-bit CADC, a 4-bit reference-embedded 8-times interpolating FADC, a C-DAC for the input sampling and residue generation, a R-string for the references of both the CADC ( $V_R$  [1:6]) and the C-DAC ( $V_{RT}$  and  $V_{RB}$ ), and a 6-bit digital encoder. Note that, unlike [22], a bootstrapped circuit for the input sampling switch is not used in this design. For a 6-bit resolution, the resolution of the CADC was selected to be 2.5-bit instead of 1.5-bit. The smaller resolution at the coarse stage can further reduce the input capacitance but consequently increases the hardware burden on the fine stage. Although the FADC can reduce its gate capacitance and power consumption thanks to the eight-time interpolation technique, the hardware complexity of the FADC increases relative to that of the CADC because the interpolation linearity and the offset calibration of the FADC should be considered. Moreover, the input capacitance of a single-channel ADC is mainly determined by the CDAC rather than the coarse comparator and is designed to be small enough thanks to the S/H sharing and the interpolation techniques.

Figure 3. Block diagram of the 6-bit 1.25 GS/s two-step flash ADC.

In this paper, the operation of the two-step flash ADC is briefly explained. For details, please refer to my previous work [22]. The 2.5-bit CADC is a flash architecture consisting of six comparators and switches for the input sampling and residue generation. Each input node of the comparators is intentionally untied to use the six 2Cus as the C-DAC elements for the fine conversion. Note that, as the sampling is actually conducted in the top-plate sampling manner, there is no gain error between the sampled input and the reference voltages from the R-string regardless of the parasitic capacitance at the top-plate node.

The thermometer output codes of the comparators ( $C_O$  [1:6]) directly control the switches and generate the residue voltage ( $V_{RES}$ ) at the top-plate node of the C-DAC for the fine stage by using the six 2 $C_{US}$ . The 4-bit FADC has only three reference-embedded VTCs at its front-end, and with the time-domain eight-time interpolation introduced in the flash ADC [26]. Thanks to the time-domain interpolation, the FADC greatly reduced the loading effect on the C-DAC; that is, the signal attenuation caused by the parasitic capacitance at the top-plate node of the C-DAC could be lowered. Savings in the power consumption and silicon area are other advantages of the interpolation technique. The reference-embedded VTC is covered in Section 3.2.

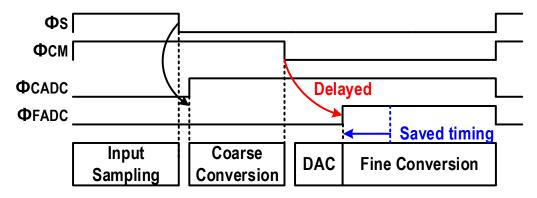

Looking at the timing diagram shown in Figure 4, the conversion clocks for the CADC and FADC ( $\Phi_{CADC}$  and  $\Phi_{FADC}$ ) are delayed versions of the input sampling clock ( $\Phi_S$ ) and the common voltage sampling clock ( $\Phi_{CM}$ ), respectively, which can be generated with a simple inverter delay; that is, the sub clock generator only needs to transmit  $\Phi_S$  and  $\Phi_{CM}$  to the sub-ADC. In this design, as the total capacitance of the C-DAC is as small as 12.8 fF (excluding parasitic) with  $C_U = 0.8$  fF, the settling time of the C-DAC is very short. This implies that the settling time can be generated by using a simple logic-gate delay from the falling edge of  $\Phi_{CM}$ . As a result, the remaining time after the fast C-DAC settling could be utilized for the FADC.

Figure 4. Timing diagram of the 6-bit 1.25 GS/s two-step flash ADC.

#### 3. Circuit Implementation

#### 3.1. Comparator Design for CADC

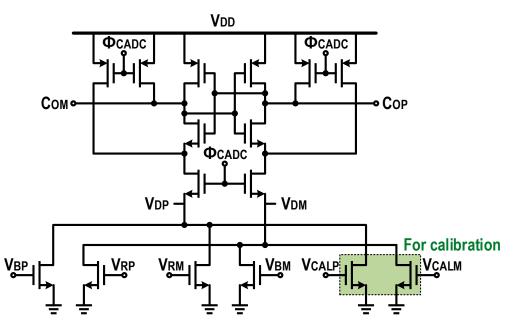

In this design, six dynamic comparators were applied to the 2.5-bit flash CADC. Since the unit capacitor of the C-DAC connected to the gate of the comparator is very small at 0.8 fF, it is necessary to consider the input kickback noise induced by the comparator. The kickback noise degrades the quality of the sampled signal to be used for the fine conversion in the proposed two-step ADC architecture. Therefore, as shown in Figure 5, the comparators were designed in a pseudo differential structure [22]. Note that the signal-dependent kickback error can be eliminated by keeping the source node of the input transistors to GND. Even though V<sub>DP/DM</sub> change during the latching operation, the kickback by them will be eliminated because the net voltages of V<sub>DP/DM</sub> are charged from GND and then discharged back to GND (eventually zero). Refer to [22] for more details on eliminating the kickback error. The estimated 1-sigma offset of the comparators is 15 mV, whereas the redundancy of the FADC is  $\pm 4$  least significant bit (LSB), which is  $\pm 25$  mV. Thus, the offset calibration of the comparators is required to prevent the nonlinearity caused by the offset mismatch. In this design, as shown in Figure 5, a differential pair connected in parallel with the input transistors was added for the offset calibration without a speed penalty. The gate voltages, V<sub>CALP</sub> and V<sub>CALM</sub>, were controlled by a 4-bit resistive digitalto-analog converter (R-DAC) with a foreground calibration [26]. The range and accuracy of the offset calibration engine could be designed to be  $\pm 90$  mV and 11.25 mV, respectively.

Figure 5. Pseudo differential comparator with the offset calibration capability used in the CADC.

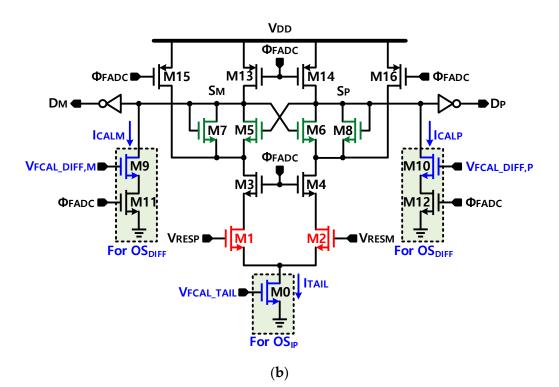

# 3.2. Gain-Boosted VTC for FADC

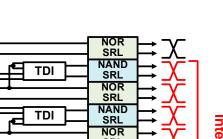

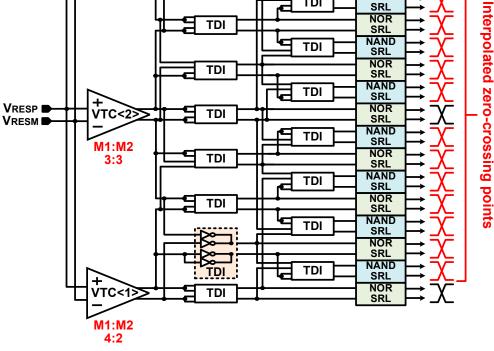

Figure 6a shows the simplified block diagram of the 4-bit FADC with the eight-time time-domain interpolation technique. To generate 17 zero-crossing points (i.e., 4-bit resolution) in a flash-type conversion manner, the FADC consisted of three VTCs, a time-domain interpolator (TDI) array, and a NAND- and NOR-based SR-Latch array. The interpolation technique generates seven additional interpolated zero-crossing points between two adjacent VTCs. Thanks to the simple inverter-based TDIs, this structure reduces the power consumption, input capacitance, area, and burden of the offset calibration. The designed input capacitance of the FADC, including the routing capacitance between the C-DAC and the FADC, was only approximately 5 fF. This allowed the total capacitance of the C-DAC to be as low as 12.8 fF, resulting in an approximately 28% signal attenuation.

The circuit of the reference-embedded VTC is shown in Figure 6b. Note that, in this design, the 1 LSB voltage of the FADC was reduced by approximately 32% compared to [22]. Therefore, the voltage-to-time conversion gain must be increased to prevent a linearity degradation caused by the input-referred offset of the back-end circuits, such as the TDIs and SR-Latches. In this design, to enhance the time gain of the VTC, a positive feedback loop, which consists of M5 and M6, was added to the output nodes of the dynamic amplifier (i.e.,  $S_P$  and  $S_M$  nodes) based on [27]. In addition, M7 and M8 was added to  $S_P$  and  $S_M$  nodes to alleviate the linearity degradation caused by the positive feedback. Consequently, the voltage-to-time gain of the VTC was increased from 0.9 ps/mV in [22] to 1.5 ps/mV.

The lower and upper VTCs (i.e., VTC<1> and VTC<3> shown in Figure 6a) have intentional offsets for embedded reference. Therefore, only one C-DAC with 16Cus was required for the residue generation, which means that the total number of the unit capacitance of the two-step flash ADC could be designed to be smaller than that of a conventional SAR ADC. The reference voltages for three VTCs were embedded by the different size ratio of M1 and M2 shown in Figure 6b. In this design, the size ratios of M1 and M2 were 4:2, 3:3, and 2:4 in that order for VTC<1:3> as shown in Figure 6a. The output time difference of the lower and upper VTCs (i.e., VTC<1> and VTC<3>) cannot be constant over a wide input range because of the transconductance (gm) nonlinearity of the input pair. However, in this design, the reference range between VTCs was approximately 32 mV, which is almost 2/3 of the previous work in [22], so the VTC gain could be designed to be more linear than that of [22].

TDI

TDI

+ v⊤c<3≥

M1:M2

2:4

**Figure 6.** (a) Four-bit 8-time time-domain interpolating FADC. (b) Reference-embedded VTC with positive feedback for gain boosting.

On the other hand, the size ratio design cannot guarantee the required offset of each VTC accurately. Thus, an offset calibration for the VTCs is mandatory. In this design, the offset mismatches of the reference-embedded VTCs were calibrated by the advanced sequential slope-matching offset calibration technique in [22]. The embedded references of the three VTCs for the calibration were implanted during the foreground calibration mode by utilizing the 4Cus of the "OS calibration" part in the C-DAC shown in Figure 3, where the weight of Cu corresponds to the step size of the VTC. Note that, in this VTC-based time-domain interpolation, not only the differential offset of each VTC (OS<sub>DIFF</sub>) but also the offsets of interpolated zero-crossing points generated by the outputs of two neighboring VTCs ( $OS_{IP}$ ) should be taken care of with calibration. The  $OS_{DIFF}$  and  $OS_{IP}$  were calibrated by the differentially controlled current sources (I<sub>CALP</sub> and I<sub>CALM</sub>) and by the tail current  $(I_{TAIL})$ , respectively, as shown in Figure 6b. One thing to note is that the change in the  $I_{TAIL}$ can also change the OS<sub>DIFF</sub> as well because it affects the operating condition of the VTC. Therefore, even though the calibration for the OS<sub>DIFF</sub> is completed, it should be calibrated repeatedly until the calibration for the  $OS_{IP}$  is carried out to compensate for the changes in the OS<sub>DIFF</sub>. The design details of the advanced sequential slope-matching offset calibration were sufficiently covered in [22].

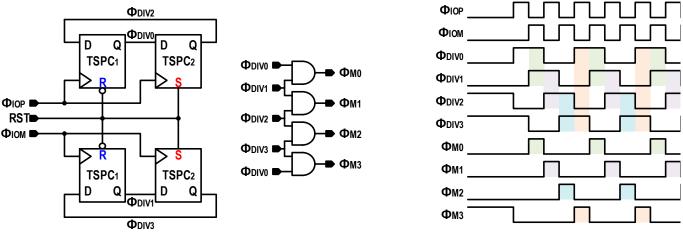

Figure 7 shows the output time difference according to the size ratios of the M5 (M6) and M7 (M8) of the VTC shown in Figure 6b. In this design, the size ratio of M5 and M7 was selected as 4:1 considering the linearity and the time gain of the VTC. As shown in Figure 7, when the size ratio of M5 and M7 is 4:1, the time gain varies from 1.56 ps/mV to 1.09 ps/mV within the interpolation range of the VTC; that is, the error of the time output due to the nonlinearity of the VTC is approximately 0.3 LSB, which is improved by half through the interpolation.

**Figure 7.** Output time difference of the VTC,  $D_P$ - $D_M$ , versus various input voltages,  $V_{RESP}$ - $V_{RESM}$ , according to the size ratios of M5 and M7 of the VTC.

#### 3.3. High-Speed Multi-Phase Clock Generation

In order to implement a conversion rate of 20 GS/s in the proposed TI ADC, 5 GHz 4-phase sampling clocks ( $\Phi_{M0\sim M3}$ ) and 1.25 GHz 16-phase sampling clocks ( $\Phi_{S0\sim S15}$  and  $\Phi_{CM0\sim CM15}$ ) are required for the 4-channel THAs and the 16-channel sub-ADCs, respectively. Since these high-speed multi-phase clocks have a very short time difference corresponding to 20 GHz (i.e., 50 ps), they need to be carefully designed to stably generate high-speed clocks. Therefore, this section deals with some design schemes for stably generating high-speed multi-phase clocks without systematic time mismatches between

the 4-channel THAs, including the DCDL logic for the monotonicity of the controlled sampling clocks.

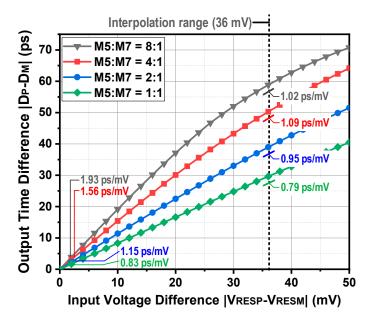

3.3.1. Clock Initial Logic

In this design, to alleviate the design burden for the high-speed multi-phase clock generation, the proposed TI ADC received externally applied 10 GHz differential clocks  $(\Phi_{\text{EXTP}} \text{ and } \Phi_{\text{EXTM}})$  instead of a 20 GHz single clock, and the differential clocks were transmitted to the input of the clock initial logic shown in Figure 8 through the clock buffer. Since the multi-phase clocks for the THAs are generated by dividing the two 10 GHz clocks  $(\Phi_{IOP} \text{ and } \Phi_{IOM})$  based on a ring-counter, the order between  $\Phi_{IOP}$  and  $\Phi_{IOM}$  triggering the clock divider is very important. If the order between  $\Phi_{IOP}$  and  $\Phi_{IOM}$  is changed whenever the ADC is activated, the order of operation between the sub-channels is also changed, which can cause the TI ADC to malfunction. Therefore, the initial clock logic shown in Figure 8a was applied to the clock path so that the positive clock always precedes the negative clock among the two 10 GHz clocks. The operation of the clock initial logic can be described with Figure 8b. When  $\Phi_{BOP}$  and  $\Phi_{BOM}$  are free running, the reset signal (RST) of the ADC is converted from "High" to "Low" for starting the clock generation of the TI ADC. EN<sub>Pre</sub> and EN<sub>P</sub> are triggered to "High" by the first and second rising edges of  $\Phi_{BOM}$ , respectively, following the falling edge of RST. Keep in mind that the DFF<sub>1</sub> is added to alleviate the metastable issue of the D-type flip flop (DFF). EN<sub>M</sub> is triggered from "Low" to "High" only after  $EN_P$  becomes "High" in synchronization with the following rising edge of  $\Phi_{BOP}$ . Therefore, the rising edge of EN<sub>M</sub> is always triggered with a delay of half of the 10 GHz clock period (i.e., 50 ps at 20 GS/s conversion rate) as that of EN<sub>P</sub>. Finally, based on the triggered sequence of  $EN_P$  and  $EN_M$ ,  $\Phi_{BOP}$  and  $\Phi_{BOM}$  are bypassed by the two NAND gates to  $\Phi_{IOP}$  and  $\Phi_{IOM}$ , respectively. One thing to note is that, for the normal clock generation, the sum of the gate delay and set-up time of the DFF should not exceed 50 ps at the 20 GS/s conversion rate. If the design margin is insufficient, an additional phase selector may be required. However, in this design, the sum of the gate delay and the set-up time of the DFF was designed to be approximately 42 ps in the slow condition.

Figure 8. Clock initial logic. (a) Block and (b) timing diagrams.

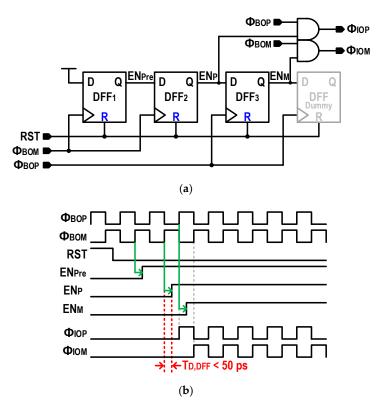

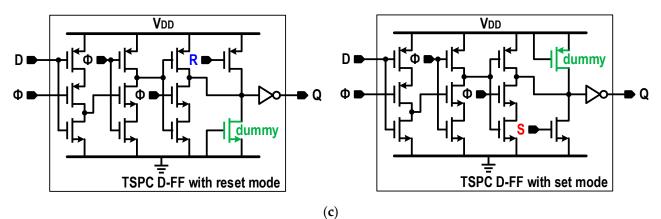

# 3.3.2. Main Clock Generation

Figure 9a shows the block diagram of the main clock generator for the sampling clocks of the four-channel THAs. The main clock generator consists of two ring-counters, and has a DFF with a reset mode and a DFF with a set mode, and four NAND gates. As shown in Figure 9b,  $\Phi_{IOP}$  and  $\Phi_{IOM}$  drive their respective ring counter, and are divided into four-phase clocks,  $\Phi_{DIV0\sim DIV3}$ , with a 50% duty cycle, shifted by the phase difference between  $\Phi_{IOP}$  and  $\Phi_{IOM}$ . Then, these four-phase clocks are converted to main sampling clocks,  $\Phi_{M0\sim M3}$ , with a 25% duty cycle for the THAs by the NAND gates. On the other hand, as shown in Figure 9c, the DFF is a true single-phase clock (TSPC) structure for lowpower and high-speed clock triggering, and a dummy transistor was added to eliminate a phase mismatch caused by the transistors for the reset and set mode. Note that the phase mismatch in the path generating the sampling clock of the THAs is a factor that attenuates the accuracy of the time skew calibration engine. As mentioned in Section 3.3.1, since the multi-phase was generated using the 10 GHz differential clocks sequentially applied by the clock initial logic instead of a 20 GHz single clock, the design burden of the DFFs to make 5 GHz four-phase clocks was halved. As a result, designing a high-speed and power-efficient main clock generator for TI architecture corresponding to a 20 GHz clock speed could be simplified.

(b)

**Figure 9.** Main clock generator. (**a**) Multi-phase generation logic. (**b**) Timing diagram. (**c**) Circuits for the TSPC DFF with set and reset modes.

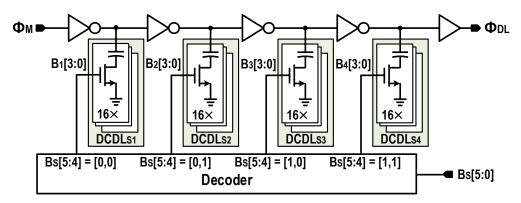

#### 3.3.3. Digitally-Controlled Delay Line

The main sampling clocks ( $\Phi_{TH0\sim TH3}$ ) of the four-channel THAs have a phase difference between the clocks due to process and layout mismatches. This phase difference causes the sampling time skew error between the THAs, which is a major source of the performance degradation according to increasing the input frequency in the TI architecture. Therefore, in this design, the time skew errors were calibrated on-chip by the DCDL shown in Figure 10, and detected off-chip based on [28,29]. Note that the time skew errors were detected based on a single-tone sinusoidal input. As shown in Figure 10, the 6-bit binary controlled DCDL consists of a capacitor array, an inverter chain, and a digital decoder. The capacitor array is divided into four banks, DCDL<sub>S1~S4</sub>, in order to improve the calibration accuracy and relieve the driving strength of the inverter buffers. As shown in Table 1, each DCDL bank is sequentially selected from DCDL<sub>S1</sub> to DCDL<sub>S4</sub> by the thermometer control according to the 2-bit most significant bit (MSB) codes (B<sub>S</sub> [5:4]). In addition, the capacitor array of each DCDL bank is controlled by the 4-bit binary code (B<sub>1~4</sub> [3:0]). Note that the B<sub>1~4</sub> [3:0] is B<sub>S</sub> [3:0] bypassed to each DCDL bank according to B<sub>S</sub> [5:4].

Figure 10. Block diagram of 6-bit DCDL.

| B <sub>S</sub> [5:4] | B <sub>1</sub> [3:0] | B <sub>2</sub> [3:0] | B <sub>3</sub> [3:0] | B <sub>4</sub> [3:0] |

|----------------------|----------------------|----------------------|----------------------|----------------------|

| 00                   | B <sub>S</sub> [3:0] | 0000                 | 0000                 | 0000                 |

| 01                   | 1111                 | B <sub>S</sub> [3:0] | 0000                 | 0000                 |

| 10                   | 1111                 | 1111                 | B <sub>S</sub> [3:0] | 0000                 |

| 11                   | 1111                 | 1111                 | 1111                 | B <sub>S</sub> [3:0] |

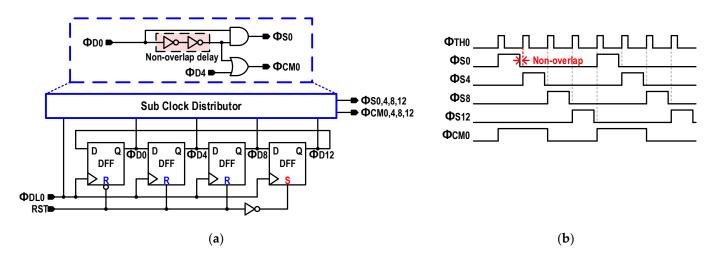

#### 3.3.4. Sub-Clock Generation

As mentioned in Section 2.2, only two 1.25 GHz clocks ( $\Phi_S$  and  $\Phi_{CM}$ ) are needed for the sub-ADC. The 1.25 GHz clocks can be generated by dividing the output of the DCDL, which is a 5 GHz clock, by four; that is, the clocks for four-channel sub-ADCs following one THA (e.g.,  $\Phi_{S0,4,8,12}$  and  $\Phi_{CM0,4,8,12}$ ) can be generated with only one clock divider, such as a 4-bit ring counter shown in Figure 11a, which can lead to reducing the area and current consumption. In the process of generating  $\Phi_M$  and  $\Phi_S$ , one thing to note is that the sampling clocks should be designed in consideration of an interference between the sub-ADCs. In other words, the falling edge of  $\Phi_S$  should be non-overlapping with the rising edge of  $\Phi_M$  for the other sub-ADC as shown in Figure 11b.

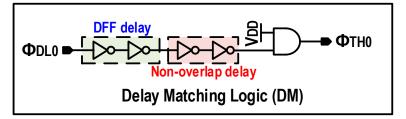

In this design, the non-overlap between the two clocks was realized using the DM logic shown in Figure 12. The DM logic guarantees that the rising edge of  $\Phi_M$  always starts after the gate delay of two inverters rather than the falling edge of  $\Phi_S$ .

Figure 12. DM logic.

# 4. Measurement Results

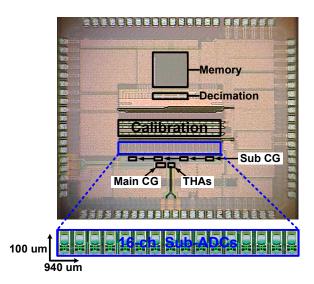

A prototype 6-bit TI two-step flash ADC was designed to have a 20 GS/s conversion rate in a 40 nm CMOS process. Figure 13 shows a die photograph. An active area of the proposed TI ADC, including four-channel THAs, a main clock generator, four-channel sub-clock generators, and sixteen-channel sub-ADCs, is 0.1 mm<sup>2</sup>, and the block for the foreground offset calibration occupies an additional area of 0.12 mm<sup>2</sup>. The decimation logic and memory were implemented on-chip for real-time measurement and channel mismatch analysis, respectively. The memory can store 1024 samples (i.e., 64 samples per sub-ADC) for the 6-bit TI ADC.

Figure 13. Die photograph.

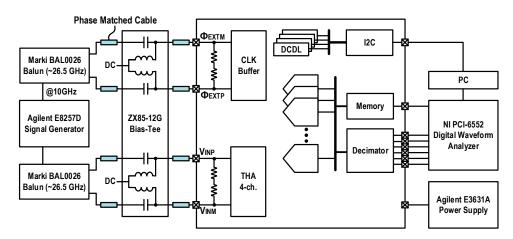

Figure 14 shows the measurement setup for the 20 GS/s TI ADC. The input voltage and clock signals via balun and bias-tee were applied to inside the chip differentially matched to 100 ohm. Note that the differential signals, such as the input or clock, were differentially matched by the matched cables. The decimated and serialized digital output codes were transferred to the digital waveform analyzer to measure the performance in real-time and to detect the inter-channel mismatch errors, such as the offset, gain, and time skew.

Figure 14. Measurement setup.

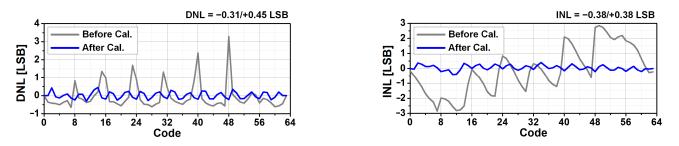

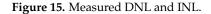

The measured differential non-linearity (DNL) and integral non-linearity (INL) profiles before and after the offset calibration for the coarse comparators and fine VTCs and the gain calibration for the four-channel THAs calibrated in the digital domain are shown in Figure 15. The peak DNL and INL improved from +3.28/-0.64 LSB and +2.84/-2.84 LSB to +0.45/-0.31 LSB and +0.38/-0.38 LSB, respectively.

Figure 16 shows the measured FFT spectra with a 0.828 GHz input at a sampling rate of 20 GS/s. The results are decimated by a factor of 459. The signal-to-noise ratio (SNR), spurious-free dynamic range (SFDR), and signal-to-noise and distortion ratio (SNDR) are improved from 14.46, 19.84, and 9.36 dB to 32.93, 42.75, and 32.58 dB, respectively, as shown in Figure 16a. The FFT spectrum without offset calibration shown in Figure 16a includes tones due to the offset mismatches between the interleaving channels as well as tones due to the offset mismatches for the comparators and VTCs used in the two-step flash ADC. Note that, since the offset mismatches for the comparators and VTCs were calibrated based on the same input common voltage used in the normal operation, the offset mismatches between the interleaving channels were also calibrated by the offset calibration process for the comparators and VTCs. Therefore, the noise floor as well as the interleaving offset tones could be improved by the offset calibration process for the comparators and VTCs. However, the gain mismatch tones between the interleaving channels still remain because of the gain mismatch between the THAs and the I-R drop of the reference voltage used by each C-DAC. These gain mismatch tones were calibrated in the digital domain based

on [28], and as a result, SNR, SFDR, and SNDR were improved to 34.02, 45.81, and 33.96 dB, respectively, as shown in Figure 16b.

**Figure 16.** Measured FFT spectra with a 0.828 GHz input at a 20 GS/s sampling rate. (**a**) With and without calibration for mismatches of comparators and VTCs. (**b**) With and without calibration for gain mismatch between the interleaving channels.

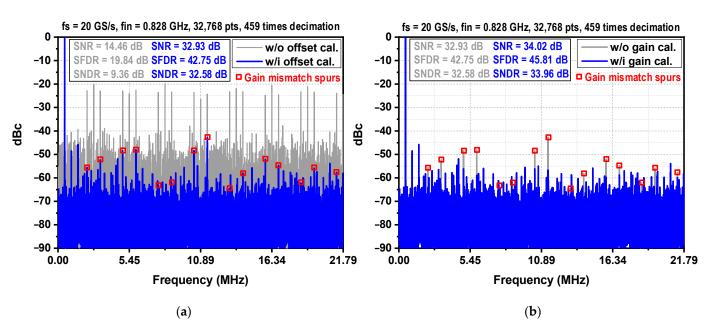

Figure 17 shows the FFT spectrum at a 9.042 GHz input. SNR, SFDR, and SNDR without skew calibration are 26.05, 30.62 and 25.69 dB, respectively, and limited by the timing skew error of approximately 950 fs, assuming only a timing skew error. As mentioned in Section 3.3.3, the timing skew error is detected off-chip, and then the sampling time is calibrated on-chip by the DCDL. The SNR, SFDR, and SNDR are improved to 31.02, 40.23, and 30.12 dB, respectively, through the skew calibration.

**Figure 17.** Measured FFT spectrum with and without skew calibration at 20 GS/s with a 9.085 GHz input.

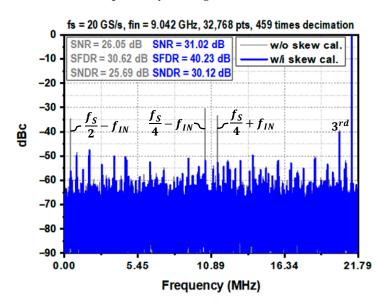

Figure 18a shows the measured dynamic performances (SNDR and SFDR) at various input frequencies with the 20 GS/s sampling frequency. Thanks to the compact input

network due to the low input capacitance implemented by the proposed S/H sharing and the eight-time interpolation, the proposed TI ADC could be designed with a high effective resolution bandwidth (ERBW) of approximately 8.5 GHz when the time skew is optimally calibrated, as shown in Figure 18a. Without the skew calibration, SNDR begins to be attenuated by the skew error above an approximately 3 GHz input frequency. Figure 18b shows the measured SNDR and SFDR with various sampling frequencies at a 0.828 GHz input frequency. It can be seen that the proposed TI ADC operates stably up to a conversion rate of 20.3 GS/s, but the performance is rapidly degraded at conversion rates higher than that.

**Figure 18.** Measured SNDR and SFDR versus various (**a**) input frequencies at 20 GS/s and (**b**) conversion rates with a 0.828 GHz input frequency.

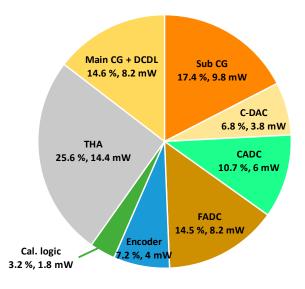

The ADC core operates at a 0.9 V single supply and consumes 56.2 mW at a sampling rate of 20 GS/s. Figure 19 shows the power breakdown. The portion of the 16-channel sub-ADCs including the C-DAC with R-string is 32%, and the clock logics, including the main clock generator, sub clock generator, and the DCDL, take 32%. The digital encoder and calibration logic take 7.2% and 3.2%, respectively. Thanks to the small input capacitance of the sub-ADCs, each THA consumes 3.6 mW, so the four-channel THAs consume 14.4 mW, which is 25.6% of the total power consumption.

Figure 19. Power breakdown.

In Table 2, the performance of the proposed TI ADC is summarized and compared with those of recently reported 6-8-bit TI ADCs with sampling frequencies above 20 GS/s. The proposed 16-channel TI two-step flash ADC is capable of high-speed operation at 20 GS/s with a single supply voltage of 0.9 V. The proposed TI ADC could be designed with a competitive area and power consumption thanks to the S/H sharing technique and the reference-embedded eight-time interpolation technique using the gain enhanced VTC. As a result, the calculated Walden figure-of-merit (FoM) at the Nyquist input is 107.4 fJ/conversion step.

Table 2. Performance comparison.

|                                          | This Work            | JSSC14<br>V. Chen<br>[8] | JSSC17<br>S. Cai<br>[20]  | VLSI16<br>Y. Frans<br>[2] | JSSC17<br>B. Xu<br>[30] | VLSI19<br>D. Pfaff<br>[3] | SSCL20<br>S-J Kim<br>[31] | VLSI21<br>M. Zhang<br>[32] |

|------------------------------------------|----------------------|--------------------------|---------------------------|---------------------------|-------------------------|---------------------------|---------------------------|----------------------------|

| Technology (nm)                          | 40                   | 32 SOI                   | 65                        | 16 FinFET                 | 28                      | 7 FinFET                  | 16 FinFET                 | 65                         |

| Architecture                             | TI Two-Step<br>Flash | TI Flash                 | TI<br>Multi-bit<br>Search | TI SAR                    | TI SAR-TDC              | TI SAR                    | TI<br>Flash-TDC           | TI Time-<br>domain         |

| # of channels                            | 16                   | 8                        | 8                         | 32                        | 16                      | 32                        | 16                        | 8                          |

| Supply (V)                               | 0.9                  | 0.9                      | 1.0                       | 0.9/1.2/1.8               | 0.85/0.95               | -                         | 0.9                       | 1.0/1.2                    |

| Resolution (bit)                         | 6                    | 6                        | 6                         | 8                         | 6                       | 8                         | 8                         | 8                          |

| $F_{S}$ (GS/s)                           | 20                   | 20                       | 25                        | 28                        | 24                      | 28                        | 20                        | 20                         |

| V <sub>IN</sub> (mVdiff)                 | 400                  | 300                      | 500                       | 1200 <sup>2</sup>         | ~240                    | -                         | 500                       | 450                        |

| DNL/INL <sub>MAX</sub> (LSB)             | 0.45/0.38            | 0.47/0.42                | 0.64/0.60                 | -                         | 0.25/0.22               | -                         | 0.95/2.39                 | -                          |

| SNDR <sub>@Nyq.</sub> (dB)               | 30.1                 | 30.7                     | 29.7                      | 31.5                      | 28.9                    | 29.4                      | 35.4                      | 38.8                       |

| SFDR <sub>@Nyq.</sub> (dB)               | 40.2                 | 39.4                     | 42                        | 39.1                      | 41                      | 39.1                      | -                         | 52.5                       |

| ENOB <sub>@Nyq.</sub> (bit)              | 4.71                 | 4.81                     | 4.62                      | 4.9                       | 4.51                    | 4.6                       | 5.6                       | 6.15                       |

| Power (mW)                               | 56.2                 | 69.5                     | 88                        | 280                       | 23                      | 150                       | 175                       | 129.9                      |

| Active area (mm <sup>2</sup> )           | 0.1                  | 0.25                     | 0.24                      | 2.8 <sup>3</sup>          | 0.03                    | 0.09 4                    | 0.1                       | 0.22                       |

| Walden FOM <sup>1</sup><br>(fJ/convstep) | 107.4                | 124.1                    | 143                       | 325.7                     | 42                      | 221                       | 180                       | 91.3                       |

|                                          |                      |                          | -                         |                           |                         |                           | 2                         |                            |

$^1$  Walden FoM = power/(2<sup>ENOB</sup> × sampling frequency).  $^2$  Tx swing range.  $^3$  Dual transceiver active area.  $^4$  Including AFE.

#### 5. Conclusions

This paper has presented a 40 nm CMOS 6-bit 20 GS/s 16-channel TI ADC using the two-step flash ADC with the S/H sharing and the reference-embedded eight-time interpolation techniques. The input bandwidth, area, and power efficiency of the single channel ADC could be improved by sharing a single S/H between the coarse and fine stages. The time gain of the VTC used in the eight-time time-domain interpolating FADC was boosted by the positive feedback loop, resulting in improving the linearity of the multibit interpolation. As a result of these, four-channel THAs consisting of the input network of the TI ADC could be implemented with a high speed and low power. In addition, the design burden of the multi-phase clock generation for the sub-ADCs could be alleviated by using the two-step flash structure. Thanks to these efforts, the prototype TI ADC operates at 20 GS/s with a single supply voltage as low as 0.9 V and consumes 56.2 mW. The effective number of bits (ENOB) at 0.828 GHz and 9.042 GHz inputs are 5.34 bit and 4.71 bit, respectively, and the Walden FoM at a 9.042 GHz input is 107.4 fJ/conversion step.

Funding: This research received no external funding.

Conflicts of Interest: The author declares no conflict of interest.

# Abbreviations

| ADC      | Analog-to-Digital Converter            |

|----------|----------------------------------------|

| TI       | Time-Interleaved                       |

| SAR      | Successive Approximation Register      |

| S/H      | Sample-and-Hold                        |

| C-DAC    | Capacitive Digital-to-Analog Converter |

| R-DAC    | Resistive Digital-to-Analog Converter  |

| R-string | Resistive string                       |

| THA      | Track-and-Hold Amplifier               |

|          |                                        |

| CADC | Coarse ADC                           |

|------|--------------------------------------|

| VTC  | Voltage-to-Time Converter            |

| FADC | Fine ADC                             |

| DFF  | D-type Flip Flop                     |

| DCDL | Digitally-Controlled Delay Line      |

| SF   | Source Follower                      |

| LVDS | Low Voltage Differential Signaling   |

| CG   | Clock Generator                      |

| DM   | Delay Matching                       |

| T/H  | Track-and-Hold                       |

| MSB  | Most Significant Bit                 |

| LSB  | Least Significant Bit                |

| TDI  | Time-Domain Interpolator             |

| TSPC | True Single Phase Clock              |

| DNL  | Differential Non-Linearity           |

| INL  | Integral Non-Linearity               |

| SNR  | Signal-to-Noise Ratio                |

| SFDR | Spurious-Free Dynamic Range          |

| SNDR | Signal-to-Noise and Distortion Ratio |

| ERBW | Effective Resolution Bandwidth       |

| FoM  | Figure of Merit                      |

| ENOB | Effective Number of Bits             |

|      |                                      |

#### References

- Kiran, S.; Cai, S.; Zhu, Y.; Hoyos, S.; Palermo, S. Digital Equalization with ADC-Based Receivers. *IEEE Microw. Mag.* 2019, 20, 62–79. [CrossRef]

- Frans, Y.; Elzeftawi, M.; Hedayati, H.; Im, J.; Kireev, V.; Pham, T.; Shin, J.; Upadhyaya, P.; Zhou, L.; Asuncion, S.; et al. A 56Gb/s PAM4 Wireline Transceiver using a 32-way Time-Interleaved SAR ADC in 16nm Fin FET. In Proceedings of the 2016 IEEE Symposium on VLSI Circuits (VLSI Circuits), Honolulu, HI, USA, 15–17 June 2016.

- Pfaff, D.; Moazzeni, S.; Gao, L.; Chuang, M.-C.; Wang, X.-J.; Palusa, C.; Abbott, R.; Ramirez, R.; Amer, M.; Huang, M.-C.; et al. A 56Gb/s Long Reach Fully Adaptive Wireline PAM-4 Transceiver in 7nm FinFET. In Proceedings of the 2019 IEEE Symposium on VLSI Circuits (VLSI Circuits), Kyoto, Japan, 9–14 June 2019.

- Pisati, M.; Bernardinis, F.D.; Pascale, P.; Nani, C.; Ghittori, N.; Pozzati, E.; Sosio, M.; Garampazzi, M.; Milani, A.; Minuti, A.; et al. A 243-mW 1.25-56-Gb/s Continuous Range PAM-4 42.5-dB IL ADC/DAC-Based Transceiver in 7-nm FinFET. *IEEE J. Solid State Circuits* 2020, 55, 6–18. [CrossRef]

- 5. Luan, J.; Zheng, X.; Wu, D.; Zhang, Y.; Wu, L.; Zhou, L.; Wu, J.; Liu, X. A 56 GS/s 8 Bit Time-Interleaved ADC in 28 nm CMOS. *Electronics* 2022, 11, 688. [CrossRef]

- 6. Jia, H.; Guo, X.; Zheng, X.; Xu, X.; Wu, D.; Zhou, L.; Wu, J.; Liu, X. A 4-bit 36 GS/s ADC with 18 GHz Analog Bandwidth in 40 nm CMOS Process. *Electronics* 2020, *9*, 1733. [CrossRef]

- Crivelli, D.; Hueda, M.; Carrer, H.; Zachan, J.; Gutnik, V.; Barco, M.D.; Lopez, R.; Hatcher, G.; Finochietto, J.; Yeo, M.; et al. A 40nm CMOS Single-Chip 50Gb/s DP-QPSK/BPSK Transceiver with Electronic Dispersion Compensation for Coherent Optical Channels. In Proceedings of the 2012 IEEE International Solid-State Circuits Conference (ISSCC), San Francisco, CA, USA, 19–23 February 2012.

- Chen, V.H.-C.; Pileggi, L. A 69.5 mW 20 GS/s 6b Time-Interleaved ADC With Embedded Time-to-Digital Calibration in 32 nm CMOS SOI. *IEEE J. Solid State Circuits* 2014, 49, 2891–2901. [CrossRef]

- Oh, D.-R.; Kim, J.-I.; Seo, M.-J.; Kim, J.-G.; Ryu, S.-T. A 6-bit 10-GS/s 63-mW 4x TI Time-Domain Interpolating Flash ADC in 65-nm CMOS. In Proceedings of the 2015 IEEE European Solid-State Circuits Conference (ESSCIRC), Graz, Austria, 14–18 September 2015.

- 10. Huang, C.-C.; Wang, C.-Y.; Wu, J.-T. A CMOS 6-Bit 16-GS/s Time-Interleaved ADC Using Digital Background Calibration Techniques. *IEEE J. Solid State Circuits* 2011, 46, 848–858. [CrossRef]

- Kull, L.; Pliva, J.; Toifl, T.; Schmatz, M.; Francese, P.A.; Menolfi, C.; Braendli, M.; Kossel, M.; Morf, T.; Andersen, T.M.; et al. A 110mW 6 bit 36 GS/s interleaved SAR ADC for 100 GBE occupying 0.048 mm<sup>2</sup> in 32 nm SOI CMOS. In Proceedings of the 2014 IEEE Asian Solid-State Circuits Conference (ASSCC), Kaohsiung, Taiwan, 10–12 November 2014.

- Tual, S.L.; Singh, P.N.; Curis, C.; Dautriche, P. A 20GHz-BW 6b 10GS/s 32mW Time-Interleaved SAR ADC with Master T&H in 28nm UTBB FDSOI Technology. In Proceedings of the 2014 IEEE International Solid-State Circuits Conference (ISSCC), San Francisco, CA, USA, 9–13 February 2014.

- 13. Tabasy, E.Z.; Shafik, A.; Lee, K.; Hoyos, S.; Palermo, S. A 6 bit 10 GS/s TI-SAR ADC With Low-Overhead Embedded FFE/DFE Equalization for Wireline Receiver Applications. *IEEE J. Solid State Circuits* **2014**, *49*, 2560–2574. [CrossRef]

- 14. Duan, Y.; Alon, E. A 6b 46GS/s ADC with >23GHz BW and Sparkle-Code Error Correction. In Proceedings of the 2015 IEEE Symposium on VLSI Circuits (VLSI Circuits), Kyoto, Japan, 17–19 June 2015.

- Figueiredo, P.M.; Cardoso, P.; Lopes, A.; Fachada, C.; Hamanishi, N.; Tanabe, K.; Vital, J. A 90nm CMOS 1.2V 6b 1GS/s Two-Step Subranging ADC. In Proceedings of the 2006 IEEE International Solid-State Circuits Conference (ISSCC), San Francisco, CA, USA, 6–9 February 2006.

- Plouchart, J.-O.; Sanduleanu, M.A.T.; Toprak-Deniz, Z.; Beukema, T.J.; Reynolds, S.; Parker, B.D.; Beakes, M.; Tierno, J.A.; Friedman, D. A 3.2GS/s 4.55b ENOB two-step subranging ADC in 45nm SOI CMOS. In Proceedings of the 2012 IEEE Custom Integrated Circuits Conference (CICC), San Jose, CA, USA, 9–12 September 2012.

- 17. Ohhata, K.; Takase, H.; Tateno, M.; Arita, M.; Imakake, N.; Yonemitsu, Y. A 1-GHz, 17.5-mW, 8-bit Subranging ADC Using Offset-Cancelling Charge-Steering Amplifier. In Proceedings of the 2012 IEEE Asian Solid-State Circuits Conference (ASSCC), Kobe, Japan, 12–14 November 2012.

- Yang, X.; Liu, J. A 10 GS/s 6 b Time-Interleaved Partially Active Flash ADC. *IEEE Trans. Circuits Syst. I* 2014, 61, 2272–2280. [CrossRef]

- Chung, Y.-H.; Wu, J.-T. A 16-mW 8-Bit 1-GS/s Digital-Subranging ADC in 55-nm CMOS. IEEE Trans. Very Large Scale Integr. (VLSI) Syst. 2015, 23, 557–566. [CrossRef]

- Cai, S.; Tabasy, E.Z.; Shafik, A.; Kiran, S.; Hoyos, S.; Palermo, S. A 25 GS/s 6b TI Two-Stage Multi-Bit Search ADC With Soft-Decision Selection Algorithm in 65 nm CMOS. *IEEE J. Solid State Circuits* 2017, 52, 2168–2179. [CrossRef]

- 21. Lee, H.; Asada, Y.; Miyahara, M.; Matsuzawa, A. A 6bit, 7mW, 700MS/s Subranging ADC Using CDAC and Gate-Weighted Interpolation. *IEEE Trans. Fundam.* 2013, *E96–A*, 422–433. [CrossRef]

- Oh, D.-R.; Seo, M.-J.; Ryu, S.-T. A 7-Bit Two-Step Flash ADC With Sample-and-Hold Sharing Technique. IEEE J. Solid State Circuits 2022, 57, 2791–2801. [CrossRef]

- Boni, A.; Pierazzi, A. Vecchi, D. LVDS I/O Interface for Gb/s-per-Pin Operation in 0.35-μm CMOS. *IEEE J. Solid State Circuits* 2001, 36, 706–711. [CrossRef]

- Lukas, K.; Pliva, J.; Toifl, T.; Schmatz, M.; Francese, P.A.; Menolfi, C.; Brändli, M.; Kossel, M.; Morf, T.; Andersen, T.M.; et al. Implementation of Low-Power 6–8 b 30–90 GS/s Time-Interleaved ADCs With Optimized Input Bandwidth in 32 nm CMOS. *IEEE J. Solid State Circuits* 2016, *51*, 636–648.

- 25. Kim, J.-I.; Sung, B.-R.-S.; Kim, W.; Ryu, S.-T. A 6-b 4.1-GS/s Flash ADC With Time-Domain Latch Interpolation in 90-nm CMOS. *IEEE J. Solid State Circuits* 2013, *48*, 1429–1441.

- Oh, D.-R.; Kim, J.-I.; Jo, D.-S.; Kim, W.-C.; Chang, D.-J.; Ryu, S.-T. A 65-nm CMOS 6-bit 2.5-GS/s 7.5-mW 8× Time-Domain Interpolating Flash ADC With Sequential Slope-Matching Offset Calibration. *IEEE J. Solid State Circuits* 2019, 54, 288–297. [CrossRef]

- Miyahara, M.; Mano, I.; Nakayama, M.; Okada, K.; Matsuzawa, A. A 2.2GS/s 7b 27.4mW Time-Based Folding-Flash ADC with Resistively Averaged Voltage-to-Time Amplifiers. In Proceedings of the 2014 IEEE International Solid-State Circuits Conference (ISSCC), San Francisco, CA, USA, 9–13 February 2014.

- 28. Razavi, B. Design Considerations for Interleaved ADCs. IEEE J. Solid State Circuits 2013, 48, 1806–1817. [CrossRef]

- Kull, L.; Luu, D.; Menolfi, C.; Brändli, M.; Francese, P.A.; Morf, T.; Kossel, M.; Cevrero, A.; Ozkaya, I.; Toifl, T. A 24–72-GS/s 8-b Time-Interleaved SAR ADC With 2.0–3.3-pJ/Conversion and >30 dB SNDR at Nyquist in 14-nm CMOS FinFET. *IEEE J. Solid State Circuits* 2018, 53, 3508–3516. [CrossRef]

- Xu, B.; Zhou, Y.; Chiu, Y. A 23-mW 24-GS/s 6-bit Voltage-Time Hybrid Time-Interleaved ADC in 28-nm CMOS. IEEE J. Solid State Circuits 2017, 52, 1091–1100. [CrossRef]

- 31. Kim, S.-J.; Myers, Z.; Herbst, S.; Lim, B.; Horowitz, M. 20-GS/s 8-bit Analog-to-Digital Converter and 5-GHz Phase Interpolator for Open-Source Synthesizable High-Speed Link Applications. *IEEE Solid-State Circuits Lett.* **2020**, *3*, 518–521. [CrossRef]

- Zhang, M.; Zhu, Y.; Chan, C.-H.; Martins, R.P. A 20GS/s 8b Time-Interleaved Time-Domain ADC with Input-Independent Background Timing Skew Calibration. In Proceedings of the 2021 IEEE Symposium on VLSI Circuits (VLSI Circuits), Kyoto, Japan, 13–19 June 2021.