# Article A Novel Switched-Capacitor Inverter with Reduced Capacitance and Balanced Neutral-Point Voltage

Zhuyu Xun 🗅, Hongfa Ding \* and Zhou He

Wuhan National High Magnetic Field Center, School of Electrical and Electronic Engineering, Huazhong University of Science and Technology, Wuhan 430074, China; xunzhuyu@outlook.com (Z.X.); he\_zhou@hust.edu.cn (Z.H.)

\* Correspondence: dhf@hust.edu.cn

**Abstract:** A novel three-phase switched-capacitor multilevel inverter (SCMLI) with reduced capacitance and balanced neutral-point voltage is proposed in this paper. Applying only one DC source, the three-phase seven-level topology possessing voltage-boosting capability is accomplished without the high-voltage stress of power switches. Owing to the inherent redundant switching states of the proposed topology, two charging approaches that can effectively limit the voltage ripples and path selection for capacitors can be realized. This provides the presented topology with reduced capacitance, balanced neutral-point voltage, good performance in not only the three-phase four-wire system but also the three-phase three-wire system, and low total harmonic distortion (THD) of the output voltage. A comprehensive comparison with previous SCMLIs in various aspects is conducted to validate the merits mentioned above. The simulation results accord with theoretical analyses, confirming the feasibility of the proposed three-phase SCMLI.

**Keywords:** multilevel inverter; switched-capacitor; reduced capacitance; neutral-point voltage imbalance

# 1. Introduction

Multilevel inverters are important circuit configurations in modern electrical power systems because of their many advantages, such as low total harmonic distortion (THD) of the output voltage, low voltage stress on power devices, and low electromagnetic interference (EMI). The main applications of these inverters include static compensators, high-voltage DC transmission systems, active power filters, and renewable energy systems that include variable-frequency motor drives [1–6]. Neutral-point-clamped (NPC) [7], flying-capacitor [8], and cascaded H-bridge [9] are three well-researched multilevel inverters. These inverters are widely used in practical and commercial applications. However, these inverters have shortcomings such as neutral-point voltage imbalance and the need for excessive isolated DC sources [10]. Owing to the inability to boost the input voltage. To overcome the drawbacks mentioned above, many new topologies have been introduced that offer more optimized component utilization, more voltage levels, higher efficiency, and so on [11,12].

Since the input voltage is relatively low compared with the output voltage, boost circuits [13,14] are required in many applications, such as grid-connected photovoltaic modules, distributed generation (DG) systems, and electric vehicles. Inductors or transformers are used in most boost circuits, making the systems bulky and heavy [15]. Therefore, a charge pump is typically adopted as a boost circuit [16]. In the charge pump, the output voltage is equal to the sum of the capacitor voltages and the input voltage. The capacitors in the charge pump are discharged when connected in series and charged when connected in parallel along with the DC source.

Inverters using the same working principle are called switched-capacitor multilevel inverters (SCMLI), which have become a recent research topic of interest [17,18]. Unlike

Citation: Xun, Z.; Ding, H.; He, Z. A Novel Switched-Capacitor Inverter with Reduced Capacitance and Balanced Neutral-Point Voltage. *Electronics* **2021**, *10*, 947. https:// doi.org/10.3390/electronics10080947

Academic Editors: João L. Afonso and Vítor Monteiro

Received: 14 March 2021 Accepted: 14 April 2021 Published: 16 April 2021

**Publisher's Note:** MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations.

**Copyright:** © 2021 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https:// creativecommons.org/licenses/by/ 4.0/). inductors or transformers, capacitors are used to boost the input voltage. Employing fewer isolated DC sources and related components, they can generate voltage levels. To boost the input voltage, capacitors need to be involved in the load current path. In most SCMLIs, all relevant capacitors are discharged at the top voltage level. In addition, the discharging state can last for a long time according to the modulation method. This time is called the longest discharging time (LDT). As a result, capacitors have difficulty maintaining their voltage, thus exceeding the maximum allowable value of the voltage ripples. This is a critical challenge for existing SCMLIs.

Several methods have been used to solve this problem, but the most adopted method is to increase the capacitance. By employing only one DC source in a three-phase topology, a boost seven-level switched-capacitor inverter was proposed in [19]. The voltage stress of all power switches did not exceed the input voltage, and the capacitance used was 4700 µF. This method increased the volume and cost of the system [20,21]. Another method involves increasing the frequency of the output voltage. A family of SCMLI topologies for highfrequency AC applications was proposed in [22]. This approach can generate more voltage levels with an optimal component count. The main applications of this method have been limited to high-frequency AC systems [23,24]. A third method involves decreasing the maximum allowable modulation index. A novel seven-level inverter for medium-voltage high-power applications was presented in [25], and the maximum allowable modulation index was 0.813. This method reduces the boosting ability of SCMLIs [26]. A fourth method involves reducing the load. A boost single-phase switched-capacitor inverter was presented in [27]. With fewer power switches, this SCMLI could generate nine voltage levels under a resistive load condition (200  $\Omega$ ). However, this method limits the power that SCMLIs can supply when the output voltage is the same [28,29].

Another problem for several SCMLIs that adopt a DC-link converter is the neutralpoint voltage imbalance [30–33]. The self-balancing characteristic of these SCMLIs selfregulates the average neutral-point voltage to a certain value (usually half the DC-link voltage). The self-balancing time is long, and the neutral-point voltage may drift excessively. In addition, a three-phase three-wire system can worsen this problem in most traditional three-phase SCMLIs. Additional hardware or software measures are necessary to solve this problem. Regarding software measures, many studies have been carried out based on NPC topology. However, there is little research on this problem in SCMLIs. Hardware measures, such as adding additional components, increase the volume and cost of the system.

Generally, the abovementioned topologies have various disadvantages. To overcome these shortcomings, a novel three-phase SCMLI is presented in this paper. The main advantages of the proposed topology are as follows:

- (1) Less capacitance  $(200 \ \mu F)$  is used.

- (2) There is no problem of neutral-point voltage imbalance.

- (3) Good performance is achieved in not only a three-phase four-wire system but also a three-phase three-wire system.

- (4) Only one DC source is used as a three-phase topology.

- (5) All floating capacitors are used to generate the top voltage level.

This paper is organized as follows: the topology of the proposed SCMLI and the operating principle are fully outlined in Section 2. Theoretical analyses of the two charging approaches are provided in Section 3. Control strategies are presented in Section 4. The voltage ripples of the capacitors are carefully analyzed in Section 5. The overall system efficiency is calculated in Section 6. Simulation results and a comprehensive comparison are presented in Section 7. Lastly, a conclusion is drawn in Section 8.

## 2. Proposed SCMLI and Operating Principle

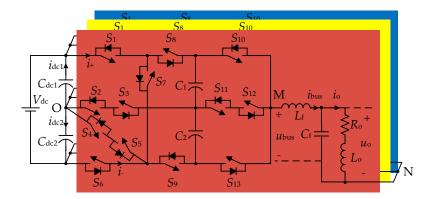

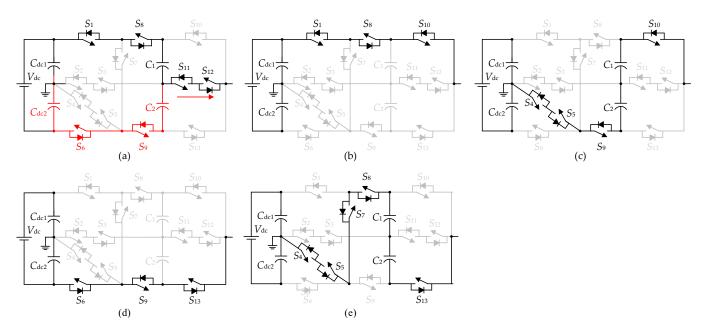

The proposed three-phase SCMLI topology is shown in Figure 1. Employing one DC source and eight capacitors, it can generate seven voltage levels (0 V, 0.5 V<sub>dc</sub>, V<sub>dc</sub>, 1.5 V<sub>dc</sub>,  $-0.5 V_{dc}$ ,  $-V_{dc}$ ,  $-1.5 V_{dc}$ ) under different kinds of load conditions. The capacitors' rated voltage is  $U_N = 0.5 V_{dc}$ . Bidirectional switches are used to block positive and negative

voltage stress. The floating capacitors  $C_{1,2}$  are used to generate the top voltage level. They can also balance the voltages of the DC-link capacitors  $C_{dc1,2}$  when needed. Furthermore, the proposed topology is used in a three-phase four-wire system when O and N are connected and is used in a three-phase three-wire system when O and N are not connected.

Figure 1. Proposed seven-level three-phase SCMLI topology.

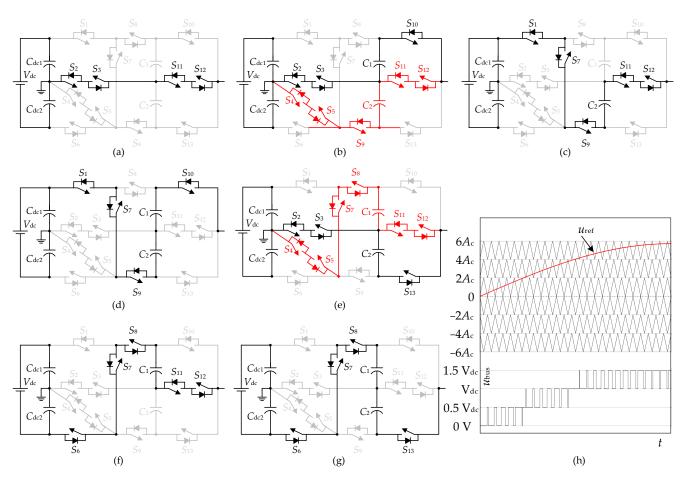

All switching states of the proposed three-phase SCMLI are listed in Table 1. Main switching states are depicted in Figure 2a–g. Other switching states are fully discussed in Sections 3 and 4. To generate 0 V,  $S_2$ ,  $S_3$ ,  $S_{11}$ , and  $S_{12}$  need to be ON, as shown in Figure 2a. In Figure 2b,e, the black and red devices represent two different paths. Both  $C_1$  and  $C_2$  can be used to generate not only 0.5 V<sub>dc</sub> but also -0.5 V<sub>dc</sub>. Selecting the right path can make  $u_{C1}$  approach  $u_{C2}$ . In Figure 2c,f, the capacitors  $C_{dc1}$ ,  $C_2$  and  $C_{dc2}$ ,  $C_1$  are used to generate V<sub>dc</sub> and  $-V_{dc}$ , respectively. To generate 1.5 V<sub>dc</sub>,  $S_1$ ,  $S_7$ ,  $S_9$ , and  $S_{10}$  need to be ON, as shown in Figure 2d. Similarly, to generate -1.5 V<sub>dc</sub>,  $S_6$ ,  $S_7$ ,  $S_8$ , and  $S_{13}$  need to be ON, as shown in Figure 2g. For multilevel inverters, there are several modulation strategies. In this paper, the phase opposition disposition PWM is adopted, which is shown in Figure 2h.

| STATES - | Voltage                         | Figure<br>Position | Switches              |                       |       |       |       |       |       |       |    |                 |                        |                 |                 |

|----------|---------------------------------|--------------------|-----------------------|-----------------------|-------|-------|-------|-------|-------|-------|----|-----------------|------------------------|-----------------|-----------------|

|          | Level                           |                    | <i>S</i> <sub>1</sub> | <i>S</i> <sub>2</sub> | $S_3$ | $S_4$ | $S_5$ | $S_6$ | $S_7$ | $S_8$ | S9 | S <sub>10</sub> | <i>S</i> <sub>11</sub> | S <sub>12</sub> | S <sub>13</sub> |

| 1        | 1.5 V <sub>dc</sub>             | Figure 2           | 1                     | 0                     | 0     | 0     | 0     | 0     | 1     | 0     | 1  | 1               | 0                      | 0               | 0               |

| 2        | V <sub>dc</sub>                 | Figure 2           | 1                     | 0                     | 0     | 0     | 0     | 0     | 1     | 0     | 1  | 0               | 1                      | 1               | 0               |

| 3        | $V_{dc}$                        | Figure 5           | 0                     | 0                     | 0     | 1     | 1     | 0     | 0     | 0     | 1  | 1               | 0                      | 0               | 0               |

| 4        | $0.5  \mathrm{V}_{\mathrm{dc}}$ | Figure 4           | 1                     | 0                     | 0     | 0     | 0     | 1     | 0     | 1     | 1  | 1               | 0                      | 0               | 0               |

| 5        | $0.5 V_{dc}$                    | Figure 4           | 0                     | 1                     | 1     | 0     | 0     | 1     | 0     | 0     | 1  | 1               | 0                      | 0               | 0               |

| 6        | $0.5 V_{dc}$                    | Figure 4           | 1                     | 1                     | 1     | 0     | 0     | 0     | 0     | 1     | 0  | 1               | 0                      | 0               | 0               |

| 7        | $0.5 V_{dc}$                    | Figure 5           | 1                     | 0                     | 0     | 0     | 0     | 0     | 0     | 1     | 0  | 1               | 0                      | 0               | 0               |

| 8        | $0.5 V_{dc}$                    | Figure 2           | 0                     | 1                     | 1     | 0     | 0     | 0     | 0     | 0     | 0  | 1               | 0                      | 0               | 0               |

| 9        | 0.5 V <sub>dc</sub>             | Figure 2           | 0                     | 0                     | 0     | 1     | 1     | 0     | 0     | 0     | 1  | 0               | 1                      | 1               | 0               |

| 10       | 0 V                             | Figure 4           | 1                     | 0                     | 0     | 0     | 0     | 1     | 0     | 1     | 1  | 0               | 1                      | 1               | 0               |

| 11       | 0 V                             | Figure 4           | 0                     | 1                     | 1     | 0     | 0     | 1     | 0     | 0     | 1  | 0               | 1                      | 1               | 0               |

| 12       | 0 V                             | Figure 4           | 1                     | 1                     | 1     | 0     | 0     | 0     | 0     | 1     | 0  | 0               | 1                      | 1               | 0               |

| 13       | 0 V                             | Figure 5           | 1                     | 0                     | 0     | 0     | 0     | 0     | 0     | 1     | 0  | 0               | 1                      | 1               | 0               |

| 14       | 0 V                             | Figure 5           | 0                     | 0                     | 0     | 0     | 0     | 1     | 0     | 0     | 1  | 0               | 1                      | 1               | 0               |

| 15       | 0 V                             | Figure 2           | 0                     | 1                     | 1     | 0     | 0     | 0     | 0     | 0     | 0  | 0               | 1                      | 1               | 0               |

| 16       | $-0.5 V_{dc}$                   | Figure 4           | 1                     | 0                     | 0     | 0     | 0     | 1     | 0     | 1     | 1  | 0               | 0                      | 0               | 1               |

| 17       | $-0.5 V_{dc}$                   | Figure 4           | 0                     | 1                     | 1     | 0     | 0     | 1     | 0     | 0     | 1  | 0               | 0                      | 0               | 1               |

| 18       | $-0.5 V_{dc}$                   | Figure 4           | 1                     | 1                     | 1     | 0     | 0     | 0     | 0     | 1     | 0  | 0               | 0                      | 0               | 1               |

| 19       | $-0.5 V_{dc}$                   | Figure 5           | 0                     | 0                     | 0     | 0     | 0     | 1     | 0     | 0     | 1  | 0               | 0                      | 0               | 1               |

| 20       | $-0.5 V_{dc}$                   | Figure 2           | 0                     | 1                     | 1     | 0     | 0     | 0     | 0     | 0     | 0  | 0               | 0                      | 0               | 1               |

| 21       | $-0.5 V_{dc}$                   | Figure 2           | 0                     | 0                     | 0     | 1     | 1     | 0     | 1     | 1     | 0  | 0               | 1                      | 1               | 0               |

| 22       | $-V_{dc}$                       | Figure 2           | 0                     | 0                     | 0     | 0     | 0     | 1     | 1     | 1     | 0  | 0               | 1                      | 1               | 0               |

| 23       | $-V_{dc}$                       | Figure 5           | 0                     | 0                     | 0     | 1     | 1     | 0     | 1     | 1     | 0  | 0               | 0                      | 0               | 1               |

| 24       | $-1.5 \mathrm{V}_{\mathrm{dc}}$ | Figure 2           | 0                     | 0                     | 0     | 0     | 0     | 1     | 1     | 1     | 0  | 0               | 0                      | 0               | 1               |

Table 1. All switching states of the proposed three-phase SCMLI.

**Figure 2.** Main switching states of the proposed three-phase SCMLI at (**a**) 0 V, (**b**) 0.5 V<sub>dc</sub>, (**c**) V<sub>dc</sub>, (**d**) 1.5 V<sub>dc</sub>, (**e**) -0.5 V<sub>dc</sub>, (**f**)  $-V_{dc}$ , and (**g**) -1.5 V<sub>dc</sub>. (**h**) The waveform of the phase opposition disposition PWM in the positive quarter cycle (switching frequency  $f_s = 5$  kHz).

# 3. Capacitor Charging Approaches

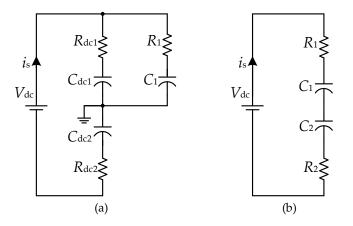

Two significant approaches are used in this paper to charge capacitors. Approach I that is first proposed in this paper plays an important role in balancing capacitors voltages and makes it possible for the proposed topology to solve the problem of neutral-point voltage imbalance. Approach II is a widely adopted approach that can charge the capacitors together. The equivalent circuits of approach I and approach II are shown in Figure 3a,b, respectively.  $R_{dc1}$ ,  $R_{dc2}$ ,  $R_1$ , and  $R_2$  are the equivalent resistances of the devices.

Figure 3. Equivalent circuit of (a) approach I and (b) approach II.

#### 3.1. Approach I

All of the DC-link capacitors  $C_{dc1,2}$  and one of the floating capacitors  $C_{1,2}$  were used to realize approach I in this paper. The circuit mode with  $C_1$ ,  $C_{dc1}$  and  $C_{dc2}$  in Figure 3a is taken as an example to illustrate approach I. The approximation that  $C_{dc1} = C_{dc2} = C_1 = C_0$ and  $R_{dc1} = R_{dc2} = R_1 = R_0$  is introduced to simplify the analysis. The following analysis is based on this approximation. According to the topology, the equivalent capacitance  $C_{eq}$ and the equivalent resistance  $R_{eq}$  can be expressed as follows:

$$C_{eq} = \frac{(C_{dc1} + C_1)C_{dc2}}{C_{dc1} + C_1 + C_{dc2}} = \frac{2}{3}C_0$$

$$R_{eq} = \frac{R_{dc1}R_1}{R_{dc1} + R_1} + R_{dc2} = \frac{3}{2}R_0$$

(1)

Therefore, the current that flows through the DC source is given by

$$i_{\rm s} = \frac{V_{\rm dc} - u_{\rm eq}(0)}{R_{\rm eq}} e^{-\frac{t}{R_{\rm eq}C_{\rm eq}}},$$

(2)

where

$$u_{\rm eq}(0) = \frac{u_{\rm Cdc1}(0) + u_{\rm C1}(0)}{2} + u_{\rm Cdc2}(0).$$

(3)

The voltage of capacitor  $C_{dc2}$  can be expressed as

$$u_{\rm Cdc2} = u_{\rm Cdc2}(0) + \frac{1}{C_{\rm dc2}} \int_{0}^{t} i_{\rm s} dt = \frac{2}{3} [V_{\rm dc} - u_{\rm eq}(0)] (1 - e^{-\frac{t}{R_0 C_0}}) + u_{\rm Cdc2}(0).$$

(4)

The voltage of capacitor  $C_{dc1}$  satisfies the following differential equation:

$$u_{\rm Cdc1} + R_{\rm dc1}C_{\rm dc1}\frac{du_{\rm Cdc1}}{dt} = V_{\rm dc} - u_{\rm Cdc2} - i_{\rm s}R_{\rm dc2} = \frac{V_{\rm dc} + u_{\rm Cdc1}(0) - u_{\rm Cdc2}(0) + u_{\rm C1}(0)}{3}.$$

(5)

According to Equation (5),  $C_{dc1}$  initial voltage is  $u_{Cdc1}(0)$  and final voltage is  $(V_{dc} + u_{Cdc1}(0) - u_{Cdc2}(0) + u_{C1}(0))/3$ . According to the full response theory of the first order circuit,  $u_{Cdc1}$  can be expressed as

$$u_{\rm Cdc1} = u_{\rm Cdc1}(0)e^{-\frac{t}{R_0C_0}} + \frac{V_{\rm dc} + u_{\rm Cdc1}(0) - u_{\rm Cdc2}(0) + u_{\rm C1}(0)}{3}(1 - e^{-\frac{t}{R_0C_0}}).$$

(6)

Similarly,  $u_{C1}$  can be expressed as

$$u_{\rm C1} = u_{\rm C1}(0)e^{-\frac{t}{R_0C_0}} + \frac{V_{\rm dc} + u_{\rm Cdc1}(0) - u_{\rm Cdc2}(0) + u_{\rm C1}(0)}{3}(1 - e^{-\frac{t}{R_0C_0}}).$$

(7)

When  $u_{Cdc1}(0) > 0.5 V_{dc} > u_{Cdc2}(0)$  and  $u_{C1}(0) < 0.5 V_{dc}$ , capacitors  $C_1$  and  $C_{dc2}$  will be charged, and capacitor  $C_{dc1}$  will be discharged according to Equations (4), (6) and (7). When  $u_{Cdc1}(0) < 0.5 V_{dc} < u_{Cdc2}(0)$  and  $u_{C1}(0) > 0.5 V_{dc}$ , capacitors  $C_1$  and  $C_{dc2}$  will be discharged, and capacitor  $C_{dc1}$  will be charged similarly. If approach I is adopted, all relevant capacitor voltages will move toward 0.5 V<sub>dc</sub>. Furthermore, these voltages will reach 0.5 V<sub>dc</sub> if  $u_{Cdc1}(0) - u_{Cdc2}(0) + u_{C1}(0) = 0.5 V_{dc}$ . As shown in Figure 4a,  $S_1$ ,  $S_8$ ,  $S_2$ , and  $S_3$  are ON.  $C_1$  and  $C_{dc1}$  are connected in parallel, and approach I is realized. To generate 0 V at the same time,  $S_{11}$  and  $S_{12}$  should be ON. Moreover, 0.5 V<sub>dc</sub> and  $-0.5 V_{dc}$  can be generated when  $S_{10}$  and  $S_{13}$  are ON, respectively. As shown in Figure 4b,  $S_2$ ,  $S_3$ ,  $S_6$ , and  $S_9$ are ON.  $C_2$  and  $C_{dc2}$  are connected in parallel, and approach I is realized. Similarly, 0 V, 0.5 V<sub>dc</sub>, and  $-0.5 V_{dc}$  can be generated at the same time.

**Figure 4.** Switching states when (**a**) approach I is realized and  $C_1$  is used, (**b**) approach I is realized and  $C_2$  is used, and (**c**) approach II is realized.

## 3.2. Approach II

Approach II, which is used to balance the floating capacitor voltages, is shown in Figure 3b. Similarly, it is assumed that  $C_1 = C_2 = C_0$  and  $R_1 = R_2 = R_0$ . According to the topology,  $R_{eq} = 2R_0$  and  $C_{eq} = 0.5C_0$ . Therefore,  $i_s$  is given by

$$i_{\rm s} = \frac{V_{\rm dc} - u_{\rm eq}(0)}{R_{\rm eq}} e^{-\frac{t}{R_{\rm eq}C_{\rm eq}}},$$

(8)

where  $u_{eq}(0) = u_{C1}(0) + u_{C2}(0)$ .  $u_{C1}$  can be calculated as follows:

$$u_{\rm C1} = u_{\rm C1}(0) + \frac{1}{C_1} \int_0^t i_{\rm s} dt = \frac{1}{2} [V_{\rm dc} - u_{\rm eq}(0)] (1 - e^{-\frac{t}{R_0 C_0}}) + u_{\rm C1}(0).$$

(9)

Similarly,  $u_{C2}$  can be expressed as follows:

$$u_{\rm C2} = \frac{1}{2} [V_{\rm dc} - u_{\rm eq}(0)] (1 - e^{-\frac{t}{R_0 C_0}}) + u_{\rm C2}(0).$$

(10)

After applying approach II, the average  $u_{C1}$  and  $u_{C2}$  reach 0.5  $V_{dc}$ , according to Equations (9) and (10). Moreover,  $u_{C1}$  and  $u_{C2}$  will reach 0.5  $V_{dc}$  if  $u_{C1}(0) = u_{C2}(0)$ . Approach II can be realized when  $S_1$ ,  $S_8$ ,  $S_6$ , and  $S_9$  are ON, as shown in Figure 4c. Any one of 0 V, 0.5  $V_{dc}$ , and  $-0.5 V_{dc}$  can be generated at the same time. These two charging approaches can be realized, which is an important feature of the proposed three-phase SCMLI.

## 4. Control Strategies to Limit Voltage Ripples

To limit voltage ripples, the control strategies of the capacitor voltages are listed in Table 2. For capacitors  $C_1$  and  $C_2$ , the control strategies can be divided into two aspects. The first aspect involves using approach II and making the average of  $u_{C1}$  and  $u_{C2}$  return to 0.5 V<sub>dc</sub>. Approach II is taken when  $|0.5(u_{C1} + u_{C2}) - 0.5 V_{dc}| > u_{\gamma}$ .  $u_{\gamma}$  is an adjustable parameter. The second aspect involves selecting the right path and making  $u_{C1}$  approach  $u_{C2}$ . The path selection for  $C_{1,2}$  is used if  $|0.5(u_{C1} + u_{C2}) - 0.5 V_{dc}| < u_{\gamma}$ .

Table 2. Control strategies of the capacitor voltages.

| Capacitors                      | Control Strategy            |  |  |  |

|---------------------------------|-----------------------------|--|--|--|

| $C_1$ and $C_2$                 | Approach II, path selection |  |  |  |

| $C_{\rm dc1}$ and $C_{\rm dc2}$ | Approach I, path selection  |  |  |  |

Similarly, for capacitors  $C_{dc1}$  and  $C_{dc2}$ , the control strategies can be divided into two aspects. The first aspect involves using approach I and making  $u_{Cdc1}$  and  $u_{Cdc2}$  move toward 0.5 V<sub>dc</sub>. Approach I is taken when  $|u_{Cdc1} - u_{Cdc2}| > u_{\alpha}$ .  $u_{\alpha}$  is also an adjustable parameter. The second aspect involves selecting the right path and making  $u_{Cdc1}$  approach

$u_{Cdc2}$ . As  $u_{Cdc1} + u_{Cdc2} = V_{dc}$ ,  $u_{Cdc1}$  and  $u_{Cdc2}$  return to 0.5  $V_{dc}$  when  $u_{Cdc1}$  reaches  $u_{Cdc2}$ . The path selection for  $C_{dc1,2}$  is used if  $|u_{Cdc1} - u_{Cdc2}| < u_{\alpha}$ .

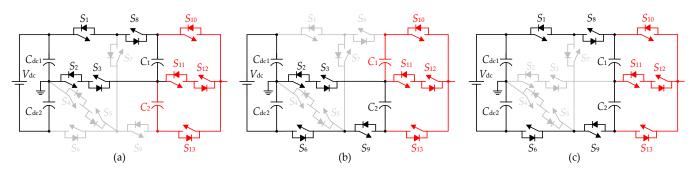

There are more paths for selection in the proposed topology, and the redundant switching states are depicted in Figure 5a–e. With respect to Figure 5a, the black and red devices represent two different paths.  $S_1$ ,  $S_8$ ,  $S_{11}$ , and  $S_{12}$  are ON, and the capacitors  $C_{dc1}$  and  $C_1$  are used to generate 0 V. Similarly,  $S_6$ ,  $S_9$ ,  $S_{11}$ , and  $S_{12}$  are ON, and capacitors  $C_{dc2}$  and  $C_2$  are used to generate 0 V. Moreover, 0.5 V<sub>dc</sub> is generated when  $S_1$ ,  $S_8$ , and  $S_{10}$  are ON, as shown in Figure 5b, whereas  $-0.5 V_{dc}$  is generated when  $S_6$ ,  $S_9$ , and  $S_{13}$  are ON, as shown in Figure 5c,e, capacitors  $C_1$  and  $C_2$  can be used to generate not only V<sub>dc</sub> but also level  $-V_{dc}$ . For capacitors in the proposed topology, path selection is an important control strategy. As shown in Figures 2 and 5, there are various paths for selection at several voltage levels, and the capacitors used are different, making it easier to balance the capacitor voltages. This is one of the main advantages of the proposed topology.

**Figure 5.** Redundant switching states of the proposed three-phase SCMLI structure at (**a**) 0 V, (**b**) 0.5 V<sub>dc</sub>, (**c**) V<sub>dc</sub>, (**d**) -0.5 V<sub>dc</sub>, and (**e**)  $-V_{dc}$ .

Usually, there is a conflict between the control strategies of  $u_{C1,2}$  and the control strategies of  $u_{Cdc1,2}$ . It is important to make a comprehensive decision according to the latest status. In this paper, the top priority is to decide whether to take approach II.  $|0.5(u_{C1} + u_{C2}) - 0.5 V_{dc}| > u_{\gamma}$ , and this is the criterion that  $u_{C1}$  and  $u_{C2}$  have to meet if approach II is to be taken. After that, approach I is taken when  $|u_{Cdc1} - u_{Cdc2}| > u_{\alpha}$ . This will make  $u_{Cdc1}$  and  $u_{Cdc2}$  move toward 0.5  $V_{dc}$ . Then, the path selection for  $C_{dc1,2}$  is used if  $|u_{Cdc1} - u_{Cdc2}| > u_{\beta}$ .  $u_{\alpha}$  is larger than  $u_{\beta}$ . Lastly, the path selection for  $C_{1,2}$  is used.

The reasons for there being no problem of neutral-point voltage imbalance for the proposed three-phase SCMLI can be divided into two aspects. On the one hand, approach I is adopted in this paper. This approach is an effective measure to balance the capacitor voltages. On the other hand, there are various paths for selection at several voltage levels. These two aspects complement each other, giving the proposed topology the ability to solve the problem of neutral-point voltage imbalance.

## 5. Capacitance Determination

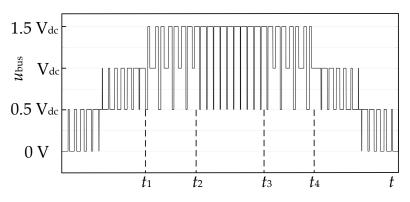

Approach II can be used at 0 V, 0.5 V<sub>dc</sub>, and -0.5 V<sub>dc</sub>. Thus, capacitors C<sub>1</sub> and C<sub>2</sub> are discharged when  $u_{ref} > V_{dc}$  and  $i_{bus} > 0$  in the positive half cycle. To address this problem, an important change to the original modulation method is made in this paper, and the new modulation wave in the positive half cycle is shown in Figure 6.

**Figure 6.** The new modulation wave in the positive half cycle (switching frequency  $f_s = 5$  kHz).

According to the original modulation method, there are two choices in a switching period when  $u_{ref} > V_{dc}$ . These choices are  $u_{bus} = V_{dc}$  and  $u_{bus} = 1.5 V_{dc}$ . In this paper, this condition is expressed as  $u_{bus} \in \{V_{dc}, 1.5 V_{dc}\}$ .  $u_{bus} \in \{0.5 V_{dc}, 1.5 V_{dc}\}$  is added when  $t_1 \le t \le t_4$  because the abovementioned control strategies can be realized at 0.5 V<sub>dc</sub>. Specifically,  $u_{bus} \in \{0.5 V_{dc}, 1.5 V_{dc}\}$  is used in half of the switching periods when  $t_1 \le t \le t_2$  or  $t_3 \le t \le t_4$ .  $u_{bus} \in \{0.5 V_{dc}, 1.5 V_{dc}\}$  is used in all the switching periods when  $t_2 \le t \le t_3$ .

The longest discharging time of floating capacitors is an important SCMLI parameter because the required capacitance can be calculated according to it. The longest discharging time  $t_{ldt}$  of floating capacitors in the proposed three-phase SCMLI can be expressed as

$$_{\rm ldt} = 2T_{\rm s} - t_{\rm c},\tag{11}$$

where  $T_s$  is the switching period, and  $t_c$  is the minimum duration of 0.5 V<sub>dc</sub> when  $t_1 \le t \le t_2$ or  $t_3 \le t \le t_4$ . According to Equation (11), the longest discharging time of floating capacitors in the proposed topology is smaller than  $2T_s$ , which is much shorter than that in other traditional SCMLIs. During the longest discharging time, the current that flows through floating capacitors is  $i_{bus}$ . The voltage variation of floating capacitors that comes from  $i_{bus}$ can be calculated as follows:

$$\frac{\int_{t_{\text{start}}}^{t_{\text{end}}} i_{\text{bus}} dt}{C_{1,2}} \approx \frac{2T_{\text{s}} - t_{\text{c}}}{C_{1,2}} i_{\text{bus}}|_{t=t_{\text{start}}} < \frac{2T_{\text{s}}}{C_{1,2}} \frac{mA_{\text{boost}}V_{\text{dc}}}{|Z_{\text{MN}}|},$$

(12)

where *m* is the modulation index, and  $A_{\text{boost}}$  is the voltage gain.  $t_{\text{start}}$  and  $t_{\text{end}}$  are the start time and end time of the longest discharging time, respectively.  $Z_{\text{MN}}$  is the total impedance between point M and point N. Considering that approach I is adopted, Equation (12) needs to satisfy

$$\frac{2T_{\rm s}}{C_{1,2}} \frac{mA_{\rm boost}V_{\rm dc}}{|Z_{\rm MN}|} < 0.5u_{\alpha}.$$

(13)

According to Equation (13), the required capacitance of floating capacitors can be calculated as follows:

$$C_{1,2} > \frac{4T_{\rm s}}{u_{\alpha}} \frac{mA_{\rm boost}V_{\rm dc}}{|Z_{\rm MN}|}.$$

(14)

According to Equations (11)–(14), reducing the longest discharging time of the floating capacitors can effectively reduce the capacitance of the floating capacitors.

Approach I, which can make  $u_{Cdc1}$  and  $u_{Cdc2}$  move toward 0.5 V<sub>dc</sub>, is taken if  $|u_{Cdc1} - u_{Cdc2}| > u_{\alpha}$ . Thus,  $u_{Cdc1}$  and  $u_{Cdc2}$  can be limited to 0.5 V<sub>dc</sub>  $\pm$  0.5  $u_{\alpha}$  with less DC-link capacitance. Similarly, the voltage variation of the DC-link capacitors between

$t_{\text{begin}}$  (the end time of the first approach I) and  $t_{\text{finish}}$  (the start time of the second approach I) can be calculated as follows:

$$\frac{\int_{t_{\text{begin}}}^{t_{\text{Imush}}} i_{\text{Cdc1}}dt}{C_{\text{dc1},2}} \approx \frac{kT_{\text{s}}}{C_{\text{dc1},2}} i_{\text{Cdc1}}|_{t=t_{\text{begin}}} < \frac{kT_{\text{s}}}{2C_{\text{dc1},2}} \frac{mA_{\text{boost}}V_{\text{dc}}}{|Z_{\text{MN}}|},$$

(15)

where  $kT_s = t_{\text{finish}} - t_{\text{begin}}$ . To coincide with approach I, Equation (15) needs to satisfy

$$\frac{kT_{\rm s}}{2C_{\rm dc1,2}} \frac{mA_{\rm boost}V_{\rm dc}}{|Z_{\rm MN}|} < 0.5u_{\alpha}.$$

(16)

According to Equation (16), the required capacitance of the DC-link capacitors can be calculated as follows:

$$C_{\rm dc1,2} > \frac{kT_{\rm s}}{u_{\alpha}} \frac{mA_{\rm boost}V_{\rm dc}}{|Z_{\rm MN}|}.$$

(17)

According to Equations (14) and (17), the required capacitance of the floating capacitors is similar to that of the DC-link capacitors. Therefore,  $C_{1,2} = C_{dc12}$  in this paper.

## 6. Efficiency Calculation

In this section, the overall efficiency of the proposed three-phase SCMLI is calculated. First, the conduction loss of the power switches  $P_{con1}$  can be expressed as

$$P_{\rm con1} = f_{\rm o} \sum_{i=1}^{N_{\rm swi}} \int_{0}^{T_{\rm o}} (i_{\rm si}^2 r_{\rm si} + i_{\rm si} V_{\rm si}) dt,$$

(18)

where  $i_{si}$ ,  $r_{si}$ , and  $V_{si}$  are the current, internal resistance, and voltage drop of the *i*-th switch, respectively.  $N_{swi}$  is the number of power switches.  $T_o$  and  $f_o$  are the period and frequency of the output voltage, respectively. The conduction loss  $P_{con2}$  that comes from the DC-link capacitors and the floating capacitors can be calculated as follows:

$$P_{\rm con2} = f_{\rm o} \sum_{i=1}^{N_{\rm ca}} \int_{0}^{T_{\rm o}} i_{\rm Ci}^2 r_{\rm Ci} dt,$$

(19)

where  $i_{\text{Ci}}$  and  $r_{\text{Ci}}$  are the current and the internal resistance of the *i*-th capacitor, respectively.  $N_{\text{ca}}$  is the number of capacitors. The conduction loss of the output filters  $P_{\text{con3}}$  can be calculated as follows:

$$P_{\rm con3} = f_0 \sum_{i=1}^{N_{\rm fil}} \int_0^{I_0} (i_{\rm Lfi}^2 r_{\rm Lfi} + i_{\rm Cfi}^2 r_{\rm Cfi}) dt,$$

(20)

where  $i_{\text{Lfi}}$  and  $r_{\text{Lfi}}$  are the current and the internal resistance of the *i*-th filter inductor, respectively.  $i_{\text{Cfi}}$  and  $r_{\text{Cfi}}$  are the current and the internal resistance of the *i*-th filter capacitor, respectively.  $N_{\text{fil}}$  is the number of filters.

To simplify the analysis, the voltage and the current of the power switches are considered to have a linear relation with time during the switching process. Therefore, the switching loss  $P_{off(i,j)}$  that is caused by the *j*-th turning OFF process of the *i*-th switch is given by

$$P_{\rm off(i,j)} = f_{\rm o} \int_{0}^{t_{\rm off}} v(t)i(t)dt = f_{\rm o} \int_{0}^{t_{\rm off}} \frac{V_{\rm off(i,j)}}{t_{\rm off}} t [-\frac{I_{\rm off(i,j)}}{t_{\rm off}}(t-t_{\rm off})]dt = \frac{1}{6} V_{\rm off(i,j)} I_{\rm off(i,j)} t_{\rm off} f_{\rm o},$$

(21)

$$P_{\rm on(i,j)} = \frac{1}{6} V_{\rm on(i,j)} I_{\rm on(i,j)} t_{\rm on} f_{\rm o},$$

(22)

where  $V_{\text{on}(i,j)}$  and  $I_{\text{on}(i,j)}$  are the voltage before the turning ON process and the current after the turning ON process, respectively. According to Equations (21) and (22), the total switching loss  $P_{\text{sw}}$  can be calculated by

$$P_{\rm sw} = \sum_{i=1}^{N_{\rm swi}} \left( \sum_{j=1}^{N_{\rm on(i)}} P_{\rm on(i,j)} + \sum_{j=1}^{N_{\rm off(i)}} P_{\rm off(i,j)} \right) = \frac{1}{6} f_0 \sum_{i=1}^{N_{\rm swi}} \left( t_{\rm on} \sum_{j=1}^{N_{\rm on(i)}} V_{\rm on(i,j)} I_{\rm on(i,j)} + t_{\rm off} \sum_{j=1}^{N_{\rm off(i)}} V_{\rm off(i,j)} I_{\rm off(i,j)} \right),$$

(23)

where  $N_{\text{on(i)}}$  and  $N_{\text{off(i)}}$  are the number of *i*-th switch turning ON processes and turning OFF processes, respectively.

According to Equations (18)–(20), and (23), the overall efficiency of the proposed topology is given by

$$= \frac{P_{\rm o}}{P_{\rm o} + P_{\rm con1} + P_{\rm con2} + P_{\rm con3} + P_{\rm sw}}.$$

(24)

## 7. Simulation Results and Comparison

η

#### 7.1. Simulation Results

MATLAB/Simulink was chosen as the simulation software. The parameters of the proposed three-phase SCMLI are listed in Table 3. The input voltage was set as 200 V, which resembles many other SCMLIs. Thus, the rated voltage of the capacitors was 100 V. The modulation ratio was 0.95, and the output voltage was 285 (300 × 0.95) V. The capacitance used was 200  $\mu$ F, which meets the requirement of Equation (15). The output power was 1884 W, and the resistive–inductive load  $Z_1$  was 40  $\Omega$ , 100 mH.  $u_{\alpha}$  was 8 V since the maximum allowable voltage ripple of capacitors was 10 V (10% of the rated voltage). The filter capacitor was 80  $\mu$ F, and the filter inductor was 4 mH. The switching frequency was 20 kHz. This frequency can reduce the requirement of capacitance according to Equation (15). The output frequency was 50 Hz.

Table 3. Parameters of the proposed three-phase SCMLI.

| Parameters                       | Value        |  |  |

|----------------------------------|--------------|--|--|

| V <sub>dc</sub>                  | 200 V        |  |  |

| Capacitor rated voltage          | 100 V        |  |  |

| Modulation ratio                 | 0.95         |  |  |

| Output voltage                   | 285 V        |  |  |

| $C_1, C_2, C_{dc1}, and C_{dc2}$ | 200 µF       |  |  |

| Output power                     | 1884 W       |  |  |

| Resistive–inductive load $Z_1$   | 40 Ω, 100 mH |  |  |

| $u_{\alpha}$                     | 8 V          |  |  |

| Filter capacitor                 | 80 µF        |  |  |

| Filter inductor                  | 4 mH         |  |  |

| Switching frequency              | 20 kHz       |  |  |

| Output frequency                 | 50 Hz        |  |  |

#### 7.1.1. Performance in Three-Phase Four-Wire System

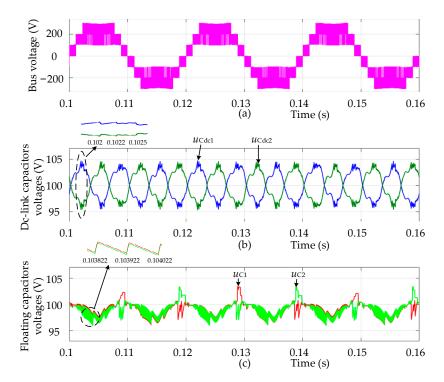

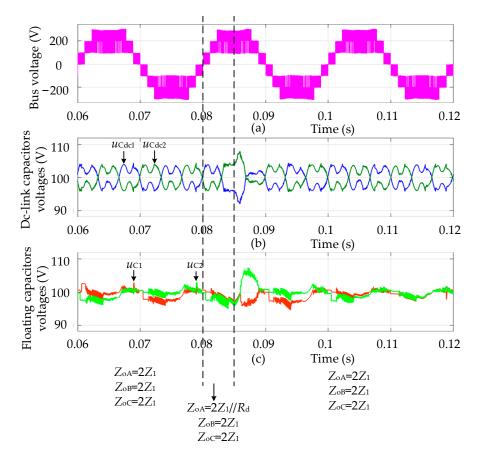

To assess the performance of the proposed three-phase SCMLI in the three-phase four-wire system,  $Z_0 = Z_1$  is given. Figure 7a shows the observed A-phase bus voltage. The top voltage level was 300 V, and the proposed three-phase SCMLI could boost the input voltage. Because  $u_{\alpha}$  was equal to 8 V, the voltages of the DC-link capacitors in the A-phase were limited to 96–104 V, as shown in Figure 7b. Approach I could move the voltage of DC-link capacitors toward 100 V when they were larger than 104 V or smaller than 96 V.

Figure 7c shows the floating capacitor voltages in the A-phase, which were approximately 96–103 V. It can be seen in this figure that the longest discharging time of floating capacitors was shorter than  $2T_s$ . These waveforms meet the voltage ripple requirement, which should be less than 10% of the rated voltage.

**Figure 7.** (**a**) The bus voltage, (**b**) DC-link capacitor voltages and (**c**) floating capacitor voltages of the A-phase under the resistive–inductive load condition.

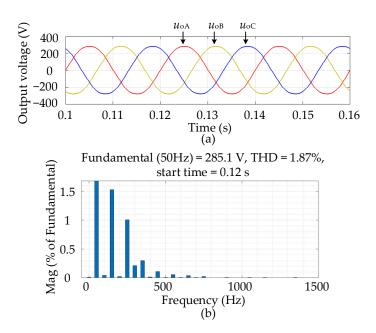

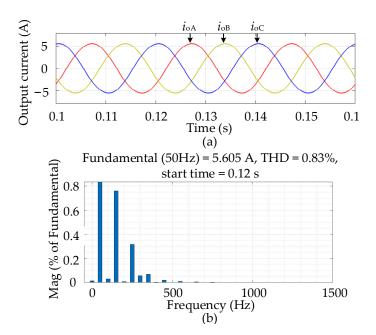

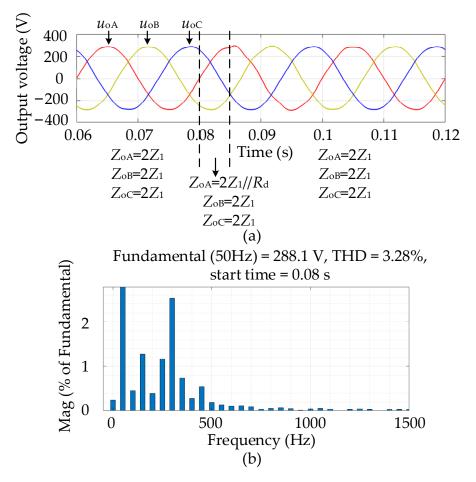

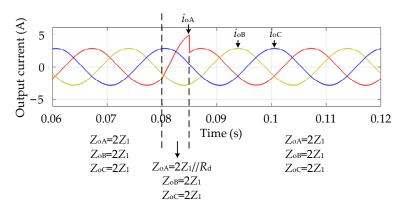

The output voltage of each phase under the resistive–inductive load condition is shown in Figure 8a, and the fast Fourier transform (FFT) result of the A-phase output voltage is shown in Figure 8b. According to the result, THD = 1.87%, and the amplitude of the fundamental component was 285.1 V. This amplitude agrees with the modulation ratio because the desired amplitude of the output voltage was 285 V. Similarly, the output current of each phase under the resistive–inductive load condition is shown in Figure 9a, and the FFT result of the A-phase output current is shown in Figure 9b. THD = 0.83%, and the amplitude of the fundamental component was 5.605 A. The quality of all the waveforms was high, which is attributable to the low-voltage ripples of the capacitors.

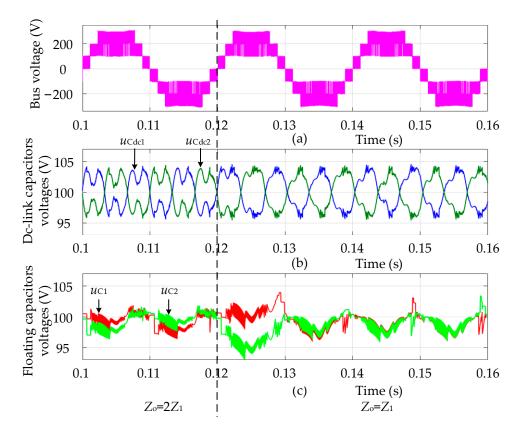

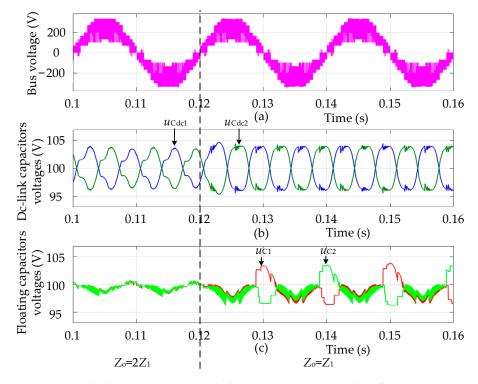

To further test the performance of the proposed three-phase SCMLI, a resistiveinductive load transient is given. The time when the load changed from  $Z_0 = 2Z_1$  to  $Z_0 = Z_1$  was 0.12 s. The bus voltage of the A-phase is shown in Figure 10a. The difference between the waveform before 0.12 s and the waveform after 0.12 s was not notable. Figure 10b shows the A-phase DC-link capacitor voltages. The voltage ripple of these capacitors was 8 V during the entire process ( $u_{\alpha} = 8$  V). Figure 10c shows the A-phase floating capacitor voltages. The transient process only lasted for a short period of time (approximately 0.01 s). After that, the floating capacitor voltages quickly returned to the steady state. These waveforms also meet the voltage ripple requirements and are in good agreement with the abovementioned theoretical analysis.

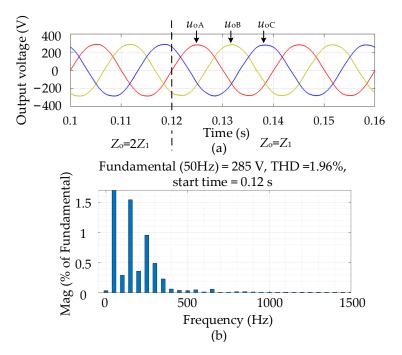

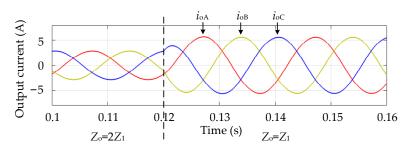

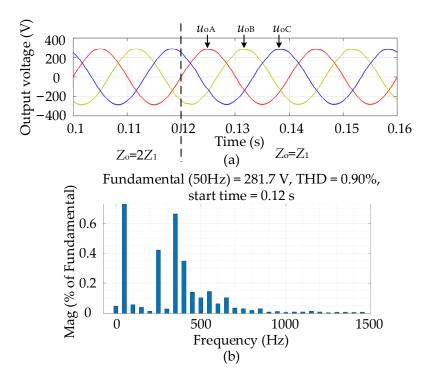

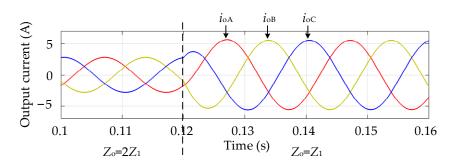

The output voltage of each phase during a resistive–inductive load transient is shown in Figure 11a, and the FFT result of the A-phase output voltage is shown in Figure 11b. THD = 1.96%, and the start time was 0.12 s. There was no significant change in the output voltage of each phase after 0.12 s. The output current of each phase under the same resistive–inductive load transient is shown in Figure 12. Similarly, the transient process only lasted for a short period of time. The output current of each phase quickly changed

from the initial steady state to a new steady state. Thus, there is no need to worry about the overvoltage problem or the overcurrent problem.

**Figure 8.** (a) The output voltage of each phase under the resistive–inductive load condition. (b) The FFT result of the A-phase output voltage.

**Figure 9.** (**a**) The output current of each phase under the resistive–inductive load condition. (**b**) The FFT result of the A-phase output current.

To test the presented three-phase SCMLI more rigorously, a special load with a temporary three-phase unbalanced disturbance is given. For each phase,  $Z_0 = 2Z_1$ . A disturbance load  $R_d = 100 \Omega$  was only added to the A-phase when 0.8 s < t < 0.85 s. Under this condition, Figure 13a shows the A-phase bus voltage, and there was no obvious change in the waveform when 0.8 s < t < 0.85 s or t > 0.85 s. Figure 13b shows the A-phase DC-link capacitor voltages. Similarly, the transient process only lasted for a short period of time (approximately 0.01 s). During this transient process,  $u_{Cdc2}$  was momentarily larger than 104 V, and  $u_{Cdc1}$  was momentarily smaller than 96 V. After that, the DC-link capacitor volt-

ages were limited to 96–104 V, as before. Figure 13c shows the A-phase floating capacitor voltages. During the same transient process,  $u_{C2}$  was momentarily larger than 105 V. After that, the floating capacitor voltages quickly returned to the steady state.

**Figure 10.** (**a**) The bus voltage, (**b**) DC-link capacitor voltages and (**c**) floating capacitor voltages of the A-phase during a resistive–inductive load transient.

**Figure 11.** (**a**) The output voltage of each phase during a resistive–inductive load transient. (**b**) The FFT result of the A-phase output voltage.

Figure 12. The output current of each phase during a resistive-inductive load transient.

**Figure 13.** (**a**) The bus voltage, (**b**) DC-link capacitor voltages and (**c**) floating capacitor voltages of the A-phase when the disturbance load was added to the A-phase.

When the disturbance load was added to the A-phase, the output voltage of each phase was as shown in Figure 14a, and the FFT result of the A-phase output voltage was as shown in Figure 14b. THD = 3.28%, and the start time was 0.08 s. The change in the output voltage of each phase during the transient process was small.

When the disturbance load was added to the A-phase, the output current of each phase was as shown in Figure 15. The amplitude of the A-phase output current  $i_{oA}$  increased because of the disturbance load when 0.8 s < t < 0.85 s. After that (t > 0.85 s), the A-phase output current  $i_{oA}$  quickly returned to the steady state. As for  $i_{oB}$  and  $i_{oC}$ , the disturbance load had no effect because it was only added to the A-phase.

All these observed waveforms in the three-phase four-wire system are in good agreement with the theoretical analyses, confirming the feasibility of the proposed three-phase SCMLI in the three-phase four-wire system.

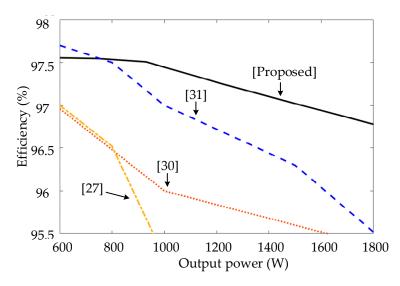

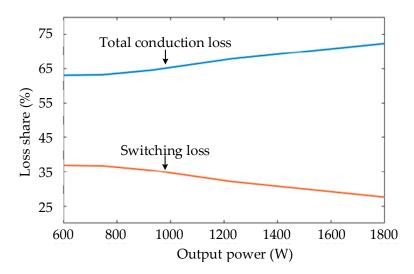

The recorded efficiency of different topologies is shown in Figure 16. The efficiency decreased with increasing output power. Compared with [27,30], the proposed topology

has greater efficiency. The efficiency of the proposed topology is similar to that of [31]. As shown in Figure 17, the share of total conduction loss was larger than that of switching loss. This is because the switching frequency was at a normal level. Furthermore, the share of switching loss increased with decreasing output power. Therefore, decreasing the switching frequency can be adopted to improve the efficiency of the proposed topology when the output power is lower than 800 W.

**Figure 14.** (**a**) The output voltage of each phase when the disturbance load was added to the A-phase. (**b**) The FFT result of the A-phase output voltage.

Figure 15. The output current of each phase when the disturbance load was added to the A-phase.

Figure 16. Recorded efficiency of different topologies.

Figure 17. The share of switching loss and total conduction loss.

#### 7.1.2. Performance in Three-Phase Three-Wire System

To test the performance of the proposed three-phase SCMLI in a three-phase threewire system, the same resistive–inductive load transient is given. The A-phase bus voltage is shown in Figure 18a. Because  $u_{\rm NO}$  was not always equal to 0, the bus voltage had more voltage levels. The resistive–inductive load transient had no effect on the bus voltage. Figure 18b shows the DC-link capacitor voltages of the A-phase. The voltage ripple of these capacitors was 10 V. Figure 18c shows the floating capacitor voltages of the A-phase. They changed from 98–101 V to 96–104 V. All these waveforms met the voltage ripple requirements during the entire process.

The output voltage of each phase during a resistive–inductive load transient is shown in Figure 19a, and the FFT result of the A-phase output voltage is shown in Figure 19b. THD = 0.90%, and the start time was 0.12 s. Even in the first period after 0.12 s, the waveform quality of each phase output voltage satisfied the requirement. The output current of each phase under the same resistive–inductive load transient is shown in Figure 20. The transient process only lasted for a short period of time. The output current of each phase quickly changed from the initial steady state to a new steady state.

The problem of neutral-point voltage imbalance became more serious for traditional SCMLIs in the three-phase three-wire system. In contrast, these observed waveforms were in line with expectations, confirming that the proposed three-phase SCMLI achieves good

performance in a three-phase three-wire system and there is no problem of neutral-point voltage imbalance.

**Figure 18.** (a) The bus voltage, (b) DC-link capacitor voltages and (c) floating capacitor voltages of the A-phase during a resistive–inductive load transient.

**Figure 19.** (**a**) The output voltage of each phase during a resistive–inductive load transient. (**b**) The FFT result of the A-phase output voltage.

Figure 20. The output current of each phase during a resistive-inductive load transient.

#### 7.2. Comparison

To better illustrate the advantages of the proposed topology, a comprehensive comparison with other up-to-date SCMLIs in various aspects is shown in Table 4. The main advantages of the proposed topology are as follows:

(1) Less capacitance (200  $\mu$ F) is used.

Proposed [19] [20] [27] [30] [33] [26] [31] [32] Topology 4700 1000 4700 200  $C_{\text{DC-link}}$ 4700 4700 1000 200 6800 4330 2200 4700 1000 2200 200  $C_{\text{floating}}$ 6800 4320 2200 1000 4700 4700 1000 /2200 200 3300 2190 2200  $N_{ca_{3p}}$ 8 9 9 6 9 6 5 5 8 TRV<sub>ca\_3p</sub> 4 15 15 3 6 3 4 4 4  $\varepsilon_{ca}$ 100% 100% 80% 100% 50% 100% 100% 100% 100%  $N_{\text{DC}_{3p}}$ 3 3 3 3 1 3 1 1 1  $40 \Omega$  $50 \Omega$ 42.2 Ω 30 Ω  $10 \Omega$  $40 \Omega$  $40 \Omega$ Load condition 200 Ω  $160 \Omega$ 100 mH 30 mH 79 mH 30 mH 100 mH 100 mH 100 mH т 1.00.9 0.91 1.0 1.0 1.0 1.0 1.0 0.95 Suffering from yes no no yes yes yes yes yes no imbalance 1.5 1.5 1.5 2 2 2 1.5 6 4 Aboost 7 13 9 9 9 9 7 7 7  $N_{\text{level}}$ 10 9 9 13  $N_{\rm sd}$ 15 12 11 11 10 33 TSV<sub>sw</sub> 9 24 12 10 11 8 8 11

Table 4. Comparison of different topology results.

$C_{\text{DC-link}}$  is the DC-link capacitance ( $\mu$ F).  $C_{\text{floating}}$  is the floating capacitance ( $\mu$ F).  $N_{\text{ca_3p}}$  is the number of capacitors in the three-phase applications.  $TRV_{\text{ca_3p}}$  is the total rated voltage of capacitors (Vdc) in the three-phase applications.  $\varepsilon_{\text{ca}}$  is the share of the floating capacitors voltages that are used to generate the top voltage level.  $N_{\text{DC_3p}}$  is the number of DC sources in the three-phase applications.  $N_{\text{level}}$  is the number of voltage levels.  $N_{\text{sd}}$  is the number of power switches and diodes in each phase.  $TSV_{\text{sw}}$  is the total standing voltage of switches ( $V_{\text{dc}}$ ) in each phase.

In most SCMLIs, the required capacitance is usually greater than 2000  $\mu$ F, thus increasing the volume and cost of the system. The capacitance used in [27,32] was 1000  $\mu$ F, but the load impedance (>150  $\Omega$ ) was much larger than that of other SCMLIs. The required capacitance increases with decreasing load impedance. The cost of capacitors increases with higher rated voltage, making the advantage of reduced capacitance in the proposed topology more obvious.

#### (2) There is no problem of neutral-point voltage imbalance.

The DC-link converter brings the problem of neutral-point voltage imbalance to [19,27,30–33]. The self-balancing characteristic of these SCMLIs self-regulates the average neutral point voltage to a certain value (usually half the DC-link voltage). However, the self-balancing time is long, and the neutral-point voltage may drift excessively. Additional hardware or software measures need to be taken to solve this problem. Regarding software

measures, there is little research about this problem in SCMLIs. Hardware measures, such as adding additional components to the system, increase the volume and cost of the system.

(3) Good performance is achieved in not only the three-phase four-wire system but also the three-phase three-wire system.

Most traditional three-phase SCMLIs [19,32,33] suffer from the problem of neutralpoint voltage imbalance, which becomes more serious in the three-phase three-wire system. Owing to the advantage above, the proposed topology can be adopted in more applications.

(4) Only one DC source is used as a three-phase topology.

The methods used in [20,26,27,30,31] all represent single-phase topologies. In the threephase applications, three DC sources are required for such topologies. This advantage of the proposed topology reduces the complexity and cost of the system.

(5) All floating capacitors are used to generate the top voltage level.

Not all floating capacitors were used to generate the top voltage level in [26,30]. The voltages of these floating capacitors are underused. This advantage of the proposed topology reduces the demand for capacitors.

Furthermore, the proposed topology is simple. Thirteen power switches are used in each phase, and the sum of their voltage stresses is only  $11 V_{dc}$ , which reaches the average level of other SCMLIs. Two DC-link capacitors and two floating capacitors in each phase are used, and the sum of their rated voltages is  $4 V_{dc}$ , which is not larger than that of the other three-phase SCMLIs. The proposed topology can generate seven voltage levels under different kinds of load conditions.

#### 8. Conclusions

A novel three-phase SCMLI with reduced capacitance and balanced neutral-point voltage was proposed in this paper. Good performance was achieved in not only the three-phase four-wire system but also the three-phase three-wire system. Only one DC source was used in the three-phase topology. A comprehensive comparison with other recently presented SCMLIs in various aspects was made, and simulation results under different kinds of load conditions were given. All observed waveforms were in good agreement with the theoretical analyses, confirming the feasibility of the proposed three-phase SCMLI.

Author Contributions: Conceptualization, Z.X.; methodology, Z.X.; software, Z.X.; validation, Z.X. and Z.H.; formal analysis, Z.X.; investigation, Z.X.; resources, Z.X.; data curation, Z.X.; writing—original draft preparation, Z.X. and Z.H.; writing—review and editing, Z.X. and Z.H.; visualization, Z.X.; supervision, H.D.; project administration, H.D.; funding acquisition, H.D. All authors have read and agreed to the published version of the manuscript.

**Funding:** This research was funded by the National Key Research and Development Program of China, Grant number 2016YFA0401702. This research was also funded by the National Natural Science Foundation of China, Grant number 51821005.

Conflicts of Interest: The authors declare no conflict of interest.

## Nomenclature

$R_{dc1}$ ,  $R_{dc2}$ ,  $R_1$  and  $R_2$

$R_0$  and  $C_0$  $R_{eq}$  and  $C_{eq}$

$i_s$

$u_{\rm N}$   $V_{\rm dc}$   $f_{\rm s}$  and  $T_{\rm s}$   $A_{\rm c}$   $u_{\rm ref}$  $u_{\rm bus}$

| Rated voltage of capacitors.                                                                         |

|------------------------------------------------------------------------------------------------------|

| Input DC voltage.                                                                                    |

| Switching frequency and switching period.                                                            |

| Amplitude of the carrier waveform.                                                                   |

| Reference voltage.                                                                                   |

| Bus voltage.                                                                                         |

| Equivalent resistance of the devices.                                                                |

| It is assumed that $R_{dc1} = R_{dc2} = R_1 = R_2 = R_0$ and $C_{dc1} = C_{dc2} = C_1 = C_2 = C_0$ . |

| Equivalent resistance and equivalent capacitance of the charging topology.                           |

| Current that flows through the DC source in the charging topology.                                   |

| $u_{\mathrm{Cd1}}, u_{\mathrm{Cd2}}, u_{\mathrm{C1}}, u_{\mathrm{C2}}$       | Voltage of capacitors.                                                                                                                                           |

|------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| $i_{Cd1}, i_{Cd2}, i_{C1}, i_{C2}$                                           | Current of capacitors.                                                                                                                                           |

| $u_{\text{Cdc1}}(0), u_{\text{Cdc2}}(0), u_{\text{C1}}(0), u_{\text{C2}}(0)$ | Initial voltage of capacitors.                                                                                                                                   |

| $u_{\rm eq}(0)$                                                              | Initial voltage of the equivalent capacitor.                                                                                                                     |

| $u_{\alpha}, u_{\beta}, u_{\gamma}$                                          | Adjustable parameters that represent the requirements of selecting the appropriate control strategy.                                                             |

| i <sub>bus</sub>                                                             | Bus current that flows through the filter inductor.                                                                                                              |

| t <sub>ldt</sub>                                                             | The longest discharging time of floating capacitors.                                                                                                             |

| tc                                                                           | Minimum duration of 0.5 V <sub>dc</sub> voltage level.                                                                                                           |

| m                                                                            | Modulation index.                                                                                                                                                |

| A <sub>boost</sub>                                                           | Voltage gain.                                                                                                                                                    |

| $t_{\text{start}}$ and $t_{\text{end}}$                                      | Start time and end time of the longest discharging time.                                                                                                         |

| Z <sub>MN</sub>                                                              | Total impedance between point M and point N (can be calculated by the filter parameter and the load condition).                                                  |

| $t_{\text{begin}}$ and $t_{\text{finish}}$                                   | End time of the first approach I and Start time of the next approach I.                                                                                          |

| k                                                                            | A parameter that satisfies the equation $kT_s = t_{\text{finish}} - t_{\text{begin}}$ .                                                                          |

| P <sub>con1</sub>                                                            | Conduction loss of the power switches.                                                                                                                           |

| $i_{\rm si}$ , $r_{\rm si}$ , and $V_{\rm si}$                               | Current, internal resistance and voltage drop of the <i>i</i> th switch.                                                                                         |

| N <sub>swi</sub>                                                             | Number of power switches.                                                                                                                                        |

| $f_{o}$ and $T_{o}$                                                          | Frequency and period of the output voltage.                                                                                                                      |

| P <sub>con2</sub>                                                            | Conduction loss that comes from DC-link and floating capacitors.                                                                                                 |

| $i_{\rm Ci}$ and $r_{\rm Ci}$                                                | Current and internal resistance of the <i>i</i> th capacitor.                                                                                                    |

| N <sub>cap</sub>                                                             | Number of capacitors.                                                                                                                                            |

| P <sub>con3</sub>                                                            | Conduction loss of the output filters.                                                                                                                           |

| $i_{\rm Lfi}$ and $r_{\rm Lfi}$                                              | Current and internal resistance of the <i>i</i> -th filter inductor.                                                                                             |

| $i_{\rm Cfi}$ and $r_{\rm Cfi}$                                              | Current and internal resistance of the <i>i</i> -th filter capacitor.                                                                                            |

| N <sub>fil</sub>                                                             | Number of filters.                                                                                                                                               |

| P <sub>off(i,j)</sub>                                                        | Switching loss caused by the <i>j</i> -th turning OFF process of the <i>i</i> -th switch.                                                                        |

| $V_{\rm off(i,j)}$ and $I_{\rm off(i,j)}$                                    | Voltage after the <i>j</i> -th turning OFF process of the <i>i</i> -th switch and current before the <i>j</i> -th turning OFF process of the <i>i</i> -th switch |

| P <sub>on(i,j)</sub>                                                         | Switching loss caused by the <i>j</i> -th turning ON process of the <i>i</i> -th switch.                                                                         |

| $V_{\text{on}(i,j)}$ and $I_{\text{on}(i,j)}$                                | Voltage before the <i>j</i> -th turning ON process of the <i>i</i> -th switch and current after the <i>j</i> -th turning ON process of the <i>i</i> -th switch.  |

| P <sub>sw</sub>                                                              | Total switching loss.                                                                                                                                            |

| N <sub>on(i)</sub> and N <sub>off(i)</sub>                                   | Number of <i>i</i> -th switch turning ON processes and turning OFF processes.                                                                                    |

| η                                                                            | Overall efficiency of the proposed topology.                                                                                                                     |

| Po                                                                           | Output power.                                                                                                                                                    |

| Zo                                                                           | Load impedance.                                                                                                                                                  |

| Z <sub>1</sub>                                                               | Load condition that is adopted in this paper.                                                                                                                    |

| R <sub>d</sub>                                                               | A disturbance load that is only added to the A-phase temporarily.                                                                                                |

# References

- Xiao, Q.; Chen, L.; Jin, Y.; Mu, Y.; Cupertino, A.F.; Jia, H.; Neyshabouri, Y.; Dragicevic, T.; Teodorescu, R. An Improved Fault-Tolerant Control Scheme for Cascaded H-Bridge STATCOM with Higher Attainable Balanced Line-to-Line Voltages. *IEEE Trans. Ind. Electron.* 2021, *68*, 2784–2797. [CrossRef]

- 2. Mathew, E.C.; Sharma, R.; Das, A. A Modular Resonant DC-DC Converter with High Step-Down Ratio for Tapping Power From HVDC Systems. *IEEE Trans. Ind. Electron.* **2021**, *68*, 324–332. [CrossRef]

- 3. Franquelo, L.G.; Rodriguez, J.; Leon, J.I.; Kouro, S.; Portillo, R.; Prats, M.M. The Age of Multilevel Converters Arrives. *IEEE Ind. Electron. Mag.* **2008**, *2*, 28–39. [CrossRef]

- 4. Dong, Z.; Wang, C.; Cui, K.; Cheng, Q.; Wang, J. Neutral-Point Voltage-Balancing Strategies of NPC-Inverter Fed Dual Three-Phase AC Motors. *IEEE Trans. Power Electron.* 2021, *36*, 3181–3191. [CrossRef]

- 5. Reddy, B.P.; Meraj, M.; Iqbal, A.; Keerthipati, S.; Bhaskar, M.S. A Hybrid Multilevel Inverter Scheme for Nine-Phase PPMIM Drive by Using Three-Phase Five-Leg Inverters. *IEEE Trans. Ind. Electron.* **2021**, *68*, 1895–1904. [CrossRef]

- 6. Riad, N.; Anis, W.; Elkassas, A.; Hassan, A.E.-W. Three-Phase Multilevel Inverter Using Selective Harmonic Elimination with Marine Predator Algorithm. *Electronics* **2021**, *10*, 374. [CrossRef]

- Nabae, A.; Takahashi, I.; Akagi, H. A New Neutral-Point-Clamped PWM Inverter. *IEEE Trans. Ind. Appl.* 1981, *IA*-17, 518–523. [CrossRef]

- Meynard, T.A.; Foch, H. Multi-level conversion: High voltage choppers and voltage-source inverters. In Proceedings of the PESC 92 Record, 23rd Annual IEEE Power Electronics Specialists Conference, Toledo, Spain, 29 June–3 July 1992.

- Hammond, P.W. A new approach to enhance power quality for medium voltage AC drives. *IEEE Trans. Ind. Appl.* 1997, 33, 202–208. [CrossRef]

- Cervone, A.; Brando, G.; Dordevic, O. Hybrid Modulation Technique with DC-Bus Voltage Control for Multiphase NPC Converters. *IEEE Trans. Power Electron.* 2020, 35, 13528–13539. [CrossRef]

- Zhang, L.; Lou, X.T.; Li, C.S.; Wu, F.; Gu, Y.F.; Chen, G.; Xu, D.W. Evaluation of Different Si/SiC Hybrid Three-Level Active NPC Inverters for High Power Density. *IEEE Trans. Power Electron.* 2020, *35*, 8224–8236. [CrossRef]

- 12. Akagi, H. Multilevel Converters: Fundamental Circuits and Systems. Proc. IEEE 2017, 105, 2048–2065. [CrossRef]

- Mayer, R.; Kattel, M.B.E.; Oliveira, S.V.G. Multiphase Interleaved Bidirectional DC/DC Converter with Coupled Inductor for Electrified-Vehicle Applications. *IEEE Trans. Power Electron.* 2021, 36, 2533–2547. [CrossRef]

- 14. Forouzesh, M.; Siwakoti, Y.P.; Gorji, S.A.; Blaabjerg, F.; Lehman, B. Step-Up DC-DC Converters: A Comprehensive Review of Voltage-Boosting Techniques, Topologies, and Applications. *IEEE Trans. Power Electron.* **2017**, *32*, 9143–9178. [CrossRef]

- 15. Jahan, H.K. A New Transformerless Inverter with Leakage Current Limiting and Voltage Boosting Capabilities for Grid-Connected PV Applications. *IEEE Trans. Ind. Electron.* **2020**, *67*, 10542–10551. [CrossRef]

- McLaughlin, P.H.; Rentmeister, J.S.; Kiani, M.H.; Stauth, J.T. Analysis and Comparison of Hybrid-Resonant Switched-Capacitor DC-DC Converters with Passive Component Size Constraints. *IEEE Trans. Power Electron.* 2021, 36, 3111–3125. [CrossRef]

- 17. Khodaparast, A.; Hassani, M.J.; Azimi, E.; Adabi, M.E.; Adabi, J.; Pouresmaeil, E. Circuit Configuration and Modulation of a Seven-Level Switched-Capacitor Inverter. *IEEE Trans. Power Electron.* **2021**, *36*, 7087–7096. [CrossRef]

- Hussan, M.R.; Sarwar, A.; Siddique, M.D.; Mekhilef, S.; Ahmad, S.; Sharaf, M.; Zaindin, M.; Firdausi, M. A Novel Switched-Capacitor Multilevel Inverter Topology for Energy Storage and Smart Grid Applications. *Electronics* 2020, *9*, 1703. [CrossRef]

- 19. Lee, S.S.; Bak, Y.; Kim, S.M.; Joseph, A.; Lee, K.B. New Family of Boost Switched-Capacitor Seven-Level Inverters (BSC7LI). *IEEE Trans. Power Electron.* **2019**, *34*, 10471–10479. [CrossRef]

- 20. Kim, K.-M.; Han, J.-K.; Moon, G.-W. A High Step-Up Switched-Capacitor 13-Level Inverter with Reduced Number of Switches. *IEEE Trans. Power Electron.* 2021, *36*, 2505–2509. [CrossRef]

- Ramaiah, S.; Lakshminarasamma, N.; Mishra, M.K. Multisource Switched Capacitor Based Boost Multilevel Inverter for Photovoltaic-Based Systems. *IEEE Trans. Power Electron.* 2020, 35, 2558–2570. [CrossRef]

- Raman, S.R.; Fong, Y.C.; Ye, Y.M.; Cheng, K.W.E. Family of Multiport Switched-Capacitor Multilevel Inverters for High-Frequency AC Power Distribution. *IEEE Trans. Power Electron.* 2019, 34, 4407–4422. [CrossRef]

- Raman, S.R.; Cheng, K.W.E.; Ye, Y.M. Multi-Input Switched-Capacitor Multilevel Inverter for High-Frequency AC Power Distribution. *IEEE Trans. Power Electron.* 2018, 33, 5937–5948. [CrossRef]

- 24. Fong, Y.C.; Raman, S.R.; Ye, Y.; Cheng, K.W.E. Generalized Topology of a Hybrid Switched- Capacitor Multilevel Inverter for High- Frequency AC Power Distribution. *IEEE J. Emerg. Sel. Top. Power Electron.* **2020**, *8*, 2886–2897. [CrossRef]

- 25. Siwakoti, Y.P.; Mahajan, A.; Rogers, D.J.; Blaabjerg, F. A Novel Seven-Level Active Neutral-Point-Clamped Converter with Reduced Active Switching Devices and DC-Link Voltage. *IEEE Trans. Power Electron.* **2019**, *34*, 10492–10508. [CrossRef]

- Nakagawa, Y.; Koizumi, H. A Boost-Type Nine-Level Switched Capacitor Inverter. *IEEE Trans. Power Electron.* 2019, 34, 6522–6532. [CrossRef]

- 27. Barzegarkhoo, R.; Moradzadeh, M.; Zamiri, E.; Kojabadi, H.M.; Blaabjerg, F. A New Boost Switched-Capacitor Multilevel Converter with Reduced Circuit Devices. *IEEE Trans. Power Electron.* **2018**, *33*, 6738–6754. [CrossRef]

- Talooki, M.F.; Rezanejad, M.; Khosravi, R.; Samadaei, E. A Novel High Step-Up Switched-Capacitor Multilevel Inverter with Self-Voltage Balancing. *IEEE Trans. Power Electron.* 2021, *36*, 4352–4359. [CrossRef]

- 29. Ye, Y.; Chen, S.; Wang, X.; Cheng, K.W.E. Self-Balanced 13-Level Inverter Based on Switched Capacitor and Hybrid PWM Algorithm. *IEEE Trans. Ind. Electron.* 2021, *68*, 4827–4837. [CrossRef]

- Siddique, M.D.; Mekhilef, S.; Shah, N.B.M.; Ali, J.S.M.; Meraj, M.; Iqbal, A.; Al-Hitmi, M.A. A New Single Phase Single Switched-Capacitor Based Nine-Level Boost Inverter Topology with Reduced Switch Count and Voltage Stress. *IEEE Access* 2019, 7, 174178–174188. [CrossRef]

- Siddique, M.D.; Mekhilef, S.; Shah, N.M.; Sandeep, N.; Ali, J.S.M.; Iqbal, A.; Ahmed, M.; Ghoneim, S.S.M.; Al-Harthi, M.M.; Alamri, B.; et al. A Single DC Source Nine-Level Switched-Capacitor Boost Inverter Topology with Reduced Switch Count. *IEEE Access* 2020, *8*, 5840–5851. [CrossRef]

- Zeng, J.; Lin, W.J.; Liu, J.F. Switched-Capacitor-Based Active-Neutral-Point-Clamped Seven-Level Inverter with Natural Balance and Boost Ability. *IEEE Access* 2019, 7, 126889–126896. [CrossRef]

- Lee, S.S.; Lim, C.S.; Lee, K.-B. Novel Active-Neutral-Point-Clamped Inverters with Improved Voltage-Boosting Capability. *IEEE Trans. Power Electron.* 2020, 35, 5978–5986. [CrossRef]