# Article Hyper-FET's Phase-Transition-Materials Design Guidelines for Ultra-Low Power Applications at 3 nm Technology Node

Hanggyo Jung <sup>1</sup>, Jeesoo Chang <sup>2</sup>, Changhyun Yoo <sup>1</sup>, Jooyoung Oh <sup>1</sup>, Sumin Choi <sup>1</sup>, Juyeong Song <sup>1</sup> and Jongwook Jeon <sup>1,\*</sup>

- <sup>1</sup> Department of Electrical and Electronics Engineering, Konkuk University, Seoul 05029, Republic of Korea

- <sup>2</sup> Data and Information Tech. (DIT) Center, Samsung Electronics, Hwasung-Si 18448, Republic of Korea

- Correspondence: jwjeon@konkuk.ac.kr; Tel.: +82-(24)-503494

**Abstract:** In this work, a hybrid-phase transition field-effects-transistor (hyper-FET) integrated with phase-transition materials (PTM) and a multi-nanosheet FET (mNS-FET) at the 3 nm technology node were analyzed at the device and circuit level. Through this, a benchmark was performed for presenting device design guidelines and for using ultra-low-power applications. We present an optimization flow considering hyper-FET characteristics at the device and circuit level, and analyze hyper-FET performance according to the phase transition time (TT) and baseline-FET off-leakage current (I<sub>OFF</sub>) variations of the PTM. As a result of inverter ring oscillator (INV RO) circuit analysis, the optimized hyper-FET increases speed by +8.74% and reduces power consumption by -16.55%, with I<sub>OFF</sub> = 5 nA of baseline-FET and PTM TT = 50 ps compared to the conventional mNS-FET in the ultra-low-power region. As a result of SRAM circuit analysis, the read static noise margin is improved by 43.9%, and static power is reduced by 58.6% in the near-threshold voltage region when the PTM is connected to the pull-down transistor source terminal of 6T SRAM for high density. This is achieved at 41% read current penalty.

**Keywords:** Boltzmann limit; low power application; phase-transition-materials (PTM); steep switching device; hybrid-phase-transition FETs (hyper-FET)

# 1. Introduction

Silicon-based metal-oxide-semiconductor field-effect transistors (MOSFETs) are being scaled down to sub-5 nm, and a multi-nanosheet FET (mNS-FET) is expected to be used in the 3 nm technical node. Although successful scaling down technology is being developed, increase in power density has become an issue due to difficulty in reducing supply voltage  $(V_{DD})$ . Recently, research on overcoming these limitations by achieving a sub-threshold swing (SS)  $\leq 60 \text{ mV/dec}$  through devices such as negative capacitance FET (NC-FET) [1] and tunneling FET (T-FET) [2] using nanomaterials is being actively conducted. In addition, a Hybrid-Phase Transition Field-Effects-Transistor (hyper-FET) [3] device utilizing the steep switching characteristic of nano-scale Phase-Transition Materials (PTM) [4,5] has been proposed, and various material and process prospective studies are actively being conducted. Recently, a study analyzed for the first time in terms of the operation characteristics of a hyper-FET device and circuit using a fin-FET of a 14 nm technology node as a baseline FET was published by Aziz, A. et al. in [6,7]. However, there are insufficient studies on the electrical characteristics of a hyper-FET upon scaling down to the latest node, such as a 3 nm technology node, and targeting of the PTM characteristics for hyper-FET device design.

In this work, following the approach of Aziz, A. et al., we focused on PTM device design for hyper-FET implementation, based on a 3 nm technology node using a mNS-FET with various threshold voltage ( $V_{th}$ ) characteristics. We propose an optimization method in consideration of device and circuit operation for optimizing the key electrical characteristics

Citation: Jung, H.; Chang, J.; Yoo, C.; Oh, J.; Choi, S.; Song, J.; Jeon, J. Hyper-FET's Phase-Transition-Materials Design Guidelines for Ultra-Low Power Applications at 3 nm Technology Node. *Nanomaterials* **2022**, *12*, 4096. https://doi.org/ 10.3390/nano12224096

Academic Editors: Xuefeng Zheng and Chun Zhao

Received: 16 October 2022 Accepted: 18 November 2022 Published: 21 November 2022

**Publisher's Note:** MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations.

**Copyright:** © 2022 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https:// creativecommons.org/licenses/by/ 4.0/). of baseline-FET and PTM constituting hyper-FET. This is a proposed flow based on a systematic analysis of previously published research results [6,7]. Hyper-FET characteristics were secured according to I<sub>OFF</sub> of baseline-FET and variation of the PTM's transition time (TT) through the systematic optimization process, and benchmarks were performed in logic INV RO and SRAM circuits with conventional CMOS devices. Since an INV RO is a circuit that represents the power and speed characteristics of numerous logic standard cell circuits, such as NAND, NOR, and XOR, the benchmark through an INV RO can be considered to have the characteristics of the entire logic circuit. Also, hyper-FET design guidelines for further circuit characteristic optimization at the 3 nm tech. node are presented.

Chapter 2 of this paper describes the device and circuit simulation environment used in this work, Chapter 3 presents the hyper-FET optimization process and the logic circuit level (INV RO, SRAM) results of benchmark performance with conventional CMOS devices, and Chapter 4 presents the conclusion of this paper.

#### 2. Simulation Environment for Hyper-FET Device and Circuit Co-Analysis

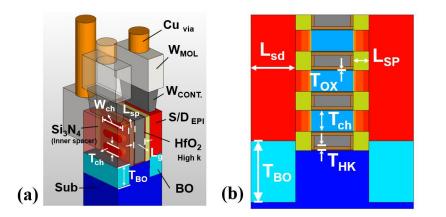

In this work, a lateral multi-nanosheet field-effect transistor (LmNS-FET) using multiple multi-nanosheet channels placed in the lateral direction in the 3 nm technology node dimension, was used as an FEOL device. The number of nanosheet channels used is three, and the main device dimensions of the 3 nm technology node, such as contact-poly-pitch (CPP) and gate length (L<sub>g</sub>), were set concerning IRDS 2020 [8] as shown in Figure 1. Table 1 summarizes the results.

Figure 1. (a) Three-dimensional structure and (b) cross-section view of the mNS-FET used in this work.

| Parameters                                  | Values                            |  |  |

|---------------------------------------------|-----------------------------------|--|--|

| Contacted poly-gate pitch (CPP)             | 45 nm                             |  |  |

| Gate length $(L_g)$                         | 16 nm                             |  |  |

| Inner spacer thickness (L <sub>sp</sub> )   | 6 nm                              |  |  |

| Channel thickness (T <sub>ch</sub> )        | 8 nm                              |  |  |

| Channel width $(W_{ch})$                    | 30 nm                             |  |  |

| Channel oxide thickness (Tox)               | 0.3 nm                            |  |  |

| Channel high-k thickness (T <sub>HK</sub> ) | 1.1 nm                            |  |  |

| Bottom oxide thickness (T <sub>BO</sub> )   | 20 nm                             |  |  |

| Channel doping                              | $10^{17} \text{ cm}^{-3}$         |  |  |

| S/D doping                                  | $3 	imes 10^2 	ext{ cm}^{-3}$     |  |  |

| PTS doping (upper of substrate 1)           | $1	imes 10^{19}~\mathrm{cm}^{-3}$ |  |  |

| Substrate 2 doping                          | $10^{17} { m cm}^{-3}$            |  |  |

The electrical characteristics of the mNS-FET were simulated using Synopsys' Sentarurus<sup>TM</sup> ver. S-2021.06-SP1, a three-dimensional TCAD software, and the model used in this case was used by adding the following models to the drift-diffusion carrier

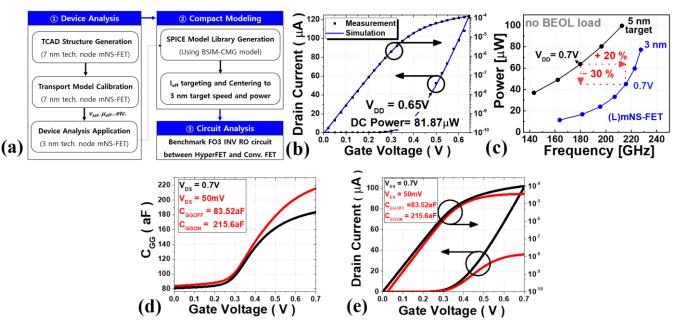

transport model. The density gradient quantization model (eQuantum Potential) was included to describe the quantum confinement effect, and the mobility model (phumob/high field saturation/Enormal) was utilized to consider the quantum effect, Coulomb scattering, and interfacial surface roughness scattering. The Lombardi mobility model was included to calculate the mobility degradation by remote phonon and Coulomb scatterings at the channel and insulator interface. A thin-layer mobility model was included to account for the thin channel thickness. The measured electrical characteristics of the mNS-FET manufactured by hardware in the 7 nm dimension and the TCAD model parameters were calibrated to increase the accuracy of the model. A model library that accurately describes the current-voltage (I-V) and capacitance-voltage (C-V) characteristics extracted through TCAD simulation were then created using the industry-standard model BSIM-CMG. Next, to have the industry's standard 3 nm model circuit characteristics, the generated model library was centered to satisfy the target speed and power of the INV RO with fan-out 3 (FO3), a benchmark circuit, to produce the final model library as summarized in Figure 2.

**Figure 2.** (a) The overall workflow for the analysis of mNS-FET-based device and circuit analysis, (b) calibration results of transport model parameters in TCAD software with measured data, and (c) the FO3 INV RO simulation result after I<sub>OFF</sub> targeting and centering to the 3 nm technology node target, (d,e) C<sub>GG</sub> versus V<sub>GS</sub> & I<sub>DS</sub> versus V<sub>GS</sub> characteristics in this model.

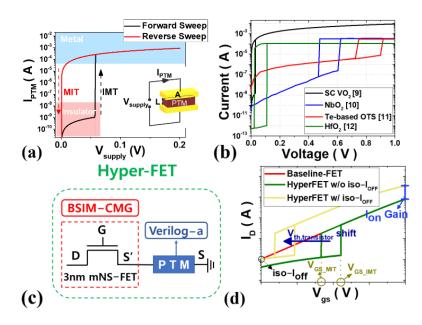

Next, the PTM compact model was developed using Verilog-A to describe the I-V characteristics according to the voltage applied to the PTM as shown in Figure 3a. The developed PTM have a low resistivity  $\rho_{MET}$  in the metal phase and a large resistivity  $\rho_{INS}$  in the insulator phase, and the current determined by the voltage applied across the PTM device is compared with the critical current density (J<sub>C</sub>) at which the phase transition occurs. Such an operation in which either an insulator-metal transition (IMT) or a metal-insulator transition (MIT) occurs through the circuit simulator can be implemented. This model reflects the characteristics of PTMs such as single crystalline VO<sub>2</sub> [9], NbO<sub>2</sub> [10], Te-based OTS [11] and HfO<sub>2</sub> [12], such as in Figure 3b, and the key parameters are summarized in Table 2. In addition, an RC-delay circuit is implemented inside Verilog-A to describe transition time (TT) [13], which has a very important effect on the circuit's dynamic operation characteristics. The dimension of the PTM, the PTM area (A<sub>PTM</sub>) and the PTM length (L<sub>PTM</sub>) are 30 nm × 15 nm (metal pitch × source/drain contact length) and 20 nm, respectively, considering the process design rule of the 3 nm tech. node.

**Figure 3.** (a) I-V characteristics of PTM; (b) Some examples of PTM; (c) Compact modeling structure of hyper-FET; (d) Transfer curve of baseline-FET and hyper-FET before and after I<sub>OFF</sub> targeting.

| Table 2. PTM's | key parameters & | : PTM-3 nm values | used in this work. |

|----------------|------------------|-------------------|--------------------|

|----------------|------------------|-------------------|--------------------|

|                                                                            | Value                                                                                                                                                      |                                                                                                                                                                                                                          |

|----------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ρ <sub>INS</sub><br>ρ <sub>MET</sub><br>Jc_imt<br>J <sub>C_MIT</sub><br>TT | Resistivity of Insulator state<br>Resistivity of Metal state<br>Critical Current Density for IMT<br>Critical Current Density for MIT<br>PTM Switching Time | $\begin{array}{c} 1.2 \times 10^2 \ \Omega \cdot \mathrm{cm} \\ 5.0 \times 10^{-4} \ \Omega \cdot \mathrm{cm} \\ 2.4 \times 10^2 \ \mathrm{A/cm^2} \\ 2.2 \times 10^3 \ \mathrm{A/cm^2} \\ 50 \ \mathrm{ps} \end{array}$ |

As shown in Figure 3c, the compact model of the hyper-FET with the PTM connected in series to the source terminal of the baseline-FET has the transfer characteristics as shown in Figure 3d. Gate voltage conditions in which an IMT and MIT occur are named  $V_{GS\_IMT}$  and  $V_{GS\_MIT}$ , respectively. Assuming that the  $V_{th}$ -shift of the baseline FET is possible through a process such as work-function engineering, the hyper-FET is expected to improve on-current compared to the conventional mNS-FET under the iso-I<sub>OFF</sub> condition.

#### 3. Hyper-FET Simulation Results and Discussions

For hyper-FET optimization, it is necessary to determine the electrical characteristics of each device under systematical analysis since there is a very close relationship between the composing baseline-FET and the electrical characteristics of the PTM. In this work, the key parameters of the PTM ( $\rho_{INS}$ ,  $\rho_{MET}$ ,  $J_{C_{-IMT}}$ ,  $J_{C_{-MIT}}$ ) were determined through the circuit characteristics according to the switching time characteristics of the PTM and the variation in baseline-FET I<sub>OFF</sub> characteristics, which were not considered in previous studies. Through this, hyper-FET design optimization was performed, and circuit-level benchmarks were performed with conventional 3 nm tech. mNS-FET.

#### 3.1. Hyper-FET Design Optimization Flow

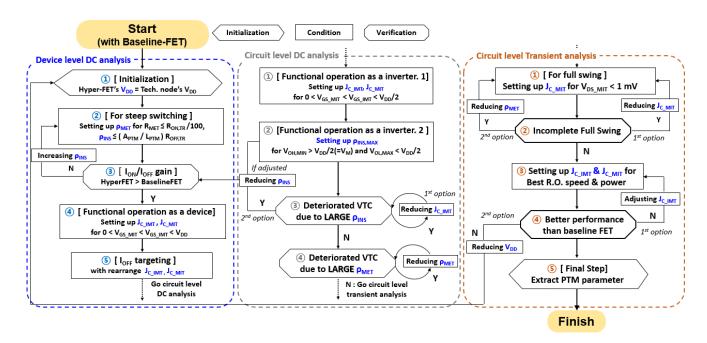

For optimal design of hyper-FET devices, device level DC (DD), circuit level DC (CD), and circuit level transient (CT) analysis are essential, as shown in Figure 4. In this subchapter, the systematic optimization process used in this work is described.

Figure 4. An optimal PTMs parameter extraction flow chart.

#### 3.1.1. Device Level DC Analysis

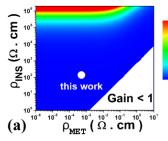

As he initial setting of the hyper-FET's V<sub>DD</sub> is used as the supply voltage of the baseline-FET, the conditions under which the resistance of the PTM (R<sub>PTM</sub>) for the hyper-FET have steep slope characteristics are discussed. In order to prevent the PTM's resistance of the metal state (R<sub>MET</sub>) from inhibiting the on-current of the hyper-FET, the  $\rho_{MET}$  is determined to be at least 100 times smaller than the resistance of the transistor in the on state (R<sub>ON,TR</sub> at V<sub>GS</sub> = V<sub>DD</sub>, V<sub>DS</sub> = V<sub>DD</sub>). Then, the resistance of the insulator state of the PTM (R<sub>INS</sub>) is determined through Figure 5a, a graph where Hyper-FET I<sub>ON</sub>/I<sub>OFF</sub> is mapped according to  $\rho_{INS}$  and  $\rho_{MET}$  made with reference to [6]. The gain increases in proportion to  $\rho_{INS}$ , but circuit operation may become difficult if too large, as shown in CD-3. Therefore, the  $\rho_{INS}$  is set so that R<sub>INS</sub> is less than the resistance of the transistor in the off state (R<sub>OFF,TR</sub> at V<sub>GS</sub> = 0 V, V<sub>DS</sub> = V<sub>DD</sub>), and I<sub>ON</sub>/I<sub>OFF</sub> gain is checked compared to the baseline-FET. Then, J<sub>C\_IMT</sub>&J<sub>C\_MIT</sub> was designed to include I<sub>C\_IMT</sub>&I<sub>C\_MIT</sub> in the yellow box of Figure 5d,e, made with reference to [6], so that hyper-FET, as shown in Figure 5b, transitions within the given supply voltage range.

**Figure 5.** (a)  $I_{ON}/I_{OFF}$  gain mapping of hyper-FET compared to baseline-FET; (b,c) schematic of the hyper-FET and the hyper-FET-based inverter; (d,e)  $I_{C\_IMT} \& I_{C\_MIT}$  ranges for proper operation in the I-V curves of (b) and (c) (yellow box & black text for (b), orange box & red text for (c)).

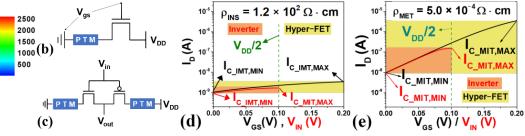

Furthermore, it is necessary to satisfy the condition of  $V_{GS_{IMT}} > V_{GS_{MIT}}$  to avoid negative hysteresis [14] in which the current of the hyper-FET oscillates, as shown in Figure 6a. This phenomenon can be understood through Figure 6b, which is a graph of voltage biased to the PTM ( $V_{PTM}$ ) and the current graph according to  $V_{GS}$ . As  $V_{GS}$  increases,

$V_{PTM}$  increases, and when  $V_{PTM}$  reaches critical voltage for an IMT ( $V_{C_{IMT}}$ ), negative differential resistance (NDR) occurs, in which  $V_{PTM}$  decreases and current increases due to the lowered resistance. If the resistance of the transistor during transition ( $R_{TR}$ ) is less than or equal to a critical resistance ( $R_C$ ), the PTMs make hysteretic switching. On the other hand, because of the large  $R_{TR}$ , the relatively lower  $V_{PTM}$  is not sufficient to keep the PTM in a metal state, so MIT occurs again, and it repeats and oscillates like a green line, which is called negative hysteresis. If  $R_{TR} > R_C$ ,  $V_{GS}$  decreases from  $V_{DD}$  and  $V_{PTM}$  satisfies critical voltage for MIT( $V_{C_{MIT}}$ ), the  $V_{PTM}$  is too large to keep the PTMs in the resistance state, so they transition back to the metal state and oscillate in the same way. The critical resistance  $R_C$  is as follows [14]:

$$R_{C} = \frac{|V_{C\_IMT} - V_{C\_MIT}|}{|I_{C\_IMT} - I_{C\_MIT}|}$$

(1)

**Figure 6.** (a) The hyper-FET transfer curve with negative hysteresis (b) I-V characteristics of PTMs according to R<sub>TR</sub>.

Lastly,  $I_{ON}$  gain is obtained by matching the  $I_{OFF}$  of hyper-FET with that of the baseline-FET, as shown in Figure 3d (of course,  $J_{C_{IMT}}$  &  $J_{C_{MIT}}$  adjustment is necessary afterwards).

#### 3.1.2. Circuit Level DC Analysis

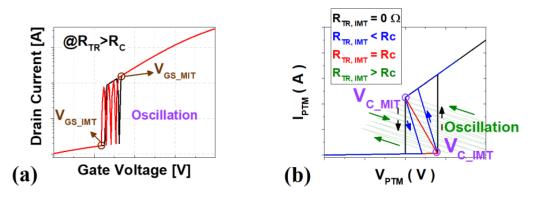

For functional operation of the logic circuit, the effect of hysteresis, which is not in the existing FET, on the VTC (Voltage-Transfer-Curve) is checked. First, as revealed in previous study [7], if an IMT does not occur before V<sub>M</sub> (logic threshold voltage) regardless of forwarding sweep or reverse sweep at the VTC in Figure 7a, the inverter current in Figure 7b does not satisfy the IMT condition and switching does not occur within the voltage range. Therefore, design J<sub>C\_IMT</sub> and J<sub>C\_MIT</sub> so that I<sub>C\_IMT</sub> and I<sub>C\_MIT</sub> are included in the orange box in Figure 5d,e are obtained with the inverter in Figure 5c since V<sub>GS\_IMT</sub> & V<sub>GS\_MIT</sub> < V<sub>DD</sub>/2 must be satisfied. In general, the characteristics are improved in proportion to  $\rho_{INS}$ , so  $\rho_{INS,MAX}$  as large as possible is required. However, when this maximum value is exceeded, the high-level output voltage's minimum (V<sub>OH,MIN</sub>) comes into contact with V<sub>M</sub>, and the VTC collapses, as shown by the green line in Figure 7c. In this case, it is necessary to either reduce J<sub>C\_IMT</sub> with the first option, or reduce  $\rho_{INS}$  with the second option. Additionally, if  $\rho_{MET}$  is too large, it adversely affects V<sub>OUT</sub>, as shown in Figure 7d. To prevent this, the initial value of  $\rho_{MET}$  is set small enough.

**Figure 7.** (a) Functional hyper-inverter's VTC; (b) Inverter current versus V<sub>IN</sub> of functional hyper-inverter; (c,d) Non-functional VTC due to (c) large R<sub>INS</sub>; (d) large R<sub>MET</sub>.

#### 3.1.3. Circuit Level Transient Analysis

In DC analysis,  $V_{OUT}$  varies as much as  $\Delta V_{OUT}$ , as shown in Figure 7a, and it was revealed in the previous paper [7] that this phenomenon is prevented when the  $V_{DS\_MIT}$ ( $V_{DS}$  at which an MIT occurs) of a hyper-FET is lower than 1 mV. If not, either  $J_{C\_MIT}$ or  $\rho_{MET}$  should be reduced. After verifying that the given values have proper VTC, the performance is evaluated using an INV RO with a fan-out of 3 (FO3) with a hyper-FET. Evaluate various performances by adjusting  $J_{C\_IMT}$  and  $J_{C\_MIT}$  under the given  $\rho_{INS}$  and  $\rho_{MET}$  conditions.  $V_{DD}$  scaling down is necessary if the target performance is not obtained because of the TT of the PTM, and has a large influence on speed limiting, which will be dealt with later in Section III-B. In this case, you must start over from DD-1. If the expected performance is satisfied, measure the power and performance and extract the parameters of the PTMs. Table 2 summarizes the key parameters of the PTMs obtained through the above flow when a 3 nm mNS-FET is used as a baseline-FET.

## 3.2. Benchmark with Conventional MOSFET Using INV RO

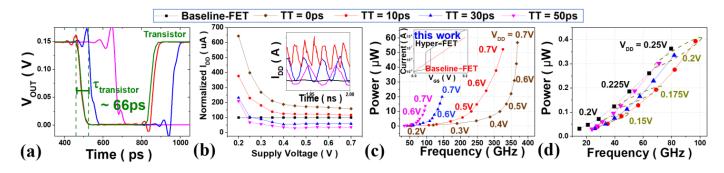

First, we discuss the results of studying the optimal characteristics of a hyper-FET for 3 nm tech. mNS-FET according to the TT of the PTM. Figure 8a shows the transient analysis of an INV RO according to the TT. The intrinsic transistor delay ( $\tau_{transistor}$ ) required for transition from  $V_{DD}$  to GND (or vice versa) is measured as 66 ps. In the case of hyper-FET, the delay is longer than  $\tau_{transistor}$  due to the TT required for the PTM to change phase. This can be understood through the internal graph of Figure 8b showing the current flowing in the hyper-FET-based INV RO, because the higher the TT of the PTM, the lower the current level. According to Figure 8b, a graph in which the average current of the internal graph is normalized to the average current of the baseline-FET, When the TT is less than 10 ps, the current level is higher than the baseline-FET over all  $V_{DD}$  ranges. However, when the TT  $\geq$  30 ps, a high current level was observed only in the ultra-low power region with a low  $\tau_{transistor}$  of 0.3 V or less. This indicates that the TT of the PTM suppresses the Hyper-FET from having a higher I<sub>ON</sub> compared to the baseline-FET at the device level. As the TT of the PTM increases, the circuit performance of the hyper-FET will deteriorate due to the increase in delay and the decrease in the current level. Therefore, in order to use it as a logic device of the hyper-FET, PTM having a TT much smaller than at least  $\tau_{transistor}$  should be used. Figure 8c shows the circuit characteristics according to the TT of the PTM. As the TT is higher, the current level is lowered and the delay is increased, so the performance and power of the circuit are both reduced. However, this tendency is reduced in the low V<sub>DD</sub> region, which is relatively smaller than the TT of the PTM due to the increased  $\tau_{transistor}$  of the transistor.

**Figure 8.** (a) INV RO transient waveforms according to the TT of the PTM; (b) Normalization of the average hyper-FET's current ( $I_{DDA}$ ) according to PTMs' TT to a baseline-FET, and the internal graph shows the transient waveform of the inverter current; (c,d) Hyper-FET's circuit characteristics of some PTM's TT (a) at  $V_{DD} = 0.2 \sim 0.7$  V (b) at  $V_{DD} \leq 0.25$  V.

Figure 8d shows the circuit characteristics with a TT lower than  $\tau_{transistor}$  in the ultralow power region ( $V_{DD} \le 0.25$  V). The baseline-FET used was  $I_{OFF} = 5$  nA at  $V_{DD} = 0.7$  V, and the value of PTM-3 nm illustrated in Table 2 was used. Table 3 summarizes the operation frequency, active power gain, and supply voltage of the hyper-FET compared to the baseline-FET with  $V_{DD} = 0.2$  V. In all cases of Table 3, the circuit performance was improved even if the supply voltage of the hyper-FET was lower than that of the baseline-FET ( $V_{DD} = 0.2$  V), which is an  $I_{ON}$  gain obtained with a steep slope, and the speed was high and the power was decreased due to the low voltage. In case of a TT = 50 ps, compared to a baseline-FET with  $V_{DD} = 0.2$  V, frequency shows a +8.96% and power -16.68% improvement, and their improvement increases as the TT decreases. This shows that at least the TT of the PTMs should be less than 50 ps for the logic device of hyper-FET based on 3 nm tech mNS-FETs.

|                              | Baseline-FET               | Hyper-FET                                |                                            |                                            |

|------------------------------|----------------------------|------------------------------------------|--------------------------------------------|--------------------------------------------|

| $I_{OFF} = 5 nA$             | $(V_{DD} = 0.2 V)$         | TT = 50 ps<br>(V <sub>DD</sub> = 0.15 V) | TT = 30 ps<br>(V <sub>DD</sub> = 0.1375 V) | TT = 10 ps<br>(V <sub>DD</sub> = 0.1375 V) |

| Operating<br>Frequency (GHz) | $2.87 	imes 10^1$ (Ref.)   | $3.13 	imes 10^1$ (+8.96%)               | $3.35 \times 10^1 \ (+16.89\%)$            | $3.50	imes 10^1$ (+21.83%)                 |

| Active Power (µW)            | $7.18\times10^{-2}$ (Ref.) | $5.98 \times 10^{-2} \\ (-16.68\%)$      | $5.09 	imes 10^{-2}$ (-29.10%)             | $5.08 \times 10^{-2}$ (-29.24%)            |

Table 3. Hyper-FET characteristics according to the TT of the PTMs.

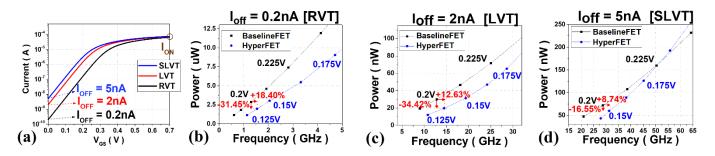

The following is the result of studying the optimal characteristics of hyper-FET according to  $V_{th}$  of the baseline-FET. Figure 9a shows the transfer characteristic of 3 nm tech. mNS-FET according to various threshold voltages, and the RVT (Regular Voltage Threshold), the LVT (Low Voltage Threshold) and the SLVT (Super Low Voltage Threshold) are named for the case where  $I_{OFF}$  is 0.2 nA, 2 nA, and 5 nA at  $V_{DD} = 0.7$  V of the baseline-FET, respectively. In addition, Figure 9b-d shows the optimized circuit characteristics in each case of  $V_{DD} \le 0.25$  V at TT = 50 ps. Table 4 summarizes the characteristics of the hyper-FET compared to the baseline FET with  $V_{DD} = 0.2$  V. As discussed earlier, the relationship between  $\tau$  and the TT is significant. The overall current level, which is determined by the  $V_{th}$  of the transistor, determines the  $\tau_{transistor}$ , and the higher the  $V_{th}$ , the freer from the disturbance of the TT. In the case of the RVT device, the hyper-FET shows improvement in frequency by +18.40% and power by -31.45% compared to the baseline-FET. However, as shown in Figure 9c,d, it is observed that as  $V_{th}$  decreases,  $\tau_{transistor}$  approaches the TT, and the amount of performance improvement decreases. In other words, if the designer knows the TT of the PTM, the higher the  $V_{th}$ , the wider the device's versatility, and the range of V<sub>th</sub> that can be optimized is suggested.

**Figure 9.** (a) Transfer characteristics according to 3 nm tech. mNS-FET's V<sub>th</sub> (**b**–**d**) Power and performance evaluation graph of (**b**) RVT ( $I_{OFF} = 0.2 \text{ nA}$ ), (**c**) LVT ( $I_{OFF} = 2 \text{ nA}$ ), (**d**) SLVT ( $I_{OFF} = 5 \text{ nA}$ ).

| Table 4. Hyper-FET characteristics according to the baseline-FET's $I_{OFF}$ . |

|--------------------------------------------------------------------------------|

|                                                                                |

|                                 | $I_{OFF} = 0.2 nA$                        |                                                                  | $I_{OFF} = 2 nA$                          |                                                                  | $I_{OFF} = 5 nA$                          |                                         |

|---------------------------------|-------------------------------------------|------------------------------------------------------------------|-------------------------------------------|------------------------------------------------------------------|-------------------------------------------|-----------------------------------------|

| TT = 50 ps                      | Baseline-FET<br>(V <sub>DD</sub> = 0.2 V) | Hyper-FET<br>(V <sub>DD</sub> = 0.138 V)                         | Baseline-FET<br>(V <sub>DD</sub> = 0.2 V) | Hyper-FET<br>(V <sub>DD</sub> = 0.138 V)                         | Baseline-FET<br>(V <sub>DD</sub> = 0.2 V) | Hyper-FET<br>(V <sub>DD</sub> = 0.15 V) |

| Operating<br>Frequency<br>(GHz) | $1.30 \times 10^{1}$ (Ref.)               | $1.54	imes 10^1$ (+18.40%)                                       | $1.29 \times 10^{1}$ (Ref.)               | $1.45 	imes 10^1$<br>(+12.63%)                                   | 2.87 × 10 <sup>1</sup><br>(Ref.)          | $3.12 	imes 10^1$<br>(+8.74%)           |

| Active Power<br>(µW)            | $2.89 \times 10^{-2}$ (Ref.)              | $\begin{array}{c} 1.98 \times 10^{-2} \\ (-31.45\%) \end{array}$ | $3.00 \times 10^{-2}$ (Ref.)              | $\begin{array}{c} 1.97 \times 10^{-2} \\ (-34.42\%) \end{array}$ | $7.18 \times 10^{-2}$ (Ref.)              | $5.99 \times 10^{-2}$<br>(-16.55%)      |

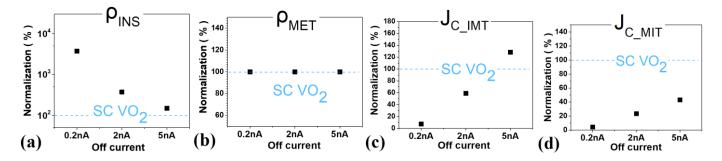

Figure 10 shows the optimal PTM's key parameter obtained through the previous flow-based circuit simulation, and shows the tendency according to  $I_{OFF}$  by normalizing the parameter of Single Crystalline (SC) VO<sub>2</sub> [9], one of the most promising candidate PTMs. First, as can be seen from the circuit DC analysis above, the optimal value of  $\rho_{INS}$  decreases proportionally as the transistor resistance decreases. Therefore, as the off-current increases, the optimal  $\rho_{INS}$  decreases and becomes similar to that of SC VO<sub>2</sub>. On the other hand, the on-current does not change much, so  $\rho_{MET}$  set small enough is almost constant. In the case of the critical current density, it shows a tendency to increase as the off-current increases to switch within the current level. In this condition, when  $I_{OFF} = 5$  nA,  $J_{C_{-IMT}}$  is 28% larger and  $J_{C_{-MIT}}$  is 57% smaller than SC VO<sub>2</sub>. Through this work, if SC VO<sub>2</sub> is used for hyper-FET utilization of 3 nm tech. mNS-FET, an SLVT device with IOFF = 5 nA is appropriate, and an adjustment of around 60% to the PTM parameter is required.

**Figure 10.** The PTM key parameter trend according to baseline-FET's  $I_{OFF}$  (**a**)  $\rho_{INS}$  (**b**)  $\rho_{MET}$  (**c**)  $J_{C\_IMT}$  (**d**)  $J_{C\_MIT}$ .

# 3.3. Benchmark with Conventional MOSFET Using 6T SRAM

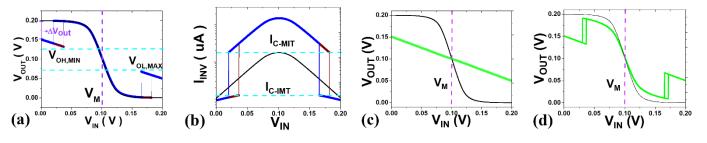

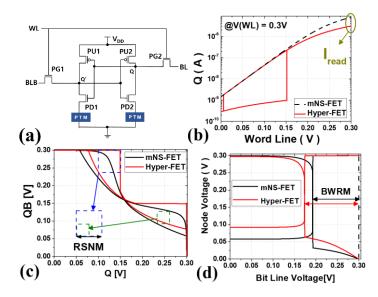

In a previous study [15], SRAM topology based on hyper-FET was reported, and a schematic is shown in Figure 11a. The device has a high-density structure with a transistor channel width ratio of pull up: pass gate: pull down = 1:1:1, and the PTM is added to only two pull-down (PD) transistor source terminals out of a total of six transistors, two

each. Figure 11b–d shows the results of I<sub>read</sub> related to read time [16], Read Static Noise Margin RSNM, and Bit-line Write Margin BWRM [17], respectively, compared to mNS-FET 6T SRAM. It is assumed that '0' is stored in Q node and '1' is stored in QB node. In the proposed topology, the PTM in the insulator state of the source of PD1 decreases the strength of PD1 in the read operation and increases the read ability by maintaining the insulator state against noise in Q (or QB). In the write operation, V<sub>Q</sub> increases due to the PTM in the insulator state connected to PD2, and at the same time, the V<sub>QB</sub> increases by the PTM in the metal state of PD1 to increase the write ability. Also, the high resistance of the insulator state reduces standby power. As a result of the analysis, the RSNM improved by 43.9%, the BWRM improved by 9.4%, and the static power was reduced by 58.6%. In this case, I<sub>read</sub> is reduced by 41.4%. Table 5 summarizes the above SRAM index results.

**Figure 11.** (a) The proposed 6T SRAM w/PTM Schematic; (b) I<sub>read</sub>; (c) RSNM results; (d) BWRM results.

|                      | I <sub>read</sub> (μA) | RSNM (mV) | BWRM (mV) | Static Power (nW) |

|----------------------|------------------------|-----------|-----------|-------------------|

| mNS-FET 6T<br>SRAM   | 2.68                   | 35.3      | 107.2     | 1.28              |

| Hyper-FET 6T<br>SRAM | 1.57                   | 50.8      | 117.3     | 0.53              |

| Improvement          | -41.4%                 | +43.9%    | +9.4%     | +58.6%            |

Table 5. Comparison with 6T SRAM.

## 4. Conclusions

In this work, we present a systematic design guideline for optimal use of a hyper-FET according to the electrical characteristics of a baseline-FET and the PTM, and, using this, the INV RO and SRAM characteristics according to the PTM's TT and various characteristics of 3 nm-tech. mNS-FET was evaluated. The presented hyper-FET optimization flow chart allows other researchers to evaluate the optimized logic circuit characteristics of any baseline-FET. Through this, it was confirmed that the circuit characteristics were further improved as the transition time of the PTM was shorter than the intrinsic delay of the transistor. Analysis results show that in the case of 3 nm tech. mNS-FETs, the PTM's TT should be less than 50 ps in the ultra-low power region (V<sub>DD</sub> < 0.3 V). In addition, hyper-FET circuit characteristics according to various threshold voltage options of 3 nm tech. mNS-FET related to intrinsic delay were evaluated and the PTM parameter trends were analyzed accordingly. As a result, at the TT = 50 ps of the PTM, the SLVT device with

$I_{OFF} = 5$  nA showed a +8.96% improvement in speed and a -16.68% improvement in power at  $V_{DD} = 0.15$  V. The PTM-3 nm key parameters used in this work are similar to those of Single Crystalline VO<sub>2</sub> [9]. Also, the 3 nm tech. mNS-FET based 6T SRAM structure with the PTM connected to the pull-down source terminal shows the RSNM improved by 43.9%, the BWRM improved by 9.4%, and the static power was reduced by 58.6%. In this case,  $I_{read}$  is reduced by 41.4%. Our systematic optimization flow and the results of logic and memory circuit characteristics not only show the potential for ultra-low power applications of 3 nm technology, but also suggest a direction for PTM optimization of transistors with various characteristics.

**Author Contributions:** H.J. and J.J. contributed to the main idea and writing of this research; C.Y. and J.C. performed transistor modeling for simulation; J.O., J.S. and S.C. performed the SRAM simulations. This research was planned and executed under the supervision of J.J. All authors have read and agreed to the published version of the manuscript.

**Funding:** This work was supported the National Foundation of Korea (NRF) grant funded by the Korean government (MSIT) (No.2020M3F3A2A01081595), and partly by the National Research Foundation of Korea (NRF) grant funded by the Korean government (MSIT) (No.2020M3F3A2A01082326).

Data Availability Statement: Not applicable.

Acknowledgments: The EDA tool was supported by the IC Design Education Center (IDEC), Republic of Korea.

Conflicts of Interest: The authors declare no conflict of interest.

#### References

- Yan, S.-C.; Wu, C.-H.; Sun, C.-J.; Lin, Y.-W.; Yao, Y.-J.; Wu, Y.-C. Trench FinFET Nanostructure with Advanced Ferroelectric Nanomaterial HfZrO<sub>2</sub> for Sub-60-mV/Decade Subthreshold Slope for Low Power Application. *Nanomaterials* 2022, 12, 2165. [CrossRef] [PubMed]

- Azam, S.M.T.; Bakibillah, A.S.M.; Hasan, M.T.; Kamal, M.A.S. Effect of Step Gate Work Function on InGaAs p-TFET for Low Power Switching Applications. *Nanomaterials* 2021, 11, 3166. [CrossRef]

- Shukla, N.; Thathachary, A.V.; Agrawal, A.; Paik, H.; Aziz, A.; Schlom, D.G.; Summet, K.G.; Engel-Herbert, R.; Datta, S. A steep-slope transistor based on abrupt electronic phase transition. *Nat. Commun.* 2015, *6*, 7812. [CrossRef] [PubMed]

- 4. Zhang, Y.; Xiong, W.; Chen, W.; Zheng, Y. Recent progress on vanadium dioxide nanostructures and devices: Fabrication, properties, applications and perspectives. *Nanomaterials* **2021**, *11*, 338. [CrossRef] [PubMed]

- Song, B.; Cao, R.; Xu, H.; Liu, S.; Liu, H.; Li, Q. A HfO<sub>2</sub>/SiTe based dual-layer selector device with minor threshold voltage variation. *Nanomaterials* 2019, 9, 408. [CrossRef] [PubMed]

- 6. Aziz, A.; Shukla, N.; Datta, S.; Gupta, S.K. Steep switching hybrid phase transition FETs (hyper-FET) for low power applications: A device-circuit co-design perspective—Part I. *IEEE Trans. Electron Devices* **2017**, *64*, 1350–1357. [CrossRef]

- Aziz, A.; Shukla, N.; Datta, S.; Gupta, S.K. Steep switching hybrid phase transition FETs (hyper-FET) for low power applications: A device-circuit co-design perspective—Part II. *IEEE Trans. Electron Devices* 2017, 64, 1358–1365. [CrossRef]

- 8. International Roadmap for Devices and Systems (IRDS<sup>™</sup>). 2020. Available online: https://irds.ieee.org/editions/2020 (accessed on 23 July 2020).

- 9. Ladd, L.A.; Paul, W. Optical and transport properties of high quality crystals of V2O4 near the metallic transition temperature. *Solid State Commun.* **1969**, *7*, 425–428. [CrossRef]

- Park, J.; Lee, D.; Yoo, J.; Hwang, H. NbO<sub>2</sub> based threshold switch device with high operating temperature (>85 C) for steep-slope MOSFET (~2 mV/dec) with ultra-low voltage operation and improved delay time. In Proceedings of the 2017 IEEE International Electron Devices Meeting (IEDM), San Francisco, CA, USA, 2–6 December 2017; pp. 23–27.

- Yoo, J.; Kim, S.H.; Chekol, S.A.; Park, J.; Sung, C.; Song, J.; Donghwa, L.; Hwang, H. 3D stackable and scalable binary ovonic threshold switch devices with excellent thermal stability and low leakage current for high-density cross-point memory applications. *Adv. Electron. Mater.* 2019, *5*, 1900196. [CrossRef]

- 12. Sun, Y.; Zhao, X.; Song, C.; Xu, K.; Xi, Y.; Yin, J.; Wang, Z.; Zhou, X.; Chen, X.; Shi, G.; et al. Performance-enhancing selector via symmetrical multilayer design. *Adv. Funct. Mater.* **2019**, *29*, 1808376. [CrossRef]

- Jerry, M.; Shukla, N.; Paik, H.; Schlom, D.G.; Datta, S. Dynamics of electrically driven sub-nanosecond switching in vanadium dioxide. In Proceedings of the 2016 IEEE Silicon Nanoelectronics Workshop (SNW), Honolulu, HI, USA, 12–13 June 2016; pp. 26–27.

- 14. Shukla, N.; Parihar, A.; Freeman, E.; Paik, H.; Stone, G.; Narayanan, V.; Wen, H.; Cai, Z.; Gopalan, V.; Engel-Herbert, R.; et al. Synchronized charge oscillations in correlated electron systems. *Sci. Rep.* **2014**, *4*, 4964. [CrossRef]

- 15. Srinivasa, S.; Aziz, A.; Shukla, N.; Li, X.; Sampson, J.; Datta, S.; Kulkarni, J.P.; Narayana, V.; Gupta, S.K. Correlated material enhanced SRAMs with robust low power operation. *IEEE Trans. Electron Devices* **2016**, *63*, 4744–4752. [CrossRef]

- 16. Mukherjee, D.; Mondal, H.K.; Reddy, B.V.R. Static noise margin analysis of SRAM cell for high speed application. *Int. J. Comput. Sci. Issues (IJCSI)* **2010**, *7*, 175.

- 17. Wang, J.; Nalam, S.; Calhoun, B.H. Analyzing static and dynamic write margin for nanometer SRAMs. In Proceedings of the 13th International Symposium on Low Power Electronics and Design (ISLPED'08), Bangalore, India, 11–13 August 2008; pp. 129–134.