MDPI

Article

# Investigation on Ge<sub>0.8</sub>Si<sub>0.2</sub>-Selective Atomic Layer Wet-Etching of Ge for Vertical Gate-All-Around Nanodevice

Lu Xie <sup>1,2</sup>, Huilong Zhu <sup>1,\*</sup>, Yongkui Zhang <sup>1</sup>, Xuezheng Ai <sup>1</sup>, Junjie Li <sup>1</sup>, Guilei Wang <sup>1,2,3,\*</sup>, Anyan Du <sup>1</sup>, Zhenzhen Kong <sup>1,2,3</sup>, Qi Wang <sup>1</sup>, Shunshun Lu <sup>1</sup>, Chen Li <sup>1,2</sup>, Yangyang Li <sup>1,2</sup>, Weixing Huang <sup>1,2</sup> and Henry H. Radamson <sup>1,2,3,\*</sup>

- <sup>1</sup> Key Laboratory of Microelectronics Devices & Integrated Technology, Institute of Microelectronics, Chinese Academy of Sciences, Beijing 100029, China; xielu@ime.ac.cn (L.X.); zhangyongkui@ime.ac.cn (Y.Z.); aixuezheng@ime.ac.cn (X.A.); lijunjie@ime.ac.cn (J.L.); duanyan@ime.ac.cn (A.D.); kongzhenzhen@ime.ac.cn (Z.K.); wangqi@ime.ac.cn (Q.W.); lushunshun@ime.ac.cn (S.L.); lichen2017@ime.ac.cn (C.L.); liyangyang@ime.ac.cn (Y.L.); huangweixing@ime.ac.cn (W.H.)

- <sup>2</sup> Microelectronics Institute, University of Chinese Academy of Sciences, Beijing 100049, China

- Research and Development Center of Optoelectronic Hybrid IC, Guangdong Greater Bay Area Institute of Integrated Circuit and System, Guangdong 510535, China

- \* Correspondence: zhuhuilong@ime.ac.cn (H.Z.); wangguilei@ime.ac.cn (G.W.); rad@ime.ac.cn (H.H.R.)

**Abstract:** For the formation of nano-scale Ge channels in vertical Gate-all-around field-effect transistors (vGAAFETs), the selective isotropic etching of Ge selective to  $Ge_{0.8}Si_{0.2}$  was considered. In this work, a dual-selective atomic layer etching (ALE), including  $Ge_{0.8}Si_{0.2}$ -selective etching of Ge and crystal-orientation selectivity of Ge oxidation, has been developed to control the etch rate and the size of the Ge nanowires. The ALE of Ge in p<sup>+</sup>- $Ge_{0.8}Si_{0.2}$ /Ge stacks with 70% HNO<sub>3</sub> as oxidizer and deionized (DI) water as oxide-removal was investigated in detail. The saturated relative etched amount per cycle (REPC) and selectivity at different HNO<sub>3</sub> temperatures between Ge and p<sup>+</sup>- $Ge_{0.8}Si_{0.2}$  were obtained. In p<sup>+</sup>- $Ge_{0.8}Si_{0.2}$ /Ge stacks with (110) sidewalls, the REPC of Ge was 3.1 nm and the saturated etching selectivity was 6.5 at HNO<sub>3</sub> temperature of 20 °C. The etch rate and the selectivity were affected by HNO<sub>3</sub> temperatures. As the HNO<sub>3</sub> temperature decreased to 10 °C, the REPC of Ge was decreased to 2 nm and the selectivity remained at about 7.4. Finally, the application of ALE in the formation of Ge nanowires in vGAAFETs was demonstrated where the preliminary  $I_d$ - $V_{ds}$  output characteristic curves of Ge vGAAFET were provided.

$\label{eq:Keywords: Weywords: Weywords: Vertical Gate-all-around (vGAA); $p^+$-$Ge$_{0.8}Si$_{0.2}$/$Ge stack; dual-selective wet etching; atomic layer etching (ALE)$

Citation: Xie, L.; Zhu, H.; Zhang, Y.; Ai, X.; Li, J.; Wang, G.; Du, A.; Kong, Z.; Wang, Q.; Lu, S.; et al. Investigation on Ge<sub>0.8</sub>Si<sub>0.2</sub>-Selective Atomic Layer Wet-Etching of Ge for Vertical Gate-All-Around Nanodevice. *Nanomaterials* **2021**, *11*, 1408. https://doi.org/10.3390/nano11061408

Academic Editor: Konstantins Jefimovs

Received: 11 May 2021 Accepted: 23 May 2021 Published: 26 May 2021

**Publisher's Note:** MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Copyright: © 2021 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

#### 1. Introduction

As the continuous scaling down of complementary metal-oxide-semiconductor (CMOS) technology nodes, novel device designs and high-mobility channel materials have been under investigation [1–8]. Vertical nanowire GAAFET is a powerful candidate for the 3 nm process, since its superiority in the short channel effects (SCEs) control [9,10] and can greatly reduce the gate pitch and increase the device integration density [11,12]. In addition, Ge is one of the most promising channel materials for pMOS due to its high carrier mobility and excellent bandgap [13]. Therefore, vertical GAAFETs with Ge as channel material have become an ideal choice for next era CMOS technology.

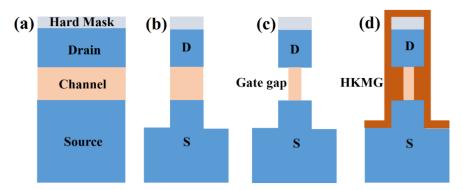

For vertical GAA devices, a new structure of vertical sandwich GAAFETs (VSAFETs) with Si source/drain and SiGe channel has been proposed [14,15]. The main process flow of VSAFETs is shown in Figure 1, the selective etching of the channel is a key step in the formation of vertical nanostructures. And the dimension of the channel is determined by selective etching. For the formation of Ge vertical nanowires, several selective etching methods have been reported, including dry etching with Cl<sub>2</sub> or CF<sub>4</sub> RF plasma [16–18] or

Nanomaterials **2021**, 11, 1408 2 of 15

mixtures of  $Cl_2/HBr$  [19] and wet etching with  $H_2O_2$  (HNO<sub>3</sub>) [20] or TMAH [21] or other alkaline solutions [22] or mixtures of HF/H<sub>2</sub>O<sub>2</sub>/CH<sub>3</sub>COOH [20,23]. SiGe/Ge multilayer structures have been used to release with SiGe sacrificial layer etching to fabricate Ge nanowires in the lateral GAA device [19,24]. However, the above-mentioned methods for forming Ge nanowires are all continuous etching methods, and the etching depth is time-dependent. They achieve high selectivity and high etch rate at the cost of repeatability. At and beyond the 3 nm technology node, the gate, and channel of vGAAFETs need to be precisely aligned and the size controlled at the atomic-scale to achieve good device performance. In order to form Ge channels with self-aligned gate structure in VSAFETs, Ge was required to be laterally released to nano-scale size with source/drain-selective etching of Ge. Atomic layer etching (ALE) [25–27] is a promising technology that can remove ultra-thin materials through at least one self-limiting reaction step to achieve lower atomic-scale process variation. At present, the ALE for isotropic selective etching of SiGe to Si [28–30] has been reported, ALE for isotropic selective etching of Ge to GeSi has not been extensively reported. However, the ALE is not universal, and the selective ALE method depends on the recipe and it is difficult to achieve.

**Figure 1.** Schematic diagram of the basic flow of vertical Gate-all-around FET (vGAAFETs). (a) Sandwich structure and hard mask growth, (b) lithographic patterning and plasma anisotropic etching, (c) channel isotropic selective etching to form laterally depressed channels and gate gaps, (d) gate gaps filling with high-k metal gate (HKMG).

In this work, a developed wet dual-selective ALE process with selective etching of Ge and crystal-orientation selectivity of Ge oxidation was proposed. Based on the principle of atomic layer etching (ALE) and the oxidation–removal reaction of HNO $_3$  and deionized (DI) water, the characteristics of Ge $_{0.8}$ Si $_{0.2}$ -selective ALE of Ge at different temperatures were investigated systematically. The ALE process with a focus on the selective etching of Ge in p<sup>+</sup>-Ge $_{0.8}$ Si $_{0.2}$ /Ge multilayers with 70% HNO $_3$  as oxidizer and DI water as oxide removal. The saturated relative etched amount per cycle (REPC) and selectivity at different HNO $_3$  temperatures between Ge and p<sup>+</sup>-Ge $_{0.8}$ Si $_{0.2}$  were investigated in detail. The application of ALE in the formation of Ge nanowires in VSAFETs was demonstrated.

## 2. Materials and Methods

The samples were performed on 200-mm p-type Si (100) wafers with a resistivity of 8–12 Ohm·cm. The high-quality epitaxial p<sup>+</sup>-Ge<sub>0.8</sub>Si<sub>0.2</sub>/Ge vertical heterostructure multilayers started with a Ge buffer layer growth by ASM E2000 (ASM, Munich, Germany) plus RPCVD on Si wafers [20]. Dichlorosilane (SiH<sub>2</sub>Cl<sub>2</sub>), germane (10% GeH<sub>4</sub> in H<sub>2</sub>), and diborane (1% B<sub>2</sub>H<sub>6</sub> in H<sub>2</sub>) were utilized as gas precursors for Si, Ge, and B, respectively. Ge<sub>0.8</sub>Si<sub>0.2</sub> layers were in-situ doped with boron (concentration:  $1.0 \times 10^{19}$  cm<sup>-3</sup>). The growth parameters and boron content have been carefully optimized to avoid boron precipitates in the Ge<sub>0.8</sub>Si<sub>0.2</sub> layers [31]. The Ge buffer layer was grown with a two-step growth of low-high temperature (400 °C and 650 °C), and then a post-growth in situ annealing was applied at 820 °C in H<sub>2</sub> ambient [32]. Then, the p<sup>+</sup>-Ge<sub>0.8</sub>Si<sub>0.2</sub>/Ge stacks were grown at 500 °C using an adjusted gas source with H<sub>2</sub> as a carrier gas. Then, a hard

Nanomaterials **2021**, 11, 1408 3 of 15

mask with 30 nm SiN and 50 nm SiO<sub>2</sub> was deposited with plasma enhanced chemical vapor deposition (PECVD) on the epitaxial  $p^+$ -Ge<sub>0.8</sub>Si<sub>0.2</sub>/Ge stack layers. Finally, the  $p^+$ -Ge<sub>0.8</sub>Si<sub>0.2</sub>/Ge stack fins were patterned by I-line optical lithography and fabricated by using HBr-based dry anisotropic etching. Afterward, the samples were cut into small slices to facilitate the etching experiments.

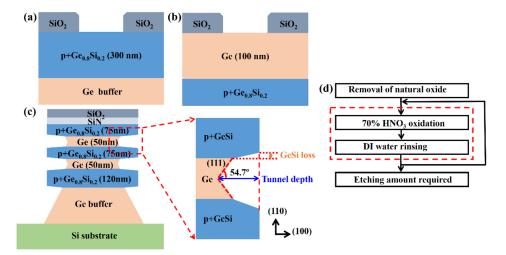

There were three kinds of samples to estimate the etch rate and selectivity between Ge and p<sup>+</sup>-Ge<sub>0.8</sub>Si<sub>0.2</sub>, as shown in Figure 2a–c. The etch rate of Ge (100 nm) and p<sup>+</sup>-Ge<sub>0.8</sub>Si<sub>0.2</sub> (300 nm) films with (100) flat surfaces were expressed by the etch rate per cycle (EPC). In order to measure the relative etch rate and selectivity of Ge and p<sup>+</sup>-Ge<sub>0.8</sub>Si<sub>0.2</sub> with ALE, a structure with (110) sidewall was fabricated and keep p<sup>+</sup>-Ge<sub>0.8</sub>Si<sub>0.2</sub>/Ge/p<sup>+</sup>- $Ge_{0.8}Si_{0.2}/Ge/p^+$ - $Ge_{0.8}Si_{0.2}$  at 120 nm/50 nm/75 nm/50 nm/75 nm, and  $p^+$ - $Ge_{0.8}Si_{0.2}$  with boron dopant concentration of  $1.0 \times 10^{19}$  cm<sup>-3</sup>. And the thickness and composition of the samples were kept constant among repetitive experiments. The prepared p+-Ge<sub>0.8</sub>Si<sub>0.2</sub>/Ge stack structure is shown in Figure 2c. The relative total etched amount (tunnel depth) and GeSi loss are shown in the insert view, selective etching of Ge at (111) planes result in a lateral angle of 54.7°. The etch selectivity between p<sup>+</sup>-Ge<sub>0.8</sub>Si<sub>0.2</sub>/Ge stacks with (110) sidewall is estimated by (tunnel depth + GeSi loss)/GeSi loss [28]. The relative etched amount per cycle (REPC) was calculated as the tunnel depth divided by the number of etching cycles. The flow diagram of ALE is shown in Figure 2d, the steps in the dashed frame are one cycle of ALE, including 70% HNO<sub>3</sub> oxidation, deionized (DI) water rinsing, and repeating the number of cycles until the required etching amount was reached. Before etching experiments, the samples were immersed in diluted BOE (dBOE, 49 wt% HF and 40 wt% NH<sub>4</sub>F with volume ratio of 1:7) for 5 min to remove the natural oxide. During the experiments, the volume of the nitric acid solution was constant at 2 L, and the DI water was with overflow rinsing. As high-concentration nitric acid is easier to decompose, the experimental process requires a high-precision density meter to monitor the concentration of HNO<sub>3</sub> solution. In view of the different oxidation mechanism of nitric acid (HNO<sub>3</sub>) concentration on Ge, the nitric acid concentration must be maintained at 70% with 5% variation in the ALE experiments compared to the continuous etching of Ge with nitric acid at low concentration. The experimental temperature was kept at 20  $^{\circ}$ C  $\pm$  0.5  $^{\circ}$ C, and the temperature with variation  $\pm 0.5$  °C of the HNO<sub>3</sub> solution was controlled by the water bath method of the cryostat at low temperature. The oxidation time  $t_{ox}$  of the control recipe is 30 s and the DI water rinsing time (oxide remove time) is set as 1 min to make sure that oxide is removed totally.

**Figure 2.** (a) Scheme of structure for  $p^+$ -Ge<sub>0.8</sub>Si<sub>0.2</sub> (a) and Ge (b) with (100) flat surface; (c) scheme of  $p^+$ -Ge<sub>0.8</sub>Si<sub>0.2</sub>/Ge stacks with SiO<sub>2</sub> and SiN as hard mask. The tunnel depth and GeSi loss are indicated in the insert view, selective etching of Ge at (111) planes result in a lateral angle of 54.7°. (d) Flow diagram of HNO<sub>3</sub>-DI water for  $p^+$ -Ge<sub>0.8</sub>Si<sub>0.2</sub>-selective etching of Ge with ALE.

Nanomaterials **2021**, 11, 1408 4 of 15

Scanning electron microscopy (SEM) was used to examine the morphology and etching depth of the samples. Transmission electron microscopy (TEM) characterized the sample to determine the layer profile and evaluate the results of wet etching. Energy dispersive spectroscopy (EDS) was employed to determine the elemental analysis of the etched layers. High-resolution X-ray diffraction (HRXRD) was used to measure the strain relaxation and examine the epitaxial quality. Atomic force microscopy (AFM) measured surface roughness.

#### 3. Results and Discussion

## 3.1. Dual-Selective Etching Ge to $p^+$ -Ge<sub>0.8</sub>Si<sub>0.2</sub> with ALE

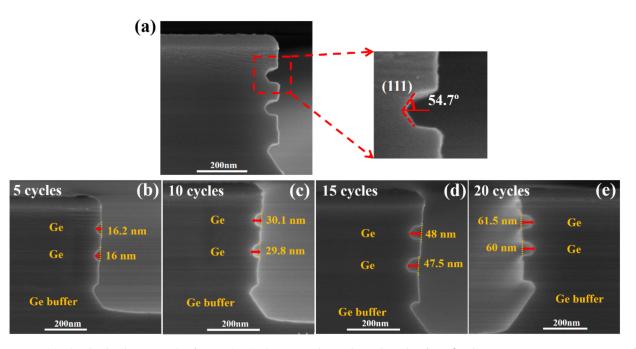

In order to form Ge channels with self-aligned gate structure in pVSAFETs, Ge was required to be laterally released to nano-scale size with ALE. First, we tried the ALE recipe of selective SiGe to Si in the previous work [28,29], using H<sub>2</sub>O<sub>2</sub> and diluted HNO<sub>3</sub> solution as oxidants to oxidize  $p^+$ -Ge<sub>0.8</sub>Si<sub>0.2</sub>/Ge stacks. However, due to the water-soluble of GeO<sub>2</sub>, GeO<sub>2</sub> generated by the reaction of Ge with H<sub>2</sub>O<sub>2</sub> and diluted HNO<sub>3</sub> solution was dissolved in water immediately, resulting in uncontrolled continuous etching [20], these recipes cannot be used as ALE recipes for Ge. Then, we used O<sub>2</sub> plasma and O<sub>3</sub> as oxidants, combined with the etchant for Ge selective etching experiments, but failed with non-selectivity (not shown). Finally, we found that (1) only a high concentration of HNO<sub>3</sub> (70% with 5% variation) as oxidant and DI water as etchant can achieve the selective ALE of Ge to  $p^+$ -Ge $_{0.8}$ Si $_{0.2}$ , and (2) 70% concentrated HNO $_3$  has crystal-orientation selectivity for the oxidation of Ge, but not for p<sup>+</sup>-Ge<sub>0.8</sub>Si<sub>0.2</sub>. The oxidation rate of HNO<sub>3</sub> on Ge surface is inversely proportional to the atomic density of the crystallographic plane, which determines the slower oxidation rate on Ge (111) planes [33,34]. Therefore, the self-saturated selective etching of Ge at (111) planes result in a lateral angle of 54.7°, as shown in the insert view of Figure 3a. Within the experimental error, this angle is equal to the theoretical angle between the (100) and (111) set of planes. A developed dual-selective ALE method, including material selectivity and crystal-orientation selective oxidation, is suitable for the selective etching of Ge in p<sup>+</sup>-Ge<sub>0.8</sub>Si<sub>0.2</sub>/Ge stacks.

**Figure 3.** (a) The dual-selective etch of Ge at (111) planes result in a lateral angle of  $54.7^{\circ}$ . The SEM cross-section images of  $p^+$ -Ge<sub>0.8</sub>Si<sub>0.2</sub>/Ge multilayers after 70% HNO<sub>3</sub>-DI water ALE at (b) 5 cycles, (c) 10 cycles, (d) 15 cycles, and (e) 20 cycles. (Oxidation time  $t_{ox} = 30$  s; temperature of HNO<sub>3</sub> = 20 °C).

Due to the ALE separated into two parts: oxidation and oxide remover. The amount of etching is determined according to the amount of oxidation, so the oxidation step is

Nanomaterials **2021**, 11, 1408 5 of 15

the key to control the etching rate. First, 70% HNO<sub>3</sub> was used to periodically oxidize the surface of the sample for time  $t_{ox}$ , showing a self-limiting surface passivation reaction, and then deionized (DI) water was used to directly remove the oxide. The oxidation of Ge in high-concentration nitric acid can be described as follows [20]:

$$Ge + 4HNO_3 \rightarrow GeO_2 \cdot H_2O + 4NO_2 \uparrow + H_2O$$

(1)

In the reaction of high-concentration nitric acid to germanium, the reaction product is GeO<sub>2</sub>·H<sub>2</sub>O. In the whole reaction process, GeO<sub>2</sub> formed at the germanium-liquid interface diffuses slowly, and enough GeO2 covers the entire germanium surface and produces passivation to prevent further corrosion of germanium [35]. Compared with ALE of SiGe to Si, the ALE of Ge to p<sup>+</sup>-Ge<sub>0.8</sub>Si<sub>0.2</sub> did not need another etchant (hydrofluoric acid or dBOE) but only DI water can directly remove oxides. To ensure the stability of the nitric acid concentration during the ALE experiment, the nitric acid concentration needs to be monitored with a high-precision density meter every 5 min. It was found that the concentration of HNO<sub>3</sub> changes by 5% within 1 h during the ALE experiment. When the nitric acid concentration changed more than 5%, that is, the nitric acid concentration is less than 65% (original nitric acid concentration is 70%), the  $p^+$ -Ge $_{0.8}Si_{0.2}$ /Ge stacks became continuous etching in HNO<sub>3</sub> solution. In order to maintain the stability and repeatability of the ALE experiment, the nitric acid solution was changed every 1 h. It can be seen that the concentration of nitric acid had a great influence on the experimental results. Since nitric acid is exothermic and volatilized when exposed to water, the sample must be dried before the next cycle in nitric acid. In order to verify whether germanium oxide is completely removed in DI water, three comparative experiments were taken at the same time: (1) 70% HNO<sub>3</sub> 30 s + DI water cleaning for 1 min, (2) 70% HNO<sub>3</sub> 30 s + DI water cleaning for 2 min and (3) 70% HNO<sub>3</sub> 30 s + DI water cleaning for 1 min + dBOE immersing for 1 min + DI water cleaning for 1 min. Excluding measurement errors, the Ge etching amounts of these three cleaning conditions were almost the same (not shown), which proved that 1 min of DI water cleaning was sufficient to remove germanium oxide without adding other etching agents. It was also proved that enough water molecules in DI water can pass through GeO<sub>2</sub> to reach the Ge-GeO<sub>2</sub> interface and strip the germanium oxide.

Samples were immersed in concentrated HNO $_3$  (70%) with oxidation time  $t_{\rm ox}=30~{\rm s}$  at HNO $_3$  temperature of 20 °C, and rinsed in DI water for at least 1 min to remove GeO $_{\rm x}$  effectively. Figure 3b–e shows the SEM cross-section images of p<sup>+</sup>-Ge $_{0.8}$ Si $_{0.2}$ /Ge stacks after etching with 5 cycles, 10 cycles, 15 cycles, and 20 cycles, respectively. Within the measurement error, the mean relative etching amounts of Ge in p<sup>+</sup>-Ge $_{0.8}$ Si $_{0.2}$ /Ge stacks were 16.1 nm, 30 nm, 47.8 nm, and 60.8 nm, respectively. The relative etching amount is linearly proportional to the number of etching cycles, and the etch rate per cycle (EPC) is independent of the etching cycle number with the mean value of 3.1 nm.

In p $^+$ -Ge $_{0.8}$ Si $_{0.2}$ /Ge stacks, the selective ALE of Ge can be performed smoothly in a 70% HNO $_3$ -DI water system. One is that the Ge layers (atoms) were oxidized preferentially by HNO $_3$  owing to the weaker Ge-Ge bond energy than those of Ge-Si and Si-Si [36–39]. Second, GeO $_2$  generated in the Ge layer is soluble in water, while SiO $_2$  generated by oxidation of the p $^+$ -Ge $_{0.8}$ Si $_{0.2}$  layer is stable and hydrophobic, and GeO $_2$  far away from the surface cannot be directly dissolved in water because of the passivation of the SiO $_2$  layer.

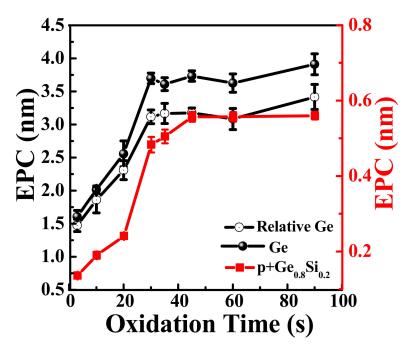

The EPC was calculated by dividing the relative etching amounts by the number of etching cycles and this experiment was carried out at HNO $_3$  temperature of 20 °C. The EPC for Ge and p $^+$ -Ge $_{0.8}$ Si $_{0.2}$  as a function of the oxidation time is shown in Figure 4. The EPC increased with the increase of oxidation time and gradually saturates when the oxidation time exceeds 30 s, indicating that the oxidation of Ge and p $^+$ -Ge $_{0.8}$ Si $_{0.2}$  in concentrated HNO $_3$  (70%) is quasi-self-limiting. When the oxidation time is 30 s, the etching selectivity between Ge and p $^+$ -Ge $_{0.8}$ Si $_{0.2}$  in (100) flat surface is 6.5, as determined from the two oxidation curves in Figure 4. The EPC of Ge and p $^+$ -Ge $_{0.8}$ Si $_{0.2}$  were 3.7 nm and 0.5 nm, respectively. The etch rate of lateral selective etching of Ge on p $^+$ -Ge $_{0.8}$ Si $_{0.2}$ /Ge stacks with (110) sidewall, which is more important in vertical device fabrication, is defined as the

Nanomaterials **2021**, 11, 1408 6 of 15

relative etched amount per cycle (REPC). Similarly, as shown in Figure 4, the REPC of Ge in the vertical structure of  $p^+$ -Ge $_{0.8}$ Si $_{0.2}$ /Ge stacks is fixed at ~3.1 nm. The estimated data in these experiments in Figure 4 show very small etching errors. Therefore, it can be verified that the ALE method is repeatable if the measurement error is taken out.

**Figure 4.** EPCs of ALE with different oxidation time for Ge and  $p^+$ -Ge<sub>0.8</sub>Si<sub>0.2</sub> (100) planes and Ge selectively etched in  $p^+$ -Ge<sub>0.8</sub>Si<sub>0.2</sub>/Ge stacks. (30 cycles; Temperature of HNO<sub>3</sub> = 20 °C; Experimental data of average values and error bars are shown in the graph).

#### 3.2. Effect of HNO<sub>3</sub> Temperature on Ge ALE

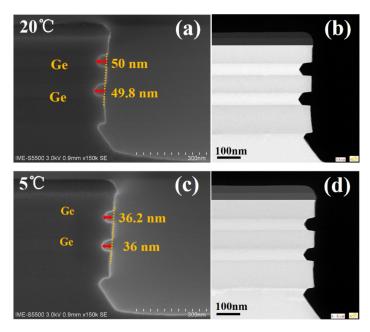

At room temperature (20 °C), the REPC of Ge (3.1 nm) is about 8 times higher than that of REPC of SiGe (0.4 nm) [29]. The etching rate is relatively fast. Since oxidation plays an important role in ALE, the effect of lowering the temperature of the nitric acid solution on the oxidation rate was studied to obtain a lower oxidation rate. Due to the strong corrosiveness of nitric acid, the temperature of the nitric acid solution is cooled by the water bath of the cryostat. In order to explore the effect of low-temperature on the REPC and selectivity between Ge and p+-Ge<sub>0.8</sub>Si<sub>0.2</sub>, experiments were carried out at HNO<sub>3</sub> temperature of 5 °C, 10 °C, 15 °C, and 20 °C, respectively. The low-temperature etching morphology was characterized by SEM and TEM. As shown in Figure 5, Ge ALE at 20 °C and 5 °C both exhibit dual-selectivity (material and crystal-orientation selectivity). The TEM results show the clear layering of the p<sup>+</sup>-Ge<sub>0.8</sub>Si<sub>0.2</sub>/Ge stacks and the etching morphology corresponding to the SEM characterization. The oxidation time was  $t_{ox} = 30 \text{ s}$ , where the cycles of 20 °C and 5 °C were 15 cycles and 20 cycles, respectively, and the etching amount of Ge is 50 nm and 36 nm, respectively. Experiments have proved that low temperature can reduce the oxidation rate of nitric acid without changing the etching morphology, which is an effective method to reduce REPC of Ge.

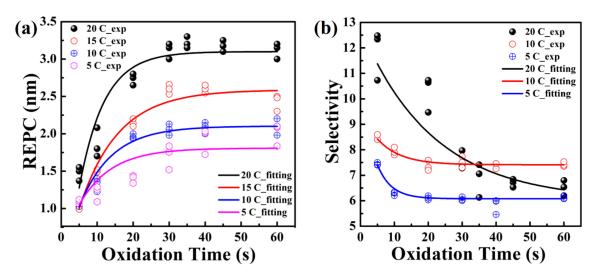

The REPC curves of ALE at different HNO<sub>3</sub> temperatures (20 °C, 15 °C, 10 °C, and 5 °C) in p<sup>+</sup>-Ge<sub>0.8</sub>Si<sub>0.2</sub>/Ge multilayers are shown in Figure 6a. As the temperature of HNO<sub>3</sub> decreased from 20 °C to 5 °C, REPC decreased from 3.1 nm to 1.8 nm. With the HNO<sub>3</sub> temperature reducing to 10 °C, the REPC of Ge was reduced to 2 nm. Similarly, the REPCs at all four temperatures reached saturation when the oxidation time exceeded 30 s, which is the quasi-self-limiting process. Due to the temperature sensitivity of the Ge oxidation reaction, the saturated oxide will be thinner with the lower HNO<sub>3</sub> temperature. The temperature with variation  $\pm$ 0.5 °C was controlled by the water bath of the low-constant temp tank. According to the corrosion model proposed by Seidei [40], its point of view was

Nanomaterials **2021**, 11, 1408 7 of 15

to attribute chemical reactions to differences in energy. When the temperature of the  $HNO_3$  decreased, the energy difference between its molecular kinetic energy and the surface activation energy of the sample became smaller, so the oxidation rate became slower.

**Figure 5.** The SEM and TEM images of etching profile of  $p^+$ -Ge<sub>0.8</sub>Si<sub>0.2</sub>/Ge multilayers after ALE at (a,b) 15 cycles (temperature of HNO<sub>3</sub> = 20 °C); (c,d) 20 cycles (temperature of HNO<sub>3</sub> = 5 °C). The oxidation time  $t_{ox}$  = 30 s.

**Figure 6.** (a) The REPC of  $p^+$ -Ge<sub>0.8</sub>Si<sub>0.2</sub>/Ge at different HNO<sub>3</sub> temperatures (20 °C, 15 °C, 10 °C, 5 °C) as a function of oxidation time. (b) The selectivity between  $p^+$ -Ge<sub>0.8</sub>Si<sub>0.2</sub> and Ge at different HNO<sub>3</sub> temperatures (20 °C, 10 °C, and 5 °C) as a function of oxidation time. The scatters and solid lines represent the experimental data and fitting curves of the experimental data.

Figure 6b shows the etching selectivity of  $p^+$ -Ge<sub>0.8</sub>Si<sub>0.2</sub>/Ge stacks at different HNO<sub>3</sub> temperatures (5 °C, 10 °C, and 20 °C). The selectivity is defined as [28]:

$$Selectivity = \frac{GeSiloss + Tuneldepth}{GeSiloss}$$

(2)

where GeSi loss is vertical etching amount of GeSi, which is equal to the horizontal etching amount, and the tunnel depth is the relative total etched amount of Ge to  $Ge_{0.8}Si_{0.2}$ , as

Nanomaterials **2021**, 11, 1408 8 of 15

shown in Figure 2c. The experimental data were obtained by measuring the SEM images of the etching profile in the  $p^+$ -Ge<sub>0.8</sub>Si<sub>0.2</sub>/Ge stacks with (110) sidewalls. The mean values of  $p^+$ -Ge<sub>0.8</sub>Si<sub>0.2</sub>/Ge selectivity at HNO<sub>3</sub> temperatures of 20 °C, 10 °C, and 5 °C were 6.5, 7.4, and 6.1, respectively. The results show that Ge ALE can achieve a high selectivity of Ge to Ge<sub>0.8</sub>Si<sub>0.2</sub>, independent of HNO<sub>3</sub> temperature. At HNO<sub>3</sub> temperatures of 20 °C, when the oxidation time increased, there was enough time for HNO<sub>3</sub> to destroy and oxidize the Si-Si bonds and Ge-Si bonds. After 30 cycles of ALE, the etching amount of Ge<sub>0.8</sub>Si<sub>0.2</sub> became larger, and the EPC became larger accordingly. Thereby reducing the selectivity of Ge to Ge<sub>0.8</sub>Si<sub>0.2</sub>, and reached saturation when the oxidation time was 45 s. At low temperatures, due to the decrease of the molecular kinetic energy of HNO<sub>3</sub>, the selectivity of Ge to Ge<sub>0.8</sub>Si<sub>0.2</sub> does not change much with time and reached saturation in about 20 s of oxidation time.

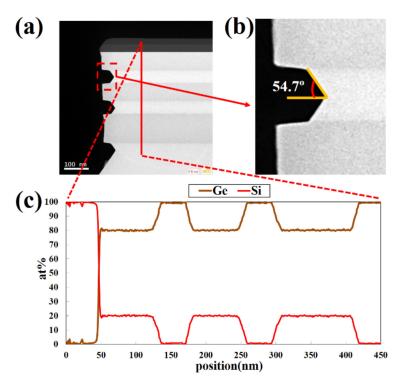

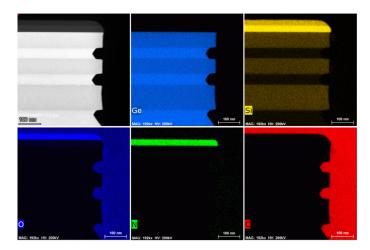

#### 3.3. Structure Characterization and Material Quality Analysis

In order to more accurately characterize the Ge ALE results in this study, the quality of the epitaxial layers and the etching morphology and element analysis of the  $p^+$ -Ge<sub>0.8</sub>Si<sub>0.2</sub>/Ge stack structure were characterized by HRTEM and EDS. Figure 7 shows the cross-section TEM micrograph and elemental analysis of the etched area of  $p^+$ -Ge<sub>0.8</sub>Si<sub>0.2</sub>/Ge stacks with (110) sidewalls with Ge ALE. The results show that the Ge content in the GeSi layer maintains at 80%, and there is no mixing between the layers. The relative etching amount is the same as that characterized by SEM. It was further verified that the selective etching of Ge on (111) planes resulted in a lateral angle of  $54.7^{\circ}$ . The EDS mapping of Figure 8 shows that the boundaries of the layers are obvious, the thickness of the film is consistent with the design, and there is no obvious element diffusion between the layers. The germanium content of the Ge layer is almost 100%. Si element is distributed in the layers of SiO<sub>2</sub>, SIN, and Ge<sub>0.8</sub>Si<sub>0.2</sub>, O mainly exists in the hard mask of SiO<sub>2</sub>.

**Figure 7.** (a,b) TEM images of etching profile, and (c) EDS analysis with line scanning of Si and Ge in vertical orientation of the Ge buffer/p $^+$ -Ge<sub>0.8</sub>Si<sub>0.2</sub>/Ge stack structure. The selective etching of Ge at (111) planes results in a lateral angle of 54.7 $^\circ$ . (20 cycles; temperature of HNO<sub>3</sub> = 15 $^\circ$ C; oxidation time  $t_{ox}$  = 30 s).

Nanomaterials **2021**, 11, 1408 9 of 15

**Figure 8.** EDS mapping near etching regions with elements Ge, Si, O, N, and C, the sample etching for 15 cycles (oxidation time  $t_{ox} = 30$  s; temperature of HNO<sub>3</sub> = 20 °C).

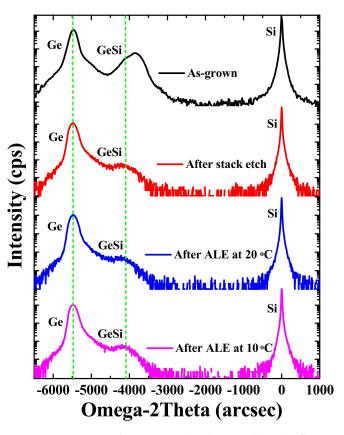

Crystallinity and strain have a strong impact on channel carrier mobility and device performance, therefore, crystal quality and strain relaxation of the sample before and after the etching steps has been studied. HRXRD is a technique that is widely used for the detection of defects in crystal materials [41]. Figure 9 displays rocking curves (RCs) measured around the (004) reflection on stack samples: as-grown, after vertical stack etch, after ALE at 20 °C, and after ALE at 10 °C. For the as-grown sample, the Ge<sub>0.8</sub>Si<sub>0.2</sub> and Ge peaks were intense with low Full-width-of-half-Maximum (FWHM) showing good crystalline quality of Ge<sub>0.8</sub>Si<sub>0.2</sub>/Ge stack. Since most of the film layer was removed by etching, the intensity of the Ge<sub>0.8</sub>Si<sub>0.2</sub> peak was weaker, while the Ge peak was still strong due to the presence of the Ge buffer layer. Compared with the as-grown sample, the Ge<sub>0.8</sub>Si<sub>0.2</sub> peak shifts towards the Ge peak after stack etching. This indicates that (tensile-strained) Ge<sub>0.8</sub>Si<sub>0.2</sub> is partially relaxed after the vertical etching. Moreover, the Ge peak became asymmetric after vertical etch and the amount of strain in the Ge was minor. No further shift of Ge<sub>0.8</sub>Si<sub>0.2</sub> or Ge peak was detected after ALE etching, which indicates that there was no further strain relaxation after lateral etching at 20 °C and 10 °C.

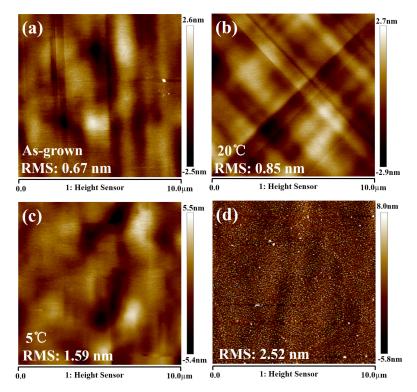

Since Ge will be used as the channel material in vertical GAAFETs, the etched germanium surface can be used as the channel interface. Due to the scattering of the surface roughness, the channel surface roughness will cause gate oxide integrity degradation and mobility degradation. Therefore, it is necessary to measure the surface roughness of Ge that has been etched many times by DI water. Figure 10 shows the AFM images of the flat (100) Ge surface with as-grown epi-Ge, after etching with ALE at HNO<sub>3</sub> temperatures of 20 °C (20 cycles), after etching with ALE at HNO<sub>3</sub> temperatures of 5 °C (20 cycles), and after etching with HF:HNO<sub>3</sub>:CH<sub>3</sub>COOH mixtures. It was found that the root mean square (RMS) roughness of the ALE process at 20 °C HNO<sub>3</sub> temperatures is 0.85 nm, which is similar to that of the as-grown sample (RMS of 0.67 nm). However, the RMS increases as the temperature of HNO<sub>3</sub> decreases. The roughness is very poor etching with HF:HNO<sub>3</sub>:CH<sub>3</sub>COOH mixtures. Table 1 shows the comparison of the RMS of flat (100) Ge surfaces of as-grown and different etching processes. It is demonstrated that the surface roughness of ALE is better than chemical continuous etching. The smoothing effect can be explained by a model, where the depressions on the surface asperity are preferentially oxidized, and the protrusions on the asperity are preferentially etched. When the temperature of nitric acid decreases, the oxidizing ability decreases, resulting in uneven surface oxidation. Finally, the height difference between the depressions and the protrusions was increased during the etching, so the surface after the low-temperature treatment is rougher. In summary, we need to make a trade-off between the etching rate and the surface roughness and choose a suitable temperature for ALE etching. Because of the equipment, the preparation process of our devices was mainly carried out at room temperature.

Nanomaterials **2021**, 11, 1408 10 of 15

**Figure 9.** HRXRD rocking curves (RCs) around (004) reflection of stack samples of as-grown, after vertical stack etch, after ALE at 20  $^{\circ}$ C, and after ALE at 10  $^{\circ}$ C with 20 cycles.

**Figure 10.** Typical AFM images ( $10 \times 10 \ \mu m^2$ ) of flat (100) Ge surfaces before and after the etching process: (a) as–grown; (b) ALE with 20 cycles (temperature of HNO<sub>3</sub> =  $20 \ ^{\circ}$ C); (c) ALE with 20 cycles (temperature of HNO<sub>3</sub> =  $5 \ ^{\circ}$ C); (d) HF:HNO<sub>3</sub>:CH<sub>3</sub>COOH mixtures.

| <b>Table 1.</b> RMS of flat (100) Ge surfaces with as-grown film and different etching processe | <b>Table 1.</b> RMS of flat | (100) Ge surfa | ces with as-grow | n film and differ | ent etching processes |

|-------------------------------------------------------------------------------------------------|-----------------------------|----------------|------------------|-------------------|-----------------------|

|-------------------------------------------------------------------------------------------------|-----------------------------|----------------|------------------|-------------------|-----------------------|

|          | As-Grown | 20 °C ALE | 15 °C ALE | 10 $^{\circ}$ C ALE | 5 °C ALE | HF:HNO <sub>3</sub> :CH <sub>3</sub> COOH |

|----------|----------|-----------|-----------|---------------------|----------|-------------------------------------------|

| RMS (nm) | 0.67     | 0.85      | 1.12      | 1.39                | 1.59     | 2.52                                      |

## 3.4. Application of ALE for Ge Vertical Sandwich GAAFETs (VSAFETs)

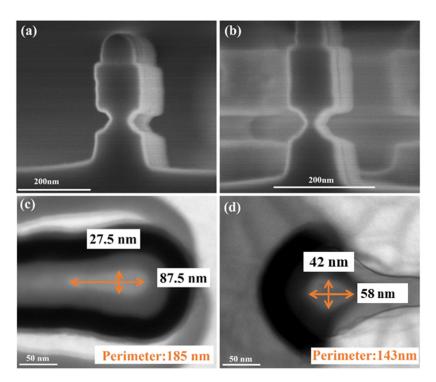

The ALE of Ge selective to  $p^+$ -Ge<sub>0.8</sub>Si<sub>0.2</sub> will be adopted in the vertical sandwich GAAFETs (VSAFETs) to form Ge channel nanowire, as mentioned in the introduction. The cross-sectional SEM images of the  $p^+$ -Ge<sub>0.8</sub>Si<sub>0.2</sub>/Ge/ $p^+$ -Ge<sub>0.8</sub>Si<sub>0.2</sub> sandwich structure forming vertical nanowire are shown in Figure 11a,b. Figure 11a,b respectively show a 40 nm Ge channel with 15 cycles of ALE and a 15 nm Ge channel with 20 cycles of ALE, implying the well-controlled Ge channel size with ALE. Figure 11c,d show the TEM top view for NS with perimeter 185 nm and NW with perimeter 143 nm formed by 30 cycles of ALE, respectively. The TEM top views were cut at the top drain, the brighter part is the channel, and the black part is metal. The vertical nanosheet (NS) and nanowire (NW) shown in Figure 11c,d were obtained on the same wafer, and the channel size and shape are determined by initial dimensions (defined by electron-beam lithography) and the dual-selective ALE.

**Figure 11.** Cross-sectional SEM images of Ge selective etching with ALE, (a) 40 nm Ge channel with 15 cycles of ALE, and (b) 15 nm Ge channel with 20 cycles of ALE. Cross-sectional TEM top views of Ge VSAFETs: (c) NS with perimeter 185 nm, (d) NW with a square cross-section with perimeter 143 nm. Oxidation time  $t_{ox} = 30$  s and temperature of HNO<sub>3</sub> = 20 °C.

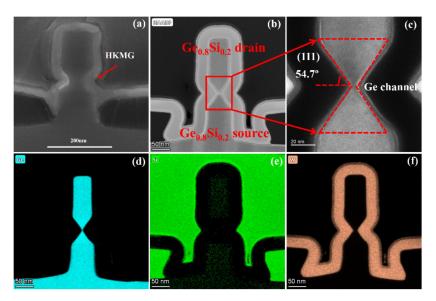

Figure 12a,b show the cross-sectional SEM and TEM images of the filled high-k metal gate (HKMG) of the gate gap formed by selective etching of the channel with ALE, respectively. Figure 12c shows the TEM image of the gate stack on the side-wall of the hourglass-shaped Ge channel. As shown in Figure 12d–f, the EDX mapping of elements Ge, Si, and W shows sharp contours, proving the absence of element intermixing. The self-saturated dual-selective etch of Ge at (111) planes result in an hourglass-shape with a lateral angle of 54.7°. The current transports along the (111) planes of the hourglass-shaped Ge channel.

**Figure 12.** (a) SEM and (b) TEM images of Ge pVSAFET with gate gaps filling high-k metal gate (HKMG). (c) The self-saturated dual-selective etch of Ge at (111) planes result in an hourglass shape with a lateral angle of 54.7°. Energy-dispersive Xray spectroscopy (EDX) mapping of (d) Ge (cyan), (e) Si (cyan), and (f) W (yellow) atoms with sharp contours.

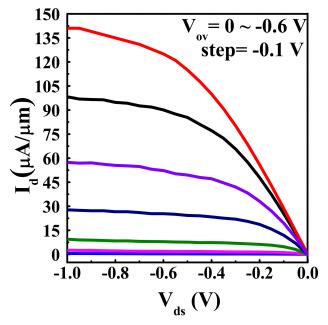

In this stage, a vertical sandwich GAAFET (VSAFET) was processed by ALE method when a Ge nanosheet (NS) with thickness of ~27.5 nm was the channel material as shown in Figure 11c. The process flow of the transistor includes sandwich structure growth, lithographic patterning and plasma anisotropic etching, channel selective etching to form channels, and filling of the high-k metal gate (HKMG) by ALD [14]. Figure 13 illustrates the  $I_d-V_{ds}$  output characteristic curve when the  $I_{on}$  is 141  $\mu A/um$  ( $I_d@V_{ov}=V_{gs}-V_t=-0.6~V, V_{ds}=-1.0~V)$ . It is important to emphasize that these results are preliminary for Ge pVSAFETs, and the device performance will be further studied in the future.

**Figure 13.**  $I_d$ – $V_{ds}$  output characteristic curves for Ge pVSAFET with NS thickness of ~27.5 nm,  $V_{ov}$  from 0 to -0.6 V, showing characteristic current saturation behavior.  $I_d$  normalizes with the perimeter of NS.

#### 4. Conclusions

In this work, a developed wet dual-selective ALE process with selective etching of Ge and crystal-orientation selectivity of Ge oxidation was proposed. With the oxidation-removal reaction of 70% HNO3 and deionized (DI) water, the characteristics of  $Ge_{0.8}Si_{0.2}$ -selective ALE of Ge at different HNO3 temperatures were investigated systematically. In p<sup>+</sup>-Ge<sub>0.8</sub>Si<sub>0.2</sub>/Ge stacks with (110) sidewalls, the saturated relative etched amount per cycle (REPC) of Ge was 3.1 nm and the saturated etching selectivity was 6.5 at an HNO3 temperature of 20 °C. The etch rate and the selectivity were affected by HNO3 temperatures. As the HNO3 temperature decreased to 10 °C, the REPC of Ge was decreased to 2 nm and the selectivity remained at about 7.4. The Ge channel size in the VSAFETs was well-controlled by ALE. The hourglass-shaped channel of the VSAFETs is formed by the dual-selective ALE of Ge, narrow in the middle and wide close to S/D. Finally, the preliminary  $I_d$ – $V_{ds}$  output characteristic curve of Ge pVSAFET was demonstrated.

**Author Contributions:** Conceptualization, L.X., H.Z., G.W. and H.H.R.; Data curation, L.X.; Funding acquisition, H.Z.; Methodology, L.X., Y.Z., X.A., J.L., A.D., Z.K., Q.W., S.L., C.L., Y.L., and W.H.; Project administration, H.Z.; Supervision, H.Z., G.W., and H.H.R.; Writing—original draft, L.X.; Writing—review & editing, L.X., H.Z., G.W., and H.H.R. All authors have read and agreed to the published version of the manuscript.

**Funding:** This work was supported by the Academy of Integrated Circuit Innovation under Grant No. Y7YC01X001 and E0YC03X001, the National Key Research and Development Program of China (Grant No. 2016YFA0301701), the Youth Innovation Promotion Association of CAS (Grant No. Y2020037), the National Natural Science Foundation of China (Grant No. 92064002), the Guangdong Greater Bay Area Institute of Integrated Circuit and System (Grant No. 2019B0909006) and the projects of the construction of new research and development institutions (Grant No. 2019B090904015).

**Data Availability Statement:** The data presented in this study are available on request from the corresponding author.

**Conflicts of Interest:** The authors declare no conflict of interest.

### References

- 1. Radamson, H.H.; Zhu, H.L.; Wu, Z.H.; He, X.B.; Lin, H.X.; Liu, J.B.; Xiang, J.J.; Kong, Z.Z.; Wang, G.L.; Li, J.; et al. State of the Art and Future Perspectives in Advanced CMOS Technology. *Nanomaterials* **2020**, *10*, 1555. [CrossRef] [PubMed]

- 2. Radamson, H.H. *Monolithic Nanoscale Photonics-Electronics Integration in Silicon and Other Group IV Elements*; Academic Press: Cambridge, MA, USA, 2014; ISBN 978-0124199750.

- 3. Liu, M.S.; Schlykow, V.; Hartmann, J.M.; Knoch, J.; Grützmacher, D.; Buca, D.; Zhao, Q.T. Vertical Heterojunction  $Ge_{0.92}Sn_{0.08}/Ge$  GAA Nanowire pMOSFETs: Low SS of 67 mV/dec, Small DIBL of 24 mV/V and Highest  $G_{m, ext}$  of 870 μS/μm. In Proceedings of the IEEE Symposium on VLSI Technology, Honolulu, HI, USA, 16–19 June 2020; pp. 1–2. [CrossRef]

- 4. Loubet, N.; Hook, T.; Montanini, P.; Yeung, C.-W.; Kanakasabapathy, S.; Guillom, M.; Yamashita, T.; Zhang, J.; Miao, X.; Wang, J.; et al. Stacked nanosheet gate-all-around transistor to enable scaling beyond FinFET. *Symp. VLSI Technol.* **2017**, T230–T231. [CrossRef]

- 5. Radamson, H.H.; Zhang, Y.B.; He, X.B.; Cui, S.H.; Li, J.J.; Xiang, J.J.; Liu, J.B.; Gu, S.H.; Wang, G.L. The Challenges of Advanced CMOS Process from 2D to 3D. *Appl. Sci.* 2017, 7, 1047. [CrossRef]

- 6. Gu, J.J.; Wang, X.W.; Shao, J.; Neal, A.T.; Manfra, M.J.; Gordon, R.G.; Ye, P.D. III-V gate-all-around nanowire MOSFET process technology: From 3D to 4D. *Int. Electron Devices Meet.* (*IEDM*) **2012**, 23.7.1–23.7.4. [CrossRef]

- 7. Radamson, H.H.; Simoen, E.; Luo, J.; Zhao, C. *Past, Present and Future of CMOS*; Woodhead Publishing: Cambridge, UK, 2018; pp. 95–114. ISBN 978-008-102-139-2.

- 8. Singh, N.; Buddharaju, K.D.; Manhas, S.K.; Agarwal, A.; Rustagi, S.C.; Lo, G.Q.; Balasubramanian, N.; Kwong, D.L. Si, SiGe nanowire devices by top-down technology and their applications. *IEEE Trans. Electron. Devices* **2008**, *55*, 3107–3118. [CrossRef]

- 9. Xu, W.J.; Wong, H.; Kakushima, K.; Iwai, H. Quasi-analytical model of ballistic cylindrical surrounding gate nanowire MOSFET. *Microelectron. Eng.* **2015**, *138*, 111–117. [CrossRef]

- 10. Bae, G.; Bae, D.I.; Kang, M.; Hwang, S.M.; Kim, S.S.; Seo, B.; Kwon, T.Y.; Lee, T.J.; Moon, C.; Choi, Y.M.; et al. 3 nm GAA technology featuring multi-bridge-channel FET for low power and high-performance applications. In Proceedings of the 2018 IEEE International Electron Devices Meeting (IEDM), San Francisco, CA, USA, 1–5 December 2018; pp. 28.7.1–28.7.4. [CrossRef]

- 11. Veloso, A.; Altamirano-Sánchez, E.; Brus, S.; Chan, B.T.; Cupak, M.; Dehan, M.; Delvaux, C.; Devriendt, K.; Eneman, G.; Ercken, M.; et al. Vertical Nanowire FET Integration and Device Aspects. *ECS Trans.* **2016**, *72*, 31–42. [CrossRef]

12. Radamson, H.H.; He, X.B.; Zhang, Q.Z.; Liu, J.B.; Cui, H.S.; Xiang, J.J.; Kong, Z.Z.; Xiong, W.; Li, J.; Gao, J.; et al. Miniaturization of CMOS. *Micromachines* **2019**, *10*, 293. [CrossRef]

- 13. Toriumi, A.; Tabata, T.; Lee, C.H.; Nishimura, T.; Kita, K.; Nagashio, K. Opportunities and challenges for Ge CMOS-Control of interfacing field on Ge is a key. *Microelectron. Eng.* **2009**, *86*, 1571–1576. [CrossRef]

- 14. Yin, X.G.; Zhang, Y.K.; Zhu, H.L.; Wang, G.L.; Li, J.J.; Du, A.Y.; Li, C.; Zhao, L.H.; Huang, W.X.; Yang, H.; et al. Vertical Sandwich Gate-All-Around Field-Effect Transistors with Self-Aligned High-k Metal Gates and Small Effective-Gate-Length Variation. *IEEE Electron Device Lett.* 2020, 41, 8–11. [CrossRef]

- 15. Zhang, Y.K.; Ai, X.Z.; Yin, X.G.; Zhu, H.L.; Yang, H.; Wang, G.L.; Li, J.J.; Du, A.Y.; Li, C.; Huang, W.X.; et al. Vertical Sandwich GAA FETs with Self Aligned High-k Metal Gate Made by Quasi Atomic Layer Etching Process. *IEEE Trans. Electron Devices* 2021. [CrossRef]

- 16. Porret, C.; Vohra, A.; Sebaai, F.; Douhard, B.; Hikavyy, A.; Loo, R. A New Method to Fabricate Ge Nanowires: Selective Lateral Etching of GeSn:P/Ge Multi-Stacks. *Solid State Phenom.* **2018**, *282*, 113–118. [CrossRef]

- 17. Fischer, A.C.; Belova, L.M.; Rikers, Y.G.M.; Malm, B.G.; Radamson, H.H.; Kolahdouz, M.; Gylfason, K.B.; Stemme, G.; Niklaus, F. 3D free-form patterning of silicon by ion implantation, silicon deposition and selective silicon etching. *Adv. Funct. Mater.* **2012**, 22, 4004–4008. [CrossRef]

- Gupta, S.; Chen, R.; Huang, Y.C.; Kim, Y.; Sanchez, E.; Harris, J.S.; Saraswat, K.C. Highly Selective Dry Etching of Germanium over Germanium–Tin (Ge<sub>1-x</sub>Sn<sub>x</sub>): A Novel Route for Ge<sub>1-x</sub>Sn<sub>x</sub> Nanostructure Fabrication. *Nano Lett.* 2013, 13, 3783–3790. [CrossRef]

- 19. Lee, Y.J.; Hou, F.J.; Chuang, S.S.; Hsueh, F.K.; Kao, K.H.; Sung, P.J.; Yuan, W.Y.; Yao, J.Y.; Lu, Y.C.; Lin, K.L.; et al. Diamond-shaped Ge and Ge<sub>0.9</sub>Si<sub>0.1</sub> Gate-All-Around Nanowire FETs with Four {111} Facets by Dry Etch Technology. In Proceedings of the 2015 IEEE International Electron Devices Meeting (IEDM), Washington, DC, USA, 7–9 December 2015; pp. 15.1.1–15.1.4. [CrossRef]

- 20. Xie, L.; Zhu, H.L.; Zhang, Y.K.; Ai, X.Z.; Wang, G.L.; Li, J.J.; Du, A.Y.; Kong, Z.Z.; Yin, X.G.; Li, C.; et al. Strained Si<sub>0.2</sub>Ge<sub>0.8</sub>/Ge multilayer Stacks Epitaxially Grown on a Low-/High-Temperature Ge Buffer Layer and Selective Wet-Etching of Germanium. *Nanomaterials* **2020**, *10*, 1715. [CrossRef]

- 21. Sebaai, F.; Witters, L.; Holsteyns, F.; Wostyn, K.; Rip, J.; Yukifumi, Y.; Lieten, R.R.; Bilodeau, S.; Cooper, E. Wet Selective SiGe Etch to Enable Ge Nanowire Formation. *Solid State Phenom.* **2016**, 255, 3–7. [CrossRef]

- 22. Liu, W.D.; Lee, Y.C.; Sekiguchi, R.; Yoshida, Y.; Komori, K.; Wostyn, K.; Sebaai, F.; Holsteyns, F. Selective Wet Etching in Fabricating SiGe and Ge Nanowires for Gate-All-Around MOSFETs. *Solid State Phenom.* **2018**, 282, 101–106. [CrossRef]

- 23. Holländer, B.; Buca, D.; Mantl, S.; Hartmann, J.M. Wet Chemical Etching of Si, Si<sub>1-x</sub>Ge<sub>x</sub>, and Ge in HF: H<sub>2</sub>O<sub>2</sub>:CH<sub>3</sub>COOH. *J. Electrochem. Soc.* **2010**, 157, H643–H646. [CrossRef]

- 24. Witters, L.; Arimura, H.; Sebaai, F.; Hikavyy, A.; Milenin, A.P.; Loo, R.; De Keersgieter, A.; Eneman, G.; Schram, T.; Wostyn, K.; et al. Strained Germanium Gate-All-Around pMOS Device Demonstration Using Selective Wire Release Etch Prior to Replacement Metal Gate Deposition. *IEEE Trans. Electron Devices* **2017**, *64*, 4587–4593. [CrossRef]

- 25. Kanarika, K.J.; Tan, S.; Yang, W.; Kim, T.; Lill, T.; Kabansky, A.; Hudson, E.A.; Ohba, T.; Nojiri, K.; Yu, J.; et al. Predicting synergy in atomic layer etching. *J. Vac. Sci. Technol. A* **2017**, *35*, 05C302. [CrossRef]

- 26. Kanarika, K.J.; Lill, T.; Hudson, E.A.; Sriraman, S.; Tan, S.; Marks, J.; Vahedi, V.; Gottscho, R.A. Overview of atomic layer etching in the semiconductor industry. *J. Vac. Sci. Technol. A* **2015**, *33*, 020802. [CrossRef]

- 27. Ikeda, K.; Imai, S.; Matsumura, M. Atomic layer etching of germanium. Appl. Surf. Sci. 1997, 112, 87–91. [CrossRef]

- 28. Li, C.; Zhu, H.L.; Zhang, Y.K.; Yin, X.G.; Jia, K.P.; Li, J.J.; Wang, G.L.; Kong, Z.Z.; Du, A.Y.; Yang, T.Z.; et al. Selective Digital Etching of Silicon–Germanium Using Nitric and Hydrofluoric Acids. *ACS Appl. Mater. Interfaces* **2020**, *12*, 48170–48178. [CrossRef] [PubMed]

- 29. Yin, X.G.; Zhu, H.L.; Zhao, L.H.; Wang, G.L.; Li, C.; Huang, W.X.; Zhang, Y.K.; Jia, K.P.; Li, J.J.; Radamson, H.H. Study of Isotropic and Si-Selective Quasi Atomic Layer Etching of Si<sub>1-x</sub>Ge<sub>x</sub>. *ECS J. Solid-State Sci. Technol.* **2020**. [CrossRef]

- 30. Li, Y.Y.; Zhu, H.L.; Kong, Z.Z.; Zhang, Y.K.; Ai, X.Z.; Wang, G.L.; Wang, Q.; Liu, Z.Y.; Lu, S.S.; Xie, L.; et al. The Effect of Doping on the Digital Etching of Silicon-Selective Silicon-Germanium Using Nitric Acids. *Nanomaterials* **2021**, *11*, 1209. [CrossRef]

- 31. Radamson, H.H.; Joelsson, K.B.; Ni, W.-X.; Hultman, L.; Hansson, G.V. Characterization of highly boron-doped Si,  $Si_{1-x}Ge_x$  and Ge layers by high-resolution transmission electron microscopy. *J. Cryst. Growth* **1995**, *157*, 80–84. [CrossRef]

- 32. Du, Y.; Kong, Z.Z.; Toprak, M.S.; Wang, G.L.; Miao, Y.H.; Xu, B.Q.; Yu, J.H.; Li, B.; Lin, H.X.; Han, J.H.; et al. Investigation of the Heteroepitaxial Process Optimization of Ge Layers on Si (001) by RPCVD. *Nanomaterials* **2021**, *11*, 928. [CrossRef]

- 33. Prabhakaran, K.; Ogino, T. Oxidation of Ge (100) and Ge (ll1) surfaces: An UPS and XPS study. *Surf. Sci.* **1995**, 325, 263–271. [CrossRef]

- 34. Wostyn, K.; Sebaai, F.; Rip, J.; Mertens, H.; Witters, L.; Loo, R.; Hikavyy, A.; Milenin, A.; Horiguchi, N.; Collaert, N.; et al. Selective Etch of Si and SiGe for Gate All-Around Device Architecture. *ECS Trans.* **2015**, *69*, 147–152. [CrossRef]

- 35. Cretella, M.C.; Gatos, H.C. The Reaction of Germanium with Nitric Acid Solutions. J. Electrochem. Soc. 1958, 105, 487. [CrossRef]

- 36. Xue, Z.Y.; Wei, X.; Liu, L.J.; Chen, D.; Zhang, B.; Zhang, M.; Wang, X. Etch characteristics of Si<sub>1-x</sub>Ge<sub>x</sub> films in HNO<sub>3</sub>: H<sub>2</sub>O: HF. *Sci. China Technol. Sci.* **2011**, *54*, 2802. [CrossRef]

- 37. Koyama, K.; Hiroi, M.; Tatsumi, T.; Hirayama, H. Etching characteristics of Si<sub>1-x</sub>Ge<sub>x</sub> alloy in ammoniac wet cleaning. *Appl. Phys. Lett.* **1990**, *57*, 2202–2204. [CrossRef]

Nanomaterials **2021**, 11, 1408 15 of 15

38. Spadafora, M.; Privitera, G.; Terrasi, A. Oxidation rate enhancement of SiGe epitaxial films oxidized in dry ambient. *Appl. Phys. Lett.* **2003**, *83*, 3713–3715. [CrossRef]

- 39. Yeo, C.C.; Cho, B.J.; Gao, F.; Lee, S.J.; Lee, M.H.; Yu, C.Y.; Liu, C.W.; Tang, L.J.; Lee, T.W. Electron mobility enhancement using ultrathin pure Ge on Si substrate. *IEEE Electron Device Lett.* **2005**, *26*, 761–763. [CrossRef]

- 40. Seidel, H.; Csepregi, L.; Heuberger, A.; Baumgartel, H. Anisotropic etching of crystalline silicon in alkaline solutions. *J. Electrochem. Soc.* **1990**, *137*, 3612.

- 41. Radamson, H.H.; Hallstedt, J. Application of high-resolution X-ray diffraction for detecting defects in SiGe (C) materials. *J. Phys. Condens. Matter* **2005**, *17*, S2315–S2322. [CrossRef]