Article

# Effective Management System for Solar PV Using Real-Time Data with Hybrid Energy Storage System

G. V. Brahmendra Kumar <sup>1</sup>, Palanisamy Kaliannan <sup>1,\*</sup>, Sanjeevikumar Padmanaban <sup>2,\*</sup>, Jens Bo Holm-Nielsen <sup>2</sup> and Frede Blaabjerg <sup>3</sup>

- School of Electrical Engineering, Vellore Institute of Technology, Vellore 632014, India; brahmendrakumar.g@gmail.com

- Center for Bioenergy and Green Engineering, Department of Energy Technology, Aalborg University, 6700 Esbjerg, Denmark; jhn@et.aau.dk

- Center of Reliable Power Electronics (CORPE), Department of Energy Technology, Aalborg University, 6700 Esbjerg, Denmark; fbl@et.aau.dk

- \* Correspondence: kpalanisamy@vit.ac.in (P.K.); san@et.aau.dk (S.P.)

Received: 11 December 2019; Accepted: 31 January 2020; Published: 7 February 2020

Abstract: This paper proposes an effective management system for stand-alone solar photovoltaic (PV) using real-time data with Hybrid Energy Storage System (HESS). The abrupt movement of fleeting clouds often gives rise to PV power output fluctuations which in turn affect the power quality and system stability due to scattered solar radiation reception. These variations can limit through a ramp-limit controller and employing a DC link controller to maintain the stable DC link voltage. The battery is used in the system for continuous power application and the sudden variations in charging and discharging of battery power can create stress on the battery. These sudden changes in a battery will be removed by the super-capacitor (SC) unit and achieves a fast DC link voltage regulation. Hence, the high energy and power density devices such as battery and SC units will deliver more stable power into the system. The control scheme is tested in Matlab/Simulink and validated by Real-Time Hardware-in-Loop (HIL) simulator using periodic one-minute data for one year from the solar PV power plant from real-time.

Keywords: solar PV smoothening; fluctuations; ramp-limit controller; power management; HESS

## 1. Introduction

Installations of solar photovoltaic (PV) and wind are steadily increasing due to exhaustion of fossil fuels, its price variation, instability in trading of coal/crude oil, and issues of greenhouse gases [1]. Utilizing more renewable energy sources (RES) minimizes the dependency on imported fossil fuels and creates sustainable energy production. However, RES is highly intermittent and fluctuating in nature. Particularly, the PV system is highly reliant on climatic or geometrical conditions and output power severely oscillates during bad climatic situations. The higher fluctuations in the injected power will seriously affect the power system stability. Hence, the energy storage system (ESS) is an essential element to mitigate these variations and improves the system power quality [2,3].

Generally, the ESSs are a battery, super-capacitor (SC), flywheel, and superconducting magnetic energy storage (SMES), etc. The battery is a continuous power application device and usage is popularly increasing worldwide. The need for high power and energy demand can be achieved by combining battery and SC devices called as HESS and it is interfaced with a DC link employing bidirectional converters, which allows power into and from the ESS devices [4,5]. The importance of these ESSs can perform a significant role in the context of microgrid ( $\mu$ G) systems.

Appl. Sci. 2020, 10, 1108 2 of 15

Generally, the group of sources associated together to form a µG such as distributed energy sources, storage systems, and loads. μGs are categorized as DC, AC, and hybrid μGs. The hybrid μG is the combination of AC and DC  $\mu$ G. The DC  $\mu$ G is more preferred over the AC  $\mu$ G. It has various benefits such as better efficacy, less control complexity, and low power loss due to fewer conversion stages [6]. The benefit of a DC power system is the lack of reactive power over an AC power system. Reactive power leads to a loss of power in the lines, over-size of the inverters and the DC bus capacitors, and decrease in the line power transmissions' ability that affects AC power systems' efficiency and their reliability. Nevertheless, only active power in the lines is transmitted in DC  $\mu$ Gs that reduce the sizing of wire and DC bus capacitors. The DC  $\mu$ Gs are thus more efficient and reliable than AC  $\mu$ Gs. In the meantime, it will reduce costs further by eliminating the power conversion stages for complete converter sources and variable-speed drives. Harmonic nonlinear load currents increase energy loss in lines, transformers, and converters, thus reducing transformers and converters efficiency in AC  $\mu$ Gs. In addition, nonlinear loads affect the control system and, in some cases, also cause instability. Due to the high permeability of nonlinear loads in power distribution systems, DC μGs are again preferred to AC µG from the point of view of performance, reliability, and stability. The regulation of DC  $\mu$ Gs is very simple compared to AC  $\mu$ Gs as the power is regulated by the DC bus voltage and the angular and frequency stability control complexity does not show up in DC  $\mu$ Gs. Thus, DC  $\mu$ G appears to be efficient, reliable, and economical [7]. The  $\mu$ Gs are performed in two modes such as grid-connected and stand-alone mode. In stand-alone mode, the power balance is achieved by the ESS. During grid-connected operation, the grid can provide the balance power as the number of sources is correlated to sufficient demand of the load [8].

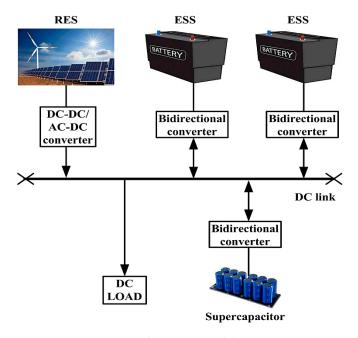

A typical DC  $\mu$ G is shown in Figure 1. In this, the RESs and ESSs are linked to the DC bus through interfacing converters. The ESSs in this system can be used to limit the PV power variations as well as maintain power stability. These converters work in parallel and there is a necessity to sustain the power balance at the DC link [9]. The instantaneous power balance is obtained from the following equation,

$$p_{in}(t) = p_{dc}(t) + p_{out}(t) \tag{1}$$

where,  $p_{in}(t) = p_{res}(t) + p_{ess}(t)$  and  $p_{out}(t) = p_{dcl}(t)$ ,  $p_{res}(t)$  is the power from RES,  $p_{dcl}(t)$  power absorbed by the DC link capacitor, and  $p_{ess}(t)$  is the power from ESS.

**Figure 1.** Typical DC microgrid ( $\mu$ G) system.

Appl. Sci. 2020, 10, 1108 3 of 15

The role of these converters is to balance the voltage level and power levels of different RESs and ESSs scattered at different locations [10]. The major problems associated with parallel operation of DC-DC converters are proper power-sharing, maximum power tracking for RESs, power loss in the converters, managing energy storage devices, voltage regulation, etc. [11].  $\mu$ Gs have a common advantage to collaborate and exchange control locally inside the given system. Therefore, it is important to devise a strategy that empowers such local energy transfer between  $\mu$ Gs that need energy and  $\mu$ Gs that have an excess of energy to move [12,13]. However, such collaboration raises numerous new challenges. Various power-sharing strategies in the literature, addressing the above-mentioned issues are discussed below [14–21].

In [14], a DC power source hybrid battery-SC based low-complexity control was proposed. The advantage of this scheme is less control complexity and being easier to implement. In [15], ramp-limit control is applied to limit the changes in power with the electric double-layer capacitor, but it does not allow continuous power application in the system. A control scheme is proposed in [16] for maintaining the power balance at DC μG in renewable and load variations as well. However, this strategy creates stress on the battery due to sudden changes in battery currents. The high-power density devices such as SCs are employed in [17] to protect the batteries from sudden changes in load or sources. In [18] the  $\mu G$  with the seamless transition between various  $\mu G$  operating modes has been proposed based on the adaptive battery control strategy. In the  $\mu$ G, the battery is modeled as a circuit equivalent instead of a constant voltage source for effective charging and discharging of the battery. In the control strategy that causes a DC link voltage to deviate from the reference value for sudden load variations, however, the batteries' slow response is not taken into consideration. In [19], an energy management system with storage describes the stored energy created by DG units or during the time where power from the network is most economical. A central EMS for DC μG was proposed in [20]. The advantage of this control is to decrease the effect of the high penetration of sustainable power source on the utility lattice and smoothen the impact of μG control change on power quality dependent on central EMS for DC μG scale framework. In [21,22], a normal boost converter is employed in renewable integrated systems. However, it has the drawback of switching losses, high current ripples, and minimizes the efficacy of the system. In [23,24], the high efficacy interleaved boost converter (IBC) approach for DC μG was proposed. The IBC increases the performance of the system, and will effectively minimize the input and output ripples and increases the efficacy of the system.

Taking the above-mentioned advantages and disadvantages of various power-sharing strategies into consideration, the aimed control scheme purpose is to (i) minimize the PV power fluctuations with ramp-limit control, (ii) the IBC will remove the current ripples and increases the efficacy of the overall system, (iii) reduces the battery unit current stress and improves the battery life span, (iv) maintains the power balance and steady DC link voltage at the DC  $\mu$ G. Hence, the improved control scheme achieves fast-acting DC link voltage to ensure better performance in the renewable integrated system.

In this paper, the objective function of the proposed method is discussed in Section 2. In Section 3, the proposed system structure and control configuration is explained. The Hardware-in-Loop (HIL) implementation is discussed in Section 4. Section 5 presents the results and discussion, and Section 6 is the conclusion.

## 2. Objective Function

## 2.1. Variations in PV Power

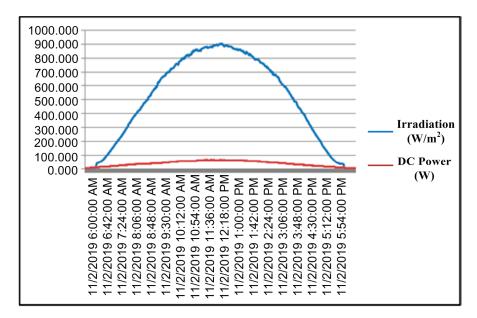

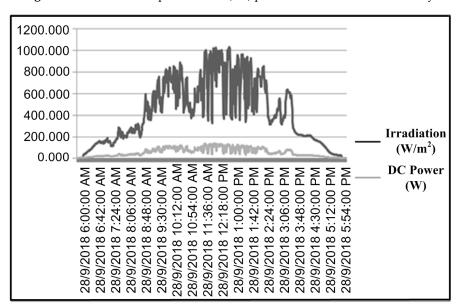

Figure 2 represents the normal solar variability. The variation is not severe during the normal solar variability. During the worst fluctuation case, the fluctuation is severe due to the fast movement of passing clouds. In the worst fluctuation case, 70% to 90% of power changes were observed based on Figure 3. In Figures 2 and 3, periodic 1-min data during a day from 6 a.m. to 6 p.m. were presented to observe the fluctuations in output PV power.

Appl. Sci. 2020, 10, 1108 4 of 15

Figure 2. Irradiation and photovoltaic (PV) power for normal solar variability.

Figure 3. Irradiation and PV power for severe solar variability.

# 2.2. Ramp-Limit Control

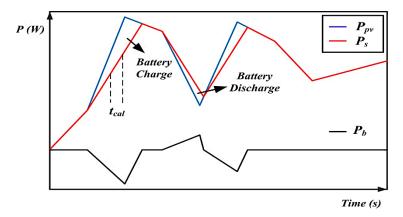

The ramp-limit controller smoothens the PV output variations [25] and the output PV power is limited by a constant limiter value ( $P_{limit}$ ). The rate of rise or fall should not be more than the maximum allowable ramp-limit, called the ramp-limit of RES. The maximum allowable ramp-limit or calculated time-step ( $t_{cal}$ ) is 10%/min. The charge/discharge characteristics of a battery using ramp-limit control are shown in Figure 4. The battery-1 power ( $P_{b1}$ ) is the difference between PV power ( $P_{pv}$ ) and smoothed power ( $P_s$ ). Then, the charge/discharge of the battery is regulated by the difference measured with the existing value of PV output. If the battery power is negative, it will charge. Conversely, if the battery power is positive, it discharges.

Appl. Sci. 2020, 10, 1108 5 of 15

Figure 4. Charge and discharge characteristics of a battery using ramp-limit control.

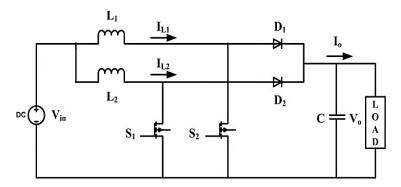

# 2.3. Interleaved Boost Converter

The IBC is shown in Figure 5. The IBC is interleaved by two structures and it performs two operations in tandem at a time. Hence, it is named as an interleaved converter. The IBC reduces the conduction losses and increases the conversion ratio. Thus, the efficacy of the system can be increased by saving energy [24].

Figure 5. Interleaved boost converter (IBC) circuit diagram.

The relation among output to input voltage is given by,

$$\frac{V_o}{V_{in}} = \frac{1}{(1-D)} \tag{2}$$

where  $V_o$  and  $V_{in}$  are the output and input voltages and D is the duty ratio. The inductor current is taken by the following relation,

$$I_L = \left(\frac{V_o}{V_{in}}\right) I_o \tag{3}$$

where  $I_0$  is the output current and  $I_L$  is the inductor current. The peak-peak inductor ripple is given by,

$$\Delta I_{L1} = \Delta I_{L2} = \left(\frac{V_{in}D}{F_{sw}L}\right) \tag{4}$$

where  $F_{SW}$  is the switching frequency and, L is the inductor.

The minimum ripple current occurs at 50% of the duty ratio [9].

If D is  $\leq 0.5$ ,

$$\Delta I_{in} = \left(\frac{V_o - 2V_{in}}{F_{sw}L}\right) D \tag{5}$$

Appl. Sci. 2020, 10, 1108 6 of 15

If D is > 0.5,

$$\Delta I_{in} = \left(\frac{V_o - 2V_{in}}{F_{sm}L}\right)(1 - D) \tag{6}$$

The value of inductor and capacitor is taken by the following equations,

$$L = \left(\frac{V_{in}D}{\Delta I_L F_{sw}}\right) \tag{7}$$

$$C = \left(\frac{V_o D F_{sw}}{R \Delta V_o}\right) \tag{8}$$

where *C* is the capacitance, *R* is the load resistance, and  $\Delta V_0$  is the change in output voltage.

A traditional boost converter has several merits, such as simple design, continual input current, and provides one polarity output voltage. However, the high efficacy and voltage gain are difficult to achieve by the boost converter. Thus, the IBC control helps to enhance the voltage gain, reduces the current ripples in the system, and switch voltage stress. However, the current sharing amongst the parallel paths can be taken into account by the IBC. Therefore, high voltage and high efficacy of the system can be achieved by the IBC strategy [26]. Thus, the IBC can serve as conquering input and output current ripples with smaller duty ratio and conduction loss.

# 3. Structure and Control Configuration of the Proposed System

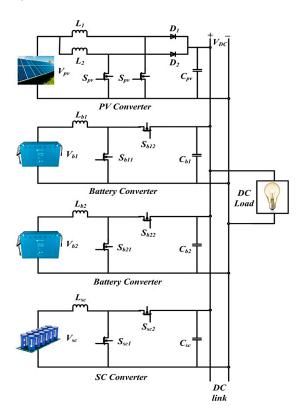

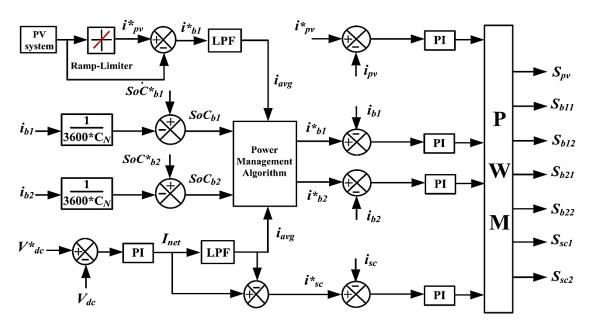

The proposed  $\mu G$  structure is shown in Figure 6. The structure consists of a PV source, two batteries, and a SC associated with an IBC and bidirectional converters to the DC link, and also a DC load linked at the DC link terminals. These converters are operated in current-controlled mode. A voltage controller is used to sustain the reference voltage across the load at the DC link. The generation of reference currents for battery and SC converters is described below.

Figure 6. Proposed μG structure.

Appl. Sci. 2020, 10, 1108 7 of 15

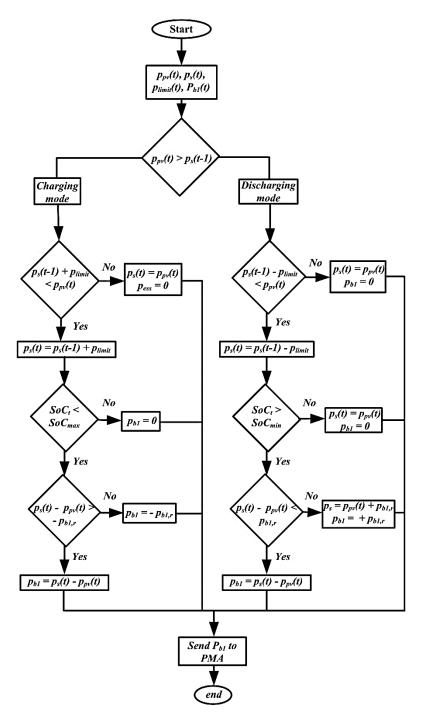

## 3.1. Reference Current Generation

Case (i): the generation of  $P_{b1}$  is based on the power management algorithm (PMA) shown in Figure 7. The variables  $P_{s(t-1)}$ ,  $P_{b,r}$ ,  $SOC_t$ ,  $SOC_{max}$ ,  $SOC_{min}$  in PMA are the  $P_s$  at previous  $t_{cal}$ , battery rated power, battery state of charge (SOC), maximum and minimum SOC, respectively.

Figure 7. Power management algorithm for battery-1.

The ramp-limit control will work only if the solar power fluctuates more than the threshold limits. Thus, the battery does not operate, and the P runs remain same as the preceding value. When the variation rate is severe, the  $P_s$  is updated to consider limit rate, and the process continues to the next step. The maximum and minimum of SOC limits vary between 0.9 and 0.1. The battery b1 does not

Appl. Sci. 2020, 10, 1108 8 of 15

operate when the SOC limitation is violated as a given value. When the rated power of b1 limitation is violated, the battery b1 charge/discharge power is equal to the rated power. Hence, the  $P_{b1}$  is calculated, and the value is transferred to the PMA. The generation of reference power for battery b1 is the difference between the  $P_s$  and  $P_{pv}$ . The required amount of power per  $t_{cal}$  is based on the setting limit rate [27]. Then the  $P_{limit}$  is calculated based on the following equation,

$$P_{limit} = \frac{t_{cal} \times (P_{pv,rated})}{60} \tag{9}$$

where  $P_{limit}$ ,  $t_{cal}$ ,  $P_{pv,rated}$  are the ramp-limit power, calculated time-step, and rated PV power, respectively.

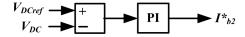

Case (ii): the power stability in the  $\mu G$  is stated by utilizing the DC link controller [2]. Figure 8 describes the functioning of a DC link controller.

Figure 8. DC link controller.

The proposed system control configuration is shown in Figure 9. The voltage controller output is reflected by the variations in DC link voltage. Thus, the storage converters can supply the net current  $(i_{net})$  to obtain the power balance at the DC link.

Figure 9. Control configuration of the proposed system.

Due to the difference in the PV/load power (i.e.,  $P_{pv} > P_l$  (or)  $P_{pv} < P_l$ ), the voltage controller output will vary, respectively, to regulate the  $I^*_{b2}$ , which is the  $i_{net}$  to be provided with a battery toward sustaining the reference voltage. The battery charge or discharge depends on the PV power variations. The battery converter reference current can be taken by employing the PI-based controller resulting net current equation,

$$i_{net} = K_p v_e + K_I \int v_e dt \tag{10}$$

where  $v_e = V_{dcref} - V_{dc}$ , is the reference and actual DC link voltage difference, which is owing to inflow and outflow power variation in the DC link.  $K_P$  and  $K_I$  are the proportional and integral constants of the voltage control loop. The  $i_{net}$  can be divided into average current ( $i_{avg}$ ) and transient current ( $i_{trs}$ ) to

Appl. Sci. 2020, 10, 1108 9 of 15

restrain the batteries from reacting to sudden changes in it. The  $i_{avg}$  is achieved by employing a low pass filter (LPF) based on the equation below,

$$i_{avg}(t) = \frac{1}{1 + s\tau_c} i_{net}(t) \tag{11}$$

In the above equation,  $\tau_c$  is the time constant of the LPF. The current  $i_{trs}$  is taken by the difference between the  $i_{net}$  and  $i_{avg}$ , as given below,

$$i_{trs}(t) = \left(1 - \frac{1}{1 + s\tau_c}\right)i_{net}(t) \tag{12}$$

The above current  $i_{trs}$  equation is used to get the reference current for the SC converter.

# 3.2. SOC of the Battery

The State of Charge (SOC) acts as a significant function in the battery-powered systems and it also improves the performance of the battery. Therefore, precise calculation of the SOC can not only preserve the battery, but also prevents over-discharge, enhances the battery life and accuracy of the system by saving energy. The battery SOC is measured by the count coulomb method [21]. The coulomb counting approach estimates the battery discharging current and integrates the discharging current over time to evaluate the SOC. The initial battery SOC ( $SOC_b$ ) is fixed at 70%. The  $SOC_b$  is determined by the resulting equation,

$$SOC_b = SOC_{in} - \frac{1}{3600C_N} \int i_b dt \tag{13}$$

where  $SOC_{in}$ ,  $C_N$ , and  $i_b$  are the battery initial SOC, nominal capacitance, and battery current, respectively.

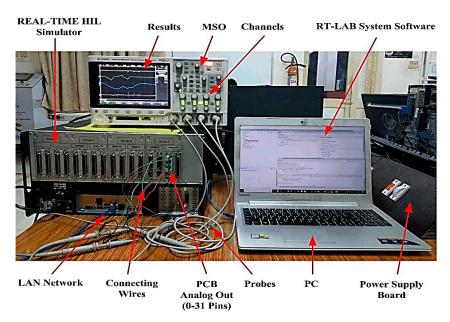

## 4. HIL Implementation

The OP5700 HIL Simulator was used to test the results using RT-LAB, MSOX3014T, programmable control board (PCB-E06-0560), probes, and connecting wires. The PCB can be used to interface between the simulation and real controller with the help of analog outputs and digital inputs to exchange the data. The real-time results setup is shown in Figure 10.

Figure 10. Real-Time (RT) results setup.

In engineering systems, HIL systems are widely used for real-time simulation pre-prototyping tests. Stacks have the ability to quickly create and synchronize prototypes. The machine and the controller are installed in OPAL-RT to run the system at the actual clock time. The high-speed nano to microsecond OPAL-RT sample speed makes this a dynamic system in real-time. The user PC controls the digital simulator (RTDS) commands for the RT-LAB. The prototype is edited, built, loaded, and executed with the use of RT-LAB. The HIL stack requirements and capacity to run real-time systems are addressed in Table 1.

| labie 1. | Haraware-in- | -Loop (HIL | ) Specifications. |

|----------|--------------|------------|-------------------|

|          |              |            |                   |

| Device Name                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | OP5700                                                        |  |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------|--|--|

| FPGA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Xilinx <sup>®</sup> Virtex <sup>®</sup> 7 FPGA on VC707 board |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Processing speed: 200 ns–2 μs                                 |  |  |

| I/O lines                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 256 lines, routed to eight analog or digital, 16 or 32        |  |  |

| High speed communication ports                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | channels                                                      |  |  |

| I/O connectors                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Up to 5 GBps                                                  |  |  |

| Monitoring connectors                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Four panels of BD37 connectors                                |  |  |

| PC interfaces                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Four panels of RJ45 connectors                                |  |  |

| Power rating                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Standard PC connectors                                        |  |  |

| , and the second | Input: 100-240 VAC, 50-60 Hz, 10/5 A                          |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Power: 600 W                                                  |  |  |

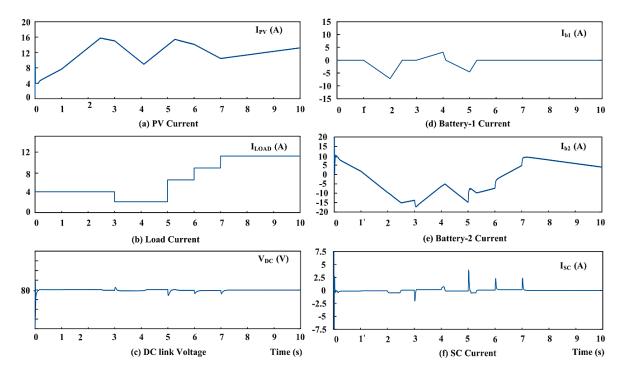

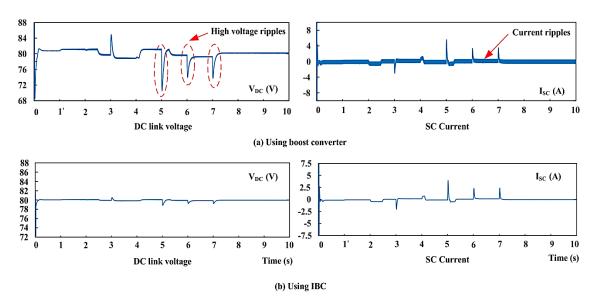

## 5. Results and Discussion

A DC  $\mu$ G configuration was developed to verify the proposed power design in Matlab/Simulink and the results from REAL-TIME HIL Simulator (OP5700) are presented in Figures 11–15. The system parameters of the proposed scheme are presented in Table 2.

Figure 11. Simulation results.

Figure 12. Analysis between the boost converter and IBC results.

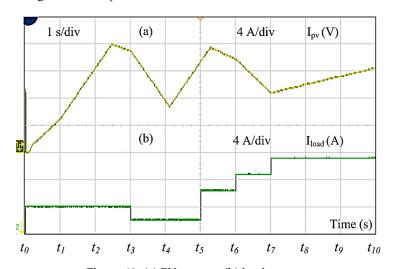

Figure 13. (a) PV current, (b) load current.

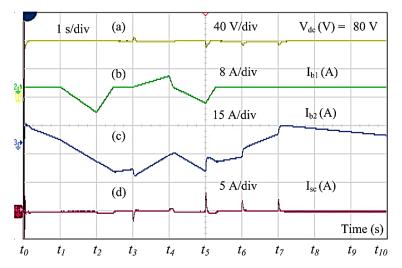

Figure 14. (a) DC link voltage, (b) battery-1 current, (c) battery-2 current, (d) super-capacitor (SC) current.

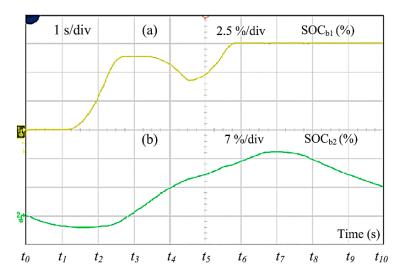

Figure 15. (a) Battery-1 SOC, (b) battery-2 SOC.

Table 2. System parameters.

| PV Pack Specifications at STC              | Values                            |  |

|--------------------------------------------|-----------------------------------|--|

| Open circuit voltage (V <sub>pv</sub> )    | 40 V                              |  |

| Short circuit current (I <sub>SC</sub> )   | 25 A                              |  |

| Battery Pack Specifications                | Values                            |  |

| Type                                       | Li-ion                            |  |

| Rated capacity                             | 12 Ah                             |  |

| Terminal voltage                           | 12 V                              |  |

| No. of batteries in series                 | 4                                 |  |

| SC pack parameters                         | Values                            |  |

| Terminal voltage (V <sub>sc</sub> )        | 12 V                              |  |

| No. of SCs in series                       | 4                                 |  |

| Max. peak current (I <sub>p</sub> )        | 200 A                             |  |

| Capacitance (C <sub>sc</sub> )             | 58 F                              |  |

| Max. continuous current (I <sub>mc</sub> ) | 19 A                              |  |

| Converter Parameters                       | Values                            |  |

| DV                                         | $L_1 = L_2 = 10 \text{ mH}$       |  |

| PV parameters                              | $C_{pv} = 500 \mu\text{F}$        |  |

| Pattama managatana                         | $L_{b1} = L_{b2} = 10 \text{ mH}$ |  |

| Battery parameters                         | $C_{b1} = C_{b2} = 500 \ \mu F$   |  |

| CC managemakana                            | $L_{sc} = 10 \text{ mH}$          |  |

| SC parameters                              | $C_{\rm sc} = 500 \ \mu F$        |  |

| DC load parameter                          | $R_{dcl} = 100 \Omega$            |  |

| DC link parameter                          | $V_{dc} = 80 \text{ V}$           |  |

# 5.1. Simulation Results

The simulation results of the proposed are presented in Figure 11. The analysis between the boost converter and IBC system results are shown in Figure 12. In the boost converter, the high ripple voltage and currents are presented in Figure 12a. The voltage drop at the DC link is more at the instant t5 in Figure 12a by 8V/s during sudden variations in the load at time t5 by 4A/s in Figure 11c; thus it affects the fast-acting DC link voltage regulation, and the high width of the current ripples and conduction losses in SC are presented in Figure 12a. It decreases the efficacy of the system. The IBC efficiently

reduces the current and voltage ripples as shown in Figure 12b, and increases the performance and reliability of the system.

## 5.2. Real-Time HIL Results

In the simulated model, the PV system rating of 40 V and the battery of ratings 48 V are considered. The IBC and bidirectional converters are operated to interlink the PV and batteries with the DC grid. The DC link reference voltage is 80 V and a variable source is connected to the DC link. The Real-Time HIL Simulator results are presented in Figures 13–15. The irregular nature of the PV current profile varying between instants  $t_1$ – $t_{10}$  by 4 A/div is shown in Figure 13a, and Figure 13b shows the randomly varying load current profile by 4 A/div. During the variable PV and/or load conditions ( $P_{pv} > P_l$  or  $P_{pv} < P_l$ ), there is a necessity to sustain power stability and provides fast DC voltage regulation into the system. At time  $t_3$ , the load current is suddenly decreased by 2 A/div and at instant  $t_5$  suddenly increased by 4 A/div; in this period the drop of the bus voltage is much less when compared to boost converter.

The battery-1 current is shown in Figure 14b. From Figure 14b, the difference between the  $P_{pv}(t)$  and  $P_s(t)$  can be seen. Figure 14c shows the battery-2 current. The battery-2 current varies according to the  $P_{pv}(t)$  and  $P_l(t)$ . The battery-2 can not only preserve charging or discharging conditions, it can also sustain the power stability at the DC link. The SC current is shown in Figure 14d and it decreases the current stress on the batteries by responding to transients in the system. Figure 14a shows the constant DC link voltage. At instant  $t_1$ – $t_3$ , the load current is constant by 4 A/div, thus during constant load conditions, there is no variation in the bus voltage. From  $t_5$ – $t_7$ , the load current is increased by 2 A/div and PV current rises at instant  $t_5$  by 4 A/div and reduces after instant  $t_5$  to  $t_7$  by 4 A/div; at these instants, the voltage drop is less than 2 A/div and also maintained the stable DC bus voltage. Hence, it is clear that even sudden a change in load also does not affect the steady DC link voltage. The SOCs of battery-1 and battery-2 is shown in Figure 15a,b. The SOC of batteries will respond according to the charging and discharging conditions of battery-1 and battery-2.

#### 6. Conclusions

A ramp-limit control-based management system for solar PV using real-time data with HESS was presented. The Real-Time HIL Simulator results were carried out to validate the proposed control system. The controller was employed to regulate the output of the batteries to reduce the variations of output PV power and to sustain the power balance at DC link. The IBC effectively minimizes the input current and output voltage ripples of the system. The SC was applied to remove the quick changes in battery currents, thereby overcomes the stress on the battery unit and improves battery life. The proposed system effectively maintains the steady DC link voltage during variable load conditions, increases the system reliability, and reduces the ripples and conduction losses in the system.

**Author Contributions:** P.K., G.V.B.K., S.P. developed the original concepts and theoretical background. P.K. and G.V.B.K. implemented the concept in PHIL environment and tested for its performance. S.P. provided his correction and theoretical validation of the results. J.B.H.-N. and F.B. provided the expert suggestion and validation of the results for its presentation. All authors have read and agreed to the published version of the manuscript.

**Funding:** This research activity is funded by Danida Fellowship Mobility Grant Project No. "19-MG05-AAU", Government of Denmark for "Renewable Energy Penetration in Microgrids and Electric Vehicles Charging Station". This project also supported by Grant Project No. SR/FST/ETI-420/2016(C)) "Fund for Improvement of S&T infrastructure in Universities & Higher Educational Institutions (FIST)" Department of Science and Technology (DST)—Government of India. Funded to establish the PHIL set-up which is a part of this research project.

**Acknowledgments:** The authors would like to acknowledge the technical expertise received from the Center for Bioenergy and Green Engineering/Center of Reliable Power Electronics (CORPE), Department of Energy Technology, Aalborg University, Esbjerg/Aalborg, Denmark.

Conflicts of Interest: The authors declare no conflict of interest.

## References

1. Li, X.; Hui, D.; Lai, X. Battery Energy Storage Station (BESS)-Based Smoothing Control of Photovoltaic (PV) and Wind Power Generation Fluctuations. *IEEE Trans. Sustain. Energy* **2013**, *4*, 464–473. [CrossRef]

- Brahmendra Kumar, G.V.; Kumar, G.A.; Eswararao, S.; Gehlot, D. Modelling and control of bess for solar integration for pv ramp rate control. In Proceedings of the 2018 International Conference on Computation of Power, Energy, Information and Communication (ICCPEIC), Tamil Nadu, India, 28–29 March 2018; pp. 368–374.

- 3. Kumar, G.; Sarojini, R.; Palanisamy, K.; Padmanaban, S.; Holm-Nielsen, J. Large Scale Renewable Energy Integration: Issues and Solutions. *Energies* **2019**, *12*, 1996. [CrossRef]

- 4. Lahyani, A.; Venet, P.; Guermazi, A.; Troudi, A. Battery/Supercapacitors Combination in UPS. *IEEE Trans. Power Electron.* **2013**, *28*, 1509–1522. [CrossRef]

- 5. Manandhar, U.; Ukil, A.; Gooi, H.B.; Tummuru, N.R.; Kollimalla, S.K.; Wang, B.; Chaudhari, K. Energy Management and Control for Grid Connected Hybrid Energy Storage System Under Different Operating Modes. *IEEE Trans. Smart Grid* 2019, 10, 1626–1636. [CrossRef]

- 6. Anand, S.; Fernandes, B.G.; Guerrero, J. Distributed control to ensure proportional load sharing and improve voltage regulation in low-Voltage dc microgrids. *IEEE Trans. Power Electron.* **2013**, *28*, 1900–1913. [CrossRef]

- 7. Lotfi, H.; Member, S.; Khodaei, A.; Member, S.; Indices, A. AC Versus DC Microgrid Planning. *IEEE Trans. Smart Grid* **2017**, *8*, 296–304. [CrossRef]

- 8. Nejabatkhah, F.; Li, Y.W. Overview of power management strategies of hybrid ac/dc microgrid. *IEEE Trans. Power Electron.* **2015**, *30*, 7072–7089. [CrossRef]

- 9. Wu, D.; Tang, F.; Dragicevic, T.; Vasquez, J.C.; Guerrero, J.M. A control architecture to coordinate renewable energy sources and energy storage systems in islanded microgrids. *IEEE Trans. Smart Grid* **2015**, *6*, 1156–1166. [CrossRef]

- Maza-Ortega, J.M.; Gomez-Exposito, A.; Barragan-Villarejo, M.; Romero-Ramos, E.; Marano-Marcolini, A. Voltage source converter-Based topologies to further integrate renewable energy sources in distribution systems. *IET Renew. Power Gener.* 2012, 6, 435–445. [CrossRef]

- 11. Augustine, S.; Lakshminarasamma, N.; Mishra, M.K. Control of photovoltaic based low-Voltage dc microgrid system for power sharing with modified droop algorithm. *IET Power Electron.* **2016**, *9*, 1132–1143. [CrossRef]

- 12. Lahon, R.; Gupta, C.P. Energy management of cooperative microgrids with high-Penetration renewables. *IET Renew. Power Gener.* **2018**, *12*, 680–690. [CrossRef]

- 13. Solanki, B.V.; Bhattacharya, K.; Cañizares, C.A. A sustainable energy management system for isolated microgrids. *IEEE Trans. Sustain. Energy* **2017**, *8*, 1507–1517. [CrossRef]

- 14. Hredzak, B.; Agelidis, V.; Demetriades, G. A low complexity control system for a hybrid dc power source based on ultracapacitor-lead acid battery configuration. *IEEE Trans. Power Electron.* **2014**, 29, 2882–2891. [CrossRef]

- 15. Kakimoto, N.; Satoh, H.; Takayama, S.; Nakamura, K. Ramp-Rate control of photovoltaic generator with electric double-Layer capacitor. *IEEE Trans. Energy Convers.* **2009**, *24*, 465–473. [CrossRef]

- 16. Savoye, F.; Venet, P.; Millet, M.; Groot, J. Impact of periodic current pulses on Li-ion battery performance. *IEEE Trans. Ind. Electron.* **2012**, *59*, 3481–3488. [CrossRef]

- 17. Jing, W.; Hung Lai, C.; Wong, S.H.W.; Wong, M.L.D. Battery-Supercapacitor hybrid energy storage system in standalone dc microgrids: A review. *IET Renew. Power Gener.* **2017**, *11*, 461–469. [CrossRef]

- 18. Eghtedarpour, N.; Farjah, E. Distributed charge/discharge control of energy storages in a renewable-Energy-Based dc micro-Grid. *IET Renew. Power Gener.* **2014**, *8*, 45–57. [CrossRef]

- 19. Oriti, G.; Julian, A.L.; Peck, N.J. Power-Electronics-Based energy management system with storage. *IEEE Trans. Power Electron.* **2016**, *31*, 452–460. [CrossRef]

- 20. Han, Y.; Xie, X.; Deng, H.; Ma, W. Central energy management method for photovoltaic dc micro-Grid system based on power tracking control. *IET Renew. Power Gener.* **2017**, *11*, 1138–1147. [CrossRef]

- 21. Tummuru, N.R.; Mishra, M.K.; Srinivas, S. Dynamic energy management of renewable grid integrated hybrid energy storage system. *IEEE Trans. Ind. Electron.* **2015**, *62*, 7728–7737. [CrossRef]

- 22. Mahmood, H.; Michaelson, D.; Jiang, J. A power management strategy for PV/battery hybrid systems in islanded microgrids. *IEEE J. Emerg. Sel. Top. Power Electron.* **2014**, 2, 870–882. [CrossRef]

23. Lai, C.; Pan, C.; Cheng, M. High-Efficiency modular high step-Up interleaved boost converter for dc-Microgrid applications. *IEEE Trans. Ind. Appl.* **2012**, *48*, 161–171. [CrossRef]

- 24. Zhao, Q.; Lee, F.C. High-Efficiency, high step-Up dc-dc converters. *IEEE Trans. Power Electron.* **2013**, *18*, 65–73. [CrossRef]

- 25. Marcos, J.; Storkel, O.; Marroyo, L.; Garcia, M.; Lorenzo, E. Storage requirements for pv power ramp-Rate control. *Solar Energy* **2014**, *99*, 28–35. [CrossRef]

- 26. Wang, D.; He, X.; Zhao, R. Zvt interleaved boost converters with built-In voltage doubler and current auto-Balance characteristic. *IEEE Trans. Power Electron.* **2008**, *23*, 2847–2854. [CrossRef]

- 27. Kim, N.-K.; Cha, H.-J.; Seo, J.-J.; Won, D.-J. Soc management algorithm of battery energy storage system for pv ramp rate control. In Proceedings of the 2017 6th International Youth Conference on Energy (IYCE), Piscataway, NJ, USA, 21–24 June 2017; pp. 1–6.

© 2020 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).