Article

# Small-Signal Analysis and Control of Soft-Switching Naturally Clamped Snubberless Current-Fed Half-Bridge DC/DC Converter

Koyelia Khatun <sup>1</sup>, Vakacharla Venkata Ratnam <sup>1</sup>, Akshay Kumar Rathore <sup>1,\*</sup> and Beeramangalla Lakshminarasaiah Narasimharaju <sup>2</sup>

- <sup>1</sup> Department of Electrical and Computer Engineering, Gina Cody School of Engineering and Computer Science, SGW Campus, Concordia University, Montreal, QC H3G 1M8, Canada; koyel.bolpur.22@gmail.com (K.K.); v\_enkat@encs.concordia.ca (V.V.R.)

- <sup>2</sup> Department of Electrical Engineering, National Institute of Technology, Warangal 506004, India; blnraju@nitw.ac.in

- \* Correspondence: akshay.rathore@concordia.ca; Tel.: +1-514-848-8484 (ext. 4486)

Received: 30 June 2020; Accepted: 25 August 2020; Published: 3 September 2020

# Featured Application: Fuel cells and Battery Applications.

**Abstract:** This paper presents small-signal analysis of a soft-switching naturally clamped snubberless isolated current-fed half-bridge (CFHB) DC-DC converter using state-space averaging. A two-loop average current controller was designed and implemented on a digital signal processor. The complete design procedure is presented here. Simulation results using software PSIM 11.1 are shown to validate the stability of the control system and the controller design. Experimental results for the step changes in load current vividly demonstrated satisfactory transient performance of the converter and validated the developed small-signal model and the control design.

Keywords: DC-DC converter; small-signal analysis; soft-switching; closed-loop control

## 1. Introduction

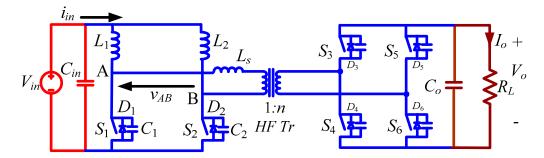

Electric transportation, energy storage, renewable energy systems, hybrid electric vehicles (HEV), and fuel cell vehicles require bidirectional power electronics for power processing [1–4]. A DC-DC front-end converter is the major part of a fuel cell inverter, which boosts the low-voltage fuel cell stack's voltage to the peak of utility line alternating current (AC) voltage [5]. Among various categories of high-frequency (HF) soft-switching isolated DC-DC converters, a current-fed converter is popular in fuel cell applications. Fuel cells produce low-voltage direct current (DC), which has a wide variation with load current and requires a high voltage conversion ratio [6–10]. Current-fed topologies offer high voltage gain with a stiff DC input current [11]. The historical problem with current-fed converters has been the necessity of a passive snubber [12,13] or an active-clamping circuit [14–16] to clamp voltage overshoot across the semiconductor devices at their turn-off. Passive snubbers lead to poor efficiency because the energy stored by the clamping capacitor is later dissipated into the resistor. However, better efficiency is obtained, along with zero voltage switching (ZVS) of the semiconductor devices, with an active-clamping circuit [14–16], at the cost of additional footprints of floating active device(s) and a large HF clamp capacitor for accurate and effective voltage clamping. Additionally, the boost factor of the converter is reduced as well as the high peak, and circulating currents can be observed at light load. In [17], a new modulation technique of high-voltage side devices was proposed to solve the voltage spike problem of primary devices, eliminating the requirement for an external snubber. A current-fed half-bridge DC-DC converter was proposed as shown in Figure 1 with a new modulation,

which was studied in [17] to achieve zero current switching (ZCS) commutation of semiconductor devices along with natural device voltage clamping.

**Figure 1.** The zero current switching (ZCS) naturally clamped current-fed half-bridge isolated DC-DC converter. Reproduced with permission from [17], IEEE, 2020.

Steady-state analysis, power circuit design, and steady-state experimental performance results of the converter have previously been presented in [17]. However, its small-signal modeling, controller design, and dynamic performance results have not yet reported. The authors reported the small-signal modeling and derived the transfer functions in [18]. Controller design and simulation results were presented to show initial results and investigation on the transient performance of the converter. This paper presents systematic small-signal analysis and experimental results to demonstrate the closed-loop dynamic performance of the converter.

## 2. Small-Signal Analysis

The following procedure was followed to derive the small-signal model and converter transfer functions:

- (1) Make assumptions

- (2) Define state variables

- (3) Write state equations for each interval of operation

- (4) Average the state equations over a switching cycle

- (5) Introduce perturbation in state variables

- (6) Equate AC and DC quantities and proceed with AC equations

- (7) Take Laplace transform

- (8) Prepare matrix small-signal model

- (9) Calculate desired transfer functions

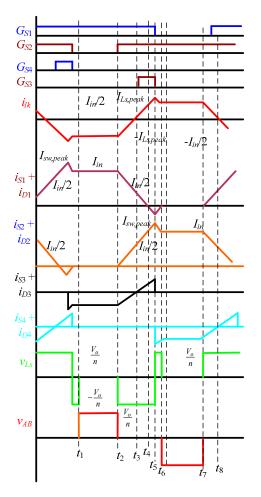

The following assumptions were made for the small-signal modeling of the converter: (1) all the power semiconductor devices are lossless and ideal; (2) inductors  $L_1$  and  $L_2$  are large enough to maintain constant current through them; (3) inductor  $L_s$  includes the leakage inductance of the HF transformer; steady-state operating waveforms are shown in Figure 2; (4) snubber/device capacitance charging and discharging intervals are short and neglected.

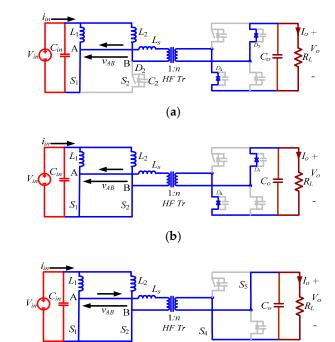

The primary side devices  $S_1$  and  $S_2$  are operated with identical gating signals phase-shifted with each other by 180°. The duty cycle of the primary switches is always kept above 50%. The operation during different intervals in a one-half switching cycle is explained with equivalent circuits shown in Figure 3.

**Figure 2.** Operating waveforms of the ZCS current-fed converter shown in Figure 1. Reproduced with permission from [17], IEEE, 2020.

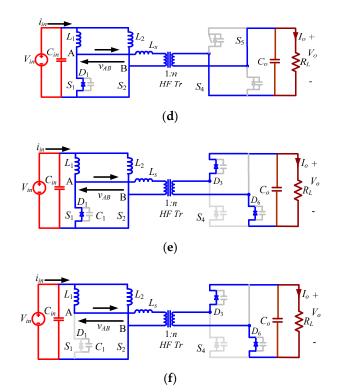

(c) Figure 3. Cont.

**Figure 3.** Equivalent circuits during different intervals of the operation for the waveform in Figure 2 Reproduced with permission from [17], IEEE, 2020. (a)  $S_2$  in blocking mode; (b)  $S_2$  is turned-on; (c) ZVS turn-on of  $S_4$  and  $S_5$ ; (d) ZCS turn-off of  $S_1$  and body diode conducts; (e)  $D_3$  and  $D_6$  start conduction for rectification; (f)  $S_1$  goes in blocking mode.

State variables defined for the small-signal modeling of the converter are: (1) currents through the transformer leakage inductor  $i_{lk1}$  and  $i_{lk2}$ ; (2) input inductor current  $i_{in}$ ; (3) output voltage  $v_o$ ; (4) input voltage  $v_{in}$ ; (5) duty cycle loss d.

Interval 1 (Figure 3a;  $t_1 < t < t_2$ )

During this interval, primary side switch  $S_1$  and anti-parallel body diodes  $D_4$  and  $D_5$  of secondary switches are conducting to rectify the HF AC waveform across the transformer secondary. Power is transferred to the load through an HF transformer. Transformer primary current is negative and constant. Switch  $S_1$  is carrying the entire input current. State equations of this interval are:

$$L_1 \frac{di_{L1}}{dt} = v_{in} \tag{1}$$

$$L_1 \frac{di_{L1}}{dt} = v_{in} \tag{2}$$

$$C_o \frac{dv_o}{dt} = \frac{i_{L_s}}{n} - \frac{v_o}{R_L} \tag{3}$$

$$L_s \frac{di_{Ls}}{dt} = 0 \tag{4}$$

Interval 2 (Figure 3b;  $t_2 < t < t_3$ )

Primary side switch  $S_2$  is turned on and starts conducting. The current from  $S_1$  is transferred to the switch  $S_2$  through the transformer primary winding with a slope limited by transformer leakage inductance  $L_s$ . State equations of this interval are:

$$L_2 \frac{di_{L2}}{dt} = v_{in} \tag{5}$$

$$L_s \frac{di_{Ls}}{dt} = \frac{v_o}{n} \tag{6}$$

Interval 3 (Figure 3c;  $t_3 < t < t_4$ )

Secondary side devices  $S_4$  and  $S_5$  are turned on with ZVS. The current waveforms follow the same pattern and slope. State equations of interval 2 still hold good.

Interval 4 (Figure 3d;  $t_4 < t < t_5$ )

Primary side device  $S_1$  turns off with ZCS, and its anti-parallel body diode starts conducting. State equations of interval 2 still hold good.

Interval 5 (Figure 3e;  $t_5 < t < t_6$ )

Secondary side devices  $S_4$  and  $S_5$  are forced commutated, and anti-parallel body diodes  $D_3$  and  $D_6$  of secondary switches take over the current.

$$L_s \frac{di_{Ls}}{dt} = -\frac{V_o}{n} \tag{7}$$

Equations (1), (3), and (5) hold good for inductor currents  $i_{L1}$ ,  $i_{L2}$ , and output capacitor  $c_0$ .

Identically, state equations for the other half-cycle can also be derived. State equations are averaged over an HF cycle. The average value for the rate of change of  $i_{LS}$  over one complete HF cycle is zero, and the averaged state equation is:

$$L_{s}\langle \frac{di_{Ls}}{dt} \rangle = 0 \tag{8}$$

So, the state variable  $i_{Ls}$  is omitted for the following analysis. Define:  $d_1T_s = t_2 - t_1$ ,  $d_2T_s = t_3 - t_2$ ,  $d_3T_s = t_4 - t_3$ ,  $d_4T_s = t_5 - t_4$ ,  $d_5T_s = t_6 - t_5$ ,  $d_6T_s = t_7 - t_6$ ,  $d_7T_s = t_8 - t_7$ ,  $d_8T_s = t_9 - t_8$ ,  $d_9T_s = t_{10} - t_9$ ,  $d_{10}T_s = t_s - t_{10}$ .

The averaged state equations of defined state variables over an HF cycle are given:

$$L_1 \langle \frac{di_{L1}}{dt} \rangle = v_{in} - d_6 \frac{v_o}{n} \tag{9}$$

$$L_2 \langle \frac{di_{L2}}{dt} \rangle = v_{in} - d_1 \frac{v_o}{n} \tag{10}$$

$$C_o \langle \frac{dv_o}{dt} \rangle = i_{average} - \frac{v_o}{R_L} \tag{11}$$

where *i*<sub>average</sub> is the average current feeding the output capacitor and load from secondary side H-bridge switches and is given by:

$$i_{average} = \frac{i_{L2}}{n}(d_1) + \frac{i_{L1}}{n}(d_6)$$

(12)

Substituting Equation (12) into Equation (11) gives:

$$C_o \frac{dv_o}{dt} = \frac{i_{L2}}{n} (d_1) + \frac{i_{L1}}{n} (d_6) - \frac{v_o}{R_L}$$

(13)

The duty ratio of the main switches, including conduction of the anti-parallel diodes, is defined as:

$$d = d_{S1} = d_1 + d_2 + d_3 + d_4 + d_5 + d_7 + d_8 + d_9 + d_{10}$$

(14)

$$d = d_{52} = d_2 + d_3 + d_4 + d_5 + d_6 + d_7 + d_8 + d_9 + d_{10}$$

(15)

Perturbation is introduced around the steady-state values of the state variables and input voltage such that  $i_{L1} = I_L + i_{L1}$ ,  $i_{L2} = I_L + i_{L2}$ ,  $v_{in} = V_{in} + \hat{v}_{in}$ ,  $v_o = V_o + \hat{v}_o$ ,  $d_{s1} = D + \hat{d}_{s1}$ , and  $d_{s2} = D + \hat{d}_{s2}$ . The state equations are modified to the following:

$$L_1 \frac{d(I_{L1} + i_{L1})}{dt} = (V_{in} + \hat{v}_{in}) - \left(1 - D - \hat{d}_{s1}\right) \frac{(V_o + \hat{v}_o)}{n}$$

(16)

$$L_2 \frac{d(I_{L2} + i_{L2})}{dt} = (V_{in} + \hat{v}_{in}) - \left(1 - D - \hat{d}_{s2}\right) \frac{(V_o + \hat{v}_o)}{n}$$

(17)

$$C_o \frac{d(V_o + \hat{v}_o)}{dt} = \left(\frac{I_{L1} + i_{L1}}{n}\right) \left(1 - D - \hat{d}_{s1}\right) + \left(\frac{I_{L2} + i_{L2}}{n}\right) \left(1 - D - \hat{d}_{s2}\right) - \left(\frac{V_o + \hat{v}_o}{R_L}\right)$$

(18)

Neglecting the second order terms and steady-state or DC terms results in the following equations:

$$L_1 \frac{di_{L1}}{dt} = \hat{v}_{in} - (1 - D)\frac{\hat{v}_0}{n} + \hat{d}_{s1}\frac{V_o}{n}$$

(19)

$$L_2 \frac{di_{L2}}{dt} = \hat{v}_{in} - (1-D)\frac{\hat{v}_o}{n} + \hat{d}_{s2}\frac{V_o}{n}$$

(20)

$$C_o \frac{d\hat{v}_o}{dt} = (1-D)\frac{i_{L1}}{n} + (1-D)\frac{i_{L2}}{n} - \frac{I_{L1}}{n}\hat{d}_{s1} - \frac{I_{L2}}{n}\hat{d}_{s2} - \frac{\hat{v}_o}{R_L}$$

(21)

Taking Laplace transform, and then solving results in:

$$sL_1 i_{L1}(s) + \frac{(1-D)\hat{v}_o(s)}{n} = \frac{V_o}{n}\hat{d}_{s1}(s) + \hat{v}_{in}(s)$$

(22)

$$sL_2i_{L2}(s) + \frac{(1-D)\hat{v}_o(s)}{n} = \frac{V_o}{n}\hat{d}_{s2}(s) + \hat{v}_{in}(s)$$

(23)

$$\frac{(1-D)}{n}i_{L1}(s) + \frac{(1-D)}{n}i_{L2}(s) - \left(sC_o + \frac{1}{R_L}\right)\hat{v}_o(s) = \frac{I_{L1}}{n}\hat{d}_{s1}(s) + \frac{I_{L2}}{n}\hat{d}_{s2}(s)$$

(24)

Writing in matrix form:

$$\begin{bmatrix} i_{L1}(s) \\ i_{L2}(s) \\ \hat{v}_{o}(s) \end{bmatrix} = \begin{bmatrix} A(s) \end{bmatrix} \cdot \begin{bmatrix} \frac{V_{o}}{n} \\ 0 \\ \frac{I_{L1}}{n} \end{bmatrix} \cdot \hat{d}_{s1}(s) + \begin{bmatrix} A(s) \end{bmatrix} \cdot \begin{bmatrix} 0 \\ \frac{V_{o}}{n} \\ \frac{I_{L2}}{n} \end{bmatrix} \hat{d}_{s2}(s) + \begin{bmatrix} A(s) \end{bmatrix} \cdot \begin{bmatrix} 1 \\ 1 \\ 0 \end{bmatrix} \hat{v}_{in}(s)$$

(25)

where

$$A(s) = \begin{bmatrix} sL_1 & 0 & \frac{(1-D)}{n} \\ 0 & sL_2 & \frac{(1-D)}{n} \\ \frac{(1-D)}{n} & \frac{(1-D)}{n} & -\left(sC_o + \frac{1}{R_L}\right) \end{bmatrix}^{-1}$$

(26)

$$sL(i_{L1}(s) + i_{L2}(s)) + \frac{2(1-D)\hat{v}_o(s)}{n} = \frac{V_o}{n} \left( \hat{d}_{s1}(s) + \hat{d}_{s2}(s) \right) + 2\,\hat{v}_{in}(s) \tag{27}$$

Writing in matrix form:

$$\begin{bmatrix} i_{L1}(s) + i_{L2}(s) \\ \hat{v}_o(s) \end{bmatrix} = \begin{bmatrix} A(s) \end{bmatrix} \cdot \begin{bmatrix} \frac{v_o}{n} \\ \frac{I_L}{n} \end{bmatrix} \cdot \left( \hat{d}_{s1}(s) + \hat{d}_{s2}(s) \right) + \begin{bmatrix} A(s) \end{bmatrix} \cdot \begin{bmatrix} 2 \\ 0 \end{bmatrix} \hat{v}_{in}(s)$$

(28)

where

$$A(s) = \begin{bmatrix} sL & \frac{2(1-D)}{n} \\ \frac{(1-D)}{n} & -(sC_o + \frac{1}{R_L}) \end{bmatrix}^{-1}$$

(29)

The control-to-output transfer function is obtained from Equation (28) by keeping  $\hat{v}_{in} = 0$ , resulting in the following equation:

$$\frac{\hat{v}_o(s)}{\hat{d}_{s1}(s) + \hat{d}_{s2}(s)} = \frac{\frac{(1-D)V_o}{n^2} - s\frac{LI_L}{n}}{(LC_o)s^2 + \frac{L}{R_L}s + \frac{2(1-D)^2}{n^2}}$$

(30)

6 of 19

## 3. Two-Loop Closed-Loop Control Design

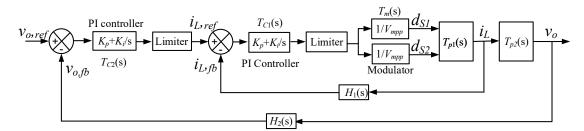

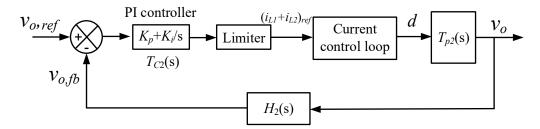

The two-loop control system is shown in Figure 4 with two proportional integral (PI) controllers and two identical modulators phase-shifted by 180°. Active current ripple is the major issue in the design of a fuel cell converter. The key to ripple reduction is to control the average inductor current  $i_L$ to be DC, which requires separating the bandwidths of voltage and current loops far apart using a slow voltage loop and a fast current loop [19]. Bandwidth (BW) of the inner current loop is selected to be higher than the outer voltage loop, which simplifies the design [20]. Therefore, it is possible to adjust the inductor current more quickly than the load voltage. The outer voltage loop regulates the load voltage by deriving reference for the input inductor current,  $i_{L1,ref}$ , and  $i_{L2,ref}$  reference. Inductor currents  $i_{L1}$  and  $i_{L2}$  are tuned to this reference value by adjusting the duty ratio of the switches.

Figure 4. Complete two-loop average current control block diagram.

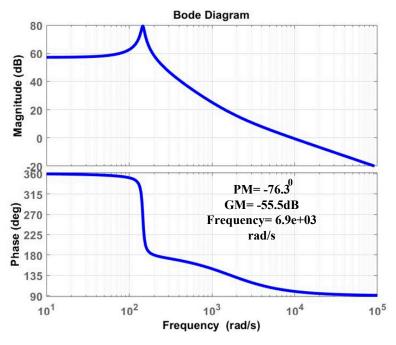

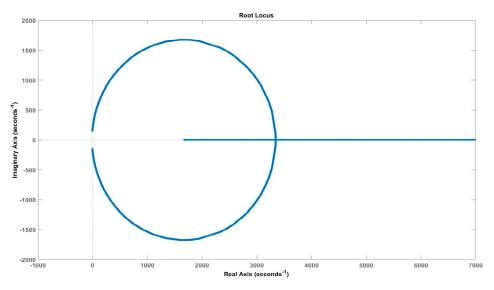

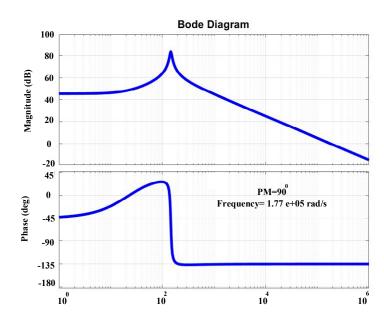

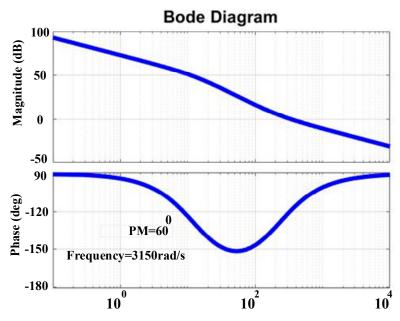

A bode plot of the control-to-output voltage transfer function given by Equation (30) is given in Figure 5. The phase margin (PM) is negative. This makes the system sensitive to small disturbances in operating points of input or source voltage and load current. Figure 6 shows that this transfer faction has right half plane zero, which adds a negative phase to the system. Instead of the phase increasing from 0 to 90 degrees, its phase increases from 0 to -90 degrees. This causes a delay in system response, which can lead to instability if not properly compensated.

Figure 5. The control-to-output voltage transfer function of the system.

Figure 6. Pole-zero map of the control-to-output voltage transfer function of the system without controller.

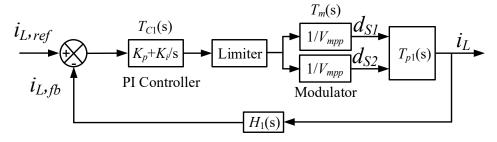

## 3.1. Current Control Loop Design

The schematic diagram of the inner current control loop is shown in Figure 7. The input inductor current is fed back to the error amplifier with the gain of  $H_1(s)$ . The error is processed by a PI controller, and the output of the controller is compared with the modulator to generate the gating signals of the devices. The inductors' currents  $i_{L1}$  and  $i_{L2}$  are then regulated by adjusting the duty ratio of the switches.

Figure 7. Inner current control loop schematic diagram.

Duty ratio to the inductor current transfer function is derived from Equation (27) and given by:

$$\frac{i_{L1}(s) + i_{L2}(s)}{\hat{d}_{s1}(s) + \hat{d}_{s2}(s)} = \frac{\left(\frac{C_o V_o}{n}\right)s + \frac{V_o}{nR_L} + \frac{2(1-D)}{n}\frac{I_L}{n}}{(LC_o)s^2 + \frac{L}{R_L}s + \frac{2(1-D)^2}{n^2}}$$

(31)

For the given specifications as shown in Table 1, the duty ratio to inductor current transfer function is given by:

$$T_{p1}(s) = \frac{i_{L1}(s) + i_{L2}(s)}{\hat{d}_{s1}(s) + \hat{d}_{s2}(s)} = \frac{0.004542s + 0.331514}{4.26 \times 10^{-8} s^2 + 5.847 \times 10^{-7} s + 3.472 \times 10^{-3}}$$

(32)

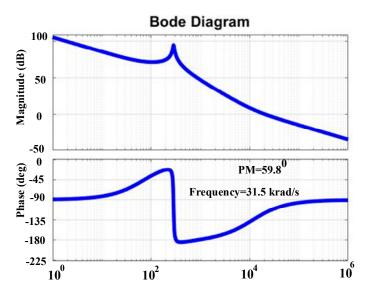

The gain margin and PM of the current control loop without controller is plotted in Figure 8, which shows  $PM = 90^{\circ}$  at 177 krad/s. The PI controller is designed at PM of  $60^{\circ}$  in Figure 9 to increase the low-frequency gain and to reduce the steady-state error [21].

| Input voltage V <sub>in</sub>           | 12 V      |

|-----------------------------------------|-----------|

| Output Voltage V <sub>o</sub>           | 288 V     |

| Peak output power <i>P</i> <sub>o</sub> | 250 W     |

| Switching frequency converter $f_s$     | 100 kHz   |

| Leakage inductor L <sub>ls</sub>        | 1.74 μH,  |

| Input Boost Inductors L                 | 200 μH,   |

| Output Capacitor C <sub>O</sub>         | 220 µF    |

| Full-load $R_L$                         | 331.77 Ω. |

Table 1. Design specifications for the control system of the converter.

**Figure 8.** Bode plot of compensated control to input current transfer function: phase margin (PM) =  $90^{\circ}$  at 177 k rad/s.

**Figure 9.** Bode plot of compensated control to input current transfer function:  $PM = 59.8^{\circ}$  at 31.5 k rad/s (5000 Hz).

The transfer function of a PI controller is given by:

$$T_{C1}(s) = K_p + \frac{K_i}{s} = \frac{K_p(s + K_i/K_p)}{s}$$

(33)

The open-loop transfer function of the current loop is given by:

$$T_{OL1}(s) = T_{C1}(s) \times T_m(s) \times T_{p1}(s) \times H_1(s)$$

(34)

LEM sensor LA25-NP is used to sense the inductor current and to provide the isolation between power circuit and controller. Here,  $H_1(s)$  is the current feedback gain and  $T_m(s)$  is the overall gain of the modulator.

Here, the current feedback gain is selected as  $H_1(s) = 1$ .

Overall gain of the modulator is chosen to be:

$$T_m(s) = \frac{1}{10} \tag{35}$$

To realize  $PM = 60^{\circ}$ , the following angle condition for the open-loop transfer function is applied:

$$T_{OL1}(jw_c) = PM - 180^{\circ} \tag{36}$$

$$T_{OLI}(jw_c) = \frac{106572K_p \left( jw_c + \frac{K_i}{K_p} \right) (jw_c + 73.02)}{jw_c (jw_c^2 + 13.72jw_c + 81502.34jw_c)}$$

(37)

To realize the desired crossover frequency, the following gain condition of unity is applied for the open-loop transfer function, i.e.,  $|T_{OL1}(jw_c)| = 1$ :

$$k_p^2 \left( 1.5625 \times 10^{10} + \frac{k_i^2}{k_p^2} \right) = 4.875 \times 10^{11}$$

(38)

PI controller parameters are designed to obtain PM of  $60^{\circ}$  [21,22] at the gain crossover frequency of 31.5k rad/s (5000 Hz) (Figure 9). Low-frequency gain is improved. It results in the gain  $K_p$  and  $K_i$  as 0.16 and 7269.58, respectively.

#### 3.2. Voltage Control Loop Design

The outer voltage control loop regulates the output voltage at the reference value by setting reference for the current through the input inductors as shown in Figure 10. The inner current control loop has faster dynamics compared to the outer voltage loop. Hence, the current loop dynamics are neglected during the design of the voltage controller [23]. Its transfer function is not included, and the perturbation in the duty cycle can be neglected. Therefore, the inductor current to output voltage transfer function  $T_{p2}(s)$  is obtained as:

$$T_{p2}(s) = \frac{v_o(s)}{\hat{i}_{L1}(s) + \hat{i}_{L2}(s)} = \frac{(1-D)}{nC_o\left(s + \frac{1}{R_L C_o}\right)}$$

(39)

$$T_{P2}(s) = \frac{0.35}{0.001848s + 0.025} \tag{40}$$

LEM sensor LV20-P is used to sense output voltage and also to provide the necessary isolation. Here, the voltage feedback gain is chosen as:

$$H_2(s) = 24$$

(41)

Figure 10. Outer voltage control loop schematic diagram.

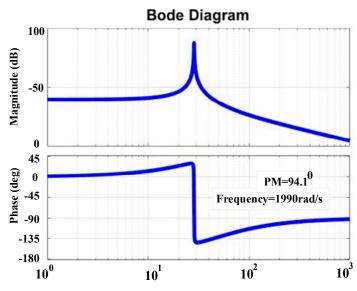

Figure 11 shows the bode plot for the uncompensated voltage control loop. For the given specifications and selected component values, the crossover frequency is high with poor low-frequency gain.

**Figure 11.** Bode plot of uncompensated plant in voltage control loop: PM = 94.1° at 1990 rad/s.

The overall open-loop transfer function of the voltage loop is given by:

$$T_{OL2}(s) = T_{C2}(s) \times T_{p2}(s) \times H_2(s) \times \frac{1}{H_1(s)}(47)$$

(42)

$$T_{OLI}(s) = \frac{0.35K_p \left(s + \frac{K_i}{K_p}\right)}{0.001848s^2 + 0.025s}$$

(43)

The gain crossover frequency for the voltage controller is selected to be 10 times slower than that of the inner current loop. Application of angle and gain conditions similar to the current control loop for the desired PM of  $60^{\circ a}$  at gain crossover frequency of 3150 rad/s results in the gain  $K_p$  and  $K_i$  as 16.83 and 9767.8, respectively. Taking into account the dynamics of the current control loop, the overall transfer function of the system can be given as Equation (44).

$$T_{OL}(s) = \left[\frac{T_{C1}(s) \times T_{p1}(s) \times T_m(s) \times H_1(s)}{1 + T_{C1}(s) \times T_{p1}(s) \times T_m(s) \times H_1(s)}\right] \times T_{C2}(s) \times T_{p2}(s) \times H_2(s) \times \frac{1}{H_1(s)}$$

(44)

The Bode plot of the compensated voltage control loop is shown in Figure 12. Low-frequency gain is improved, indicating reduced steady-state error. The desired positive PM of 60° indicates a stable system rejecting disturbances for wide operating input voltage and load power variations.

Figure 12. Bode plot of the compensated voltage control loop system:  $PM = 60^{\circ}$  at 3150 rad/s (500 Hz).

### 4. Simulation and Experimental Results

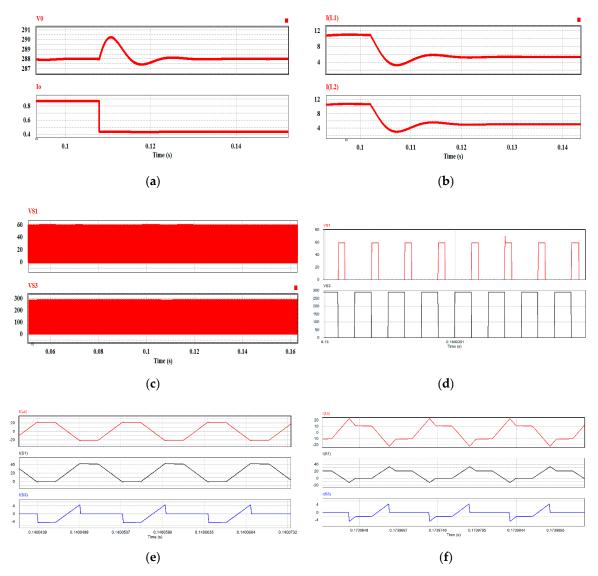

The simulation model of the circuit topology and two-loop control was developed on software package PSIM 11 and was run to capture waveforms and observe transient performance of the converter under load-current variations. Simulation results are illustrated in Figures 13 and 14.

**Figure 13.** Simulation waveforms for  $V_{in} = 12$  V with step change in load from 50% load to rated full load; (a)  $V_o$  is output voltage,  $I_o$  is output current, (b)  $I_{L1}$  and  $I_{L2}$  are input inductor currents, and (c)  $V_{s1}$  and  $V_{s3}$  are voltages across the switches  $S_1$  and  $S_3$ , respectively.

**Figure 14.** Simulation waveforms for  $V_{in} = 12$  V with step change in load from rated load to half load with identical nomenclature. (a)  $V_0$  is output voltage,  $I_0$  is output current, (b)  $I_{L1}$  and  $I_{L2}$  are input inductor currents, and (c)  $V_{s1}$  and  $V_{s3}$  are voltages across the switches  $S_1$  and  $S_3$ , respectively, (d) zoomed waveform of  $V_{s1}$  and  $V_{s3}$ , (e).  $I_{Ls}$  is the transformer primary current and  $I_{S1}$  and  $I_{S2}$  are the current through the switches  $S_1$  and  $S_3$ , respectively at full-load steady-state and (f)  $I_{Ls}$  is the transformer primary current and  $I_{S1}$  and  $I_{S2}$  are the current through the switches  $S_1$  and  $I_{S2}$  are the current through the switches  $S_1$  and  $I_{S2}$  are the current through the switches  $S_1$  and  $I_{S2}$  are the current through the switches  $S_1$  and  $S_3$ , respectively at half-load steady-state.

The load is changed from 50% load to rated load (Figure 13) and from full load to 50% load (Figure 14). It should be observed that the overshoot or undershoot in output voltage for both step changes is 2V, which demonstrates the excellent stability of control. Load current and the two input inductor currents smoothly change to the next steady-state value. The settling time of the inductors' current and load voltage is nearly 25 ms. The voltage across the primary switches (VS1) is clamped at the reflected output voltage, and the voltage across the secondary devices (VS3) is clamped at the output voltage V<sub>o</sub> without any overshoot during the load transients, ensuring safe operation of the converter. Figure 14d (zoomed waveform in transient period) shows voltage across the primary side devices is always clamped at output voltage. Figure 14e,f shows steady-state (zoomed) waveforms at rated load and half load, respectively. It should be noted that primary side devices maintain ZCS, and secondary side devices maintain ZVS under both conditions.

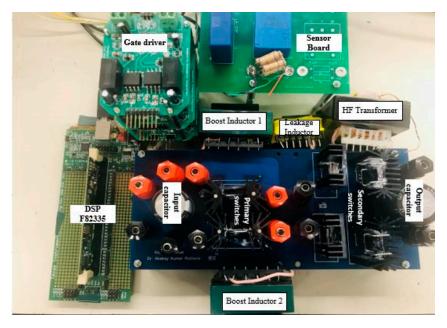

Figure 15 shows the experimental prototype of the converter. It is operated by the designed controller, which has been tested in the laboratory for the step changes in load for a fixed 12 V input voltage. Table 2 shows the details of the components used in the hardware prototype.

Figure 15. Laboratory prototype of the half-bridge converter.

| IRFB4127PbF 200 V, 76 A, $R_{ds,on} = 17 \text{ m}\Omega$                            |

|--------------------------------------------------------------------------------------|

| IPP60R125CP 650 V, 11 A, $R_{ds,on} = 0.125 \ \Omega$                                |

| TDK5901PC40Z core, 3.9 μH                                                            |

| 3C95ETD49 ferrite core; $N_1 = 5$ , $N_2 = 45$                                       |

| 3C95ETD49 ferrite core, $N = 42$ , $L = 200 \ \mu H$                                 |

| 220 μF, 450 V electrolytic capacitor<br>0.68 μF, 450 V high frequency film capacitor |

|                                                                                      |

Table 2. Component parameters of the hardware prototype.

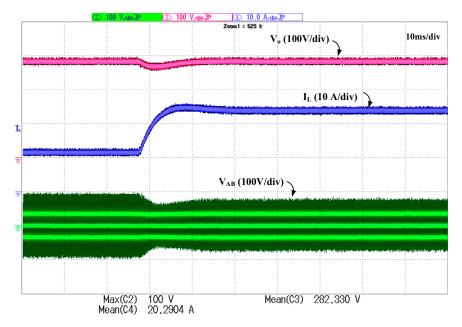

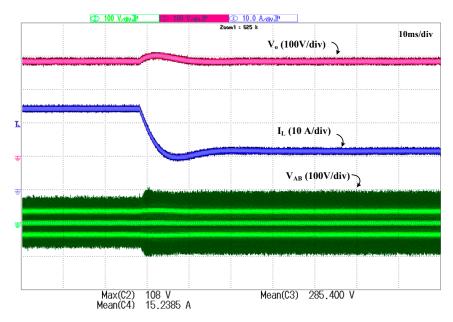

Gating signals for the semiconductor devices are generated by Texas Instruments (TI) digital signal processor (DSP) TMS320F28335. Experimental waveforms for the step change in load are shown in Figures 16 and 17. Figure 16 demonstrates the experimental waveforms of inductor current  $i_L$ , voltage  $V_{AB}$ , and output voltage  $V_o$  with respect to time for the step change in load from rated load to 50% load. The similar waveforms for step change in load from 50% to rated load are manifested in Figure 17. Overshoot and undershoot in the output voltage are negligible during load transients. Further, output voltage  $V_o$  is maintained at the constant value. The variations in inductor current  $I_L$  and  $V_{AB}$  (transformer primary voltage, that is, the sum of voltage across the two primary switches  $S_1$  and  $S_2$ ) are within safe limiting values. Therefore, the switches do not experience any voltage spike during transition, which ensures safe and normal operation of the converter. Inductor current  $I_L$  is adjusted to their new steady-state values smoothly. The settling time is nearly 20 ms. This demonstrates stable performance over a wide load variation. It should be noticed that the experimental settling time is higher than the simulation value because the hardware experiences power loss, voltage drop, stray inductance/capacitance, system delay, and parasitic elements, which cause aberration from the ideal model. Better dynamic performance may be achieved by proper tuning of the controller parameters.

**Figure 16.** Hardware result for step change in load from 50% load to full load: (1) voltage  $V_{AB}$  (100 V/div), (2) inductor current  $i_L$  (10 A/div), and (3) output voltage  $V_o$  (100 V/div).

**Figure 17.** Hardware result for step change in load from full load to 50% load: (1) voltage  $V_{AB}$  (100 V/div), (2) inductor current  $i_L$  (10 A/div), and (3) output voltage  $V_o$  (100 V/div).

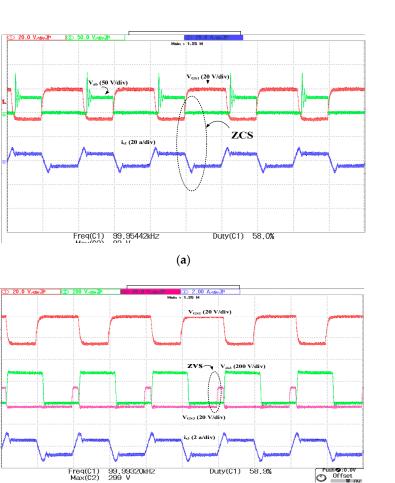

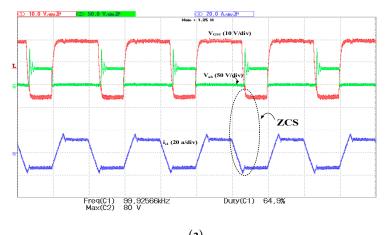

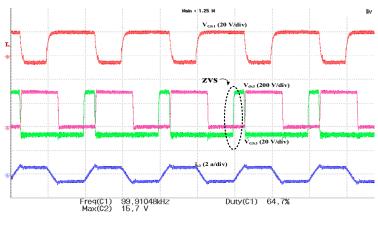

Figures 18 and 19 show the steady-state zoomed waveforms under half load and full load, respectively. Figures 18a and 19a show the gate-to-source  $V_{GS}$  and drain-to-source  $V_{ds}$  voltage waveforms across primary side MOSFET and transformer primary current  $i_s$  waveform at half load and full load, respectively. It is clearly demonstrated that the current through the switch naturally goes to zero. The negative current shows the antiparallel body diode conduction across the switch before turning off the gating signals, ensuring ZCS turn-off of the primary side semiconductor devices.

(b)

**Figure 18.** Experimental results for  $v_{in} = 12$  V at 50% load: (a) gate-to-source voltage  $V_{Gs1}$  (20 V/div), current across primary-side MOSFET  $i_{s1}$  (20 A/div), and voltage  $V_{AB} = 50$  V/div; (b) gate-to-source voltage  $V_{GS3}$  (20 V/div), drain-to-source voltage  $V_{ds3}$  (200 V/div), and current across secondary-side MOSFET  $i_{s3}$  (2 A/div).

(a) Figure 19. Cont.

(b)

**Figure 19.** Experimental results for  $v_{in} = 12$  V at full load: (a) gate-to-source voltage  $V_{Gs1}$  (20 V/div), current across primary-side MOSFET  $i_{s1}$  (20 A/div), and voltage  $V_{AB} = 50$  V/div; (b) gate-to-source voltage  $V_{GS3}$  (20 V/div), drain-to-source voltage  $V_{ds3}$  (200 V/div), and current across secondary-side MOSFET  $i_{s3}$  (2 A/div).

Voltage waveforms  $V_{GS}$  and  $V_{DS}$  across the devices clearly demonstrate the ZCS of the primary side devices and ZVS of the secondary side devices under both load conditions. The results are satisfactory during the transients that occurred due to sudden load disturbances while maintaining the steady-state performance. The steady-state performance is retained at the originally proposed in [17]. Corresponding gate-to-source  $V_{GS}$  and drain-to-source voltage  $V_{ds}$  waveforms of the secondary side devices are shown in Figures 18b and 19b. In these waveforms, gate-to-source voltage ( $V_{GS}$ ) is applied when the voltage across secondary device  $V_{DS}$  is zero already, which ensures ZVS operation in secondary devices. It confirms the soft-switching of all the devices.

Table 3 shows the comparison between the conventional active-clamped converter and the proposed snubberless topology. It is clear from the comparison that the snubberless operation with proposed control has several merits in terms of voltage gain, efficiency, reduced current, transformer size, and soft-switching range. Simple control has resulted in these merits with a demerit of limited duty range.

| Topology                        | Active-Clamped                                                                 | Proposed Snuberless                                                       |

|---------------------------------|--------------------------------------------------------------------------------|---------------------------------------------------------------------------|

| Soft-switching                  | ZVS<br>(soft-switching at turn-on)                                             | ZCS<br>(soft-switching at turn-off)                                       |

| Soft-switching range            | Limited range<br>(soft-switching is lost with the source<br>voltage variation) | Full range<br>(inherent soft-switching for the entire<br>operating range) |

| Device voltage                  | Higher voltage and variable with duty cycle                                    | Clamped at reflected output voltage and<br>duty cycle independent         |

| Boost Capability (voltage gain) | Voltage gain (boost) is compromised;<br>20% reduction at rated load            | Natural boost gain                                                        |

| Device RMS current              | Circulating current is present that increases average and RMS value            | 10% reduction in the rms current due to the absence of active clamp       |

| Device peak current             | 1.5× input current                                                             | Same as input current (33% less)                                          |

| Transformer current             | Same as input current                                                          | Half of the input current (50% less)                                      |

| Efficiency                      | High                                                                           | 2% improvement                                                            |

| Power flow                      | Unidirectional                                                                 | Bidirectional                                                             |

| Duty cycle variation            | Wide range (0 to 1)                                                            | Limited (0.5 to 1)                                                        |

| Transformer                     | Higher turns ratio, higher kVA rating and volume                               | Relatively lower turns ratio, reduced kVA rating and volume (40% less)    |

Table 3. Comparison of proposed snubberless topology with active-clamped topology.

#### 5. Conclusions

This paper studied small-signal modeling and derived transfer functions of an isolated naturally clamped snubberless current-fed half-bridge DC-DC converter. A two-loop average current controller was designed offering fixed-frequency duty cycle modulation of the semiconductor devices using two controllers. Initial verification of the small-signal model and the controller was done using PSIM 11 and investigation of the dynamic performance of the converter. Experimental results on a laboratory hardware proof-of-concept prototype demonstrated the satisfactory and smooth transient performance of the converter and the effectiveness of the designed closed-loop controller. The simplicity of implementation and practicality of the proposed control are the benefits of the overall system. The proposed analysis is effective for non-isolated as well as interleaved half-bridge and interleaved-boost topologies. It is suitable for fuel cell applications.

**Author Contributions:** Formal analysis, K.K.; Funding acquisition, A.K.R.; Methodology, K.K., V.V.R., and B.L.N.; Project administration, V.V.R.; Resources, A.K.R.; Software, B.L.N.; Supervision, A.K.R.; Validation, K.K. and V.V.R.; Writing—original draft, K.K. and V.V.R.; Writing—review and editing, A.K.R. and B.L.N. All authors have read and agreed to the published version of the manuscript.

**Funding:** This research was funded by the Natural Sciences and Engineering Research Council of Canada (NSERC), grant number N01678.

**Acknowledgments:** The authors would like to acknowledge the support of the National Institute of Technology, Warangal, India and the support of Scheme for Promotion of Academic and Research Collaboration (SPARC) funded by MHRD, Government of India with file no SPARC/2018-2019/P1392/SL. SPARC, India.

Conflicts of Interest: The authors declare no conflict of interest.

### References

- 1. Aso, S.; Kizaki, M.; Nonobe, Y. Development of hybrid fuel cell vehicles in Toyota. In Proceedings of the IEEE Power Conversion Conference, Nagoya, Japan, 2–5 April 2007; pp. 1606–1611.

- 2. Emadi, A.; Williamson, S.S. Fuel cell vehicles: Opportunities and challenges. In Proceedings of the IEEE Power Engineering Society General Meeting, Denver, CO, USA, 6–10 June 2004; pp. 1640–1645.

- Emadi, A.; Rajashekara, K.S.; Williamson, S.S.; Lukic, S.M. Topological overview of hybrid electric and fuel cell vehicular power system architectures and configurations. *IEEE Trans. Veh. Technol.* 2005, 54, 763–770. [CrossRef]

- Khaligh, A.; Li, Z. Battery, Ultracapacitor, FuelCell, and Hybrid Energy Storage Systems for Electric, Hybrid Electric, FuelCell, and Plug-In Hybrid Electric Vehicles: State of the Art. *IEEE Trans. Veh. Technol.* 2010, 59, 2806–2814. [CrossRef]

- Rathore, A.K.; Bhat, A.K.S.; Oruganti, R. Analysis, Design and Experimental Results of Wide Range ZVS Active-Clamped L-L Type Current-Fed DC/DC Converter for Fuel Cells to Utility Interface. *IEEE Trans. Ind. Electron.* 2011, 59, 473–485. [CrossRef]

- 6. Wu, T.-F.; Chen, Y.-C.; Yang, J.-G.; Kuo, C.-L. Isolated bidirectional full-bridge DC–DC converter with a flyback snubber. *IEEE Trans. Power Electron.* **2010**, *25*, 1915–1922.

- Su, G.-J.; Adams, D.J.; Peng, F.Z.; Li, H. Experimental evaluation of a soft-switching DC/DC converter for fuel cell vehicle applications. In Proceedings of the Power Electronics in Transportation, Auburn Hills, MI, USA, 24–25 October 2002; pp. 39–44.

- Song, W.; Lehman, B. Current-fed dual-bridge DC–DC converter. *IEEE Trans. Power Electron.* 2007, 22, 461–469. [CrossRef]

- 9. Averberg, A.; Meyer, K.R.; Mertens, A. Current-fed full-bridge converter for fuel cell systems. In Proceedings of the IEEE Power Electronics Specialists Conference, Rhodes, Greece, 15–19 June 2008; pp. 866–872.

- Yakushev, V.; Meleshim, V.; Fraidlin, S. Full bridge isolated current fed converter with active-clamp. In Proceedings of the IEEE Applied Power Electronics Conference, Dallas, TX, USA, 14–18 March 1999; pp. 560–566.

- Rathore, A.K.; Prasanna, U.R. Comparison of soft-switching voltage-fed and current-fed bi-directional isolated Dc/Dc converters for fuel cell vehicles. In Proceedings of the IEEE International Symposium on Industrial Electronics, Hangzhou, China, 28–31 May 2012; pp. 252–257.

- Zhu, L. A Novel Soft-Commutating Isolated Boost Full-bridge ZVS-PWM DC-DC Converter for Bi-directional High Power Applications. In Proceedings of the 2004 IEEE 35th Annual Power Electronics Specialists Conference, Aachen, Germany, 20–25 June 2004; Volume 21, pp. 422–429.

- Kim, E.S.; Joe, K.Y.; Choi, H.Y.; Kim, Y.H.; Cho, Y.H. An Improved Soft Switching Bi-directional PSPWM FB DC/DC Converter. In Proceedings of the IEEE Industrial Electronics Conference, Aachen, Germany, 31 August–4 September 1998; pp. 740–743.

- 14. Miura, Y.; Kaga, M.; Horita, Y.; Ise, T. Bidirectional Isolated Dual Full-bridge dc-dc Converter with Active Clamp for EDLC. In Proceedings of the IEEE Energy Conversion Congress and Exposition, Atlanta, GA, USA, 12–16 September 2010; pp. 1036–1143.

- Wang, K.; Lin, C.Y.; Zhu, L.; Qu, D.; Lee, F.C.; Lai, J.S. Bidirectional DC/DC Converters for Fuel Cell Systems. In Proceedings of the IEEE Power Electronics in Transportation, Dearborn, MI, USA, 22–23 October 1998; pp. 47–51.

- Wang, K.; Lee, F.C.; Lai, J. Operation Principles of Bi-directional Full-bridge DC/DC Converter with Unified Soft switching Scheme and Soft-starting Capability. In Proceedings of the IEEE Applied Power Electronics Conference and Exposition, New Orleans, LA, USA, 6–10 February 2000; pp. 111–118.

- 17. Rathore, A.K.; Prasanna, U.R. Analysis, design, and experimental results of novel snubberless bi-directional naturally clamped ZCS/ZVS current-fed half-bridge dc/dc converter for fuel cell vehicles. *IEEE Trans. Ind. Electron.* **2013**, *60*, 4482–4491. [CrossRef]

- Khatun, K.; Rathore, A.K. Small Signal Modeling, Closed Loop Design, and Transient Results of Snubberless Naturally-Clamped Soft-Switching Current-Fed Half-bridge DC/DC Converter. In Proceedings of the IEEE International Symposium on Industrial Electronics (ISIE), Vancouver, BC, Canada, 12–14 June 2019; pp. 2571–2576.

- Lai, J.; Park, S.; Moon, S.; Chen, C.L. A High-Efficiency 5-kW Soft-Switched Power Conditioning System for Low-Voltage Solid Oxide Fuel Cells. In Proceedings of the IEEE Power Conversion Conference-Nagoya, Nagoya, Japan, 2–5 April 2007; pp. 463–470.

- Venkatraman, R.; Bhat, A.K.S. Small-signal analysis of a soft-switching, single-stage two-switch AC-to-DC converter. In Proceedings of the IEEE Power Electronics Specialists Conference, Vancouver, BC, Canada, 17–21 June 2001; pp. 1824–1830.

- 21. Krein, P. Elements of Power Electronics, 2nd ed.; Oxford University Press: Oxford, UK, 2014.

- 22. Bibian, S.; Jin, H. High performance predictive dead-beat digital controller for DC power supplies. *IEEE Trans. Power Electron.* **2002**, 17, 420–426. [CrossRef]

- 23. Erickson, R.; Madigan, M.; Singer, S. Design of a simple high-power-factor rectifier based on the flyback converter. In Proceedings of the IEEE Applied Power Electronics Conference and Exposition (APEC), Los Angeles, CA, USA, 11–16 March 1990; pp. 792–801.

© 2020 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).