Article

# Analysis of Work-Function Variation Effects in a Tunnel Field-Effect Transistor Depending on the Device Structure

# Garam Kim<sup>1</sup>, Jang Hyun Kim<sup>2</sup>, Jaemin Kim<sup>1</sup> and Sangwan Kim<sup>3,\*</sup>

- <sup>1</sup> Department of Electronic Engineering, Myongji University, Yongin 17058, Korea; garamkim@mju.ac.kr (G.K.); jaemin@esl.mju.ac.kr (J.K.)

- <sup>2</sup> School of Electrical Engineering, Pukyong National University, 45 Yongso-ro, Nam-gu, Busan 608-737, Korea; janghyun@pknu.ac.kr

- <sup>3</sup> Department of Electrical and Computer Engineering, Ajou University, Suwon 16499, Korea

- \* Correspondence: sangwan@ajou.ac.kr

Received: 7 May 2020; Accepted: 3 August 2020; Published: 4 August 2020

# Featured Application: This work can be applied to analyze and reduce the WFV effect of TFETs.

**Abstract:** Metal gate technology is one of the most important methods used to increase the low on-current of tunnel field-effect transistors (TFETs). However, metal gates have different work-functions for each grain during the deposition process, resulting in work-function variation (WFV) effects, which means that the electrical characteristics vary from device to device. The WFV of a planar TFET, double-gate (DG) TFET, and electron-hole bilayer TFET (EHBTFET) were examined by technology computer-aided design (TCAD) simulations to analyze the influences of device structure and to find strategies for suppressing the WFV effects in TFET. Comparing the WFV effects through the turn-on voltage (V<sub>turn-on</sub>) distribution, the planar TFET showed the largest standard deviation ( $\sigma$ V<sub>turn-on</sub>) of 20.1 mV, and it was reduced by –26.4% for the DG TFET and –80.1% for the EHBTFET. Based on the analyses regarding metal grain distribution and energy band diagrams, the WFV of TFETs was determined by the number of metal grains involved in the tunneling current. Therefore, the EHBTFET, which can determine the tunneling current by all of the metal grains where the main gate and the sub gate overlap, is considered to be a promising structure that can reduce the WFV effect of TFETs.

**Keywords:** tunnel field-effect transistors (TFETs); work-function variation (WFV); electron-hole bilayer TFET (EHBTFET)

## 1. Introduction

The trend towards reducing the power consumption and improving the scale-down properties of complementary metal-oxide semiconductor (CMOS) devices results in a decreased voltage supply. To achieve a high on/off current ratio at a low supply voltage, the subthreshold swing (SS) must be lowered. However, metal-oxide-semiconductor (MOS) field-effect transistors (MOSFETs) cannot lower the SS below 60 mV/dec due to the physical limitations of their operation [1–3]. To overcome this problem, new devices based on various principles have been proposed and studied, such as the negative capacitance field-effect transistor (NCFET) [4–6], resistive gate field-effect transistor (FET) (ReFET) [7], nano-electro mechanical FET (NEMFET) [8,9], positive feedback FET [10,11], impact ionization metal-oxide-semiconductor (I-MOS) [12,13], conventional transistor with an oxide-based threshold switching device [14], and tunnel FET (TFET) [15–22]. Among them, TFETs are considered

as one of the most promising ultra-low power devices due to its high CMOS process compatibility and low-level leakage current [15–22].

However, TFETs suffer from low-level on-current ( $I_{on}$ ) as an alternative of MOSFETs. Therefore, there have been much research to improve the  $I_{on}$  of TFETs by modifying the materials and structures of TFETs [23–31]. Among them, metal gate technology, which is also widely used in MOSFETs, can improve the gate controllability and increase  $I_{on}$  by eliminating the polysilicon depletion effect [32]. However, metal gates have different work-functions for each grain due to different grain orientations during the deposition process. This results in a work-function variation (WFV) effect that causes variations in the threshold voltage ( $V_{th}$ ) and other electrical characteristics of TFETs [33]. In this study, the WFV effects of a planar TFET, a double gate (DG) TFET, and an electron-hole bilayer TFET (EHBTFET) are compared using technology computer-aided design (TCAD) simulations to analyze the effects of the structure and to find a way to improve the WFV of TFETs. In the case of the planar TFET and DG TFET, a tunneling current occurs along the channel (lateral tunneling) at the source junction. On the contrary, the tunneling current of the EHBTFET is generated across the channel (vertical tunneling) at the body between two gates, and the electrical characteristics of this structure have been actively studied through TCAD simulations and modeling [34–38].

#### 2. Device Structure and Simulation Method

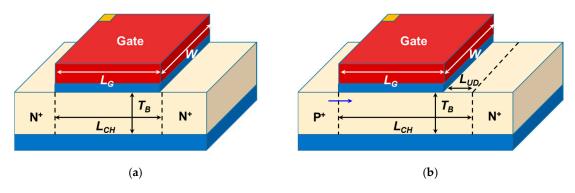

Figure 1 shows the structures of MOSFET (Figure 1a), planar TFET (Figure 1b), DG TFET (Figure 1c), and EHBTFET (Figure 1d) used in this research. The design parameters used for the simulations are summarized in Table 1. In the modern integrated chip (IC) process, the grain size of the metal gate has a range of approximately 5 to 20 nm [39,40]. The grain size decreases when the DC (direct current) power of the sputtering process increases [40]. On the other hand, the grain size increases when the process temperature increases during or after the deposition process [39,41]. In this research, TiN (titanium nitride) was applied as the gate metal for the WFV effect analysis. In the case of TiN, it is also known that the grain size can be reduced by incorporating Cu or C when the TiN layer is deposited [42,43]. In this simulation and analysis, each metal grain was assumed to be a cube with a side length of 10 nm within the general range of the modern IC process. With regard to the WF value distribution of TiN, much research is still on-going, in order to develop a better understanding of the WF variation in TiN (e.g., considering the work-function (WF) of the grain boundary [44] and increment of the high-WF grain portion with the increased process temperature [41]). In this study, it was assumed that 60% of TiN grains were crystallized in <200> with 4.6 eV WF and 40% were crystallized in <111> with 4.4 eV WF, which are generally accepted values [39]. The blue arrows in Figure 1 indicate the positions where the tunneling mainly occurs in the on-state of each structure. Unlike the planar TFET and DG TFET, where tunneling occurs at the boundary between the source and channel region, EHBTFET has a tunneling current between the main gate (MG) and the sub gate (SG), as shown by the arrow in Figure 1d.

Figure 1. Cont.

**Figure 1.** Basic schematics and major parameter definitions of the (**a**) metal-oxide-semiconductor field-effect transistor (MOSFET), (**b**) planar tunnel field-effect transistor (TFET), (**c**) double-gate (DG) TFET, and (**d**) electron-hole bilayer TFET (EHBTFET) used in this research.

| Table 1. Device | parameters of devices u | used for the technology | computer-aided design | n (TCAD) simulation. |

|-----------------|-------------------------|-------------------------|-----------------------|----------------------|

|                 |                         |                         |                       |                      |

| Parameter                                       | Value                        |

|-------------------------------------------------|------------------------------|

| Gate length (L <sub>G</sub> )                   | 70 nm                        |

| Channel width (W)                               | 70 nm                        |

| Equivalent oxide thickness (EOT)                | 2 nm                         |

| Channel length (L <sub>CH</sub> )               | 90 nm                        |

| Channel thickness $(T_B)$                       | 10 nm                        |

| Drain underlap (L <sub>UD</sub> )               | 20 nm                        |

| Source underlap (L <sub>US</sub> )              | 20 nm                        |

| MOSFET source/drain doping concentration        | $10^{20} \text{ cm}^{-3}$    |

| TFET <i>p</i> -type source doping concentration | $10^{20} \text{ cm}^{-3}$    |

| TFET <i>n</i> -type drain doping concentration  | $10^{18} \text{ cm}^{-3}$    |

| Gate work function                              | 4.6 eV (60%)<br>4.4 eV (40%) |

In order to compare and analyze the WFV effects of each structure, three-dimensional (3D) simulations were conducted using Synopsys Senataurus<sup>TM</sup> (Ver. K-2015.06-SP1, Synopsys, Mountain View, CA, USA) [45]. Fermi–Dirac statistics, doping concentration dependent mobility, Shockley–Read–Hall (SRH) recombination, and modified local density approximation (MLDA) models were used to calculate and extract the electrical characteristics of TFETs in the simulation. For an accurate calculation of band-to-band tunneling (BTBT), a dynamic non-local BTBT model was applied with theoretically calculated parameters [46] generally used in recent TFET research [47–49].

### 3. Results and Discussions

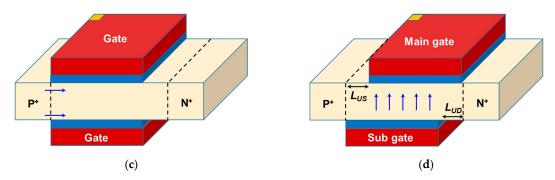

Figure 2 shows the transfer characteristics of the MOSFET, planar TFET (Figure 2b), DG TFET (Figure 2c), and EHBTFET (Figure 2d) when the drain voltage ( $V_D$ ) is 0.5 V and source voltage ( $V_S$ ) is 0 V. The metal grain profiles of the gate area were randomly generated by the randomization algorithm provided in the Sentaurus tool, depending on the TiN grain orientation. Thirty samples with uniquely randomized metal gate grain profiles for each structure were used for the simulation and the WFV effect analysis in this research. In the case of the EHBTFET in Figure 2c, a voltage of -0.67 V was applied to the SG to transport the holes from the source region to the channel region near SG and generate BTBT between the MG and the SG. For a comparison of the WFV effects, the average and standard deviation of  $V_{th}$ , SS and  $I_{on}$  for each structure were obtained and are summarized in Table 2. The  $V_{th}$  of MOSFET is defined as the gate voltage when  $V_D$  is 0.5 V and the drain current is  $10^{-12}$  A. Instead of  $V_{th}$ , the turn-on voltage ( $V_{turn-on}$ ) of TFETs is defined as the gate voltage current, and is extracted when  $V_D$  is 0.5 V and the drain current is  $10^{-18}$  A. In this research,  $V_{turn-on}$  was used for the WFV analysis instead of  $V_{th}$ , because the drain current of TFETs is much lower than that of MOSFETs,

the definition of V<sub>th</sub> in TFETs is controversial [50,51], and the SS variation effect of TFETs is large [33]. SS is defined as an average swing when the drain current is increased from  $10^{-12}$  to  $10^{-10}$  A (MOSFET) or  $10^{-18}$  to  $10^{-16}$  A (TFET). I<sub>on</sub> is defined as the drain current when V<sub>G</sub> is average V<sub>turn-on</sub> (average V<sub>th</sub> in MOSFETs) + 0.6 V and V<sub>D</sub> is 0.5 V. As shown in Figure 2 and Table 2, the  $\sigma$ V<sub>turn-on</sub> of the planar TFET has the largest value (20.1 mV). In the case of the DG TFET,  $\sigma$ V<sub>turn-on</sub> is reduced by -26.4% in comparison to the planar TFET. Moreover, in the EHBTFET, the  $\sigma$ V<sub>turn-on</sub> is drastically reduced to -80.1% compared to the planar TFET, showing the smallest  $\sigma$ V<sub>turn-on</sub> among the three types of TFET structures. The  $\sigma$ S and normalized  $\sigma$ I<sub>on</sub> also show the same tendency as  $\sigma$ V<sub>turn-on</sub>.

**Figure 2.** Transfer characteristics of the (**a**) MOSFET, (**b**) planar TFET, (**c**) DG TFET and (**d**) EHBTFET when the drain voltage (V<sub>D</sub>) is 0.5 V.

**Table 2.** Average and standard deviation of the turn-on voltage ( $V_{turn-on}$ ), subthreshold swing (SS), and on-current ( $I_{on}$ ) of the devices extracted from Figure 2.

|                                                         | MOSFET                                      | Planar TFET                                 | DG TFET                                     | EHBTFET                                      |

|---------------------------------------------------------|---------------------------------------------|---------------------------------------------|---------------------------------------------|----------------------------------------------|

| Average V <sub>th</sub> or Average V <sub>turn-on</sub> | -55.0 mV                                    | 325.1 mV                                    | 283.0 mV                                    | 680.4 mV                                     |

| $\sigma V_{th}$ or $\sigma V_{turn-on}$                 | 14.0 mV                                     | 20.1 mV                                     | 14.8 mV                                     | 4.0 mV                                       |

| Average SS                                              | 121.6 mV/decade                             | 64.3 mV/decade                              | 54.5 mV/decade                              | 4.6 mV/decade                                |

| σSS                                                     | 0.5 mV/decade                               | 5.6 mV/decade                               | 4.7 mV/decade                               | 1.2 mV/decade                                |

| Average I <sub>on</sub>                                 | $7.11 \times 10^{-4} \text{ A/}\mu\text{m}$ | $1.08 \times 10^{-9} \text{ A/}\mu\text{m}$ | $3.26 \times 10^{-9} \text{ A/}\mu\text{m}$ | $4.33 \times 10^{-10} \text{ A/}\mu\text{m}$ |

| σI <sub>on</sub> /Average I <sub>on</sub>               | 0.122                                       | 0.348                                       | 0.263                                       | 0.155                                        |

V<sub>th</sub>: threshold voltage.

The reduction in the WFV effect on the DG TFET and EHBTFET compared to the planar TFET can be interpreted as a result of an increase in the number of metal grains that affect  $V_{turn-on}$  determination. It is known that as the number of metal grains affecting  $V_{turn-on}$  increases, the WFV effect is suppressed by a higher averaging effect [52–54]. When the number of grains changes, the variance of the WF distribution (var( $\Phi_M$ )) according to the number of grains (*N*) can be expressed as the following equation [55]:

$$\operatorname{var}(\Phi_{M}) = \frac{1}{N} \left[ \sum_{i=1}^{r} P_{i} \Phi_{i}^{2} - \left( \sum_{i=1}^{r} P_{i} \Phi_{i} \right)^{2} \right]$$

(1)

where  $\Phi_i$  and  $P_i$  represent the WF value of each grain and the probability of achieving the WF value. As can be seen from (1), var( $\Phi_M$ ) and the resulting WFV effects change when *N* changes. For example, as the grain size of the metal gate increases during the fabrication process (e.g., increase in the heat budget), the number of grains affecting the characteristics of the device decreases and the WFV effects increase. If the grain size is large enough that the overall gate area is filled by one metal grain, the V<sub>turn-on</sub> of 60% of devices is determined by a metal grain with a 4.6 eV WF and the V<sub>turn-on</sub> of the other 40% of devices is determined by a metal grain with a 4.4 eV WF. On the other hand, when the grain size of the metal gate is reduced during the fabrication process (e.g., by incorporating carbon into TiN), the WFV effects can be reduced [43]. If the grain size is continuously reduced and the metal gate reaches an almost amorphous state, it can be considered that there is no difference among the grain distributions of each device and the V<sub>turn-on</sub> values of all the devices converge to the average V<sub>turn-on</sub>.

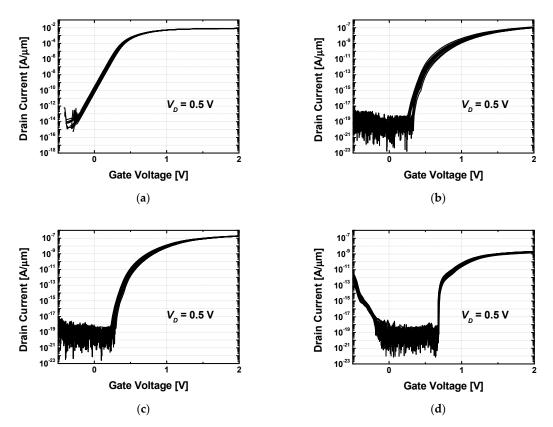

As the grain size controlled by the process condition can affect the number of grains and the WFV effects, the device structure of TFETs can also affect the WFV effect if the structure can change the grain number, having effects on the V<sub>turn-on</sub> determination. In order to analyze the reason why the  $\sigma$ V<sub>turn-on</sub> of the TFETs is different, depending on the structures, the metal grain distributions and the energy band diagrams were compared for the lowest and highest V<sub>turn-on</sub> among the simulated results of planar TFETs with the randomly generated metal grain profiles. Figure 3a,b show the metal grain distributions of planar TFETs, with the highest value of V<sub>turn-on</sub> at 0.367 V and the lowest value at 0.289 V, respectively. In the gate region of Figure 3a,b, a red color represents metal grains with WF of 4.6 eV, while a blue color shows other grains with WF of 4.4 eV. Comparing Figure 3a,b, there is a clear difference between the two samples in terms of the distribution of metal grains adjacent to the source region. Figure 3a, with high V<sub>turn-on</sub>, shows that most of the metal grains close to the source region have a WF of 4.6 eV, while Figure 3b, with low V<sub>turn-on</sub>, shows that there are more metal grains with a WF of 4.4 eV around the source region.

**Figure 3.** Metal grain distributions of planar TFETs in extreme cases (red color: metal grains with a work-function (WF) of 4.6 eV, and blue color: metal grains with a WF of 4.4 eV) among the simulated samples. (a) Maximum V<sub>turn-on</sub> (0.367 V) case of planar TFETs. (b) Minimum V<sub>turn-on</sub> (0.289 V) case of planar TFETs.

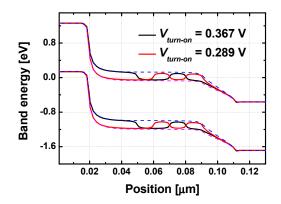

Figure 4 shows the energy band diagrams of these two extreme cases of planar TFETs when  $V_D$  is 0.5 V and  $V_G$  is 0.4 V. Due to the difference in the distribution of the metal grains analyzed above, the energy band bending between the source and the channel region becomes larger in the case of  $V_{turn-on} = 0.289$  V (red dash line) than in the case of  $V_{turn-on} = 0.367$  V (black solid line). As a result, when the same  $V_G$  is applied, there is a difference in the tunneling width of the two cases and accordingly, the  $V_{th}$  is also different. As described above, the planar TFET is relatively vulnerable to the WFV effect, as the  $V_{th}$  of the planar TFET is only determined by the energy band of the channel adjacent to the source region, while the  $V_{th}$  of the conventional MOSFET is determined by the entire

channel under the gate [33]. In the metal grain distributions shown in Figure 3a,b, planar TFETs have a  $\Delta V_{turn-on}$  of 78 mV (0.367 V–0.289 V) between the two cases. On the other hand, the DG TFET and EHBTFET show a  $\Delta V_{turn-on}$  of 65 mV (0.371–0.306 V) and 5 mV (0.685–0.679 V), respectively, when one of two gates has the same metal grain distribution, as shown in Figure 3a,b.

**Figure 4.** Energy band diagrams of planar TFETs with the highest value of  $V_{turn-on}$  at 0.367 V (black solid line) and the lowest value of  $V_{turn-on}$  at 0.289 V (red solid line) among the simulated samples when  $V_D$  is 0.5 V and  $V_G$  is 0.4 V. The blue dashed line and magenta dashed line show the most extreme cases in theory when the entire gate of the planar TFET is 4.6 and 4.4 eV, respectively.

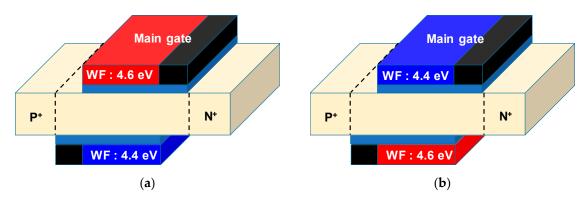

As confirmed in the analysis of Figures 3 and 4, only seven metal grains near the source junction mainly affect the tunneling current and the  $V_{turn-on}$  of the planar TFET. Meanwhile, in the case of DG TFETs, the addition of another gate on the opposite side doubles the number of metal grains (14 metal grains) that affect the tunneling current and reduces the effect of WFV. Unlike the planar TFET or DG TFET, in the on-state of the EHBTFET, electrons are collected under MG and holes are collected under SG. As the bias of MG increases, energy band bending and a tunneling current are generated in the channel between the two gates. The EHBTFET has a tunneling current at the channel between MG and SG, and all of the metal grains (70 metal grains) where MG and SG overlap are included in  $V_{turn-on}$  determination, which greatly reduces the effect of WFV.

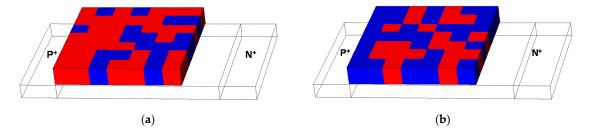

This analysis can be confirmed indirectly by comparing the probabilities of the most extreme theoretical cases of the planar TFET, DG TFET and EHBTFET. As discussed above, the V<sub>turn-on</sub> of the planar TFET and DG TFET is controlled by the metal grains near the source. Therefore, the planar TFET has the maximum value of V<sub>turn-on</sub> when all WFs of seven metal grains adjacent to the source are 4.6 eV and the minimum V<sub>turn-on</sub> when they are all 4.4 eV; the probabilities are 2.8% (0.6<sup>7</sup>) and 0.2% (0.4<sup>7</sup>), respectively. Similarly, for the DG TFET, the probability of the maximum V<sub>turn-on</sub> is  $7.8 \times 10^{-2}$ % (0.6<sup>14</sup>) and the probability of the minimum V<sub>turn-on</sub> is  $2.7 \times 10^{-4}$ % (0.4<sup>14</sup>). In the case of the EHBTFET, as tunneling occurs from the valence band of the channel near SG to the conduction band of the channel near MG, the V<sub>turn-on</sub> reaches the maximum when all MG grains have a WF of 4.6 eV and all SG grains have a WF of 4.4 eV where MG and SG overlap, as shown in Figure 5a; its probability is  $2.0 \times 10^{-20}$ % (0.6<sup>35</sup> × 0.4<sup>35</sup>). Additionally, in the opposite case, as shown in Figure 5b, the V<sub>turn-on</sub> reaches the minimum and its probability is equal to the probability of the maximum V<sub>turn-on</sub>. By comparing the probabilities of the most extreme cases in the three structures, it was confirmed that the EHBTFET has the smallest probabilities, and this difference is caused by the difference in the number of metal grains that affect the V<sub>turn-on</sub>.

**Figure 5.** Expected metal grain distributions of EHBTFETs in the most extreme theoretical cases (red color: metal grains with a WF of 4.6 eV, blue color: metal grains with a WF of 4.4 eV, and black color: metal grains that have less effect on the  $V_{turn-on}$  of EHBTFET). (a) Expected maximum  $V_{turn-on}$  case of EHBTFETs in theory. (b) Expected minimum  $V_{turn-on}$  case of EHBTFETs in theory.

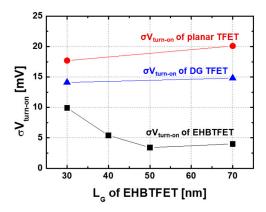

In order to prove that the WFV improvement of the EHBTFET is due to the large number of metal grains, the  $\sigma V_{turn-on}$  of the planar TFET, DG TFET, and EHBTFET was examined while reducing the L<sub>G</sub> of the EHBTFET, as shown in Figure 6. The WFV effects of the planar TFET and DG TFET were determined by the metal grains located at the edge between the source and the channel. Therefore, the  $\sigma V_{turn-on}$  of the planar TFET and DG TFET is not significantly affected by the change in the gate length. On the other hand, when the L<sub>G</sub> of the EHBTFET decreases, the number of metal grains in the overlapping areas of MG and SG decreases and the  $\sigma V_{turn-on}$  of the EHBTFET increases accordingly. By comparing when L<sub>G</sub> was 70 nm and when L<sub>G</sub> was 30 nm, it can be seen that the  $\sigma V_{turn-on}$  of the EHBTFET increased from 4.0 to 9.9 mV as the number of metal grains affecting the tunneling current decreased from 70 to 14, respectively. Therefore, if L<sub>G</sub> continues to decrease, the WFV effects of the EHBTFET are expected to be similar to those of other TFET structures. In addition, the electrical performance (e.g., I<sub>on</sub>) also degrades as the tunneling area (i.e., overlap area between main and sub gates) of the EHBTFET decreases with the smaller L<sub>G</sub>. Consequently, when the scaling down of TFETs continues, it is necessary to maintain the L<sub>G</sub> by using a vertical channel [38] to maintain the advantages of the EHBTFET in the WFV effects.

**Figure 6.** The  $\sigma V_{turn-on}$  of the planar TFET, DG TFET, and EHBTFET when the L<sub>G</sub> is changed. While reducing the L<sub>G</sub>, the L<sub>CH</sub> is reduced by the same length, and L<sub>UD</sub> and L<sub>US</sub> are kept at 20 nm.

#### 4. Conclusions

In this research, the WFV effects of the planar TFET, DG TFET, and EHBTFET were compared and analyzed by TCAD simulation. As a result of extracting the  $\sigma V_{turn-on}$  and examining the metal grain distributions, it was confirmed that the planar TFET has the greatest WFV effect because only a few metal grains around the source region affect the  $V_{turn-on}$ . On the other hand, the EHBTFET is the most immune from the WFV effect, as all of the metal grains where MG and SG overlap determine the V<sub>turn-on</sub>.

**Author Contributions:** Conceptualization, G.K. and S.K.; validation, J.H.K. and J.K.; investigation, G.K.; data curation, G.K.; writing—original draft preparation, G.K.; writing—review and editing, J.H.K., J.K. and S.K; visualization, G.K. All authors have read and agreed to the published version of the manuscript.

**Funding:** This research was supported in part by the MOTIE/KSRC under Grant 10080575 (Future Semiconductor Device Technology Development Program), and in part by the NRF of Korea funded by the MSIT under Grant NRF-2019M3F3A1A03079739, NRF-2019M3F3A1A02072091 (Intelligent Semiconductor Technology Development Program), NRF-2020R1G1A1007430 and NRF-2020M3F3A2A01081672, and in part by 2019 Research Fund of Myongji University. The EDA tool was supported by the IC Design Education Center (IDEC), Korea.

Conflicts of Interest: The authors declare no conflict of interest.

## References

- 1. Lundstrom, M. Device physics at the scaling limit: What matters?[MOSFETs]. In Proceedings of the International Electron Device Meeting (IEDM), Washington, DC, USA, 8–10 December 2003. [CrossRef]

- 2. Frank, D.J.; Dennard, R.H.; Nowak, E.; Solomon, P.M.; Taur, Y.; Wong, H.S.P. Device scaling limits of Si MOSFETs and their application dependencies. *Proc. IEEE* **2001**, *89*, 259–287. [CrossRef]

- Cheung, K.P. On the 60 mV/dec @ 300 K limit for MOSFET subthreshold swing. In Proceedings of the International Symposium on VLSI Technology, System and Application, Hsin Chu, Taiwan, 26–28 April 2010. [CrossRef]

- 4. Li, K.-S.; Chen, P.-G.; Lai, T.-Y.; Lin, C.-H.; Cheng, C.-C.; Chen, C.-C.; Wei, Y.-J.; Hou, Y.-F.; Liao, M.-H.; Lee, M.-H. Sub-60mV-swing negative-capacitance FinFET without hysteresis. In Proceedings of the International Electron Devices Meeting (IEDM), Washington, DC, USA, 7–9 December 2015. [CrossRef]

- 5. Lin, C.-I.; Khan, A.I.; Salahuddin, S.; Hu, C. Effects of the variation of ferroelectric properties on negative capacitance FET characteristics. *IEEE Trans. Electron Devices* **2016**, *63*, 2197–2199. [CrossRef]

- 6. McGuire, F.A.; Cheng, Z.; Price, K.; Franklin, A.D. Sub-60 mV/decade switching in 2D negative capacitance field-effect transistors with integrated ferroelectric polymer. *Appl. Phys. Lett.* **2016**, *109*, 93101. [CrossRef]

- Huang, Q.; Huang, R.; Pan, Y.; Tan, S.; Wang, Y. Resistive-Gate Field-Effect Transistor: A Novel Steep-Slope Device Based on a Metal—Insulator—Metal—Oxide Gate Stack. *IEEE Electron Device Lett.* 2014, 35, 877–879. [CrossRef]

- Kam, H.; Lee, D.T.; Howe, R.T.; King, T.-J. A new nano-electro-mechanical field effect transistor (NEMFET) design for low-power electronics. In Proceedings of the International Electron Devices Meeting (IEDM), Washington, DC, USA, 5–7 December 2005. [CrossRef]

- 9. Abelé, N.; Fritschi, R.; Boucart, K.; Casset, F.; Ancey, P.; Ionescu, A.M. Suspended-gate MOSFET: Bringing new MEMS functionality into solid-state MOS transistor. In Proceedings of the International Electron Devices Meeting (IEDM), Washington, DC, USA, 5–7 December 2005. [CrossRef]

- Padilla, A.; Yeung, C.W.; Shin, C.; Hu, C.; Liu, T.-J.K. Feedback FET: A novel transistor exhibiting steep switching behavior at low bias voltages. In Proceedings of the International Electron Devices Meeting (IEDM), San Francisco, CA, USA, 15–17 December 2008. [CrossRef]

- Hwang, S.; Kim, H.; Kwon, D.W.; Lee, J.-H.; Park, B.-G. Si<sub>1-x</sub>Ge<sub>x</sub> Positive Feedback Field-effect Transistor with Steep Subthreshold Swing for Low-voltage Operation. *J. Semicond. Technol. Sci.* 2017, 17, 216–222. [CrossRef]

- 12. Choi, W.Y.; Song, J.Y.; Lee, J.D.; Park, Y.J.; Park, B.-G. 100-nm n-/p-channel I-MOS using a novel self-aligned structure. *IEEE Electron Device Lett.* **2005**, *26*, 261–263. [CrossRef]

- 13. Ramaswamy, S.; Kumar, M.J. Junction-less impact ionization MOS: Proposal and investigation. *IEEE Trans. Electron Devices* **2014**, *61*, 4295–4298. [CrossRef]

- Huang, X.; Fang, R.; Yang, C.; Fu, K.; Fu, H.; Chen, H.; Yang, T.-H.; Zhou, J.; Montes, J.; Kozicki, M. Steep-slope field-effect transistors with AlGaN/GaN HEMT and oxide-based threshold switching device. *Nanotechnology* 2019, 30, 215201. [CrossRef]

- 15. Ionescu, A.M.; Riel, H. Tunnel field-effect transistors as energy-efficient electronic switches. *Nature* **2011**, 479, 329–337. [CrossRef]

- 16. Choi, W.Y.; Park, B.-G.; Lee, J.D.; Liu, T.-J.K. Tunneling field-effect transistors (TFETs) with subthreshold swing (SS) less than 60 mV/dec. *IEEE Electron Device Lett.* **2007**, *28*, 743–745. [CrossRef]

- 17. Kim, S.W.; Kim, J.H.; Liu, T.-J.K.; Choi, W.Y.; Park, B.-G. Demonstration of L-shaped tunnel field-effect transistors. *IEEE Trans. Electron Devices* **2016**, *63*, 1774–1778. [CrossRef]

- Lee, R.; Kwon, D.W.; Kim, S.; Kim, D.H.; Park, B.-G. Investigation of feasibility of tunneling field effect transistor (TFET) as highly sensitive and multi-sensing biosensors. *J. Semicond. Technol. Sci.* 2017, 17, 141–146. [CrossRef]

- Mayer, F.; Le Royer, C.; Damlencourt, J.F.; Romanjek, K.; Andrieu, F.; Tabone, F.C.; Previtali, B.; Deleonibus, S. Impact of SOI, Si<sub>1-x</sub>Ge<sub>x</sub>OI and GeOI substrates on CMOS compatible Tunnel FET performance. In Proceedings of the International Electron Device Meeting (IEDM), San Francisco, CA, USA, 15–17 December 2008. [CrossRef]

- Gandhi, R.; Chen, Z.; Singh, N.; Banerjee, K.; Lee, S. CMOS-compatible vertical-silicon-nanowire gate-all-around ptype tunneling FETs with ≤50-mV/decade subthreshold swing. *IEEE Electron Device Lett.* 2011, 32, 1504–1506. [CrossRef]

- 21. De Michielis, L.; Lattanzio, L.; Ionescu, A.M. Understanding the superlinear onset of tunnel-FET output characteristic. *IEEE Electron Device Lett.* **2012**, *33*, 1523–1525. [CrossRef]

- 22. Toh, E.-H.; Wang, G.H.; Samudra, G.; Yeo, Y.-C. Device physics and design of double-gate tunneling field-effect transistor by silicon film thickness optimization. *Appl. Phys. Lett.* **2007**, *90*, 263507. [CrossRef]

- Kim, S.H.; Kam, H.; Hu, C.; Liu, T.-J.K. Germanium-source tunnel field effect transistors with record high I ON/I OFF. In Proceedings of the International Conference on VLSI Technology, Kyoto, Japan, 15–18 June 2009.

- 24. Nayfeh, O.M.; Chleirigh, C.N.; Hennessy, J.; Gomez, L.; Hoyt, J.L.; Antoniadis, D.A. Design of tunneling field-effect transistors using strained-silicon/strained-germanium type-II staggered heterojunctions. *IEEE Electron Device Lett.* 2008, 29, 1074–1077. [CrossRef]

- 25. Han, G.; Guo, P.; Yang, Y.; Zhan, C.; Zhou, Q.; Yeo, Y.-C. Silicon-based tunneling field-effect transistor with elevated germanium source formed on (110) silicon substrate. *Appl. Phys. Lett.* **2011**, *98*, 153502. [CrossRef]

- Kim, M.; Wakabayashi, Y.; Nakane, R.; Yokoyama, M.; Takenaka, M.; Takagi, S. High I<sub>on</sub>/I<sub>off</sub> Ge-source ultrathin body strained-SOI tunnel FETs. In Proceedings of the International Electron Device Meeting (IEDM), San Francisco, CA, USA, 15–17 December 2014. [CrossRef]

- Takagi, S.; Kim, M.; Noguchi, M.; Ji, S.-M.; Nishi, K.; Takenaka, M. III-V and Ge/strained SOI tunnel FET technologies for low power LSIs. In Proceedings of the International Conference on VLSI Technology, Kyoto, Japan, 16–19 June 2015. [CrossRef]

- Krishnamohan, T.; Kim, D.; Raghunathan, S.; Saraswat, K. Double-gate strained-Ge heterostructure tunneling FET (TFET) with record high drive currents and <60mV/dec subthreshold slope. In Proceedings of the International Electron Device Meeting (IEDM), San Francisco, CA, USA, 15–17 December 2008. [CrossRef]

- 29. Kim, G.; Lee, J.; Kim, J.H.; Kim, S. High on-current Ge-channel heterojunction tunnel field-effect transistor using direct band-to-band tunneling. *Micromachines* **2019**, *10*, 77. [CrossRef]

- 30. Kim, J.H.; Kim, H.W.; Kim, G.; Kim, S.; Park, B.-G. Demonstration of Fin-Tunnel Field-Effect Transistor with Elevated Drain. *Micromachines* **2019**, *10*, 30. [CrossRef]

- 31. Kim, J.H.; Kim, H.W.; Shin, S.-S.; Kim, S.; Park, B.-G. Transient Analysis of Tunnel Field-Effect Transistor with Raised Drain. *J. Nanosci. Nanotechnol.* **2019**, *19*, 6212–6216. [CrossRef]

- Boucart, K.; Ionescu, A.M. Double-gate tunnel FET with high-κ gate dielectric. *IEEE Trans. Electron Devices* 2007, 54, 1725–1733. [CrossRef]

- 33. Choi, K.M.; Choi, W.Y. Work-function variation effects of tunneling field-effect transistors (TFETs). *IEEE Electron Device Lett.* **2013**, *34*, 942–944. [CrossRef]

- Lattanzio, L.; De Michielis, L.; Ionescu, A.M. The electron-hole bilayer tunnel FET. Solid State Electron. 2012, 74, 85–90. [CrossRef]

- 35. Lattanzio, L.; Dagtekin, N.; De Michielis, L.; Ionescu, A.M. On the static and dynamic behavior of the germanium electron-hole bilayer tunnel FET. *IEEE Trans. Electron Devices* **2012**, *59*, 2932–2938. [CrossRef]

- 36. Alper, C.; Palestri, P.; Padilla, J.L.; Ionescu, A.M. The electron-hole bilayer TFET: Dimensionality effects and optimization. *IEEE Trans. Electron Devices* **2016**, *63*, 2603–2609. [CrossRef]

- Padilla, J.L.; Alper, C.; Gamiz, F.; Ionescu, A.M. Switching behavior constraint in the heterogate electron–hole bilayer tunnel FET: The combined interplay between quantum confinement effects and asymmetric configurations. *IEEE Trans. Electron Devices* 2016, *63*, 2570–2576. [CrossRef]

- Kim, S.; Choi, W.Y.; Park, B.-G. Vertical-structured electron-hole bilayer tunnel field-effect transistor for extremely low-power operation with high scalability. *IEEE Trans. Electron Devices* 2018, 65, 2010–2015. [CrossRef]

- 39. Dadgour, H.; De, V.; Banerjee, K. Statistical modeling of metal-gate work-function variability in emerging device technologies and implications for circuit design. In Proceedings of the IEEE/ACM International Conference on Computer-Aided Design, San Jose, CA, USA, 10–13 November 2008. [CrossRef]

- 40. Lima, L.P.B.; Moreira, M.A.; Diniz, J.A.; Doi, I. Titanium nitride as promising gate electrode for MOS technology. *Phys. Status Solidi C* **2012**, *9*, 1427–1430. [CrossRef]

- 41. Bolotov, L.; Fukuda, K.; Tada, T.; Matsukawa, T.; Masahara, M. Spatial variation of the work function in nano-crystalline TiN films measured by dual-mode scanning tunneling microscopy. *Jpn. J. Appl. Phys.* **2015**, *54*, 04DA03. [CrossRef]

- 42. He, J.L.; Setsuhara, Y.; Shimizu, I.; Miyake, S. Structure refinement and hardness enhancement of titanium nitride films by addition of copper. *Surf. Coat. Technol.* **2001**, *137*, 38–42. [CrossRef]

- 43. Ohmori, K.; Matsuki, T.; Ishikawa, D.; Morooka, T.; Aminaka, T.; Sugita, Y.; Chikyow, T.; Shiraishi, K.; Nara, Y.; Yamada, K. Impact of additional factors in threshold voltage variability of metal/high-k gate stacks and its reduction by controlling crystalline structure and grain size in the metal gates. In Proceedings of the International Electron Devices Meeting (IEDM), San Francisco, CA, USA, 15–17 December 2008. [CrossRef]

- 44. Ruiz, A.; Seoane, N.; Claramunt, S.; García-Loureiro, A.; Porti, M.; Couso, C.; Martin-Martinez, J.; Nafria, M. Workfunction fluctuations in polycrystalline TiN observed with KPFM and their impact on MOSFETs variability. *Appl. Phys. Lett.* **2019**, *114*, 093502. [CrossRef]

- 45. Synopsys, Inc. *Sentaurus Device User Guide*; Synopsys Inc.: Mountain View, CA, USA, 2015. Available online: http://www.sentaurus.dsod.pl/manuals/data/sdevice\_ug.pdf (accessed on 30 April 2020).

- Kao, K.-H.; Verhulst, A.S.; Vandenberghe, W.G.; Soree, B.; Groeseneken, G.; De Meyer, K. Direct and indirect band-to-band tunneling in germanium-based TFETs. *IEEE Trans. Electron Devices* 2011, 59, 292–301. [CrossRef]

- 47. Llorente, C.D.; Colinge, J.-P.; Martinie, S.; Cristoloveanu, S.; Wan, J.; Le Royer, C.; Ghibaudo, G.; Vinet, M. New prospects on high on-current and steep subthreshold slope for innovative Tunnel FET architectures. *Solid State Electron.* **2019**, *159*, 26–37. [CrossRef]

- 48. Li, W.; Liu, H.; Wang, S.; Chen, S.; Han, T.; Yang, K. Design and investigation of dopingless dual-gate tunneling transistor based on line tunneling. *AIP Adv.* **2019**, *9*, 045109. [CrossRef]

- 49. Lee, J.W.; Choi, W.Y. Design Guidelines for Gate-Normal Hetero-Gate-Dielectric (GHG) Tunnel Field-Effect Transistors (TFETs). *IEEE Access* 2020, *8*, 67617–67624. [CrossRef]

- 50. Boucart, K.; Ionescu, A.M. A new definition of threshold voltage in tunnel FETs. *Solid State Electron*. **2008**, *52*, 1318–1323. [CrossRef]

- 51. Ortiz-Conde, A.; García-Sánchez, F.J.; Muci, J.; Sucre-González, A.; Martino, J.A.; Der Agopian, P.G.; Claeys, C. Threshold voltage extraction in Tunnel FETs. *Solid State Electron.* **2014**, *93*, 49–55. [CrossRef]

- 52. Dadgour, H.F.; Endo, K.; De, V.K.; Banerjee, K. Grain-orientation induced work function variation in nanoscale metal-gate transistors—Part I: Modeling, analysis, and experimental validation. *IEEE Trans. Electron Devices* **2010**, *57*, 2504–2514. [CrossRef]

- 53. Nam, H.; Shin, C. Study of high-k/metal-gate work-function variation using Rayleigh distribution. *IEEE Electron Device Lett.* **2013**, *34*, 532–534. [CrossRef]

- 54. Nam, H.; Lee, Y.; Park, J.-D.; Shin, C. Study of Work-Function Variation in High-κ/Metal-Gate Gate-All-Around Nanowire MOSFET. *IEEE Trans. Electron Devices* **2016**, *63*, 3338–3341. [CrossRef]

- 55. Dadgour, H.F.; Endo, K.; De, V.K.; Banerjee, K. Grain-orientation induced work function variation in nanoscale metal-gate transistors—Part II: Implications for process, device, and circuit design. *IEEE Trans. Electron Devices* **2010**, *57*, 2515–2525. [CrossRef]

© 2020 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).