MDPI

Article

# Analysis and Hardening of SEGR in Trench VDMOS with Termination Structure

Yuan Wang <sup>1</sup>, Tao Liu <sup>1</sup>, Lingli Qian <sup>1</sup>, Hao Wu <sup>1,2</sup>, Yiren Yu <sup>1</sup>, Jingyu Tao <sup>1</sup>, Zijun Cheng <sup>1</sup> and Shengdong Hu <sup>1,\*</sup>

- School of Microelectronics and Communication Engineering, Chongqing University, Chongqing 400044, China

- <sup>2</sup> Science and Technology on Analog Integrated Circuit Laboratory, Chongqing 401332, China

- \* Correspondence: hushengdong@hotmail.com

Abstract: Single-event gate-rupture (SEGR) in the trench vertical double-diffused power MOSFET (VDMOS) occurs at a critical bias voltage during heavy-ion experiments. Fault analysis demonstrates that the hot spot is located at the termination of the VDMOS, and the gate oxide in the termination region has been damaged. The SEGR-hardened termination with multiple implantation regions is proposed and simulated using the Sentaurus TCAD. The multiple implantation regions are introduced, leading to an increase in the distance between the gate oxide and the hole accumulation region, as well as a decrease in the resistivity of the hole conductive path. This approach is effective in reducing the electric field of the gate oxide to below the calculated critical field, and results in a lower electric field than the conventional termination.

Keywords: single-event gate-rupture (SEGR); heavy ion; trench VDMOS; radiation hardness

### 1. Introduction

Trench vertical double-diffused power MOSFETs (VDMOS) are widely used in power management systems as ideal power switches for space radiation environments [1–3]. These devices will be exposed to energetic neutrons, protons, and heavy ions when used in space. Heavy ions can trigger single-event gate-rupture (SEGR) in devices, causing gate oxide damage and even device burnout. Under the heavy-ion strikes, a large number of electron–hole pairs are generated along the track, and the gate oxide will break down to produce a conductive path, leading to a serious failure.

SEGR was first reported by Fischer [4], and since then, many studies have been carried out on the mechanism of SEGR. Darwish et al. [5] proposed that the surface electric field is sufficiently high to cause SEGR and that increasing the thickness of the gate oxide is an effective method to avoid SEGR. Nichols et al. [6] proved that SEGR is sensitive to the temperature and the incident angle. Titus et al. [7-11] studied the impact of particle energy, the position of particle Bragg peak, and the particle type on SEGR using experimental and simulation methods. Lauenstein et al. [12] reported the effects of charge generated by heavy ions in the gate oxide layer, the drift layer, and the substrate layer on SEGR. Titus et al. [13] reviewed the mechanism of single-event burnout (SEB) and SEGR. Privat et al. [14] investigated the impact of the latent defects on SEGR during switching operations. Recently, more studies have focused on the SEGR hardening technologies, such as the thicker gate oxide at the trench bottom proposed by Ttius et al. [3] and Darwish et al. [15], the W-shaped gate dielectric proposed by [16], the high-k gate dielectric proposed by X. Wan et al. [17] and A. Javanainen et al. [18], the widened split gate proposed by Jiang Lu et al. [19], the super-junction power MOS proposed by Muthuseenu et al. [20], and so on. As we all know, the termination is an essential part for all VDMOS devices; however, many hardening guidelines focus on the cell region of the VDMOS. The hardening technology for the termination is of great importance.

Citation: Wang, Y.; Liu, T.; Qian, L.; Wu, H.; Yu, Y.; Tao, J.; Cheng, Z.; Hu, S. Analysis and Hardening of SEGR in Trench VDMOS with Termination Structure. *Micromachines* **2023**, *14*, 688. https://doi.org/10.3390/mi14030688

Academic Editor: Sadia Ameen

Received: 27 February 2023 Revised: 12 March 2023 Accepted: 13 March 2023 Published: 20 March 2023

Copyright: © 2023 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Micromachines 2023, 14, 688 2 of 10

In this paper, heavy-ion tests were performed on trench VDMOS with a  $V_{\rm BR}$  of 60 V. It was found that SEGR occurred in the termination and the gate oxide was damaged. The failure mechanism was analyzed using Sentaurus TCAD. The termination is more prone to SEGR than the cell, and thus, the SEGR-hardened termination with multiple implantation regions was proposed. It was shown to be an effective method to suppress SEGR and improve radiation reliability.

## 2. Device and Experiments

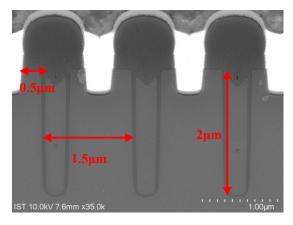

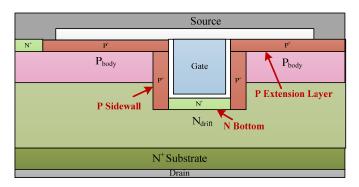

The cross-sectional SEM schematic photograph of the 60 V n-channel trench VDMOS is shown in Figure 1. The devices were manufactured using 0.35  $\mu m$  process. The trench structure is formed by Si trench etching, oxide growth, and poly-silicon deposition. Specifically, the gate oxide is grown after the ion doping and drive-in process to improve its quality. Table 1 lists the main parameters of the device. Because of the trench structure, the trench VDMOS exhibits a smaller cell pitch of 1.5  $\mu m$  and a higher drift doping concentration of  $3\times10^{16}$  cm $^{-3}$ . Therefore, the devices achieve a static on-state resistance of 15 m $\Omega$  and a continuous drain current of 35 A.

Figure 1. Device structure: cross-sectional SEM photograph.

| <b>Table 1.</b> The main parame | eters of the device. |

|---------------------------------|----------------------|

|---------------------------------|----------------------|

| Parameter                                               | Value                |

|---------------------------------------------------------|----------------------|

| Cell pitch, $W_{\text{cell}}$ (µm)                      | 1.5                  |

| Thickness of drift layer, $L_d$ ( $\mu$ m)              | 8                    |

| Thickness of gate oxide, $t_{ox}$ (µm)                  | 0.06                 |

| Concentration of drift layer, $N_d$ (cm <sup>-3</sup> ) | $3 \times 10^{16}$   |

| Concentration of P-body, $N_p$ (cm <sup>-3</sup> )      | $1.9 \times 10^{17}$ |

| Concentration of P+ and N+ $(cm^{-3})$                  | $1 \times 10^{19}$   |

The trench VDMOS devices were irradiated using a  $^{181}$ Ta ions with a linear energy transfer (LET) of  $80.28\,\mathrm{MeV\cdot mg^{-1}\cdot cm^{-2}}$ , which were normal to the surface of the device with a beam flux of  $1\times10^4\,\mathrm{ions/cm^2/s}$ . When the total ion beam of  $1\times10^7\,\mathrm{ions/cm^2}$  was achieved, the beam was shuttered immediately following the detection of the gate and drain leakage currents. However, when the device failed, the experiment would be terminated in advance.

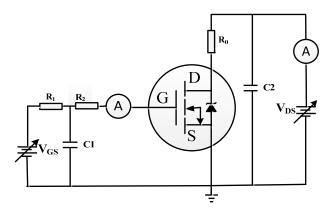

Figure 2 presents the basic test circuit for SEB and SEGR referring to the method 1080.1 in the MIL-STD-750-1 [21]. The gate resistor–capacitor network provides a low-pass filter to protect the gate oxide from switching transients. The drain resistor helps limit the current and voltage to prevent device failure from SEB. During the heavy-ion experiment, the drain–source voltage ( $V_{\rm DS}$ ) was biased at 24 V or 48 V, the gate–source voltage ( $V_{\rm GS}$ ) was biased at 0 V. The gate leakage current and the drain current were measured in real time.

Micromachines 2023, 14, 688 3 of 10

Figure 2. The basic test circuit for SEB and SEGR.

### 3. Experimental Results and Analysis

Figures 3a and 3b show the gate leakage current and the drain current curve at  $V_{\rm DS}$  = 24 V,  $V_{\rm GS}$  = 0 V and  $V_{\rm DS}$  = 48 V,  $V_{\rm GS}$  = 0 V, respectively. As is shown in Figure 3a, the gate leakage current and the drain current had little change. This indicates that the device would not exhibit SEB or SEGR at the  $V_{\rm DS}$  = 24 V and  $V_{\rm GS}$  = 0 V. However, in Figure 3b, the gate leakage current increased from below 1 nA to 1  $\mu$ A and exceeded the upper limit value, while the drain current varied within 1  $\mu$ A. It is obviously seen that the SEGR event had occurred. After the heavy-ion experiment, the device was measured again using the AgilentB1505A and the test results show that the gate oxide of the device had suffered damage.

**Figure 3.** The single event test data of the trench VDMOS: (a)  $V_{DS}$  = 24 V,  $V_{GS}$  = 0 V; (b)  $V_{DS}$  = 48 V,  $V_{GS}$  = 0 V.

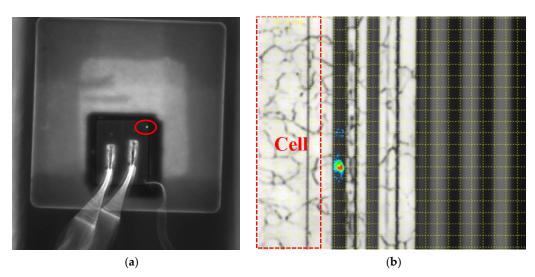

In order to locate the failure point of the post-irradiated trench VDMOS more accurately, an emission microscopy (EMMI) with a wavelength range from 350 nm to 1100 nm

Micromachines 2023, 14, 688 4 of 10

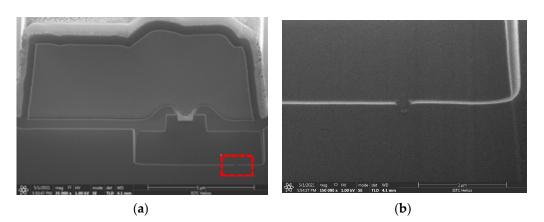

was used to detect hot spots, as shown in Figure 4. In Figure 4a, one hot spot was detected, and it can be seen clearly under a microscope. The enlarged image of the hot spot was shown in Figure 4b. By comparing it with the trench device layout, it is obviously seen that the hot pot appeared in the termination region. The red dash frame in Figure 4b represents the cell region of the device. In addition, the location of the hot spot was cut by the focused ion beam (FIB), and then the FIB-cut cross section was scanned by the scanning electron microscope (SEM), as shown in Figure 5a, the red dash frame of which was magnified as shown in Figure 5b. From Figure 5b, it is obvious that the gate oxide in the termination region had been damaged. It can be further proven that the SEGR occurred. The failure of the post-irradiated trench was caused by the SEGR in the termination region.

**Figure 4.** One hot spot detected by the EMMI (a) and the enlarged image under a microscope (b). The red dash frame in (b) represents the cell regions of the device.

**Figure 5.** The FIB cut cross section of the hot spot by SEM (a) and the enlarged image of the red dash frame in (a) by SEM (b).

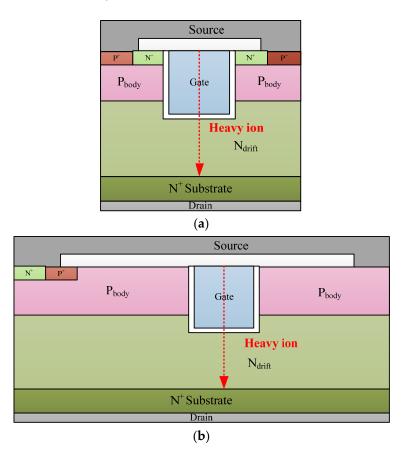

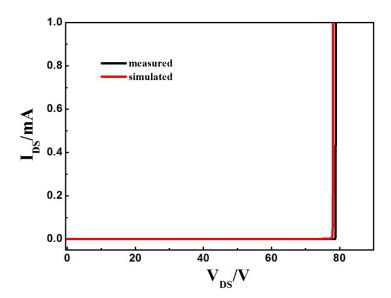

To analyze the SEGR of the trench VDMOS clearly, Sentaurus TCAD simulations were performed on the trench VDMOS. The cross section of the cell and termination are shown in Figure 6a,b. The termination structure is the gate bus region used to transfer the gate signal in the cell region. The mobility model, Shockley–Read–Hall (SRH) recombination, Auger, and avalanche model were adopted in the simulation. The simulation models have been calibrated with the measured results. Figure 7 shows the simulated breakdown characteristic of the cell, which fits well with the experimental results. To mimic heavy-ion strikes, the HeavyIon model was used in simulations. The heavy ions with an LET of  $80 \text{ MeV} \cdot \text{mg}^{-1} \cdot \text{cm}^{-2}$  were normally incident to the middle of the trench gate in the cell and termination structure. The Gaussian distribution was used in the HeavyIon model,

Micromachines 2023, 14, 688 5 of 10

with the radius and the length of heavy ions defined as  $0.5~\mu m$  and  $8~\mu m$ , respectively. The length of heavy ions was long enough to penetrate the whole drift region. The incident time of the heavy ion is 0.1~n s.

**Figure 6.** The cross section of the cell (a) and the termination (gate bus) (b). The red dotted arrows show the incident position and direction in simulation.

Figure 7. Experimental and simulated breakdown characteristics for the trench VDMOS.

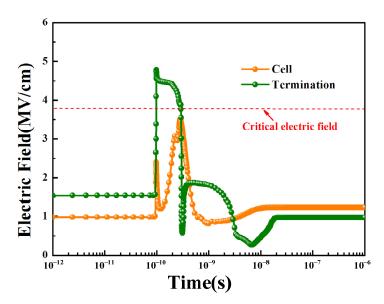

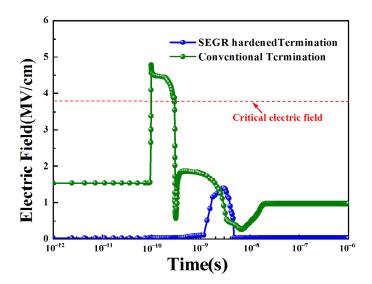

According to reference [22], the calculated critical breakdown electric field for the gate oxide is  $3.76 \times 10^6$  V/cm under  $^{181}$ Ta ions for triggering the SEGR. Figure 8 shows the simulated electric field of gate oxide at the position of the maximum electric field in the

Micromachines 2023, 14, 688 6 of 10

cell and the termination at  $V_{\rm DS}$  = 40 V,  $V_{\rm GS}$  = 0 V. As shown in Figure 3, the highest electric field in the termination was much larger than that of the cell. Meanwhile, the highest electric field in the cell has not reached the critical electric breakdown field, but that in the termination has far exceeded it.

**Figure 8.** Simulated electric field of gate oxide at the position of the maximum electric field in the cell and the termination under heavy-ion strikes.

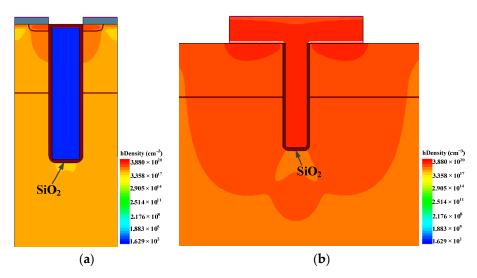

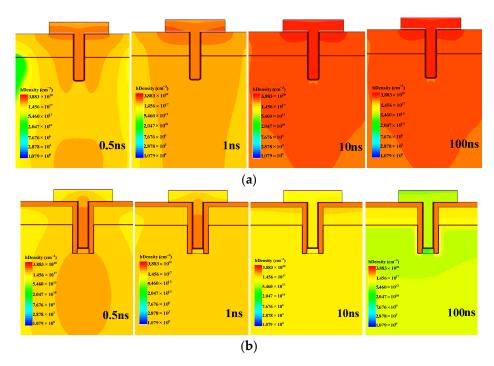

During the heavy-ions strike, a large number of electron–hole pairs are generated. The electrons are swept down to the drain substrate, while the holes move to the gate when the  $V_{\rm GS}$  is zero or negative and the  $V_{\rm DS}$  is positive. More accumulated holes at the bottom of the gate oxide lead to a higher electric field of the gate oxide. However, the moving path of the holes in the termination is much longer than that in the cell, therefore the holes in the termination are difficult to release, which results in a higher electric field of the gate oxide. Figure 9 shows the hole density distribution near the gate oxide in the cell and the termination at 100 ns. It proves that the hole density in the termination is much higher than that in the cell.

Figure 9. Hole density distribution near gate oxide in (a) the cell and (b) the termination at 100 ns.

### 4. Hardening Design and Discussion

Figure 10 shows the cross section of the SEGR-hardened termination with multiple implantation regions of the bottom N-well region (BNW), the p-type sidewall region (SW),

Micromachines 2023, 14, 688 7 of 10

and the p-type extension layer (EL). The doping concentrations of BNW, SW, and EL are  $5 \times 10^{16} \, \mathrm{cm^{-3}}$ ,  $1 \times 10^{18} \, \mathrm{cm^{-3}}$ , and  $1 \times 10^{19} \, \mathrm{cm^{-3}}$ , respectively. BNW increases the distance between the gate oxide and the hole accumulation region, which diminishes the induced electric field. Owing to the higher doping concentration of SW and EL, the resistivity of the holes' conductive path can be obviously decreased to accelerate the holes' release. Therefore, the accumulated holes induced by the heavy-ion strikes can be easily discharged, and the electric field of the gate oxide is decreased.

Figure 10. The cross section of the SEGR-hardened termination.

The simulated electric field of the gate oxide at the position of the maximum electric field in the conventional termination and the SEGR-hardened termination at  $V_{\rm DS} = 40~\rm V$ ,  $V_{\rm GS} = 0~\rm V$  is shown in Figure 11. It can be seen that the maximum electric field has reduced from 4.78 MV/cm in the conventional termination to 1.39 MV/cm in the SEGR-hardened termination. This means that the SEGR technique is highly effective in restraining the increase in the electric field in the gate oxide.

**Figure 11.** Simulated electric field of gate oxide at the position of the maximum electric field in the conventional termination and the SEGR-hardened termination with time under heavy-ion strikes.

Figure 12 shows the distribution of hole density over time of the conventional termination and the SEGR-hardened termination. It is clear that as the multiple implantation regions are introduced, the accumulated holes near gate oxide are fewer in the SEGR-hardened termination, leading to a lower electric field than the conventional termination and further ensuring the radiation reliability of the device.

Micromachines 2023, 14, 688 8 of 10

**Figure 12.** Hole density distribution near gate oxide for the conventional termination and the SEGR-hardened termination: (a) conventional termination; (b) SEGR-hardened termination.

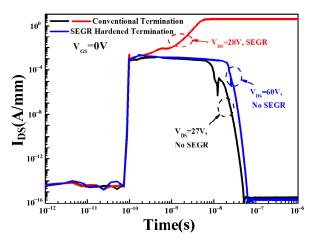

To further demonstrate the improvement of SEGR hardening, the SEGR-triggering criteria for the conventional termination and the SEGR-hardened termination are investigated in detail. As shown in Figure 13, it is clear seen that when  $V_{\rm GS}$  is set as 0 V, the conventional termination does not trigger SEGR when  $V_{\rm DS}$  is 27 V and below, and when  $V_{\rm DS}$  is 28 V, SEGR occurs. Thus, the SEGR-triggering voltage (V<sub>SEGR</sub>) of the conventional termination is 28 V. The SEGR-hardened termination does not trigger SEGR when  $V_{\rm DS}$  is 60 V and below, which can be considered to be a safe operating area (SOA); we believe that the device will not exhibit SEGR at  $V_{\rm GS}$  = 0 V for 60 V trench VDMOS. Compared with the conventional termination, the SEGR-triggering critical voltage for the SEGR-hardened termination is improved by 114%.

**Figure 13.** Comparison of  $I_{DS}$  when  $V_{DS}$  is 27 V and 28 V of the conventional termination and when  $V_{DS}$  is 60 V of the SEGR-hardened termination.

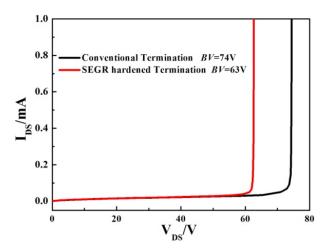

The termination structure could affect the breakdown voltage of the trench VDMOS; therefore, the breakdown characteristics for the conventional termination and the SEGR-hardened termination are investigated, as is shown in Figure 14. With the introduction of multiple implantation regions for hardening, the BV is slightly decreased from 74 V to 63 V.

Micromachines 2023, 14, 688 9 of 10

However, compared to the low triggering voltage and failure consequences of SEGR, these small impacts of the hardening method are still acceptable.

**Figure 14.** Simulated breakdown characteristic curves for the conventional termination and the SEGR-hardened termination.

#### 5. Conclusions

In conclusion, single-event gate-rupture in trench VDMOS occurs under heavy-ions strike. With fault analysis demonstrating that the gate oxide in the termination has been damaged. The SEGR-hardened termination with multiple implantation regions of BNW, SW, and EL is proposed and simulated using Sentaurus TCAD. The multiple implantation regions result in a lower electric field in the gate oxide. Compared with the conventional termination, the SEGR-hardened termination has better radiation performance with the LET of  $80.28~{\rm MeV\cdot mg^{-1}\cdot cm^{-2}}$ .

**Author Contributions:** Conceptualization and Writing—Original draft, Y.W.; Software and Data curation, L.Q.; Software, T.L., H.W., Y.Y., J.T. and Z.C.; Supervision and Writing—Reviewing and Editing, S.H. All authors have read and agreed to the published version of the manuscript.

**Funding:** This work is in part by the National Natural Science Foundation of China under Grant 62174017, in part by the National Laboratory of Science and Technology on Analog Integrated Circuit under Grant 2021-JCJQ-LB-049-4, and in part by the Natural Science Foundation Project of CQ CSTC under Grant cstc2020jcyjmsxmX0243.

Data Availability Statement: Data are available on request due to restrictions, e.g., privacy or ethical.

Conflicts of Interest: The authors declare no conflict of interest.

## References

- 1. Williams, R.K.; Darwish, M.N.; Blanchard, R.A.; Siemieniec, R.; Rutter, P.; Kawaguchi, Y. The trench power MOSFET: Part I—History, technology, and prospects. *IEEE Trans. Electron Devices* **2017**, *64*, 674–691. [CrossRef]

- 2. Ma, L.; Amali, A.; Kiyawat, S.; Mirchandani, A.; He, D.; Thapar, N.; Sodhi, R.; Spring, K.; Kinzer, D. New trench MOSFET technology for DC-DC converter applications. In Proceedings of the ISPSD '03, 2003 IEEE 15th International Symposium on Power Semiconductor Devices and ICs, Cambridge, UK, 14–17 April 2003; pp. 354–357. [CrossRef]

- 3. Titus, J.; Jamiolkowski, L.; Wheatley, C. Development of cosmic ray hardened power MOSFET's. *IEEE Trans. Nucl. Sci.* **1989**, 36, 2375–2382. [CrossRef]

- 4. Fischer, T.A. Heavy-Ion-Induced, Gate-Rupture in Power MOSFETs. IEEE Trans. Nucl. Sci. 1987, 34, 1786–1791. [CrossRef]

- 5. Darwish, M.; Shibib, M.; Pinto, M.; Titus, J. Single event gate rupture of power DMOS transistors. In Proceedings of the IEEE International Electron Devices Meeting, Washington, DC, USA, 5–8 December 1993; pp. 671–674. [CrossRef]

- 6. Nichols, D.K.; Coss, J.R.; Mccarty, K.P. Single event gate rupture in commercial power MOSFETs. In Proceedings of the RADECS 93, Second European Conference on Radiation and its Effects on Components and Systems (Cat. No.93TH0616-3), Saint Malo, France, 13–16 September 1993; pp. 462–467. [CrossRef]

- 7. Titus, J.; Wheatley, C.; Allenspach, M.; Schrimpf, R.; Burton, D.; Brews, J.; Galloway, K.; Pease, R. Influence of ion beam energy on SEGR failure thresholds of vertical power MOSFETs. *IEEE Trans. Nucl. Sci.* **1996**, *43*, 2938–2943. [CrossRef]

Micromachines 2023, 14, 688 10 of 10

8. Wheatley, T.; Wheatley, C.; Titus, J. Early lethal SEGR failures of VDMOSFETs considering nonuniformity in the rad-hard device distribution. *IEEE Trans. Nucl. Sci.* **2001**, *48*, 2217–2221. [CrossRef]

- 9. Titus, J.; Wheatley, C.; Gillberg, J.; Burton, D. A study of ion energy and its effects upon an SEGR-hardened stripe-cell MOSFET technology [space-based systems]. *IEEE Trans. Nucl. Sci.* **2001**, *48*, 1879–1884. [CrossRef]

- Liu, S.; Boden, M.; Cao, H.; Sanchez, E.; Titus, J.L. Evaluation of Worst-Case Test Conditions for SEE on Power DMOSFETs. In Proceedings of the 2006 IEEE Radiation Effects Data Workshop, Ponte Vedra Beach, FL, USA, 17–21 July 2006; pp. 165–171.

[CrossRef]

- 11. Liu, S.; Titus, J.L.; Zafrani, M.; Cao, H.; Carrier, D.; Sherman, P. Worst-Case Test Conditions of SEGR for Power DMOSFETs. *IEEE Trans. Nucl. Sci.* **2010**, *57*, 279–287. [CrossRef]

- 12. Lauenstein, J.-M.; Goldsman, N.; Liu, S.; Titus, J.L.; Ladbury, R.L.; Kim, H.S.; Phan, A.M.; LaBel, K.A.; Zafrani, M.; Sherman, P. Effects of Ion Atomic Number on Single-Event Gate Rupture (SEGR) Susceptibility of Power MOSFETs. *IEEE Trans. Nucl. Sci.* **2011**, *58*, 2628–2636. [CrossRef]

- 13. Titus, J.L. An Updated Perspective of Single Event Gate Rupture and Single Event Burnout in Power MOSFETs. *IEEE Trans. Nucl. Sci.* **2013**, *60*, 1912–1928. [CrossRef]

- 14. Privat, A.; Touboul, A.D.; Petit, M.; Huselstein, J.J.; Wrobel, F.; Forest, F.; Vaille, J.R.; Bourdarie, S.; Arinero, R.; Chatry, N.; et al. Impact of Single Event Gate Rupture and Latent Defects on Power MOSFETs Switching Operation. *IEEE Trans. Nucl. Sci.* **2014**, *61*, 1856–1864. [CrossRef]

- 15. Hohl, J.; Johnnson, G. Features of the triggering mechanism for single event burnout of power MOSFETs. *IEEE Trans. Nucl. Sci.* **1989**, 36, 2260–2266. [CrossRef]

- 16. Darwish, M.; Yue, C.; Lui, K.H.; Giles, F.; Chan, B.; Chen, K.-I.; Pattanayak, D.; Chen, Q.; Terrill, K.; Owyang, K. A new power W-gated trench MOSFET (WMOSFET) with high switching performance. In Proceedings of the ISPSD '03, 2003 IEEE 15th International Symposium on Power Semiconductor Devices and ICs, Cambridge, UK, 14–17 April 2003. [CrossRef]

- 17. Wan, X.; Zhou, W.S.; Ren, S.; Liu, D.G.; Xu, J.; Bo, H.L.; Zhang, E.X.; Schrimpf, R.D.; Fleetwood, D.M.; Ma, T.P. SEB Hardened Power MOSFETs with High-K Dielectrics. *IEEE Trans. Nucl. Sci.* 2015, 62, 2830–2836. [CrossRef]

- 18. Javanainen, A.; Ferlet-Cavrois, V.; Bosser, A.; Jaatinen, J.; Kettunen, H.; Muschitiello, M.; Pintacuda, F.; Rossi, M.; Schwank, J.R.; Shaneyfelt, M.R.; et al. SEGR in SiO<sub>2</sub>–Si<sub>3</sub>N<sub>4</sub> Stacks. *IEEE Trans. Nucl. Sci.* **2014**, *61*, 1902–1908. [CrossRef]

- 19. Lu, J.; Liu, H.; Luo, J.; Wang, L.; Li, B.; Li, B.; Zhang, G.; Han, Z. Improved single-event hardness of trench power MOSFET with a widened split gate. In Proceedings of the 2016 16th European Conference on Radiation and Its Effects on Components and Systems (RADECS), Bremen, Germany, 19–23 September 2016; pp. 1–5. [CrossRef]

- 20. Muthuseenu, K.; Barnaby, H.J.; Galloway, K.F.; Koziukov, A.E.; Maksimenko, T.A.; Vyrostkov, M.Y.; Bu-Khasan, K.B.; Kalashnikova, A.A.; Privat, A. Analysis of SEGR in Silicon Planar Gate Super-Junction Power MOSFETs. *IEEE Trans. Nucl. Sci.* **2021**, *68*, 611–616. [CrossRef]

- 21. MIL-STD-750-1 "Environmental Test Methosd for Semiconductor Devices Part 1: Test Methods 1000 through 1999". Available online: http://www.assistdocs.com (accessed on 21 August 2012).

- 22. Chen, Z.; Zhang, C.; Wu, M.; Wang, T.; Zeng, Y.; Wan, X.; Jin, H.; Xu, J.; Tang, M. Analysis and Mitigation of Single-Event Gate Rupture in VDMOS With Termination Structure. *IEEE Trans. Nucl. Sci.* **2021**, *68*, 1272–1278. [CrossRef]

**Disclaimer/Publisher's Note:** The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content.