MDPI

Article

# The Design of a Novel 2-42 GHz MEMS True-Time Delay Network for Wideband Phased Array Systems

Qiannan Wu <sup>1,2,3,4,\*</sup>, Zemin Shi <sup>2,3,4,5</sup>, Xudong Gao <sup>2,3,4,5</sup>, Jing Li <sup>2,3,4,5</sup>, Yongxin Zhan <sup>2,3,4,5</sup>, Guangzhou Zhu <sup>2,3,4</sup>, Junqiang Wang <sup>2,3,4,5,6</sup> and Mengwei Li <sup>2,3,4,5,6,\*</sup>

- School of Semiconductors and Physics, North University of China, Taiyuan 030051, China

- Academy for Advanced Interdisciplinary Research, North University of China, Taiyuan 030051, China

- Center for Microsystem Intergration, North University of China, Taiyuan 030051, China

- School of Instrument and Intelligent Future Technology, North University of China, Taiyuan 030051, China

- <sup>5</sup> School of Instrument and Electronics, North University of China, Taiyuan 030051, China

- <sup>6</sup> Key Laboratory of Dynamic Measurement Technology, North University of China, Taiyuan 030051, China

- Correspondence: qiannanwoo@nuc.edu.cn (Q.W.); lmwprew@163.com (M.L.)

**Abstract:** This article presents the design method of a compact MEMS switched-line true-time delay line (TTDL) network over a wide frequency range extending from 2 to 42 GHz using TTDL units. The TTDL units, namely the cascading radio frequency micro-electromechanical system (RF MEMS) switches and GCPW, were employed in the proposed TTDL network to improve the delay-bandwidth product (DBW) while maintaining its compact size and low delay variation (DV). For comparison, a theoretical analysis of the RF MEMS switch was performed while observing the switch performance with various top electrodes. The MEMS TTDL network has a compact size of 5 mm  $\times$  5 mm, with a maximum delay of 200 ps and a minimum of 30 ps. The maximum insertion loss of 9 states is 10 dB, and the in/out return loss is better than 20 dB across 2-42 GHz. The group delay variations are within  $\pm$ 2.5% for all the delay states over the operating frequency range. To the best of our knowledge, the proposed TTDL network obtains the most control bits among the TTDL networks offered to date.

**Keywords:** true-time delay lines (TTDL); delay-bandwidth product (DBW); radio frequency micro-electromechanical system (RF MEMS) switch; delay variation (DV); phased arrays

Citation: Wu, Q.; Shi, Z.; Gao, X.; Li, J.; Zhan, Y.; Zhu, G.; Wang, J.; Li, M. The Design of a Novel 2-42 GHz MEMS True-Time Delay Network for Wideband Phased Array Systems. *Micromachines* 2023, 14, 246. https://doi.org/10.3390/mi14020246

Academic Editors: Yao-Chuan Tsai and Ching-Liang Dai

Received: 28 November 2022 Revised: 10 December 2022 Accepted: 12 December 2022 Published: 18 January 2023

Copyright: © 2023 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

#### 1. Introduction

In recent years, the development of true-time delay lines (TTDL) has been promoted primarily by their usefulness in replacing the traditional phase shifter in phased array systems. To improve the frequency response of the broadband phased array antenna and obtain better beam pointing characteristics, it is necessary to connect variable true-time delay lines (V-TTDL) in the antenna RF link to compensate for the effect of the antenna scanning aperture [1]. A variable true-time delay line with a fixed reference period stepping in the subarray level instead of the cell level is a standard scheme used to insert a real-time delay device in engineering [2]. At present, the main types of traditional time delay lines are SAW delay lines [3], optical fiber delay lines [4], and transmission line delay lines [5]. These devices are usually monolithic, aiming at reducing the die area of the integrated circuit, with switch powers ranging from roughly milliwatts to several watts [6].

There are many different designs for transmission-line delay lines. Some of the more prominent designs are the distributed micro-electromechanical system transmission lines (DMTLs), the reflection-type true-time delay lines, and switch-linearity true-time delay lines (TTDL). Distributed micro-electromechanical system transmission lines are well-established design methods that maintain good performance at relatively high frequencies but are generally more extensive because they contain a large number of MEMS structures. In a specific range, the higher the number of bits of the real delay Lines (TTDL), the smaller the drift of the scanning beam will be [7]. However, the published literature and the TTDL

Micromachines 2023, 14, 246 2 of 9

network products that have emerged generally have problems such as fewer control bits, a narrow working frequency band, and a small group delay amount. For the first time, M. Kim and J.B. Hacker of Rockwell sciences have successfully manufactured two four-bit TTD networks with a direct metal-to-metal contact MEMS switch. The TTD network was designed to produce a flat delay time over a DC-40 GHz bandwidth. However, the delay range is only  $106.9 \sim 193.9$  ps, with only four control bits [8]. Shiban K Koul et al. proposed a three-bit phase shifter based on a radio frequency micro-electromechanical system (RFMEMS). The phase shifter used a MEMS single-pole eight-throw (SP8T) switch. The device was fabricated on a  $635~\mu m$  alumina substrate using coplanar waveguide (CPW) transmission lines. A symmetrical and compact SP8T switch is the main component of the three-bit phase shifter. The phase shifter provides an average return loss of better than 14 dB and an average insertion loss of 4.4~dB at 34.75–35.25~GHz. The mean phase error measured at 35~GHz is less than 0.98~degrees. The total area of the manufactured three-displacement phase apparatus is  $5.95~mm^2$ . The delay range available in the 34.75–35.25~GHz operating frequency band is approximately 80~ps to 157.8~ps [9].

This paper is organized as follows. We first recall the RF MEMS switch theory foundations while proposing a single-ended cantilever metal contact RF MEMS switch [10] model with excellent performance in DC~50 GHz. We put forward a model for a true-time delay unit in the TTDL network, which consists of a tee junction and three RF MEMS switches loading a GCPW line. Then, a TTDL network, which consists of a T-junction and three metal-to-metal contact RF MEMS switches loading a GCPW, is proposed to solve the problems mentioned above associated with existing TTDL networks. Finally, the manufacturing process used to build the switch model of the TTDL network is introduced.

## 2. Theory and Design

## 2.1. Design of the RF MEMS Switch

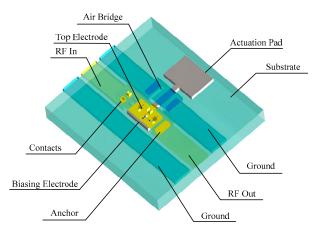

RF MEMS switches have superior RF performance in terms of insertion loss, isolation, power handling, and linearity over other RF switching devices [10]. To date, past advances in metal-to-metal contact MEMS switches have made the monolithic fabrication of high-quality switched-wire true-time delay (TTD) networks a relatively easy task. The structure diagram of the RF MEMS switch is shown in Figure 1.

Figure 1. Structure of the RF MEMS switch.

Since a certain number of RF MEMS switches are used in the true-time delay lines, while it is very susceptible to the time delay, the switching speed must be emphatically considered. The switching time ( $t_{od}$ ) for an over-damped system such as an RF MEMS switch Q < 0.5 is given [11] by

$$t_{od} = \frac{2bg^3}{3\varepsilon_0 AV_S^2} = \frac{9V_P^2}{8\pi f QV_S^2} \tag{1}$$

Micromachines 2023, 14, 246 3 of 9

where b and A are the air damping constant and the top electrode area, respectively.  $V_p$  and  $V_s$  are the pull-in and supplied voltage. f and  $\varepsilon_0$  are the mechanical resonance frequency of the switch and the permittivity of free space. The actuation voltage  $V_s$  is selected to be slightly higher than the pull-in voltage calculated in (1), to increase the switching speed.

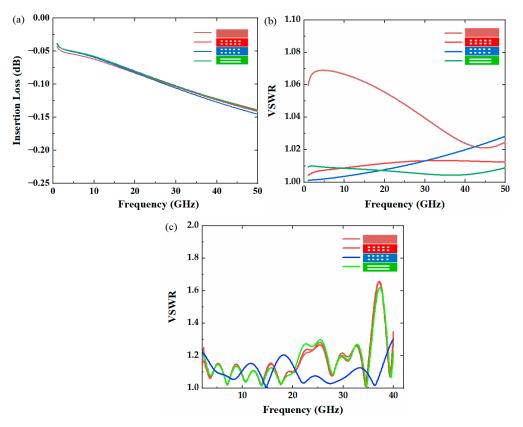

Four types of RF switches with different top electrodes are compared, which are a straight plate, square-etch hole, circular-etch hole, and slot-etch hole. The dimensions of the four upper electrodes are shown in Table 1. The insertion loss and voltage standing wave ratio (VSWR) are simulated using the ANSOFT HFSS software. The simulated performance is shown in Figure 2a–c.

| <b>Table 1.</b> Structural p | parameters of | four top | electrodes. |

|------------------------------|---------------|----------|-------------|

|------------------------------|---------------|----------|-------------|

| Dimension | Value (μm) | Comments                        |

|-----------|------------|---------------------------------|

| L         | 62         | Length of electrode             |

| W         | 25         | Width of electrode              |

| R         | 2          | Radius of circular-etch hole    |

| S         | 4          | Side length of square-etch hole |

| S1        | 4          | Side length of slot-etch hole   |

| S2        | 41         | Width of slot-etch hole         |

**Figure 2.** (a) Insertion loss (S<sub>21</sub>) simulation results of four different types of top electrode switches. (b) Voltage standing wave ratio (VSWR) simulation results of four different types of top electrode switches. (c) VSWR of four release holes in State\_3.

As shown in Figure 2, the simulated insertion loss of the four top electrode switches is almost the same, but the VSWR, which significantly affects the overall matching of the true-time delay lines, has different performance. The VSWR of the switch with the straight top electrode is the worst, and the other three with etch holes are better. We can conclude that the etch hole of the top electrode can not only help to increase the switching speed but also improves the voltage standing wave ratio. As shown in Figure 2c, we use HFSS to simulate the VSWR of the full TTDL network. It can be seen that the VSWR with a circular

Micromachines 2023, 14, 246 4 of 9

upper electrode release hole is significantly better than that with a slot-type release hole, even though the slot provides a smaller VSWR in the case of a single switch.

## 2.2. TTDL Unit Structure and Design

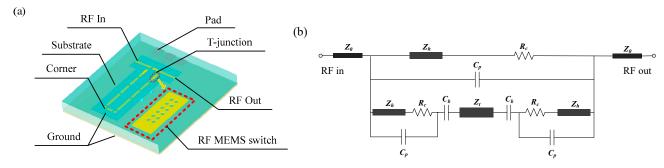

A one-bit TTDL unit is shown in Figure 3a. It consists of two T-junctions, corners, two transmission lines of different electrical lengths, and three RF MEMS switches. The two T-junctions and the three RF MEMS switches connected to them can form two valid paths to select delay transmission lines with different electrical lengths, so that the signal can achieve the purpose of delaying. The "ON" state equivalent circuit diagram of a one-bit TTDL unit is shown in Figure 3b.

**Figure 3.** (a) Structure of the TTDL unit. (b) The "ON" state equivalent circuit diagram of the TTDL unit.

$Z_0$  is the equivalent impedance of the coplanar waveguide (CPW),  $R_c$  is the contact resistance between the upper electrode and the CPW signal line,  $C_p$  is the coupling capacitance at the input and output ends of the CPW signal line,  $Z_h$  is the characteristic impedance of the upper electrode section of the RF MEMS switch,  $C_b$  is the grounding capacitance between the air bridge membrane structure and the lower signal line, and  $Z_t$  is the equivalent impedance of the transmission line, which contributes the group delay.

In normal conditions, the distance between the input and output of the signal line is much greater than the distance between the top electrode and the CPW signal line. Therefore, when analyzing the equivalent circuit of the RF MEMS switch, the influence of  $C_p$  can be ignored [12]. The inductance matching section will complement the grounding capacitance  $C_p$ .

The performance of the TTDL unit is highly dependent upon the design of the T-junction, since the signal must traverse 18 switches and 18 tee junctions for the selected most significant bit (MSB) state. The T-junctions are critical components that control the flow of the RF signal, and the presence of a discontinuity in the ground of the CPW here has a significant impact on the performance of the device. Consequently, an air bridge must be erected at the corner of the T-junction to connect the ground wires on both sides of the signal line to suppress the influence caused by the asymmetry of the ground wires. However, this three-dimensional bridge membrane structure will form an additional grounding capacitance with the lower signal line, so an inductance matching section should be added [13].

The corner is a necessary part of the TTDL network to change the signal transmission direction. The CPW discontinuity also occurs at the corner because there is a significant distance difference between the electromagnetic waves propagating in the slots on both sides of the signal line, which causes odd mode transmission [14], so a transition structure is required.

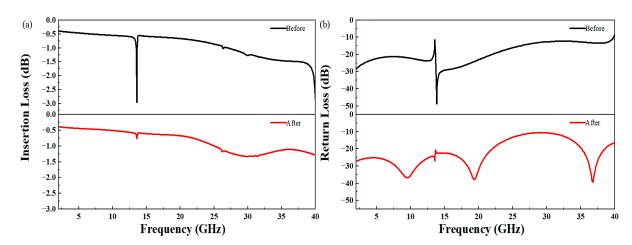

By adding the inductance matching section and corner transition structure and introducing an air bridge, the insertion loss and return loss of the TTDL unit can be greatly improved, as shown in Figure 4a,b, respectively.

Micromachines 2023, 14, 246 5 of 9

**Figure 4.** Simulation results before and after optimization for the TTDL unit: (a) insertion loss  $(S_{21})$ , (b) return loss  $(S_{11})$ .

# 2.3. Design of TTDL Network

In engineering, group delay is always regarded as the envelope delay of a signal [15–18]. In most cases, the TTDL network needs an architecture with a specific gain and linear phase in the required frequency range to provide the best possible impedance match and delay flatness.

Equation (2) shows the relationship between the transmission line length, the equivalent dielectric constant of the substrate, and the group delay amount:

$$\tau_{\rm d} = \frac{d\phi(\omega)}{d\omega} = \frac{l}{v_p} = \frac{l}{c} \sqrt{\frac{\varepsilon_s + 1}{2}}$$

(2)

where  $\tau_d$  is the group delay, l is the active length of the transmission line,  $v_p$  is the phase velocity,  $\varepsilon_s$  is the equivalent dielectric constant of the substrate, and c is the speed of light in a vacuum.

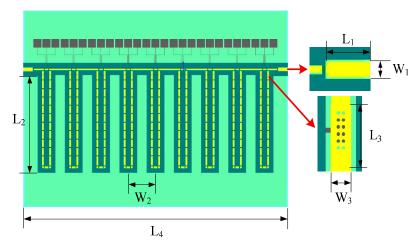

Based on Equation (2) and the TTDL unit pre-simulation and analysis in the previous section, we designed a 9-bit TTDL network. The MEMS switch-line TTDL network comprises nine cascaded TTDL units, using a network of GCPW lines, 25  $\mu m$  wide, on a 300- $\mu m$ -thick silicon dioxide substrate, and the characteristic impedance of its input/output terminals is 50  $\Omega$ . The 9-bit TTDL network was fabricated using MEMS technology and is mainly composed of a metal structure on the surface, a ground plane on the back, a through-hole between the two, and a substrate, as shown in Figure 5.

Figure 5. MEMS TTDL network diagram.

Micromachines 2023, 14, 246 6 of 9

The structural parameters are shown in Table 2.

| <b>Table 2.</b> Structural | parameters of the | TTDL network. |

|----------------------------|-------------------|---------------|

|----------------------------|-------------------|---------------|

| Dimension | Value (μm) | Comments                   |

|-----------|------------|----------------------------|

| L1        | 182        | Length of port signal line |

| L2        | 3376       | Length of TTDL per unit    |

| L3        | 62         | Length of RF switch        |

| L4        | 5000       | Length of substrate        |

| W1        | 120        | Width of port signal line  |

| W2        | 515        | Width of TTDL unit         |

| W3        | 25         | Width of RF switch         |

| T1        | 300        | Thickness of substrate     |

| T2        | 3          | Thickness of background    |

| Т3        | 2          | Thickness of structure     |

| D1        | 4          | Diameter of etch hole      |

By controlling the length of the delay transmission line and optimizing the spacing between TTDL units, a TTDL network with excellent RF performance can be obtained. The structural parameters are shown in Table 1. The RF performance of the TTDL network was modeled and simulated using the ANSOFT HFSS software.

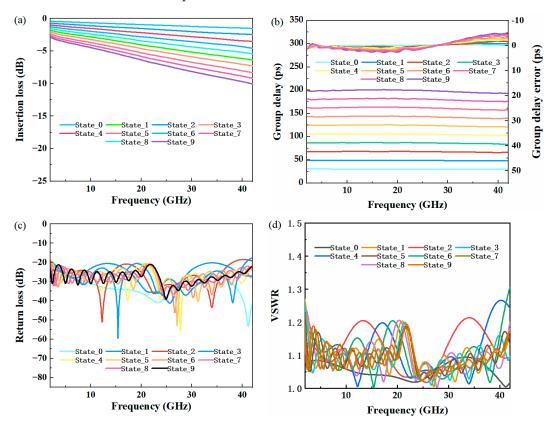

Figure 6a–d show the simulation results for the  $IL(S_{21})$ , group delay, group delay error, RL(S11), and VSWR of the TTDL network, respectively. When upper switches 1~9 are closed and other switches are disconnected, it represents the start bit of the TTDL network, and the group delay is 30.01 ps. When switch 1 is off, and upper switches 2~9 and lower switches  $1'\sim9''$  are closed, it means that the first bit is enabled, the group delay is 48.04 ps, and the step is 18 ps. By analogy, from the second to ninth bits, the TTDL network has ten delay states, realizing a nine-bit controllable group delay from 30 ps to 200 ps, and the interval is 18 ps.

**Figure 6.** Simulated results of the TTDL network: (a) insertion loss, (b) group delay and group delay error, (c) return loss, and (d) VSWR.

Micromachines 2023, 14, 246 7 of 9

| <b>Table 3.</b> Corresponding TTDL network performance of each switch state | (@42GHz) |  |

|-----------------------------------------------------------------------------|----------|--|

|                                                                             |          |  |

| State   | Group Delay<br>(ps) | Insertion Loss<br>(I.L) (dB) | Return Loss<br>(R.L) (dB) | VSWR |

|---------|---------------------|------------------------------|---------------------------|------|

| State_0 | 30.01               | -1.55                        | -41.18                    | 1.02 |

| State_1 | 48.04               | -2.50                        | -26.98                    | 1.09 |

| State_2 | 65.91               | -3.54                        | -19.30                    | 1.24 |

| State_3 | 83.03               | -4.58                        | -17.55                    | 1.31 |

| State_4 | 102.26              | -5.47                        | -20.77                    | 1.20 |

| State_5 | 120.62              | -6.42                        | -21.65                    | 1.18 |

| State_6 | 139.22              | -7.30                        | -26.74                    | 1.10 |

| State_7 | 157.85              | -8.35                        | -24.08                    | 1.13 |

| State_8 | 175.55              | -9.21                        | -22.14                    | 1.17 |

| State_9 | 193.33              | -10.07                       | -22.04                    | 1.17 |

The simulation results show that the group delay of the most significant bit (MSB) state of the TTDL network is 193.33 ps at 42 GHz, which corresponds to a maximum insertion loss of approximately -10.07 dB. The least significant bit (LSB) state of the TTDL network is 30.01 ps at 42 GHz, which corresponds to a minimum insertion loss of approximately -1.55 dB. At 42 GHz, the difference between the insertion loss and return loss is greater than 10 dB for nine states. The group DV across the bandwidth is within  $\pm 2.5\%$  for all the delay states. As a result, the TTDL can support wide steering angles for the phased array antenna with a broad bandwidth. This nine-bit TTDL network performs well in an adjustable TTDL network, and it can switch ten channels with fewer switches.

## 3. Comparison and Discussion

The modeled results of the MEMS TTDL network are shown in Table 4, together with other published results. DBW is defined as the product of the maximum delay and bandwidth [19]. It can be seen that this work achieves the most control bits and largest DBW.

Table 4. Comparison of TTDL networks.

| Ref.      | Frequency<br>(GHz) | Bit<br>(Resolution) | Maximum<br>Delay (ps) | DBW  | Technology | Size<br>(mm²)      |

|-----------|--------------------|---------------------|-----------------------|------|------------|--------------------|

| 2003 [8]  | 0 - 40             | 3                   | 61 - 86               | 3.44 | MEMS       | $0.84 \times 0.62$ |

| 2013 [20] | 15 - 40            | 3                   | 42                    | 1.05 | CMOS       | $1.1 \times 0.9$   |

| 2014 [21] | 10 - 50            | Continuous          | 32.8                  | 1.31 | CMOS       | 0.22               |

| 2015 [22] | 1 - 2.5            | _                   | 550                   | 0.83 | CMOS       | 0.07               |

| 2018 [23] | 6 - 18             | 8                   | 255                   | 3.06 | GaAs HBT   | $3.5 \times 3.7$   |

| 2020 [24] | 0.1 - 0.5          | _                   | 2000                  | 0.8  | CMOS       | 0.12               |

| 2022 [25] | 0 - 0.8            | 4                   | 3800                  | 3.04 | CMOS       | 1.98               |

| This work | 2 - 42             | 9                   | 200                   | 8    | MEMS       | $5 \times 5$       |

# 4. Conclusions

A compact MEMS wideband switched-line TTDL network operating over 2-42 GHz is presented using compact TTDL units. The proposed TTDL units are composed of the RF MEMS switch and GCPW to compensate for the DV. The TTDL network provides nine-bit delay control with an MSB value of 200 ps and an LSB value of 30 ps, with an RMS delay of fewer than 5 ps, respectively. Compared with other reported TTDL networks, the proposed TTDL network has the most control bits and highest DBW to date. The results show that the proposed TTDL network is an attractive option for a wideband phased array antenna system.

Micromachines 2023, 14, 246 8 of 9

**Author Contributions:** Conceptualization, methodology, software, validation, formal analysis, Q.W. and Z.S.; investigation, Q.W., Z.S., G.Z., J.L. and X.G.; resources, Q.W., Z.S. and M.L.; data curation, Q.W. and Z.S.; writing—original draft preparation, Z.S. and Y.Z.; writing—review and editing, Q.W. and Z.S.; visualization, Q.W., Z.S., G.Z., J.W. and X.G.; supervision, M.L.; project administration, Q.W. and M.L.; funding acquisition, Q.W. and M.L. All authors have read and agreed to the published version of the manuscript.

**Funding:** This research was funded by the Equipment Development Department New Product Project, Shanxi Province Postgraduate Education Reform Project, "Double First-Class" Disciplines National First-Class Curriculum Construction, and National Future Technical College Construction Project, grant numbers 2019XW0010, 110121, 11013168, and 11013169.

Data Availability Statement: Not applicable.

**Acknowledgments:** We thank the School of Instrument and Intelligent Future Technology for their funding support.

Conflicts of Interest: The authors declare no conflict of interest.

#### References

- 1. Sun, H.; Li, S.; Wang, Q.; Li, X. True Time Delay Technique Application in Phased Array Antenna. J. Microw. 2021, 37, 9–15.

- Zhang, J.; Li, J.; Sun, H. A study on layered schemereal—Time delayers for the wideband phased array. Mod. Radar 2010, 32, 75–78.

- 3. Shi, R.; Ruan, J.; Lv, J. Dual-Frequency Interrogation and Hierarchical Evaluation Scheme for SAW Reflective Delay-Line Sensors. *IEEE Trans. Ultrason. Eng.* **2020**, *67*, 1258–1266. [CrossRef] [PubMed]

- 4. Kéfélian, F.; Jiang, H.; Lemonde, P.; Santarelli, G. Ultralow-frequency-noise stabilization of a laser by locking to an optical fiber-delay line. *Opt. Lett.* **2009**, *34*, 914–916. [CrossRef] [PubMed]

- 5. Barker, S.; Rebeiz, G.M. Distributed MEMS true-time delay phase shifters and wide-band switches. *IEEE Trans. Microw. Theory Tech.* **1998**, *46*, 1881–1890. [CrossRef]

- 6. Barker, N.S.; Rebeiz, G.M. Optimization of Distributed MEMS Transmission-Line Phase Shifters-U-Band and W-Band Designs. *IEEE Trans. Microw. Theory Tech.* **2000**, *48*, 1957–1966.

- 7. Xu, Z.; Wu, T.; Yu, S. Beam Steering Technique for Distributed Wideband Phased Array Radar. Mod. Radar 2021, 43, 70–74.

- 8. Hacker, J.B.; Mihailovich, R.E.; Kim, M.; DeNatale, J.F. A Ka band 3-bit RF MEMS true-time-delay network. *IEEE Trans. Microw. Theory Tech.* **2003**, *51*, 305–308. [CrossRef]

- 9. Koul, S.K.; Dey, S.; Poddar, A.K.; Rohde, U.L. Ka-band reliable and compact 3-bit true-time-delay phase shifter using MEMS single-pole-eight-throw switching networks. *J. Micromech. Microeng.* **2016**, 26, 10. [CrossRef]

- 10. Li, M.; Liu, Q.; Wu, Q. Broadband radio frequency MEMS series contact switch with low insertion loss. *Microsyst. Technol.* **2019**, 25, 1619–1625. [CrossRef]

- 11. Rebeiz, G.M. RF MEMS: Theory, Design, and Technology; John Wiley & Sons: Hoboken, NJ, USA, 2003; p. 92.

- 12. Hou, Z. Study on a DC-Contact Series RF MEMS Switch for High Power and Wide Band Applications. Ph.D. Dissertation, Tsinghua University, Beijing, China, 2008.

- 13. Weller, T.M.; Henderson, R.M.; Robertson, S.V.; Katehi, L.P.B. Optimization of MM-wave distribution networks using silicon-based CPW. In *IEEE MTT-S International Microwave Symposium Digest*; IEEE Press: New York, NY, USA, 1998; Volume 2, pp. 537–540.

- 14. Li, X.; Fang, S.; Pei, H.; Wang, Z. Novel CPW-ACPW phase compensated structure in CPW bend. In Proceedings of the 9th International Symposium on Antennas, Propagation, and Electromagnetic Theory, Guangzhou, China, 29 November 2010.

- 15. Wang, J.; Feng, Z. Time-domain nature of group delay. Chin. Phys. B 2015, 24, 100301. [CrossRef]

- 16. Wang, L.J.; Kuzmich, A.; Dogariu, A. Gain-assisted superluminal light propagation. *Nature* **2019**, 406, 277–279. [CrossRef] [PubMed]

- 17. Stenner, M.D.; Gauthier, D.J.; Neifeld, M.A. The speed of information in a 'fast-light' optical medium. *Nature* **2003**, 425, 695–698. [CrossRef] [PubMed]

- 18. Büttiker, M.; Washburn, S. Ado about nothing much? Nature 2003, 244, 271–272. [CrossRef] [PubMed]

- 19. Jung, M.; Min, B.W. A Compact 3-30-GHz 68.5-ps CMOS True-Time Delay for Wideband Phased Array Systems. *IEEE Trans. Microw. Theory Tech.* **2020**, *68*, 5371–5380. [CrossRef]

- 20. Park, S.; Jeon, S. A 15-40 GHz CMOS true-time delay circuit for UWB multi-antenna systems. *IEEE Microw. Wirel. Compon. Lett.* **2013**, 23, 149–151. [CrossRef]

- 21. Ma, Q.; Leenaerts, D.; Mahmoudi, R. A 10-50GHz True-Time-Delay phase shifter with max 3.9% delay variation. In Proceedings of the IEEE Radio Frequency Integrated Circuits Symposium, Tampa, FL, USA, 1–3 June 2014.

- 22. Garakoui, S.; Klumperink, K.E.A.; Nauta, M.B.; van Vliet, F.E. Compact cascadable g m-C all-pass true time delay cell with reduced delay variation over frequency. *IEEE J. Solid-State Circuits* **2015**, *50*, 693–703. [CrossRef]

- 23. Jeong, J.C.; Yom, I.B.; Kim, J.D.; Lee, W.Y.; Lee, C.H. A 6-18-GHz GaAs multifunction chip with 8-bit true time delay and 7-bit amplitude control. *IEEE Trans. Microw. Theory Tech.* **2018**, *66*, 2220–2230. [CrossRef]

Micromachines 2023, 14, 246 9 of 9

24. Zolkov, E.; Madjar, A.; Weiss, R.; Cohen, E. Analysis and Design of N-Path True-Time-Delay Circuit. *IEEE Trans. Microw. Theory Tech.* **2020**, *68*, 5381–5394. [CrossRef]

25. Lin, C.C.; Puglisi, C.; Ghaderi, E.; Xu, Q.Y.; Cabric, D. Multi-Mode Spatial Signal Processor with Rainbow-Like Fast Beam Training and Wideband Communications Using True-Time-Delay Arrays. *IEEE J. Solid-State Circuits* **2022**, *57*, 3348–3360. [CrossRef]

**Disclaimer/Publisher's Note:** The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content.