# Review Random Telegraph Noise in 3D NAND Flash Memories

Alessandro S. Spinelli \*🕩, Gerardo Malavena 🕑, Andrea L. Lacaita ២ and Christian Monzio Compagnoni 🕑

Dipartimento di Elettronica, Informazione e Bioingegneria, Politecnico di Milano, 20133 Milan, Italy; gerardo.malavena@polimi.it (G.M.); andrea.lacaita@polimi.it (A.L.L.); christian.monzio@polimi.it (C.M.C.) \* Correspondence: alessandro.spinelli@polimi.it; Tel.: +39-02-2399-4001

**Abstract:** In this paper, we review the phenomenology of random telegraph noise (RTN) in 3D NAND Flash arrays. The main features of such arrays resulting from their mainstream integration scheme are first discussed, pointing out the relevant role played by the polycrystalline nature of the string silicon channels on current transport. Starting from that, experimental data for RTN in 3D arrays are presented and explained via theoretical and simulation models. The attention is drawn, in particular, to the changes in the RTN dependences on the array working conditions that resulted from the transition from planar to 3D architectures. Such changes are explained by considering the impact of highly-defective grain boundaries on percolative current transport in cell channels in combination with the localized nature of the RTN traps.

Keywords: 3D NAND Flash memories; random telegraph noise; Flash memory reliability

Citation: Spinelli, A.S.; Malavena, G.; Lacaita, A.L.; Monzio Compagnoni, C. Random Telegraph Noise in 3D NAND Flash Memories. *Micromachines* **2021**, *12*, 703. https://doi.org/10.3390/mi12060703

Academic Editors: Cristian Zambelli and Rino Micheloni

Received: 11 May 2021 Accepted: 4 June 2021 Published: 16 June 2021

**Publisher's Note:** MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations.

**Copyright:** © 2021 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https:// creativecommons.org/licenses/by/ 4.0/).

# 1. Introduction

Random telegraph noise (RTN) in MOS transistors has been an important topic of interest in the solid-state device community since the 80s, when results of low-frequency noise characterization [1] showed a transition from a typical 1/f behavior at high temperatures to a series of discrete switching events as temperature was lowered. Similar observations were soon made when moving from large- to small-area devices [2], and interpreted in terms of capture/emission of electrons by single interface traps. On the theoretical side, this result highlighted the importance of the number fluctuation contribution to the flicker noise, but prompted the emergence of a new limitation to MOS device operation as well [3].

Moving from early investigations and models [4-9], the RTN picture grew more complex, as novel time and amplitude observations [10-14] hinted at a non-negligible role played by non-uniform electron conduction in submicron devices [15,16]. This idea gained traction when the phenomenon began to be investigated in Flash memories [17-23], demonstrating current fluctuations up to 60% [22] and threshold voltage ( $V_T$ ) shifts reaching 700 mV [18] in 90-nm technology node devices. The physical picture now accepted that accounts for such results is based on the fact that, in scaled devices, dopants must be viewed as individual ions rather than a continuous distribution, resulting in randomly-placed charges in the depletion region. Such random point charges [24–27] give rise to sharp peaks in the band energy profile of the channel of an MOS transistor, resulting in local modulation of the current flow and filamentary conduction. If a "strategic" trap happens to be placed right above a current path, electron trapping will effectively shut off such a path, resulting in a large drain current and  $V_T$  fluctuation [28–31]. On the other hand, if the trap is placed over a region in which little current flows, its trapping/detrapping will barely affect the overall current. Such an idea has been successfully applied to explain the statistical distribution of the RTN fluctuations in NOR and NAND arrays, measured in terms of their amplitude [19,32,33] and time constants [34–36], providing a useful tool for extracting information about the impact of device parameters on RTN. A recent review of the issue can be found in [37].

The above-mentioned framework has served nicely the Flash community until the first decade of the 21st century, when several limitations to the scaling of the planar NAND

technology prompted the emergence of 3D arrays [38]. In such devices, the RTN picture just outlined fell short of adequately describing the experimental data, in view of the peculiar characteristics of the polycrystalline material used as conduction channel.

In the following, we will review in detail the physics of RTN in 3D NAND Flash memories, discussing the main experimental data and physical models developed to quantitatively account for them. We begin our discussion with a brief summary of the main 3D array architecture and cell structure, followed by a description of electron transport in 3D NAND channels. This will allow us to develop a consistent picture of RTN in 3D NAND devices, whose main features will be highlighted. After this part, we will focus our attention on the main experimental data presented in the literature, taking advantage of the model results to provide interpretation for them.

#### 2. Array and Cell Structure

Among the several architectural solutions for 3D storage [39–46], the one employing vertical-channel strings crossed by a set of planar wordlines has become the most effective one [47–50], and is the focus of this section. Here we will briefly describe the main features of such an array, namely its organization and cell structure, referring to previous works for further details [51].

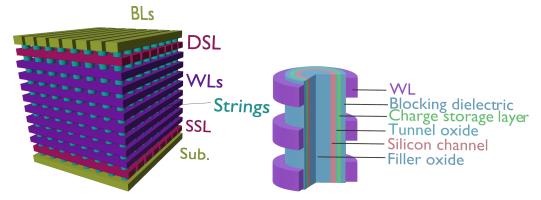

A pictorial view of the array is shown in Figure 1 (left): note that the cell strings run vertically from the substrate to the bitlines. As in planar arrays, select elements are needed near the source and drain ends of the string, integrated in rows running orthogonally to the bitlines. The rest of the cells are contacted by planar wordlines that span over an entire block of the array. One of the advantages of this structure is that the large increase in density allowed by the exploitation of the third dimension makes it possible to relieve some of the pressure on channel length scaling and its many drawbacks from the viewpoint of process complexity and reliability, well known in planar devices [52,53]: cell length in 3D NAND is around 25-30 nm [54], with the additional advantage of becoming less dependent on the availability of advanced lithography tools. A second advantage of this solution lies in its manufacturing process: memory cells are not patterned individually, but they are formed all at once as cylindrical holes are cut through the stacked wordlines, creating the strings. This procedure entails that the elementary cell becomes a gate-all-around, vertical-channel transistor, with the advantage of a better electrostatic control from the gate. A schematic view of such a device is shown in Figure 1 (right): starting from the outside we meet a contacted wordline, a blocking dielectric and a charge-storage layer, that can either be a floating gate [47,55–59], similar to planar NAND devices, or a charge-trap layer [60–64], followed by the tunnel oxide. Beyond the oxide, we can notice a thin silicon region and an inner oxide filling the central region of the cylinder, labeled filler oxide for simplicity. This structure, where the conductive channel is a hollow cylinder, is referred to as a "Macaroni" MOSFET, and is the result of clever device engineering in 3D NAND: in fact, after the vertical high-aspect ratio holes have been etched in the structure of Figure 1 (left), and the blocking, storage and tunnel layers deposited, the remaining part of the cylinder must be filled with silicon. The result is a polycrystalline channel whose central region is plagued by a large defectivity, impairing the device performance. To avoid such a drawback, a very thin polysilicon layer is deposited on the gate dielectric, while the remaining central region of the cylinder is filled with a dielectric [40], gaining two distinct advantages: first, thinning of the silicon body results in reduced short-channel effects and better electrostatic control from the gate; second, defect removal further contributes to better subthreshold slope and array performance.

**Figure 1.** (Left) Conceptual view of a vertical-channel 3D NAND array with its main elements (SSL = source select line, WLs = wordlines, DSL = drain select line, BLs = bitlines). (**Right**) pictorial view of an array string highlighting the structure of the elementary memory cells.

#### 3. Polysilicon Conduction

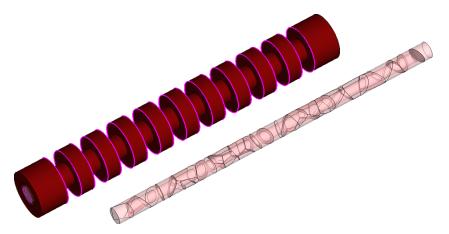

The overview on the memory cell design given in the previous section already suggested that the polycrystalline character of the conduction channel is a key parameter from the viewpoint of device performance. A polycrystalline material, in fact, is formed by single-crystal regions labeled grains, with different crystallographic orientations. Such regions are separated by highly-defective interfaces, or grain boundaries (GBs) [65]. A pictorial view of a NAND string of ten cells with its inner polysilicon region and grains is shown in Figure 2: note the random structure of grains and GBs, that are the key elements affecting device current and variability.

**Figure 2.** Pictorial view of a ten-cell memory string (**left**) and of the inner polysilicon regions separated into polycrystalline grains (**right**). The example is the result of a TCAD simulation of the cell structure where polysilicon grains are obtained via Voronoi tessellation of the silicon region.

One of the key properties of polysilicon is its trap density, whose value has been estimated by several works, based on either direct optical or electrical experimental measurements [66–74] or via numerical device simulations [75–79]. Many of such results point to a double-exponential energy distribution of donor-like and acceptor-like states of the form (for acceptor-like states in the upper half of the energy gap):

$$N_{GB}(E) = N_T e^{-(E - E_C)/E_T} + N_D e^{-(E - E_C)/E_D},$$

(1)

where the reported range for the acceptor-like states parameters is listed in Table 1. Note that the first exponential distribution is characterized by a large peak density  $N_T$  and a small characteristic energy  $E_T$ , and is usually referred to as tail states distribution, as a consequence of its location near the edge of the gap. The second has a lower peak density  $N_D$  but a higher energy  $E_D$ , and is usually labeled deep states distribution. Note also that

trap densities are given as volumetric densities: this was useful in early simulation works, where a uniform trap density in the semiconductor body was assumed for simplicity. From a physical viewpoint, however, traps are expected to be mainly located at GBs, and an areal density  $\sigma$  is then needed. A conversion between volumetric and areal densities is readily achieved assuming for simplicity a spherical grain size with radius  $r_G$ , and placing all volume traps on the sphere surface. This leads to

$$4\pi r_G^2 \sigma = \frac{4}{3}\pi r_G^3 N_{GB} \Rightarrow \sigma = \frac{r_G}{3} N_{GB},$$

(2)

or a very similar conversion factor as in [79].

**Table 1.** Range of parameter values for the acceptor-like states in the polysilicon, according to the literature (see text for references).

| $N_T  [{ m cm}^{-3}  { m eV}^{-1}]$ | $E_T$ [meV] | $N_D \ [{ m cm}^{-3} \ { m eV}^{-1}]$  | $E_D$ [meV] |

|-------------------------------------|-------------|----------------------------------------|-------------|

| $9 	imes 10^{19} 	extrm{}10^{21}$   | 16.6–80     | $1.2 \times 10^{18}  9 \times 10^{19}$ | 80–500      |

Electron transport in polysilicon has been studied since the 70s, as this material found applications in resistors, interconnections, and silicon-gate MOSFETs. From the viewpoint of current conduction, we can identify two modeling approaches, that differ in the way GBs are treated: one approach is to extend the drift-diffusion model usually adopted in monocrystalline silicon, describing GBs as trapping centers with a reduced mobility [80–82]; the other is based on a thermionic emission model at the GBs [83–87]. Although the latter seems to be gaining traction in recent literature, a definitive conclusion has not been reached, yet, and a recent study of the different dependences implied by such models can be found in [88,89].

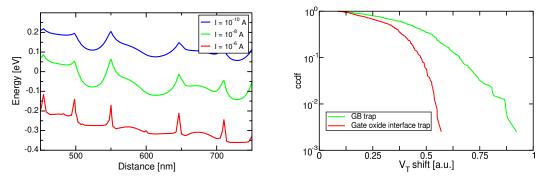

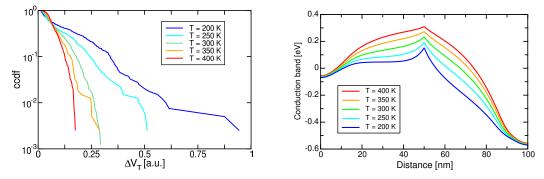

The above-mentioned numerical models of conduction have been used to investigate the effect of GBs on variability in nanowires [90–95] and 3D NAND devices [96,97]. A recent study based on a drift-diffusion transport within the grains and thermionic emission at the GBs [98–101] has demonstrated a good capability to reproduce several features of experimental data, including its temperature dependence. Figure 3 (left) shows a typical conduction-band profile along the channel of a 3D NAND string, for increasing values of the control-gate bias, as resulting from such model. Note that the profile is not smooth, featuring peaks in correspondence of the highly-defective GBs. As gate bias is increased, the band bending lowers the conduction-band profile, increasing the localized trap occupation and sharpening the peaks, which become the true bottlenecks of conduction [100]. This result makes clear that GBs are an additional source of non-uniformity in the current conduction, which means that they might be expected to play a main role in RTN. This is even more apparent if we consider that GB trap densities (see Table 1) are much larger than typical doping concentrations used in 3D NAND strings. A similar approach was also followed by [102].

The above-mentioned model has been applied to investigate the impact of GB traps on RTN [99,101] within a Monte Carlo approach: random configuration of GBs are first generated in the silicon region after a Voronoi tessellation [92], and traps are placed at the interfaces following the previously-discussed energy distribution. Drain current is computed up to a specified threshold, defined at a constant current level, after which an additional RTN trap is filled with an electron and the resulting  $V_T$  shift computed. Results for a template device are also reported in Figure 3, for the case of a single trap placed at one random position in a GB, and for a trap placed at a random position at the silicon/gate oxide interface. It is clear that GB traps are much more effective in modulating the electron conduction and result in larger  $V_T$  fluctuations.

**Figure 3.** (Left) Conduction band profile for a 3D NAND string at different current levels. (right) RTN complementary cumulative distribution functions (ccdfs) for traps placed at the GBs or at the gate/oxide interface for a template device.

In spite of these encouraging results, several important features of this model still have to be assessed, such as the actual grain size [103–105], the mobility degradation and conduction process at the grain boundaries [106,107], and the impact of all these quantities, including architectural parameters and cell design, on RTN.

## 4. Experimental Data

The previous section was meant to provide a framework for the interpretation of the most relevant experimental data presented in the literature, that are discussed in the following. It must be noted, however, that RTN, as well as other reliability concerns in 3D NAND memories, remains a highly-confidential matter and very few data are published. We begin our analysis of RTN with single-trap data, moving then to statistical distributions and impact on device performance.

#### 4.1. Single-Trap Data

Investigation of the microscopic properties of RTN single traps in 3D NAND devices can be found in [108,109], where a statistical analysis of the noise power spectral density was also carried out. In those papers it was reported that the string current fluctuations due to single-trap RTN depend on the sensing current: as the current is increased, its fluctuations also increase when measured in absolute terms, but decrease in terms of relative change. Such a dependence was also found in [110] for the above-threshold region, and ascribed to the effect of traps at the silicon-oxide interfaces. These dependences reflect similar behaviors observed both experimentally and numerically in planar or cylindrical devices [111–113], where the increased screening exerted by the mobile carriers as the gate bias is raised, mitigating the effect of the RTN trap, was invoked as an explanation. Several works reported investigations of the capture and emission time constants and their dependence on gate bias and temperature, including the activation energies [114–117]. Their results do not point to any particular difference in the microscopic nature of such traps with respect to those active in planar devices (apart from a faster capture/emission dynamics suggested in [114]): this of course is not surprising and supports an interpretation of the RTN phenomenon based on the spatial distribution of such traps rather than on some peculiar characteristics.

#### 4.2. Array Statistical Data

From the viewpoint of the memory performance, the statistical distribution of the RTNinduced  $\Delta V_T$  is the main parameter. This kind of fluctuations in poly-Si channels were first shown (to our knowledge) in [118], on a nanowire structure (no filler oxide), showing an exponential distribution for  $\Delta V_T$ , which is a typical result of a percolation process. The same exponential dependence was reported on vertical NAND devices in [119–123], suggesting that the RTN distribution in arrays follows an  $e^{-\Delta V_T/\lambda}$  law, and can be effectively characterized by the slope  $\lambda$  of the exponential distribution. A comparison between 3D and planar cell RTN is reported in [124], where a larger RTN distribution was reported for the former, while an opposite result was claimed in [121]. It is obviously difficult if not impossible to critically assess those results and search for the reason of this discrepancy. However, from a general standpoint, the slope  $\lambda$  is related to both the trap density (affecting the percolation centers) and the electrostatic impact of a single trapped electron, that have an opposite trend when moving from planar to 3D devices: 3D cells are expected to have a higher trap density thanks to the presence of GBs, but feature also a larger cell (i.e., a larger capacitance and a lower electrostatic impact of a single electron). So, the different results might just be a consequence of different cell designs.

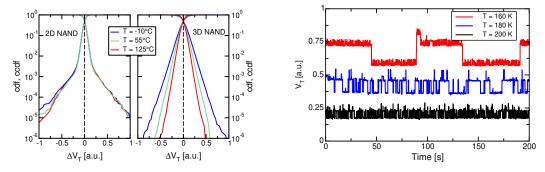

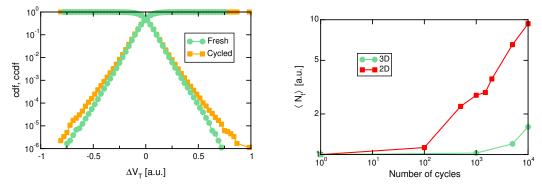

The impact of GB traps on RTN can also be noted in the comparison reported in [125,126] and carried out as a function of temperature in the range from -10 to 125 °C, that is shown in Figure 4 (left). First, please note that the shape of the two distributions is different: in 2D cells we notice clear exponential tails due to RTN departing from a central distribution, related to measurement noise in cells not affected by RTN; in 3D arrays, instead, we notice a single exponential distribution, suggesting that the large majority of cells in the 3D array are affected by RTN. A second point to stress is that the slope of the exponential distribution is reduced with respect to planar technologies [121,125,127]. Given the previous point, such an improvement seems mainly a consequence of the larger cell size of 3D arrays, although a role could also be played by the different conduction mechanism and percolation in planar and 3D devices (see for example [113] for a discussion on the RTN dependences in 3D devices). Finally, different temperature dependences are also apparent: while planar device RTN is temperature-independent [128], 3D NAND exhibit a decrease in  $\lambda$  at higher temperatures, as also reported in [115,116].

**Figure 4.** (Left) RTN cumulative density function (cdf) and its complementary (ccdf) for 2D and 3D NAND arrays at different temperatures [125,126], © 2017, IEEE. (**Right**)  $V_T$  fluctuations due to single RTN traps at different temperatures.

Such a different temperature dependence is important from a reliability standpoint and deserves further investigation. To this aim, the right side of Figure 4 shows the behavior of a single RTN trap as a function of time, for different temperatures. Besides a decrease in the absolute value of  $V_T$  for higher temperatures, reflecting an increase in the current, it is obvious that the fluctuation amplitude is decreasing as well. This behavior has been observed on a number of traps [126] and is the responsible for the improved RTN distribution. At first glance, the temperature dependence could be simply related to the thermal energy of the electrons and their better or worse capability to overcome the energy barriers, but this would not explain the difference between planar and 3D dependences. So, we must assume that temperature affects the percolation itself. To check this, we conducted simulations with the model presented in the previous section [98–101], for a template 3D NAND device at different temperatures. Results are presented in Figure 5 (left). Note that the decrease of the RTN slope at higher temperature is accounted for by the model, allowing to exploit its results to provide some more insight: to this aim, we have simulated a template device with a single GB orthogonal to the current flow and placed at the middle of the gate. Results for the conduction band at threshold at different temperatures are reported in Figure 5

(right), and feature significant differences: indeed, the conduction band peak, located at the GB and due to the localized trapped charge, becomes sharper at low temperatures, meaning that there is an increased trapped charge at low temperatures, resulting in more percolation centers. A reason for this lies in our definition of the threshold condition, that is a constant-current (10 nA) criterion. When temperature is lowered, thermal emission is reduced, and the string current lowers. To reach the same 10 nA value, gate bias must be increased, lowering the conduction band and leading to additional trap filling. Note also that this phenomenon does not take place in planar devices, where the percolation centers are the ionized dopants, whose density obviously does not change with the gate bias.

**Figure 5.** (Left) Simulation results for the RTN ccdf in a template 3D NAND device for different temperatures. (**Right**) Conduction band profile at different temperatures for a template device with a single GB located at the center of the channel.

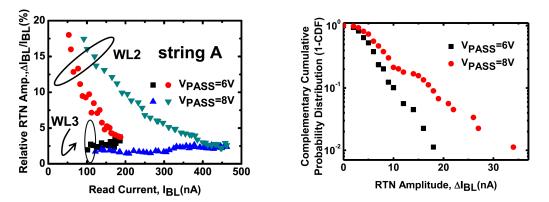

Additional dependences exhibited by random telegraph noise in 3D NAND were reported by [108,122] with reference to read current and pass voltage. Figure 6 (left) shows RTN data for cells on different wordlines as a function of the read current and pass voltage. While some cells do not exhibit significant RTN, the one labelled as WL2 features a decreasing relative fluctuation of the current as the read current is increased, in agreement with data previously discussed. However, data also show a dependence on the pass voltage, whose increase leads to a higher RTN. Similar data are reported in Figure 6 (right), where the RTN distribution is shown. Data show that the tail slope of the bitline current increases as the pass voltage is increased. This result was related to the previous one by the authors of [122], as increasing the pass voltage means a reduction of the read threshold voltage and an increase in the RTN fluctuations. However, further analysis are needed to clarify the link between the string operating conditions and the measured RTN.

**Figure 6.** RTN ccdf as a function of the read current (**left**) and of the pass bias, at a read current of 100 nA (**right**). From [122], © 2016, IEEE.

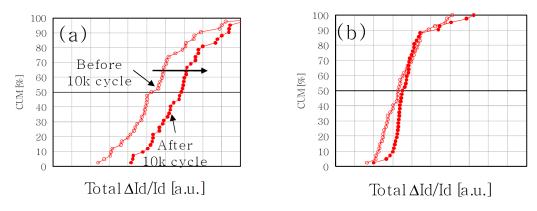

Finally, the effect of cycling on RTN in 3D arrays has been investigated in [110,119,126] and data from [126] are reported in Figure 7 (left). Note that the RTN  $\Delta V_T$  data for a fresh and a cycled array show only a minimal increase in the height and slope of the distribution,

which is again different from the noticeable increase in the RTN distribution reported in planar devices (see [128,129]). Such a difference can also be appreciated in Figure 7 (right), depicting the average number of traps  $\langle N_t \rangle$  extracted from fitting the RTN distributions with a simplified model [32]: note that the departing of  $\langle N_t \rangle$  from the initial value takes place at much higher cycling doses in the 3D NAND case than in the planar array. While this suggests an increased hardening of 3D cells against cycling-induced defects, it should not be forgotten that 3D cells feature a native trap density higher than their planar counterparts (see Figure 4, left), mostly due to the GB traps not present in crystalline silicon, which may hide the initial-stage growth of cycling-induced defects. It is also interesting to note that a stronger dependence on cycling in 3D arrays was instead reported in [119], which might be ascribed to either a larger trap generation rate due to different cycling conditions or to a lower number of native traps, as fewer traps in the NAND cells would result in a more noticeable increment due to cycling. Furthermore, a transient effect related to a non-stationary condition, as hinted by the asymmetric RTN distribution there reported (see [130] for discussion) could also affect the evaluation.

**Figure 7.** (Left) RTN cdf for a 3D NAND before and after cycling to 10k cycles [126], © 2018, IEEE. (**Right**) Average number of RTN traps as a function of cycling [126], © 2018, IEEE.

It is also interesting to note that data reported in Figure 7 were taken with programmed cells. However, in [110,131] a higher sensitivity of RTN to cycling was reported when cells are measured in the erased state (Figure 8). In the authors' view, this result is not a consequence of a different generation rate or annealing of stress-induced traps, but rather the result of different conduction profiles of the electrons as a consequence of the charge stored in the cells, enhancing the impact of newly-created traps at the interface. Such results demonstrate that the RTN picture is still not complete, notwithstanding the excellent work put forward by the scientific community.

**Figure 8.** RTN cdf before and after cycling for the case of erased (**a**) and programmed (**b**) cells [110], © 2014, IEEE.

# 5. Conclusions

Ever since its first detection in MOS devices, RTN has retained two opposite faces, being a remarkable probe into the microscopic physics of carrier interactions with defects on one side, and a reliability threat on the other. It appears safe to say that even the transition to 3D NAND has not affected such characters, that are instead enhanced by the additional challenges built by the polycrystalline conduction channel. In this frame, this work has presented a review of the most significant experimental results in the field of random telegraph noise in 3D NAND, highlighting its current understanding and some open issues that require further efforts from the scientific and technological communities.

Funding: This research received no external funding.

Acknowledgments: The authors would like to acknowledge support from C. Miccoli, G. Paolucci, D. Resnati and G. Nicosia.

Conflicts of Interest: The authors declare no conflict of interest.

## References

- Ralls, K.S.; Skocpol, W.J.; Jackel, L.D.; Howard, R.E.; Fetter, L.A.; Epworth, R.W.; Tennant, D.M. Discrete resistance switching in submicrometer silicon inversion layers: Individual interface traps and low-frequency (1/f) noise. *Phys. Rev. Lett.* 1984, 52, 228–231. [CrossRef]

- 2. Uren, M.J.; Day, D.J.; Kirton, M.J. 1/f and random telegraph noise in silicon metal-oxide-semiconductor field-effect transistors. *Appl. Phys. Lett.* **1985**, *47*, 1195–1197. [CrossRef]

- 3. Howard, R.E.; Skocpol, W.J.; Jackel, L.D.; Mankiewich, P.M.; Fetter, L.A.; Tennant, D.M.; Epworth, R.; Ralls, K.S. Single electron switching events in nanometer-scale Si MOSFET's. *IEEE Trans. Electron Devices* **1985**, *32*, 1669–1674. [CrossRef]

- 4. Kirton, M.J.; Uren, M.J. Capture and emission kinetics of individual Si:SiO<sub>2</sub> interface states. *Appl. Phys. Lett.* **1986**, *48*, 1270–1272. [CrossRef]

- Hung, K.K.; Ko, P.K.; Hu, C.; Cheng, Y.C. Flicker noise characterization of advanced MOS technologies. In Proceedings of the 1988 International Electron Devices Meeting, San Francisco, CA, USA, 11–14 December 1988; pp. 34–37.

- Hung, K.K.; Ko, P.K.; Hu, C.; Cheng, Y.C. Random telegraph noise of deep-submicrometer MOSFET's. *IEEE Electron Device Lett.* 1990, 11, 90–92. [CrossRef]

- 7. Fang, P.; Hung, K.K.; Ko, P.K.; Hu, C. Hot-electron-induced traps studied through the random telegraph noise. *IEEE Electron Device Lett.* **1991**, *12*, 273–275. [CrossRef]

- 8. Simoen, E.; Diericks, B.; Claeys, C.L.; Declerck, G.J. Explaining the amplitude of RTS noise in submicrometer MOSFET's. *IEEE Trans. Electron Devices* **1992**, *39*, 422–429. [CrossRef]

- 9. Tsai, M.H.; Ma, T.P.; Hook, T.B. Channel length dependence of random telegraph signal in sub-micron MOSFET's. *IEEE Electron Device Lett.* **1994**, *15*, 504–506. [CrossRef]

- 10. Uren, M.J.; Kirton, M.J.; Collins, S. Anomalous telegraph noise in small-area silicon metal-oxide-semiconductor field-effect transistors. *Phys. Rev. B* **1988**, *37*, 8346–8350. [CrossRef]

- 11. Kirton, M.J.; Uren, M.J. Noise in solid-state microstructures: A new perspective on individual defects, interface states and low-frequency (1/f) noise. *Adv. Phys.* **1989**, *38*, 367–468. [CrossRef]

- 12. Kirton, M.J.; Uren, M.J.; Collins, S.; Schultz, M.; Karmann, A.; Scheffer, K. Individual defects at the Si:SiO<sub>2</sub> interface. *Semicond. Sci. Technol.* **1989**, *4*, 1116–1126. [CrossRef]

- 13. Nakamura, H.; Yasuda, N.; Taniguchi, K.; Hamaguchi, C.; Toriumi, A. Existence of double-charged oxide traps in submicron MOSFET's. *Jpn. J. Appl. Phys.* **1989**, *28*, L2057–L2060. [CrossRef]

- 14. Ohata, A.; Toriumi, A.; Iwase, M.; Natori, K. Observation of random telegraph signals: Anomalous nature of defects at the Si/SiO<sub>2</sub> interface. *J. Appl. Phys.* **1990**, *68*, 200–204. [CrossRef]

- 15. Mueller, H.H.; Schulz, M. Conductance modulation of submicrometer metal-oxide-semiconductor field effect transistors by single-electron trapping. *J. Appl. Phys.* **1996**, *79*, 4178–4180. [CrossRef]

- Mueller, H.H.; Schulz, M. Statistics of random telegraph noise in sub-µm MOSFETs. In Proceedings of the 14th International Conference: Noise in Physical Systems and 1/f Fluctuations, Leuven, Belgium, 14–18 July 1997; pp. 195–200.

- Kurata, H.; Otsuga, K.; Kotabe, A.; Kajiyama, S.; Osabe, T.; Sasago, Y.; Narumi, S.; Tokami, K.; Kamohara, S.; Tsuchiya, O. The impact of random telegraph signals on the scaling of multilevel Flash memories. In Proceedings of the 2006 Symposium on VLSI Circuits, Honolulu, HI, USA, 15–17 June 2006; pp. 112–113.

- Tega, N.; Miki, H.; Osabe, T.; Kotabe, A.; Otsuga, K.; Kurata, H.; Kamohara, S.; Tokami, K.; Ikeda, Y.; Yamada, R. Anomalously large threshold voltage fluctuation by complex random telegraph signal in floating gate Flash memory. In Proceedings of the 2006 International Electron Devices Meeting, San Francisco, CA, USA, 11–13 December 2006; pp. 491–494.

- Gusmeroli, R.; Monzio Compagnoni, C.; Riva, A.; Spinelli, A.S.; Lacaita, A.L.; Bonanomi, M.; Visconti, A. Defects spectroscopy in SiO<sub>2</sub> by statistical random telegraph noise analysis. In Proceedings of the 2006 International Electron Devices Meeting, San Francisco, CA, USA, 11–13 December 2006; pp. 483–486.

- Kurata, H.; Otsuga, K.; Kotabe, A.; Kajiyama, S.; Osabe, T.; Sasago, Y.; Narumi, S.; Tokami, K.; Kamohara, S.; Tsuchiya, O. Random telegraph signal in Flash memory: Its impact on scaling of multilevel Flash memory beyond the 90-nm node. *IEEE J. Solid-State Circuits* 2007, 42, 1362–1369. [CrossRef]

- Fukuda, K.; Shimizu, Y.; Amemiya, K.; Kamoshida, M.; Hu, C. Random telegraph noise in Flash memories—Model and technology scaling. In Proceedings of the 2007 International Electron Devices Meeting, Washington, DC, USA, 10–12 December 2007; pp. 169–172.

- 22. Fantini, P.; Ghetti, A.; Marinoni, A.; Ghidini, G.; Visconti, A.; Marmiroli, A. Giant random telegraph signals in nanoscale floating-gate devices. *IEEE Electron Device Lett.* **2007**, *28*, 1114–1116. [CrossRef]

- Miki, H.; Osabe, T.; Tega, N.; Kotabe, A.; Kurata, H.; Tokami, K.; Ikeda, Y.; Kamohara, S.; Yamada, R. Quantitative analysis of random telegraph signals as fluctuations of threshold voltages in scaled Flash memory cells. In Proceedings of the 2007 IEEE International Reliability Physics Symposium Proceedings—45th Annual Phoenix, AZ, USA, 15–19 April 2007; pp. 29–35.

- Wong, H.S.; Taur, Y. Three-dimensional "atomistic" simulation of discrete random dopant distribution effects in sub-0.1 μm MOSFET's. In Proceedings of the IEEE International Electron Devices Meeting, Washington, DC, USA, 5–8 December 1993; pp. 705–708.

- Asenov, A. Random dopant induced threshold voltage lowering and fluctuations in sub-0.1 μm MOSFET's: A 3-D "atomistic" simulation study. *IEEE Trans. Electron Devices* 1998, 45, 2505–2513. [CrossRef]

- Asenov, A.; Brown, A.R.; Davies, J.H.; Saini, S. Hierarchical approach to "atomistic" 3-D MOSFET simulation. *IEEE Trans. Comput. Aided Des.* 1999, 18, 1558–1565. [CrossRef]

- 27. Asenov, A.; Saini, S. Suppression of random dopant-induced threshold voltage fluctuations in sub-0.1 μm MOSFET's with epitaxial and δ-doped channels. *IEEE Trans. Electron Devices* **1999**, *46*, 1718–1724. [CrossRef]

- Vandamme, L.K.J.; Sodini, D.; Gingl, Z. On the anomalous behavior of the relative amplitude of RTS noise. *Solid-State Electron*. 1998, 42, 901–905. [CrossRef]

- Asenov, A.; Balasubramaniam, R.; Brown, A.R.; Davies, J.H.; Saini, S. Random telegraph signal amplitudes in sub 100 nm (decanano) MOSFETs: A 3D "atomistic" simulation study. In Proceedings of the International Electron Devices Meeting, San Francisco, CA, USA, 10–13 December 2000; pp. 279–282.

- 30. Asenov, A.; Balasubramaniam, R.; Brown, A.R.; Davies, J.H. RTS amplitudes in decananometer MOSFETs: 3-D simulation study. *IEEE Trans. Electron Devices* 2003, *50*, 839–845. [CrossRef]

- Asenov, A.; Brown, A.R.; Davies, J.H.; Kaya, S.; Slavcheva, G. Simulation of intrinsic parameter fluctuations in decananometer and nanometer-scale MOSFETs. *IEEE Trans. Electron Devices* 2003, 50, 1837–1852. [CrossRef]

- 32. Monzio Compagnoni, C.; Gusmeroli, R.; Spinelli, A.S.; Lacaita, A.L.; Bonanomi, M.; Visconti, A. Statistical model for random telegraph noise in Flash memories. *IEEE Trans. Electron Devices* **2008**, *55*, 388–395. [CrossRef]

- 33. Ghetti, A.; Monzio Compagnoni, C.; Spinelli, A.S.; Visconti, A. Comprehensive analysis of random telegraph noise instability and its scaling in deca-nanometer Flash memories. *IEEE Trans. Electron Devices* **2009**, *56*, 1746–1752. [CrossRef]

- Monzio Compagnoni, C.; Castellani, N.; Mauri, A.; Spinelli, A.S.; Lacaita, A.L. Three-dimensional electrostatics- and atomistic doping-induced variability of RTN time constants in nanoscale MOS devices—Part II: Spectroscopic implications. *IEEE Trans. Electron Devices* 2012, 59, 2495–2500. [CrossRef]

- Castellani, N.; Monzio Compagnoni, C.; Mauri, A.; Spinelli, A.S.; Lacaita, A.L. Three-dimensional electrostatics- and atomistic doping-induced variability of RTN time constants in nanoscale MOS devices—Part I: Physical investigation. *IEEE Trans. Electron Devices* 2012, 59, 2488–2494. [CrossRef]

- Adamu-Lema, F.; Monzio Compagnoni, C.; Amoroso, S.M.; Castellani, N.; Gerrer, L.; Markov, S.; Spinelli, A.S.; Lacaita, A.L.; Asenov, A. Accuracy and issues of the spectroscopic analysis of RTN traps in nanoscale MOSFETs. *IEEE Trans. Electron Devices* 2013, 60, 833–839. [CrossRef]

- 37. Spinelli, A.S.; Monzio Compagnoni, C.; Lacaita, A.L. Random telegraph noise in Flash memories. In *Noise in Nanoscale Semiconductor Devices*; Grasser, T., Ed.; Springer: Berlin, Germany, 2020; Chapter 6, pp. 201–227.

- 38. Monzio Compagnoni, C.; Goda, A.; Spinelli, A.S.; Feeley, P.; Lacaita, A.L.; Visconti, A. Reviewing the evolution of the NAND Flash technology. *Proc. IEEE* 2017, *105*, 1609–1633. [CrossRef]

- Tanaka, H.; Kido, M.; Yahashi, K.; Oomura, M.; Katsumata, R.; Kito, M.; Fukuzumi, Y.; Sato, M.; Nagata, Y.; Matsuoka, Y.; et al. Bit cost scalable technology with punch and plug process for ultra high density Flash memory. In Proceedings of the 2007 IEEE Symposium on VLSI Technology, Kyoto, Japan, 12–14 June 2007; pp. 14–15.

- Fukuzumi, Y.; Katsumata, R.; Kito, M.; Kido, M.; Sato, M.; Tanaka, H.; Nagata, Y.; Matsuoka, Y.; Iwata, Y.; Aochi, H.; et al. Optimal integration and characteristics of vertical array devices for ultra-high density, bit-cost scalable Flash memory. In Proceedings of the International Electron Devices Meeting, San Francisco, CA, USA, 10–12 December 2007; pp. 449–452.

- Maeda, T.; Itagaki, K.; Hishida, T.; Katsumata, R.; Kito, M.; Fukuzumi, Y.; Kido, M.; Tanaka, H.; Komori, Y.; Ishiduki, M.; et al. Multi-stacked 1 G cell/layer pipe-shaped BiCS Flash memory. In Proceedings of the 2009 Symposium on VLSI Circuits, Kyoto, Japan, 16–18 June 2009; pp. 22–23.

- 42. Ishiduki, M.; Fukuzumi, Y.; Katsumata, R.; Kito, M.; Kido, M.; Tanaka, H.; Komori, Y.; Nagata, Y.; Fujiwara, T.; Maeda, T.; et al. Optimal device structure for pipe-shaped BiCS Flash memory for ultra high density storage device with excellent performance and reliability. In Proceedings of the 2009 IEEE International Electron Devices Meeting, Baltimore, MD, USA, 7–9 December 2009; pp. 625–628.

- 43. Katsumata, R.; Kito, M.; Fukuzumi, Y.; Kido, M.; Tanaka, H.; Komori, Y.; Ishiduki, M.; Matsunami, J.; Fujiwara, T.; Nagata, Y.; et al. Pipe-shaped BiCS Flash memory with 16 stacked layers and multi-level-cell operation for ultra high density storage devices. In Proceedings of the 2009 Symposium on VLSI Technology, Kyoto, Japan, 15–17 June 2009; pp. 136–137.

- Jang, J.; Kim, H.S.; Cho, W.; Cho, H.; Kim, J.; Shim, S.I.; Jang, Y.; Jeong, J.H.; Son, B.K.; Kim, D.W.; et al. Vertical cell array using TCAT (Terabit Cell Array Transistor) technology for ultra high density NAND Flash memory. In Proceedings of the 2009 Symposium on VLSI Technology, Kyoto, Japan, 15–17 June 2009; pp. 192–193.

- Kim, W.; Choi, S.; Sung, J.; Lee, T.; Park, C.; Ko, H.; Jung, J.; Yoo, I.; Park, Y. Multi-layered vertical gate NAND Flash overcoming stacking limit for terabit density storage. In Proceedings of the 2009 Symposium on VLSI Technology, Kyoto, Japan, 15–17 June 2009; pp. 188–189.

- Lue, H.T.; Chen, S.H.; Shih, Y.H.; Hsieh, K.Y.; Lu, C.Y. Overview of 3D NAND Flash and progress of vertical gate (VG) architecture. In Proceedings of the 2012 IEEE 11th International Conference on Solid-State and Integrated Circuit Technology, Xi'an, China, 29 October–1 November 2012; pp. 914–917.

- 47. Tanaka, T.; Helm, M.; Vali, T.; Ghodsi, R.; Kawai, K.; Park, J.K.; Yamada, S.; Pan, F.; Einaga, Y.; Ghalam, A.; et al. A 768Gb 3b/cell 3D-floating-gate NAND Flash memory. In Proceedings of the 2016 IEEE International Solid-State Circuits Conference, San Francisco, CA, USA, 31 January–4 February 2016; pp. 142–143.

- 48. Parat, K.; Goda, A. Scaling trends in NAND Flash. In Proceedings of the 2018 IEEE International Electron Devices Meeting, San Francisco, CA, USA, 1–5 December 2018; pp. 27–30.

- 49. Siau, C.; Kim, K.H.; Lee, S.; Isobe, K.; Shibata, N.; Verma, K.; Ariki, T.; Li, J.; Yuh, J.; Amarnath, A.; et al. A 512Gb 3-bit/cell 3D Flash memory on 128-wordline-layer with 132MB/s write performance featuring circuit-under-array technology. In Proceedings of the 2019 IEEE International Solid-State Circuits Conference, San Francisco, CA, USA, 17–21 February 2019; pp. 218–220.

- 50. Kim, D.H.; Kim, H.; Yun, S.; Song, Y.; Kim, J.; Joe, S.M.; Kang, K.H.; Jang, J.; Yoon, H.J.; Lee, K.; et al. A 1Tb 4 b/cell NAND Flash memory with *t*<sub>*PROG*</sub> = 2 ms, *t*<sub>*R*</sub> = 110 μs and 1.2 Gb/s high-speed IO rate. In Proceedings of the 2020 IEEE International Solid-State Circuits Conference, San Francisco, CA, USA, 16–20 February 2020.

- 51. Micheloni, R. (Ed.) 3D Flash Memories; Springer: Berlin, Germany, 2016.

- 52. Spinelli, A.S.; Monzio Compagnoni, C.; Lacaita, A.L. Reliability of NAND Flash memories: Planar cells and emerging issues in 3D devices. *Computers* **2017**, *6*, 16. [CrossRef]

- 53. Monzio Compagnoni, C.; Spinelli, A.S. Reliability of NAND Flash arrays: A review of what the 2-D-to-3-D transition meant. *IEEE Trans. Electron Devices* **2019**, *66*, 4504–4516. [CrossRef]

- 54. Goda, A. 3D NAND technology achievements and future scaling perspectives. *IEEE Trans. Electron Devices* **2020**, *67*, 1373–1381. [CrossRef]

- 55. Whang, S.; Lee, K.; Shin, D.; Kim, B.; Kim, M.; Bin, J.; Han, J.; Kim, S.; Lee, B.; Jung, Y.; et al. Novel 3-Dimensional dual control-gate with surrounding floating-gate (DC-SF) NAND Flash cell for 1Tb file storage application. In Proceedings of the 2010 International Electron Devices Meeting, San Francisco, CA, USA, 6–8 December 2010; pp. 668–671.

- 56. Noh, Y.; Ahn, Y.; Yoo, H.; Han, B.; Chung, S.; Shim, K.; Lee, K.; Kwak, S.; Shin, S.; Choi, I.; et al. A new metal control gate last process (MCGL process) for high performance DC-SF (dual control gate with surrounding floating gate) 3D NAND Flash memory. In Proceedings of the 2012 Symposium on VLSI Technology (VLSIT), Honolulu, HI, USA, 12–14 June 2012; pp. 19–20.

- 57. Aritome, S.; Whang, S.; Lee, K.; Shin, D.; Kim, B.; Kim, M.; Bin, J.; Han, J.; Kim, S.; Lee, B.; et al. A novel three-dimensional dual control-gate with surrounding floating-gate (DC-SF) NAND flash cell. *Solid-State Electron.* **2013**, *79*, 166–171. [CrossRef]

- 58. Aritome, S.; Noh, Y.; Yoo, H.; Choi, E.S.; Joo, H.S.; Ahn, Y.; Han, B.; Chung, S.; Shim, K.; Lee, K.; et al. Advanced DC-SF cell technology for 3-D NAND Flash. *IEEE Trans. Electron Devices* **2013**, *60*, 1327–1333. [CrossRef]

- 59. Parat, K.; Dennison, C. A floating gate based 3-D NAND technology with CMOS under array. In Proceedings of the 2015 IEEE International Electron Devices Meeting, Washington, DC, USA, 7–9 December 2015; pp. 48–51.

- 60. Sako, M.; Watanabe, Y.; Nakajima, T.; Sato, J.; Muraoka, K.; Fujiu, M.; Kouno, F.; Nakagawa, M.; Masuda, M.; Kato, K.; et al. A low-power 64 Gb MLC NAND-Flash memory in 15 nm CMOS technology. *IEEE J. Solid-State Circuits* **2015**, *51*, 128–129.

- 61. Park, K.T.; Nam, S.; Kim, D.; Kwak, P.; Lee, D.; Choi, Y.H.; Choi, M.H.; Kwak, D.H.; Kim, D.H.; Kim, M.S.; et al. Three-dimensional 128 Gb MLC vertical NAND Flash memory with 24-WL stacked layers and 50 MB/s high-speed programming. *IEEE J. Solid-State Circuits* **2015**, *50*, 204–213. [CrossRef]

- 62. Kang, D.; Jeong, W.; Kim, C.; Kim, D.H.; Cho, Y.S.; Kang, K.T.; Ryu, J.; Kang, K.M.; Lee, S.; Kim, W.; et al. 256 Gb 3 b/cell V-NAND Flash memory with 48 stacked WL layers. *IEEE J. Solid-State Circuits* **2016**, *52*, 210–217. [CrossRef]

- 63. Lee, S.; Lee, J.; Park, I.; Park, J.; Yun, S.; Kim, M.; Lee, J.; Kim, M.; Lee, K.; Kim, T.; et al. A 128 Gb 2 b/cell NAND Flash memory in 14nm technology with t<sub>PROG</sub> = 640 μs and 800 MB/s I/O rate. In Proceedings of the 2016 IEEE International Solid-State Circuits Conference, San Francisco, CA, USA, 31 January–4 February 2016; pp. 138–139.

- 64. Lee, S.; Kim, C.; Kim, M.; Joe, S.; Jang, J.; Kim, S.; Lee, K.; Kim, J.; Park, J.; Lee, H.J.; et al. A 1 Tb 4 b/cell 64-stacked-WL 3D NAND flash memory with 12 MB/s program throughput. In Proceedings of the 2018 IEEE International Solid-State Circuits Conference, San Francisco, CA, USA, 11–15 February 2018; pp. 340–342.

- 65. Seager, C.H. Grain boundaries in polycrystalline silicon. Ann. Rev. Mater. Sci. 1985, 15, 271–302. [CrossRef]

- 66. Jackson, W.B.; Johnson, N.M.; Biegelsen, D.K. Density of gap states of silicon grain boundaries determined by optical absorption. *Appl. Phys. Lett.* **1983**, *43*, 195–197. [CrossRef]

- 67. Werner, J.; Peisl, M. Exponential band tails in polycrystalline semiconductor films. Phys. Rev. B 1985, 31, 6681–6683. [CrossRef]

- 68. Fortunato, G.; Migliorato, P. Determination of gap state density in polycrystalline silicon by field-effect conductance. *Appl. Phys. Lett.* **1986**, *49*, 1025–1027. [CrossRef]

- 69. Evans, P.V.; Nelson, S.F. Determination of grain-boundary defect-state densities from transport measurements. *J. Appl. Phys.* **1991**, *69*, 3605–3611. [CrossRef]

- 70. Kimura, M.; Nozawa, R.; Inoue, S.; Shimoda, T.; Lui, B.O.K.; Tam, S.W.B.; Migliorato, P. Extraction of trap states at the oxide-silicon interface and grain boundary for polycrystalline silicon thin-film transistors. *Jpn. J. Appl. Phys.* 2001, 40, 5227–5236. [CrossRef]

- 71. Ikeda, H. Evaluation of grain boundary trap states in polycrystalline-silicon thin-film transistors by mobility and capacitance measurements. *J. Appl. Phys.* **2002**, *91*, 4637–4645. [CrossRef]

- 72. Hastas, N.A.; Tassis, D.H.; Dimitriadis, C.A.; Kamarinos, G. Determination of interface and bulk traps in the subthreshold region of polycrystalline silicon thin-film transistors. *IEEE Trans. Electron Devices* **2003**, *50*, 1991–1994. [CrossRef]

- 73. Kimura, M. Extraction of trap densities in entire bandgap of poly-Si thin-film transistors fabricated by solid-phase crystallization and dependence on process conditions of post annealing. *Solid-State Electron.* **2011**, *63*, 94–99. [CrossRef]

- 74. Wei, X.; Deng, W.; Fang, J.; Ma, X.; Huang, J. Determination of bulk and interface density of states in metal oxide semiconductor thin-film transistors by using capacitance–voltage characteristics. *Eur. Phys. J. Appl. Phys.* **2017**, *80*, 10103. [CrossRef]

- 75. Hack, M.; Shaw, J.G.; LeComber, P.G.; Willums, M. Numerical simulations of amorphous and polycrystalline silicon thin-film transistors. *Jpn. J. Appl. Phys.* **1990**, *29*, 2360–2362. [CrossRef]

- 76. Jacunski, M.D.; Shur, M.S.; Hack, M. Threshold voltage, field effect mobility, and gate-to-channel capacitance in polysilicon TFTs. *IEEE Trans. Electron Devices* **1996**, *43*, 1433–1440. [CrossRef]

- 77. Valdinoci, M.; Colalongo, L.; Baccarani, G.; Pecora, A.; Policicchio, I.; Fortunato, G.; Plais, F.; Legagneux, P.; Reita, C.; Priba, D. Analysis of electrical characteristics of polycrystalline silicon thin-film transistors under static and dynamic conditions. *Solid-State Electron.* **1997**, *41*, 1363–1369. [CrossRef]

- 78. Chow, T.; Wong, M. An analytical model for the transfer characteristics of a polycrystalline silicon thin-film transistor with a double exponential grain-boundary trap-state energy dispersion. *IEEE Electron Dev. Lett.* **2009**, *30*, 1072–1074. [CrossRef]

- 79. Amit, I.; Englander, D.; Horvitz, D.; Sasson, Y.; Rosenwaks, Y. Density and energy distribution of interface states in the grain boundaries of polysilicon nanowire. *Nano Lett.* **2014**, *14*, 6190–6194. [CrossRef]

- 80. Peisl, M.; Wieder, A.W. Conductivity in polycrystalline silicon—Physics and rigorous numerical treatment. *IEEE Trans. Electron Devices* **1983**, *30*, 1792–1797. [CrossRef]

- Kim, D.M.; Khondker, A.; Ahmed, S.S.; Shah, R.R. Theory of conduction in polysilicon: Drift-diffusion approach in crystallineamorphous-crystalline semiconductor system—Part I: Small signal theory. *IEEE Trans. Electron Devices* 1984, 31, 480–493. [CrossRef]

- Khondker, A.N.; Kim, D.M.; Ahmed, S.S.; Shah, R.R. Theory of conduction in polysilicon: Drift-diffusion approach in crystallineamorphous-crystalline semiconductor system—Part II: General I-V theory. *IEEE Trans. Electron Devices* 1984, 31, 493–500. [CrossRef]

- 83. Seto, J.Y.W. The electrical properties of polycrystalline silicon films. J. Appl. Phys. 1975, 46, 5247–5254. [CrossRef]

- 84. Baccarani, G.; Riccò, B.; Spadini, G. Transport properties of polycrystalline silicon films. *J. Appl. Phys.* **1978**, *49*, 5565–5570. [CrossRef]

- 85. Mandurah, M.M.; Saraswat, K.C.; Kamins, T.I. A model for conduction in polycrystalline silicon—Part I: Theory. *IEEE Trans. Electron Devices* **1981**, *28*, 1163–1171. [CrossRef]

- 86. Lu, N.C.C.; Gerzberg, L.; Lu, C.Y.; Meindl, J.D. Modeling and optimization of monolithic polycrystalline silicon resistors. *IEEE Trans. Electron Devices* **1981**, *28*, 818–830. [CrossRef]

- 87. Lee, J.Y.; Wang, F.Y. Temperature dependence of carrier trnsport in polycrystalline silicon. *Microelectron. J.* **1986**, *17*, 23–32. [CrossRef]

- Mannara, A.; Spinelli, A.S.; Lacaita, A.L.; Monzio Compagnoni, C. Current transport in polysilicon-channel GAA MOSFETs: A modeling perspective. In Proceedings of the 49th European Solid-State Device Research Conference (ESSDERC), Cracow, Poland, 23–26 September 2019; pp. 222–225.

- 89. Mannara, A.; Malavena, G.; Spinelli, A.S.; Monzio Compagnoni, C. A comparison of modeling approaches for current transport in polysilicon-channel nanowire and macaroni GAA MOSFETs. *J. Comp. Electr.* **2021**, *20*, 537–544. [CrossRef]

- 90. Hsiao, Y.H.; Lue, H.T.; Chen, W.C.; Chen, C.P.; Chang, K.P.; Shih, Y.H.; Tsui, B.Y.; Lu, C.Y. Modeling the variability caused by random grain boundary and trap-location induced asymmetrical read behavior for a tight-pitch vertical gate 3D NAND Flash memory using double-gate thin-film transistor (TFT) device. In Proceedings of the 2012 International Electron Devices Meeting, San Francisco, CA, USA, 10–13 December 2012; pp. 609–612.

- Hsiao, Y.H.; Lue, H.T.; Chen, W.C.; Chang, K.P.; Shih, Y.H.; Tsui, B.Y.; Hsieh, K.Y.; Lu, C.Y. Modeling the impact of random grain boundary traps on the electrical behavior of vertical gate 3-D NAND Flash memory devices. *IEEE Trans. Electron Devices* 2014, 61, 2064–2070. [CrossRef]

- 92. Yang, C.W.; Su, P. Simulation and investigation of random grain-boundary-induced variabilities for stackable NAND Flash using 3-D Voronoi grain patterns. *IEEE Trans. Electron Devices* **2014**, *61*, 1211–1214. [CrossRef]

- Kim, J.; Lee, J.; Oh, H.; Rim, T.; Baek, C.K.; Meyyappan, M.; Lee, J.S. The variability due to random discrete dopant and grain boundary in 3D NAND unit cell. In Proceedings of the 2014 IEEE International Nanoelectronics Conference (INEC), Sapporo, Japan, 28–31 July 2014; pp. 66–68.

- 94. Wang, P.Y.; Tsui, B.Y. A novel approach using discrete grain-boundary traps to study the variability of 3-D vertical-gate NAND Flash memory cells. *IEEE Trans. Electron Devices* **2015**, *62*, 2488–2493. [CrossRef]

- 95. Degraeve, R.; Clima, S.; Putcha, V.; Kaczer, B.; Roussel, P.; Linten, D.; Groeseneken, G.; Arreghini, A.; Karner, M.; Kernstock, C.; et al. Statistical poly-Si grain boundary model with discrete charging defects and its 2D and 3D implementation for vertical 3D NAND channels. In Proceedings of the 2015 IEEE International Electron Devices Meeting, Washington, DC, USA, 7–9 December 2015; pp. 121–124.

- Lun, Z.; Shen, L.; Cong, Y.; Du, G.; Liu, X.; Wang, Y. Investigation of the impact of grain boundary on threshold voltage of 3-D MLC NAND Flash memory. In Proceedings of the 2015 Silicon Nanoelectronics Workshop (SNW), Kyoto, Japan, 14–15 June 2015; pp. 35–37.

- 97. Oh, H.; Kim, J.; Lee, J.; Rim, T.; Baek, C.K.; Lee, J.S. Effects of single grain boundary and random interface traps on electrical variations of sub-30 nm polysilicon nanowire structures. *Microelectron. Eng.* **2016**, *149*, 113–116. [CrossRef]

- 98. Resnati, D.; Mannara, A.; Nicosia, G.; Paolucci, G.M.; Tessariol, P.; Lacaita, A.L.; Spinelli, A.S.; Monzio Compagnoni, C. Temperature activation of the string current and its variability in 3-D NAND Flash arrays. In Proceedings of the 2017 IEEE International Electron Devices Meeting, San Francisco, CA, USA, 2–6 December 2017; pp. 103–106.

- 99. Nicosia, G.; Mannara, A.; Resnati, D.; Paolucci, G.M.; Tessariol, P.; Lacaita, A.L.; Spinelli, A.S.; Goda, A.; Monzio Compagnoni, C. Inpact of temperature on the amplitude of RTN fluctuations in 3-D NAND Flash cells. In Proceedings of the 2017 IEEE International Electron Devices Meeting, San Francisco, CA, USA, 2–6 December 2017; pp. 521–524.

- 100. Resnati, D.; Mannara, A.; Nicosia, G.; Paolucci, G.M.; Tessariol, P.; Spinelli, A.S.; Lacaita, A.L.; Monzio Compagnoni, C. Characterization and modeling of temperature effects in 3-D NAND Flash arrays—Part I: Polysilicon-induced variability. *IEEE Trans. Electron Devices* 2018, 65, 3199–3206. [CrossRef]

- 101. Nicosia, G.; Mannara, A.; Resnati, D.; Paolucci, G.M.; Tessariol, P.; Spinelli, A.S.; Lacaita, A.L.; Goda, A.; Monzio Compagnoni, C. Characterization and modeling of temperature effects in 3-D NAND Flash arrays—Part II: Random telegraph noise. *IEEE Trans. Electron Devices* 2018, 65, 3207–3213. [CrossRef]

- 102. Verreck, D.; Arreghini, A.; Schanovsky, F.; Stanojević, Z.; Steiner, K.; Mitterbauer, F.; Karner, M.; den Bosch, G.V.; Furnémont, A. 3D TCAD model for poly-Si channel current and variability in vertical NAND Flash memory. In Proceedings of the 2019 International Conference on Simulation of Semiconductor Processes and Devices (SISPAD), Udine, Italy, 4–6 September 2019; pp. 61–64.

- 103. Degraeve, R.; Toledano-Luque, M.; Arreghini, A.; Tang, B.; Capogreco, E.; Lisoni, J.; Roussel, P.; Kaczer, B.; Van den bosch, G.; Groeseneken, G.; et al. Characterizing grain size and defect energy distribution in vertical SONOS poly-Si channels by means of a resistive network model. In Proceedings of the 2013 IEEE International Electron Devices Meeting, Washington, DC, USA, 9–11 December 2013; pp. 558–561.

- 104. Yoo, W.S.; Ishigaki, T.; Ueda, T.; Kang, K.; Kwak, N.Y.; Sheen, D.S.; Kim, S.S.; Ko, M.S.; Shin, W.S.; Lee, B.S.; et al. Grain size monitoring of 3D Flash memory channel poly-Si using multiwavelength Raman spectroscopy. In Proceedings of the 2014 14th Annual Non-Volatile Memory Technology Symposium (NVMTS), Jeju, Korea, 27–29 October 2014; pp. 44–47.

- 105. Kim, S.Y.; Park, J.K.; Hwang, W.S.; Lee, S.J.; Lee, K.H.; Pyi, S.H.; Cho, B.J. Dependence of grain size on the performance of a polysilicon channel TFT for 3D NAND Flash memory. *J. Nanosci. Nanotechnol.* **2016**, *16*, 5044–5048. [CrossRef] [PubMed]

- He, D.; Okada, N.; Fortmann, C.M.; Shimizu, I. Carrier transport in polycrystalline silicon films deposited by a layer-by-layer technique. *J. Appl. Phys.* 1994, *76*, 4728–4733. [CrossRef]

- 107. Walker, A.J.; Herner, S.B.; Kumar, T.; Chen, E.H. On the conduction mechanism in polycrystalline silicon thin-film transistors. *IEEE Trans. Electron Devices* 2004, *51*, 1856–1866. [CrossRef]

- 108. Jeong, M.K.; Joe, S.M.; Seo, C.S.; Han, K.R.; Choi, E.; Park, S.K.; Lee, J.H. Analysis of random telegraph noise and low frequency noise properties in 3-D stacked NAND Flash memory with tube-type poly-Si channel structure. In Proceedings of the 2012 Symposium on VLSI Technology (VLSIT), Honolulu, HI, USA, 12–14 June 2012; pp. 55–56.

- 109. Jeong, M.K.; Joe, S.M.; Jo, B.S.; Kang, H.J.; Bae, J.H.; Han, K.R.; Choi, E.; Cho, G.; Park, S.K.; Park, B.G.; et al. Characterization of traps in 3-D stacked NAND Flash memory devices with tube-type poly-Si channel structure. In Proceedings of the 2012 International Electron Devices Meeting, San Francisco, CA, USA, 10–13 December 2012.

- Kang, D.; Lee, C.; Hur, S.; Song, D.; Choi, J.H. A new approach for trap analysis of vertical NAND Flash cell using RTN characteristics. In Proceedings of the 2014 IEEE International Electron Devices Meeting, San Francisco, CA, USA, 15–17 December 2014; pp. 367–370.

- 111. Amoroso, S.M.; Monzio Compagnoni, C.; Ghetti, A.; Gerrer, L.; Spinelli, A.S.; Lacaita, A.L.; Asenov, A. Investigation of the RTN distribution of nanoscale MOS devices from subthreshold to on-state. *IEEE Electron Device Lett.* **2013**, *34*, 683–685. [CrossRef]

- 112. Saraza-Canflanca, P.; Martin-Martinez, J.; Castro-Lopez, R.; Roca, E.; Rodriguez, R.; Nafria, M.; Fernandez, F.V. A detailed study of the gate/drain voltage dependence of RTN in bulk pMOS transistors. *Microelectron. Eng.* **2019**, *215*, 111004. [CrossRef]

- 113. Spinelli, A.S.; Monzio Compagnoni, C.; Lacaita, A.L. Variability effects in nanowire and macaroni MOSFETs—Part II: Random telegraph noise. *IEEE Trans. Electron Devices* 2020, 67, 1492–1497. [CrossRef]

- 114. Andrade, M.; Toledano-Luque, M.; Fourati, F.; Degraeve, R.; Martino, J.; Claeys, C.; Simoen, E.; Van den bosch, G.; Van Houdt, J. RTN assessment of traps in polysilicon cylindrical vertical FETs for NVM application. *Microelectron. Eng.* 2013, 109, 105–108. [CrossRef]

- 115. Toledano-Luque, M.; Degraeve, R.; Roussel, P.J.; Luong, V.; Tang, B.; Lisoni, J.G.; Tan, C.L.; Arreghini, A.; Van den bosch, G.; Groeseneken, G.; et al. Statistical spectroscopy of switching traps in deeply scaled vertical poly-Si channel for 3D memories. In Proceedings of the 2013 IEEE International Electron Devices Meeting, Washington, DC, USA, 9–11 December 2013; pp. 562–565.

- 116. Lee, C.M.; Tsui, B.Y. Random telegraph signal noise arising from grain boundary traps in nano-scale poly-Si nanowire thin-film transistors. In Proceedings of the 2013 International Symposium on VLSI Technology, Systems and Application (VLSI-TSA), Hsinchu, Taiwan, 22–24 April 2013; pp. 47–48.

- 117. Nicosia, G.; Goda, A.; Spinelli, A.S.; Monzio Compagnoni, C. Investigation of the temperature dependence of random telegraph noise fluctuations in nanoscale polysilicon-channel 3-D Flash cells. *Solid-State Electron.* **2019**, 151, 18–22. [CrossRef]

- 118. Degraeve, R.; Toledano-Luque, M.; Suhane, A.; Van den bosch, G.; Arreghini, A.; Tang, B.; Kaczer, B.; Roussel, P.; Kar, G.S.; Van Houdt, J.; et al. Statistical characterization of current paths in narrow poly-Si channels. In Proceedings of the 2011 International Electron Devices Meeting, Washington, DC, USA, 5–7 December 2011; pp. 287–290.

- Nowak, E.; Kim, J.H.; Kwon, H.; Kim, Y.G.; Sim, J.S.; Lim, S.H.; Kim, D.S.; Lee, K.H.; Park, Y.K.; Choi, J.H.; et al. Intrinsic fluctuations in vertical NAND Flash memories. In Proceedings of the 2012 Symposium on VLSI Technology (VLSIT), Honolulu, HI, USA, 12–14 June 2012; pp. 21–22.

- 120. Toledano-Luque, M.; Degraeve, R.; Kaczer, B.; Tang, B.; Roussel, P.J.; Weckx, P.; Franco, J.; Arreghini, A.; Suhane, A.; Kar, G.S.; et al. Quantitative and predictive model of reading current variability in deeply scaled vertical poly-Si channel for 3D memories. In Proceedings of the 2012 International Electron Devices Meeting, San Francisco, CA, USA, 10–13 December 2012.

- Goda, A.; Miccoli, C.; Monzio Compagnoni, C. Time dependent threshold-voltage fluctuations in NAND Flash memories: From basic physics to impact on array operation. In Proceedings of the 2015 IEEE International Electron Devices Meeting, Washington, DC, USA, 7–9 December 2015; pp. 374–377.

- 122. Chou, Y.L.; Wang, T.; Lin, M.; Chang, Y.W.; Liu, L.; Huang, S.W.; Tsai, W.J.; Lu, T.C.; Chen, K.C.; Lu, C.Y. Poly-silicon trap position and pass voltage effects on RTN amplitude in a vertical NAND Flash cell string. *IEEE Electron Dev. Lett.* 2016, 37, 998–1001. [CrossRef]

- 123. Hsieh, C.C.; Lue, H.T.; Hsu, T.H.; Du, P.Y.; Chiang, K.H.; Lu, C.Y. A Monte Carlo simulation method to predict large-density NAND product memory window from small-array test element group (TEG) verified on a 3D NAND Flash test chip. In Proceedings of the 2016 IEEE Symposium on VLSI Technology, Honolulu, HI, USA, 14–16 June 2016; pp. 63–64.

- 124. Hung, C.H.; Lue, H.T.; Hung, S.N.; Hsieh, C.C.; Chang, K.P.; Chen, T.W.; Huang, S.L.; Chen, T.S.; Chang, C.S.; Yeh, W.W.; et al. Design innovations to optimize the 3D stackable vertical gate (VG) NAND Flash. In Proceedings of the 2012 International Electron Devices Meeting, San Francisco, CA, USA, 10–13 December 2012; pp. 227–230.

- 125. Resnati, D.; Goda, A.; Nicosia, G.; Miccoli, C.; Spinelli, A.S.; Monzio Compagnoni, C. Temperature effects in NAND Flash memories: A comparison between 2-D and 3-D arrays. *IEEE Electron Dev. Lett.* **2017**, *38*, 461–464. [CrossRef]

- 126. Nicosia, G.; Goda, A.; Spinelli, A.S.; Monzio Compagnoni, C. Impact of cycling on random telegraph noise in 3-D NAND Flash arrays. *IEEE Electron Dev. Lett.* 2018, 39, 1175–1178. [CrossRef]

- 127. Cappelletti, P. Non volatile memory evolution and revolution. In Proceedings of the 2015 IEEE International Electron Devices, Washington, DC, USA, 7–9 December 2015; pp. 241–244.

- 128. Miccoli, C.; Paolucci, G.M.; Monzio Compagnoni, C.; Spinelli, A.S.; Goda, A. Cycling pattern and read/bake conditions dependence of random telegraph noise in decananometer NAND Flash arrays. In Proceedings of the 2015 IEEE International Reliability Physics Symposium, Monterey, CA, USA, 19–23 April 2015; pp. MY.9.1–MY.9.4.

- 129. Monzio Compagnoni, C.; Spinelli, A.S.; Beltrami, S.; Bonanomi, M.; Visconti, A. Cycling effect on the random telegraph noise instabilities of NOR and NAND Flash arrays. *IEEE Electron Device Lett.* **2008**, *29*, 941–943. [CrossRef]

- 130. Monzio Compagnoni, C.; Gusmeroli, R.; Spinelli, A.S.; Lacaita, A.L.; Bonanomi, M.; Visconti, A. Statistical investigation of random telegraph noise *I<sub>D</sub>* instabilities in Flash cells at different initial trap-filling conditions. In Proceedings of the 2007 45th Annual IEEE International Reliability Physics Symposium Proceedings, Phoenix, AZ, USA, 15–19 April 2007; pp. 161–166.

- 131. Choi, N.; Kang, H.J.; Lee, J.H. Analysis of random telegraph noise characteristics with two different cell states in 3-D NAND Flash memory. *J. Semicond. Technol. Sci.* **2019**, *19*, 153–157. [CrossRef]