# Article Negative Capacitance Vacuum Channel Transistors for Low Operating Voltage

## Woo Young Choi

Department of Electronic Engineering, Sogang University, Seoul 04107, Korea; wchoi@sogang.ac.kr; Tel.: +82-2-715-8467

Received: 22 April 2020; Accepted: 27 May 2020; Published: 27 May 2020

**Abstract:** This study proposes negative capacitance vacuum channel transistors. The proposed negative capacitance vacuum channel transistors in which a ferroelectric capacitor is connected in series to the gate of the vacuum channel transistors have the following two advantages: first, adding a ferroelectric capacitor in series with a gate capacitor makes the turn-on voltage lower and on–off transition steeper without causing hysteresis effects. Second, the capacitance matching between a ferroelectric capacitor and a vacuum channel transistor becomes simplified because the capacitance of a vacuum channel transistor as seen from a ferroelectric capacitor is constant.

**Keywords:** negative capacitance; ferroelectric capacitor; capacitance matching; NC vacuum channel transistor; vacuum channel transistor; steep switching; hysteresis effects

## 1. Introduction

Over the past 60 years of the semiconductor industry, the size of metal-oxide-semiconductor field-effect transistors (MOSFETs) has been scaled down obeying Moore's law: feature sizes of transistors are scaled at a rate of approximately 0.7 times every 18 months. As the semiconductor market size increases, its applications extend beyond consumer electronics, extending, for example, to transistors, microchips, solar cells, and light-emitting diodes. Recently, electronic devices have faced burgeoning demand from aerospace and extreme-environment applications. For example, in the case of aerospace applications, many kinds of challenges from harsh environments exist. Extremely low and high temperature and high levels of cosmic ray and radiation lead to catastrophic damage to the electronic systems without proper shielding packages. Unfortunately, it is well-known that MOSFETs, which are the most widely used electronic devices, are difficult to use for these applications because they are vulnerable to radiation and temperature [1–11]. Even if state-of-the-art shielding methods can protect MOSFETs from harsh environments, the following issues still remain: large volume, large weight, high power consumption, and complex system design.

Thus, as an alternative, a vacuum channel transistor has been proposed, which replaces the semiconductor channel with a vacuum channel. Owing to the unique properties of a vacuum channel, vacuum channel transistors are robust even if they are exposed to radiation and high or low temperatures [12]. Furthermore, it is well-known that a vacuum environment is superior to a solid one in terms of carrier transport because ballistic transport is feasible in the former while the latter experiences various scattering mechanisms, such as lattice vibration scattering, ionized impurity scattering, surface roughness scattering, etc. [13]. For example, the electron velocities in vacuum and silicon are theoretically  $3 \times 10^{10}$  cm/s and  $\sim 10^7$  cm/s. Thus, vacuum channel transistors have the potential to implement higher performance and power gain than MOSFETs. In spite of the above-mentioned advantages, vacuum channel transistors experience a high operating voltage ( $V_{DD}$ ) [14], which is due to their current flowing mechanism: Fowler–Nordheim tunneling, where electrons tunnel through the barrier in the presence of a high electric field [15,16]. Because Fowler–Nordheim tunneling makes

electrons tunnel through a rounded triangular barrier generated at the source-to-channel junction, electrons tunnel from the source tip into the vacuum channel with a positive drain voltage ( $V_D$ ) when the gate voltage ( $V_G$ ) exceeds the turn-on voltage. In the case of the optimized vacuum channel transistors, an insulated-gate structure with a pyramidal source and a flat drain is introduced to boost the on-current ( $I_{on}$ ) and gate controllability by increasing the local electric field [17,18]. However, despite the optimization and downscaling of vacuum channel transistors, their  $V_{DD}$  is still higher than that of MOSFETs, which makes them hard to utilize in low-power extreme-environment applications.

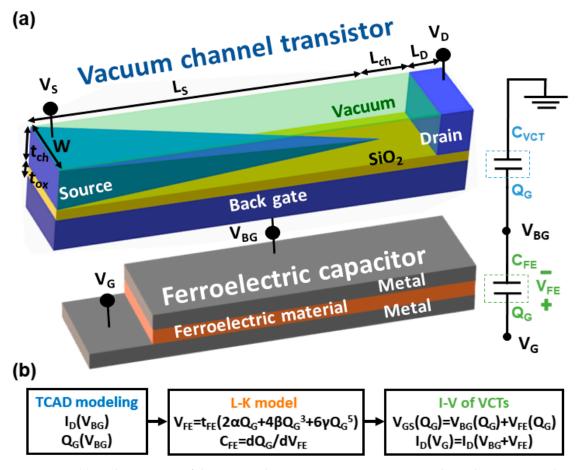

In this paper, for a low  $V_{DD}$ , a negative capacitance vacuum channel transistor is proposed for the first time, as shown in Figure 1a. The gate of a vacuum channel transistor is connected to a ferroelectric capacitor to combine the advantages of vacuum channel transistors with negative capacitance. The negative capacitance effects of ferroelectric materials have recently been exploited to induce internal voltage gain out of the gate stack [19]. The underlying physics for an abrupt on-off switching operation of a negative capacitance transistor is the passive amplification of the gate voltage at the interface between the FE gate oxide and the semiconductor channel. Essentially, the charge balance between the series-connected ferroelectric and linear positive capacitor induces a depolarization field and stabilizes the ferroelectric capacitor at a negative capacitance state that in turn amplifies the surface potential of the electron device. It has been reported that there are two important aspects of a negative capacitance transistor: amplification and stabilization. The differential amplification of the gate voltage at the interface between the surface channel and the gate oxide makes the on-off transition of a negative capacitance transistor more abrupt. On the other hand, negative capacitance is unstable by nature. Thus, the positive capacitances can stabilize the ferroelectric in its negative capacitance state, leading to a stable voltage amplification. Conventionally, a metallic layer is located between the gate and vacuum channel transistor to average out the nonuniform potential profile along the source-drain direction and the charge nonuniformity coming from domain formation in the ferroelectric. It makes the single-domain Landau–Khalatnikov (LK) equation valid. The influence of the internal voltage gain stemming from negative capacitance has also been recently confirmed in the case of polymer ferroelectric bulk MOSFETs [20–23], negative capacitance finFETs [24–26], and negative capacitance nanoelectromechanical (NEM) relays [27]. This manuscript is the first application of negative capacitance to vacuum channel transistors whose channel is vacuum rather than semiconductor.

The proposed negative capacitance vacuum channel transistors have the following two benefits: first, adding a ferroelectric capacitor in series with a gate dielectric capacitor makes the turn-on voltage lower and on-off transition more abrupt without causing unwanted hysteresis effects. Second, the capacitance matching between a ferroelectric capacitor and a vacuum channel transistor is simplified because the capacitance of a vacuum channel transistor as seen from a ferroelectric capacitor is constant. When a vacuum channel transistor is connected to ferroelectric materials, the capacitance matching between the ferroelectric-layer ( $C_{FE}$ ) and the vacuum channel transistor ( $C_{VCT}$ ) is important. As capacitance matching is improved, the subthreshold swing (SS) and transconductance of vacuum channel transistors improve, which leads to a lower  $V_{\text{DD}}$  [28]. For the optimized matching condition,  $C_{\rm VCT}^{-1} + C_{\rm FE}^{-1}$  needs to be made as small as possible while maintaining positive values for all charges to minimize SS and avoiding hysteresis effects:  $C_{VCT}$  ( $Q_G$ )<sup>-1</sup>  $\ge -C_{FE}$  ( $Q_G$ )<sup>-1</sup> [20], where  $Q_G$  is the gate charge. However, in the case of MOSFETs, their gate capacitance is dependent on bias conditions, which makes the capacitance matching of negative capacitance MOSFETs difficult [29]. For example, as V<sub>G</sub> increases, the gate capacitance of n-channel MOSFETs increases nonlinearly from the subthreshold to a strong inversion. In contrast, the capacitance matching of negative capacitance vacuum channel transistors is expected to be simplified and stable because there is no semiconductor channel region. The ferroelectric capacitor in standalone condition cannot show the negative capacitance behavior because to stabilize the total system, it is necessary to introduce a series combination of a ferroelectric capacitor and a linear positive capacitor connected to a voltage source. The C<sub>VCT</sub> remains constant regardless of the  $Q_G$ , because the  $Q_G$  of the vacuum channel transistors increases linearly with the

increment of the back-gate voltage ( $V_{BG}$ ). The advantages of negative capacitance vacuum channel transistors are discussed in detail in the following section.

**Figure 1.** (a) Bird's eye view of the proposed negative capacitance vacuum channel transistor and its equivalent capacitor network model. The channel length ( $L_{ch}$ ), source length ( $L_S$ ), drain length ( $L_D$ ), and width (W) are 10 nm, 200 nm, 10 nm, and 30 nm, respectively. (b) Simulation procedure of negative capacitance vacuum channel transistors combining technology computer-aided design (TCAD) simulation results with the Landau–Khalatnikov (LK) equation.

### 2. Simulation Method

Figure 1b summarizes the simulation procedure of the negative capacitance vacuum channel transistors. First, the drain current ( $I_D$ ) and  $Q_G$  of vacuum channel transistors are calculated as a function of  $V_{BG}$  using a commercial three-dimensional technology computer-aided design (TCAD) simulator [30]. The simulation models include band-to-band tunneling, Fowler–Nordheim tunneling, Fermi distribution, Shockley-Read-Hall (SRH) recombination, and dynamic nonlocal tunneling models. HfSiO and SiO<sub>2</sub> are used as ferroelectric and gate dielectric materials, respectively. The work function of the back-gate, source, and drain is 4.32 eV, which corresponds to that of tungsten. The physical parameters of the simulated negative capacitance vacuum channel transistors are as follows: the channel ( $t_{ch}$ ) and oxide thickness ( $t_{ox}$ ) are 15 nm and 5 nm, respectively. The source length ( $L_S$ ), channel length ( $L_{ch}$ ), and channel width ( $W_{ch}$ ) are 200 nm, 10 nm, and 30 nm, respectively. Parasitic capacitance components of vacuum channel transistors are included in the TCAD simulation, while the leakage through the ferroelectric layer is ignored for concise discussion. Second, to derive the voltage drop ( $V_{FE}$ ) and capacitance ( $C_{FE}$ ) across the ferroelectric capacitor, the LK equation is coupled with TCAD simulation using Equations (1) and (2) [20].

$$C_{\rm FE} = dQ_{\rm G}/dV_{\rm FE} = 1/t_{\rm FE} \left( \alpha_0 Q_{\rm G} + 3\beta_0 Q_{\rm G}^2 + 5\gamma_0 Q_{\rm G}^4 \right)$$

(2)

where  $\alpha_0$ ,  $\beta_0$ , and  $\gamma_0$  refer to the Landau coefficients of HfSiO ( $\alpha_0 = -1.73 \times 10^9 \text{ m/F}$ ,  $\beta_0 = 7.68 \times 10^{10} \text{ m}^5/\text{F/C}^2$ , and  $\gamma_0 = 0 \text{ m}^9/\text{F/C}^4$ , as presented in [31]). The value of  $\alpha_0$  is negative for all known ferroelectric materials below Curie temperature, which leads to hysteretic characteristics of ferroelectrics. It shows the double-well shape of free energy for negative capacitance behavior of ferroelectric capacitors.  $t_{\text{FE}}$  is the ferroelectric layer thickness. Equations (1) and (2) calculate  $V_{\text{FE}}$  and  $C_{\text{FE}}$  by using  $Q_{\text{G}}$  values obtained in the first step. Finally, the calculated  $V_{\text{FE}}$  is added to  $V_{\text{BG}}$  to obtain  $V_{\text{G}}$ , as shown in Figure 1a. Then, simulated  $I_{\text{D}}$  vs.  $V_{\text{G}}$  and  $I_{\text{D}}$  vs.  $V_{\text{D}}$  curves of negative capacitance vacuum channel transistors are generated.

### 3. Simulation Results

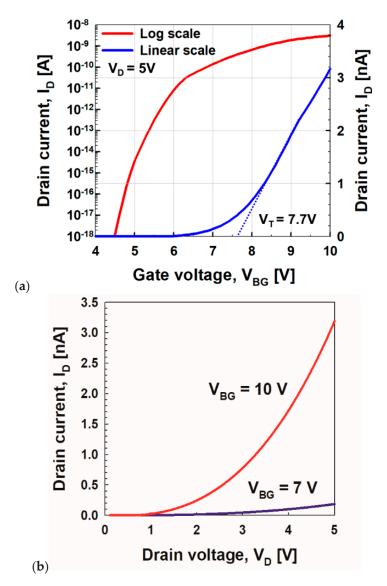

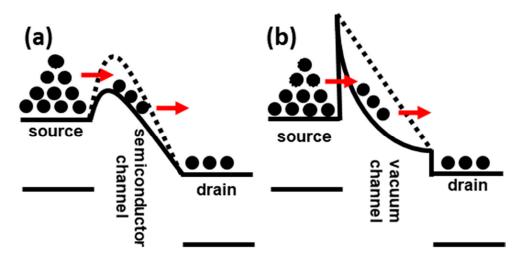

Figure 2 shows the  $I_{\rm D}$  vs.  $V_{\rm BG}$  and  $I_{\rm D}$  vs.  $V_{\rm D}$  curves of a vacuum channel transistor, which corresponds to negative capacitance vacuum channel transistors without ferroelectric capacitors. The output curves in Figure 2b show the typical current vs. voltage characteristics of Fowler-Nordheim tunneling. Thus,  $V_{\rm BG}$  rather than  $V_{\rm G}$  controls the vacuum channel transistor. As previously reported, the dominant carrier transport mechanisms of vacuum channel transistors are Fowler-Nordheim tunneling and thermionic emission [13], as shown in Figure 3. In the case of vacuum channel transistors, the semiconductor channel is replaced with a vacuum channel. In the case of MOSFETs, carriers stored in the source region are injected into the semiconductor channel region by lowering the energy barrier height using the  $V_{\rm G}$ . Then, the carriers move from the source into the semiconductor channel using thermionic emission: high-energy carriers following the Fermi–Dirac distribution are injected over the energy barrier. Subsequently, the carriers move along the channel while experiencing scattering events, which are described by a carrier mobility. On the contrary, in the case of vacuum channel transistors, the carriers stored in the source need to overcome the energy barrier between the source and vacuum channel. Fowler-Nordheim tunneling is a more viable option than thermionic emission, because the vacuum level is significantly higher than the energy level of the semiconductor. Once the  $V_{\rm BG}$  is high enough to narrow the source-to-channel barrier width, the source carriers begin to be injected into the channel region. After the injection, the carriers drift through the channel into the drain without experiencing scattering events analogous to ballistic transport in extremely short-channel semiconductor MOSFETs. During this process, vacuum channel transistors generally experience a high  $V_{\rm DD}$ . For efficient source carrier injection, the electric field or energy band bending near the source-to-channel junction must be increased. To meet this condition, the source tip is sharpened, as shown in Figure 1a, and a multiple-gate structure is introduced. However, these geometrical approaches are insufficient to obtain a dramatic reduction in V<sub>DD</sub> and SS. Thus, the introduction of a ferroelectric capacitor is helpful for alleviating the weal spots of vacuum channel transistors.

**Figure 2.** Simulated (**a**) drain current ( $I_D$ ) vs. back-gate voltage ( $V_{BG}$ ) and (**b**)  $I_D$  vs. drain voltage ( $V_D$ ) without ferroelectric capacitors.

**Figure 3.** Energy band diagrams of a (**a**) metal-oxide-semiconductor field-effect transistors (MOSFET) and (**b**) vacuum channel transistor. The carrier transport mechanism of a MOSFET is thermionic emission, while that of a vacuum channel transistor is Fowler–Nordheim tunneling, respectively.

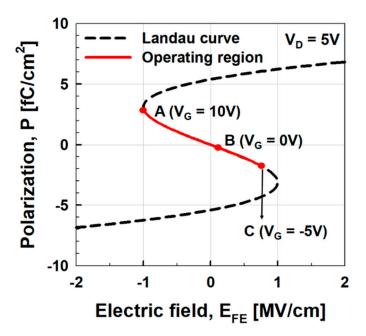

In Figure 2, the threshold voltage ( $V_{\rm T}$ ) extracted by the linear extrapolation method is ~7.7 V at  $V_{\rm D} = 5$  V. Even if  $V_{\rm G}$  increases up to 10 V,  $I_{\rm D}$  only reaches ~3 nA per source tip. Then, ferroelectric materials such as HfSiO are connected in series with the back-gate stack of negative capacitance vacuum channel transistors whose polarization (P) vs. electric field across a ferroelectric layer ( $E_{\rm FE}$ ) curve is shown in Figure 4. On the Landau curve, the operating points corresponding to  $V_{\rm D} = 5$  V and  $V_{\rm G} = -5-10$  V are shown. If the operating point is located at A, it lowers the gate voltage ( $V_{\rm G} = V_{\rm BG} + V_{\rm FE}$ ) required to reach the same value of  $I_{\rm D}$ . This leads to a higher  $I_{\rm on}$  and lower turn-on voltage. At operating point B,  $E_{FE}$  is still positive, which means that  $V_{\rm BG}$  is negative even when  $V_{\rm G} = 0$  V. This leads to a lower off-current ( $I_{\rm off}$ ).

**Figure 4.** Polarization (*P*) vs. electric field ( $E_{\text{FE}}$ ) of the ferroelectric material, HfSiO. Solid line shows the operating regions of negative capacitance vacuum channel transistors. Points A, B, and C represent position on Landau curve for  $V_{\text{G}}$  = 10 V, 0 V, and -5 V, while  $V_{\text{D}}$  is fixed at 5 V.

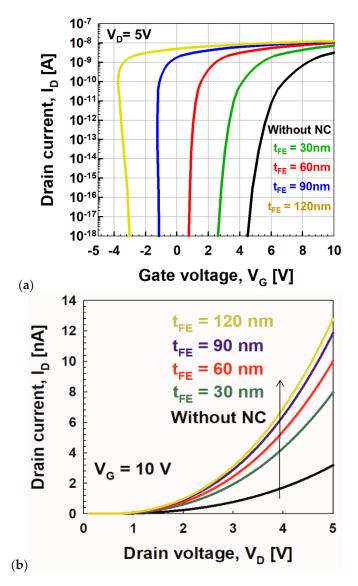

Figure 5 shows the influence of the ferroelectric capacitor on the transfer and output curves of negative capacitance vacuum channel transistors with the variation of  $t_{\text{FE}}$ . This clearly shows the performance boosting of negative capacitance vacuum channel transistors as  $t_{\text{FE}}$  increases. The surface potential of vacuum channel transistors can be higher than the applied  $V_{\text{G}}$ , resulting in negative capacitance effects of the ferroelectric material. As  $t_{\text{FE}}$  increases, turn-on voltage decreases,  $I_{\text{on}}$  increases, and *SS* improves. Among the values of  $t_{\text{FE}}$ , 60 nm is considered to be an optimal value because minimal *SS* is achieved without hysteresis effects, whereas turn-on voltage is <1 V. If  $t_{\text{FE}}$  exceeds 60 nm, the hysteresis operation featuring S-shaped transfer curves becomes more pronounced.

**Figure 5.** Simulated (**a**)  $I_D$  vs.  $V_G$  and (**b**)  $I_D$  vs.  $V_D$  curves of negative capacitance vacuum channel transistors for various ferroelectric thicknesses ( $t_{FE}$  = 30 nm, 60 nm, 90 nm, and 120 nm). The S-shape of thicker than 60-nm-thick ferroelectric-HfSiO indicates the hysteresis behavior.

#### 4. Discussion

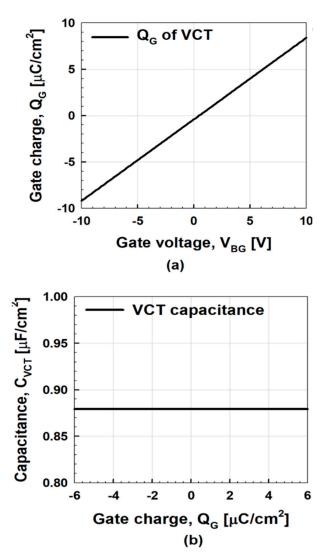

For more detailed analysis, Figure 6a,b shows  $Q_G$  vs.  $V_{BG}$  and  $C_{VCT}$  vs.  $Q_G$  of vacuum channel transistors. It should be noted that  $C_{VCT}$  remains constant regardless of bias conditions unlike negative capacitance MOSFETs. Although  $C_{FE}$  is a nonlinear function of  $Q_G$ , it can be matched with  $C_{VCT}$  around zero  $Q_G$ . It means that perfect capacitance matching between  $C_{VCT}$  and  $C_{FE}$  is easier in the case of negative capacitance vacuum channel transistors than negative capacitance MOSFETs: minimizing *SS* without causing hysteresis effects as shown in Figure 7a,b. Considering the equivalent capacitance model in Figure 1a, the body factor (*m*) of negative capacitance vacuum channel transistors can be expressed as [19]

$$m = 1 + \frac{C_{\rm VCT}}{C_{\rm FE}} = \frac{C_{\rm VCT}^{-1} - \left(-C_{\rm FE}^{-1}\right)}{C_{\rm VCT}^{-1}} \tag{3}$$

which determines the coupling between the  $C_{VCT}$  and  $C_{FE}$ . For the minimization of *m* without hysteresis effects, the following two requirements must be met: first, total capacitance ( $C_{total}$ ) should remain positive in the entire range of operation;  $C_{total}^{-1} = C_{FE}^{-1} + C_{VCT}^{-1} \ge 0$ , which means

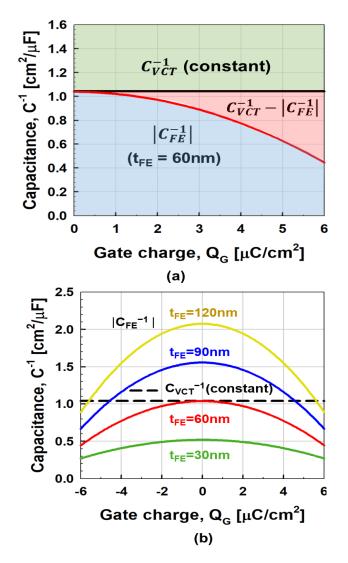

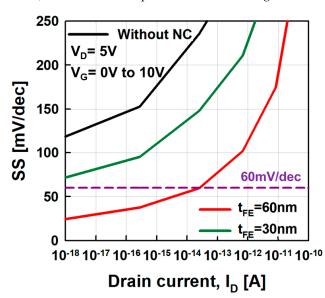

$C_{\text{VCT}}^{-1} \ge -C_{\text{FE}}^{-1}$  [22]. Second,  $C_{\text{total}}^{-1}$  should be made as small as possible [20]. As shown in Figure 7a, as  $C_{\text{VCT}}^{-1}$ , which is independent of  $Q_{\text{G}}$ , decreases down to  $C_{\text{FE}}^{-1}$ , the gap between  $C_{\text{VCT}}^{-1}$  and  $C_{\text{FE}}^{-1}$  becomes narrower, which leads to a reduced *SS*. For example, in Figure 7a, the value of  $C_{\text{VCT}}^{-1}$  is constant:  $1.04 \text{ cm}^2/\mu\text{F}$ . In contrast, when  $V_{\text{G}}$  is 0.4 V and  $t_{\text{FE}}$  is 60 nm, the value of  $-C_{\text{FE}}^{-1}$  is  $1.03 \text{ cm}^2/\mu\text{F}$ . This implies that m = 0 is feasible by adjusting  $t_{\text{FE}}$ . Thus, Figure 5 shows that the increase in  $I_{\text{D}}$  is steepest near  $V_{\text{G}} = 0.4 \text{ V}$  when  $t_{\text{FE}}$  is optimized to 60 nm. Figure 7b shows the relationship between  $C_{\text{VCT}}^{-1} |C_{\text{FE}}^{-1}|$  and  $Q_{\text{G}}$  with the variation of  $t_{\text{FE}}$ . As  $t_{\text{FE}}$  becomes greater than 60 nm,  $-C_{\text{FE}}^{-1}$  exceeds  $C_{\text{VCT}}^{-1}$  near  $Q_{\text{G}} = 0$ , making two intersections, which lead to hysteresis effects or the S shape of the transfer curves. On the contrary, if  $t_{\text{FE}}$  becomes less than 60 nm, and  $-C_{\text{FE}}^{-1}$  becomes less than  $C_{\text{VCT}}^{-1}$  for all QGs. Even if no hysteresis effect is observed, *SS* reduction is limited. Figure 8 shows the *SS* vs.  $I_{\text{D}}$  curves under the three  $t_{\text{FE}}$  conditions. As  $t_{\text{FE}}$  increases, *SS* decreases. If  $I_{\text{D}}$  is fixed at  $10^{-9}$  nA, *SS* becomes 118 mV/dec, 74 mV/dec, and 25 mV/dec at  $t_{\text{FE}} = 0$  nm, 30 nm, and 60 nm, respectively. As shown in Figure 5, the 60-nm- $t_{\text{FE}}$  case shows minimal *SS* without causing hysteresis effects.

**Figure 6.** (a)  $V_{BG}$  vs.  $Q_G$  and (b) vacuum channel transistor ( $C_{VCT}$ ) vs.  $Q_G$  of vacuum channel transistors.

**Figure 7.** Comparison of vacuum channel transistor capacitance vs. ferroelectric capacitance as function of  $Q_{\rm G}$  for (**a**) ferroelectric thickness ( $t_{\rm FE}$ ) is 60 nm, and (**b**) various ferroelectric thicknesses ( $t_{\rm FE}$  = 30 nm, 60 nm, 90 nm, and 120 nm). The calculated capacitances are according LK model.

**Figure 8.** *SS* as a function of  $V_{\rm G}$  for different  $t_{\rm FE}$  (0 nm, 30 nm, and 60 nm).

## 5. Conclusions

In this paper, the low-voltage operation of negative capacitance vacuum channel transistors are simulated using the unique property of ferroelectric materials. In addition, a negative capacitance effect is achieved for abrupt on–off transition without causing hysteresis effects through capacitance matching to stabilize the total system. The ferroelectric capacitor can amplify the  $V_{BG}$ , the *SS* can be lowered, and the  $I_D$  vs.  $V_G$  curve steepens. The operation voltage can be lowered below 1 V at the 60-nm thickness HfSiO without showing hysteresis behavior. The  $Q_G$  of the vacuum channel transistor is constantly increased as  $V_{BG}$  increases, and  $C_{VCT}$  is constant as  $Q_G$  increases. Thus, the negative capacitance vacuum channel transistor capacitance and ferroelectric capacitance. Therefore, the *SS* characteristic is better because the difference between  $C_{VCT}^{-1}$  and  $-C_{FE}^{-1}$  is reduced compared to the solid-state device with fluctuating gate capacitance. Thus, the *SS* of the negative capacitance vacuum channel transistor could be approximately 20 mV/dec. In this paper, the negative capacitance vacuum channel transistor has been proven to be an important position in industrial applications.

**Funding:** This work was supported in part by the NRF of Korea funded by the MSIT under Grant NRF-2019M3F3A1A02072089 (Intelligent Semiconductor Technology Development Program), NRF-2018R1A2A2A05019651 (Mid-Career Researcher Program), NRF-2015M3A7B7046617 (Fundamental Technology Program), NRF-2016M3A7B4909668 (Nano-Material Technology Development Program), in part by the IITP funded by the MSIT under Grant IITP-2020-2018-0-01421 (Information Technology Research Center Program), in part by the MOTIE/KSRC under Grant 10080575 (Technology Innovation Program) and in part by the IDEC (IC Design Education Center), Korea.

Conflicts of Interest: The authors declare no conflict of interest.

## References

- Swift, G.M.; Allen, G.R.; Tseng, C.W.; Carmichael, C.; Miller, G.; George, J.S. Static Upset Characteristics of the 90 nm Virtex-4QV FPGAs. In Proceedings of the IEEE Radiation Effects Data Workshop (REDW), Tucson, AZ, USA, 14–18 July 2008; pp. 98–105.

- 2. Gregory, A. Virtex-4QV Static SEU Characterization Summary. In *NASA Electronic Parts and Packaging;* National Aeronautics and Space Administration: Washington, DC, USA, 2008.

- 3. Gregory, A.; Larry, E.; Chen, W.T.; Gary, S.; Carl, C. Error Detect and Correct Enabled Block Random Access Memory (Block RAM) Within the Xilinx XQR5VFX130. *IEEE Trans. Nucl. Sci.* **2010**, *57*, 3426–3431.

- 4. Muñoz-Quijada, M.; Sanchez-Barea, S.; Vela-Calderon, D.; Guzman-Miranda, H. Fine-Grain Circuit Hardening Through VHDL Datatype Substitution. *Electronics* **2019**, *8*, 24. [CrossRef]

- 5. Duzellier, S. Radiation effects on electronic devices in Space. Aerosp. Sci. Technol. 2005, 9, 93–99. [CrossRef]

- 6. Cai, C.; Fan, X.; Liu, J.; Li, D.; Liu, T.; Ke, L.; Zhao, P.; He, Z. Heavy-ion induced single event upsets in advanced 65 nm radiation hardened FPGAs. *Electronics* **2019**, *8*, 323. [CrossRef]

- 7. Paul, L. Radiation Tolerant Electronics. *Electronics* **2019**, *8*, 730.

- Kuwahara, T.; Tomioka, Y.; Fukuda, K.; Sugimura, N.; Sakamoto, Y. Radiation effect mitigation methods for electronic systems. In Proceedings of the 2012 IEEE/SICE International Symposium on System Integration (SII), Fukuoka, Japan, 16–18 December 2012; pp. 307–312.

- 9. Selčan, D.; Kirbiš, G.; Kramberger, I. Nanosatellites in LEO and beyond: Advanced Radiation protection techniques for COTS-based spacecraft. *Acta Astronaut*. **2017**, *131*, 131–144. [CrossRef]

- Furano, G.; Tavoularis, A.; Santos, L.; Ferlet-Cavrois, V.; Boatella, C.; Garcia Alia, R.; Fernandez Martinez, P.; Kastriotou, M.; Wyrwoll, V.; Danzeca, S.; et al. FPGA SEE Test with Ultra-High Energy Heavy Ions. In Proceedings of the 2018 IEEE International Symposium on Defect and Fault Tolerance in VLSI and Nanotechnology Systems (DFT), Chicago, IL, USA, 8–10 October 2018; pp. 1–4.

- 11. Zhou, X.; Jia, Y.; Hu, D.; Wu, Y. A simulation-based comparison between Si and SiC MOSFETs on single-event burnout susceptibility. *IEEE Trans. Electron Devices* **2019**, *66*, 2551–2556. [CrossRef]

- 12. Han, J.; Moon, D.; Meyyappan, M. Nanoscale vacuum channel transistor. *Nano Lett.* **2017**, *17*, 2146–2151. [CrossRef]

- 13. Srisonphan, S.; Jung, Y.S.; Kim, H.K. Metal–oxide–semiconductor field-effect transistor with a vacuum channel. *Nat. Nanotechnol.* **2012**, *7*, 504. [CrossRef]

- 14. Han, J.; Oh, J.S.; Meyyappan, M. Cofabrication of vacuum field emission transistor (VFET) and MOSFET. *Appl. Phys. Lett.* **2014**, *13*, 464–468. [CrossRef]

- 15. Heeger, A.J.; Parker, I.D.; Yang, Y. Carrier injection into semiconducting polymers: Fowler-Nordheim field-emission tunneling. *Synth. Met.* **1994**, *67*, 23–29. [CrossRef]

- 16. Murphy, E.L.; Good, R. Thermionic emission, field emission, and the transition region. *Phys. Rev.* **2016**, *102*, 1464. [CrossRef]

- 17. Han, J.; Oh, J.S.; Meyyappan, M. Vacuum nanoelectronics: Back to the future?—Gate insulated nanoscale vacuum channel transistor. *Appl. Phys. Lett.* **2012**, *13*, 213505. [CrossRef]

- 18. Kim, J.; Kim, J.; Oh, H.; Meyyappan, M.; Han, J.W.; Lee, J.-S. Design guidelines for nanoscale vacuum field emission transistors. *J. Vac. Sci. Technol. B Microelectron.* **2016**, *34*, 042201. [CrossRef]

- 19. Salahuddin, S.; Datta, S. Use of negative capacitance to provide voltage amplification for low power nanoscale devices. *Nano Lett.* **2008**, *8*, 405–410. [CrossRef]

- 20. Jain, A.; Alam, M.A. Stability constraints define the minimum subthreshold swing of a negative capacitance field-effect transistor. *IEEE Trans. Electron Devices* **2014**, *61*, 2235–2242. [CrossRef]

- 21. Rusu, A.; Salvatore, G.A.; Jiménez, D.; Ionescu, A.M. Metal-ferroelectric-meta-oxide-semiconductor field effect transistor with sub-60mV/decade subthreshold swing and internal voltage amplification. In Proceedings of the International Electron Device Meeting (IEDM), San Francisco, CA, USA, 6–8 December 2010.

- 22. Khan, A.I.; Yeung, C.W.; Hu, C.; Salahuddin, S. Ferroelectric negative capacitance MOSFET: Capacitance tuning & antiferroelectric operation. In Proceedings of the International Electron Device Meeting (IEDM), Washington, DC, USA, 5–7 December 2011.

- 23. Jo, J.; Choi, W.Y.; Park, J.-D.; Shim, J.W.; Yu, H.-Y.; Shin, C. Negative capacitance in organic/ferroelectric capacitor to implement steep switching MOS devices. *Nano Lett.* **2015**, *15*, 4553–4556. [CrossRef]

- 24. Ko, E.; Lee, H.; Goh, Y.; Jeon, S.; Shin, C. Sub-60-mV/decade negative capacitance FinFET with sub-10-nm hafnium-based ferroelectric capacitor. *IEEE J. Electron Devices Soc.* **2017**, *5*, 306–309. [CrossRef]

- 25. Ko, E.; Lee, J.W.; Shin, C. Negative capacitance FinFET with sub-20-mV/decade subthreshold slope and minimal hysteresis of 0.48 V. *IEEE Electron Device Lett.* **2017**, *38*, 418–421. [CrossRef]

- Khan, A.I.; Chatterjee, K.; Duarte, J.P.; Lu, Z.; Sachid, A.; Khandelwal, S.; Ramesh, R.; Hu, C.; Salahuddin, S. Negative capacitance in short channel finFETs externally connected to an epitaxial ferroelectric capacitor. *IEEE Electron Device Lett.* 2016, *37*, 111–114. [CrossRef]

- 27. Choe, K.; Shin, C. Adjusting the operating voltage of an nanoelectromechanical relay using negative capacitance. *IEEE Trans. Electron Devices* **2017**, *64*, 5270–5273. [CrossRef]

- Agarwal, H.; Kushwaha, P.; Duarte, J.P.; Lin, Y.-K.; Sachid, A.B.; Kao, M.-Y.; Chang, H.-L.; Salahuddin, S.; Hu, C. Engineering negative differential resistance in NCFETs for analog applications. *IEEE Trans. Electron Devices* 2018, 65, 2033–2039. [CrossRef]

- Agarwal, H.; Kushwaha, P.; Lin, Y.; Kao, M.; Liao, Y.; Dasgupta, A.; Salahuddin, S.; Hu, C. Proposal for capacitance matching in negative capacitance field-effect transistors. *IEEE Electron Device Lett.* 2019, 40, 463–466. [CrossRef]

- 30. Synopsys, Inc. Sentaurus Device User Guide; Synopsys, Inc.: Mountain View, CA, USA, 2018.

- 31. Lee, M.H.; Fan, S.-T.; Tang, C.-H.; Chen, P.-G.; Chou, Y.-C.; Chen, H.-H.; Kuo, J.-Y.; Xie, M.-J.; Liu, S.-N.; Liao, M.-H.; et al. Physical thickness 1.x nm ferroelectric HfZrOx negative capacitance FETs. In Proceedings of the International Electron. Device Meeting (IEDM), San Francisco, CA, USA, 3–7 December 2016.

© 2020 by the author. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).