# Article Melt Blown Fiber-Assisted Solvent-Free Device Fabrication at Low-Temperature

Minjong Lee<sup>1</sup>, Joohoon Kang<sup>2,\*</sup> and Young Tack Lee<sup>1,\*</sup>

- <sup>1</sup> Department of Electrical and Computer Engineering, Inha University, Incheon 22212, Korea; ydr8273@inha.edu

- <sup>2</sup> School of Advanced Materials Science and Engineering, Sungkyunkwan University (SKKU), Suwon 16419, Korea

- \* Correspondence: joohoon@skku.edu (J.K.); ytlee@inha.ac.kr (Y.T.L.)

Received: 30 November 2020; Accepted: 9 December 2020; Published: 10 December 2020

**Abstract:** In this paper, we propose a solvent-free device fabrication method using a melt-blown (MB) fiber to minimize potential chemical and thermal damages to transition-metal-dichalcogenides (TMDCs)-based semiconductor channel. The fabrication process is composed of three steps; (1) MB fibers alignment as a shadow mask, (2) metal deposition, and (3) lifting-up MB fibers. The resulting WSe<sub>2</sub>-based p-type metal-oxide-semiconductor (PMOS) device shows an ON/OFF current ratio of ~2 × 10<sup>5</sup> (ON current of ~-40  $\mu$ A) and a remarkable linear hole mobility of ~205 cm<sup>2</sup>/V·s at a drain voltage of -0.1 V. These results can be a strong evidence supporting that this MB fiber-assisted device fabrication can effectively suppress materials damage by minimizing chemical and thermal exposures. Followed by an MoS<sub>2</sub>-based n-type MOS (NMOS) device demonstration, a complementary MOS (CMOS) inverter circuit application was successfully implemented, consisted of an MoS<sub>2</sub> NMOS and a WSe<sub>2</sub> PMOS as a load and a driver transistor, respectively. This MB fiber-based device fabrication can be a promising method for future electronics based on chemically reactive or thermally vulnerable materials.

**Keywords:** solvent-free lithography; transition metal dichalcogenides; melt blown fiber; micro-scaled shadow mask; complementary metal-oxide-semiconductor

## 1. Introduction

Microfabrication techniques have been persistently developed as industrial standards increase for high-performance next-generation electronic device applications. Photolithography has been a commonly used method for the spatially precise patterning process in the integrated circuit (IC) technology. Although this conventional photolithography can provide high-resolution patterns, process complexity and high-cost equipment should be involved. Furthermore, several steps incorporated with solvent and thermal exposure, such as photoresist (PR) coating, curing, and developing, can cause detrimental effects to fully exploit intrinsic properties of semiconductors. In order to overcome the limitations, soft lithography has been considered, as promising alternatives have many advantages, such as low-cost, low-temperature processable, and chemical-free methods [1,2]. Although the PR-based patterning steps are not involved during the soft-lithography process, which can avoid chemical and thermal exposure, poor electrical contacts between metal-semiconductor junctions are still remaining as a challenge. Beyond the electronic device fabrications, chemical and thermal exposure-free approaches are desired in the field of display. To handle chemically sensitive organic materials for organic-light-emitting diode fabrication, a chemical-free fabrication process is highly demanded to minimize potential chemical reaction of organic materials. In an effort to find solutions to overcome such limitations,

several approaches have been introduced, including inkjet printing [3], fine-metal-shadow masking [4,5], and microcontact-printing [6].

In a decade, two-dimensional (2D) van der Waals semiconductors such as transition-metaldichalcogenides (TMDCs) have been intensively studied to fully exploit their superlative electronic properties [7–10]. For example, MoS<sub>2</sub> and WSe<sub>2</sub> as semiconducting members of TMDCs have been extensively studied with great possibilities for future electronics within high-speed [11], flexible [12], and immune short channel effects in the device, which scale down [13]. Similar to the other semiconductors, however, the photolithography process also causes electrical property degradations of such semiconductors, due to solvent-induced chemical reactions and/or thermal degradation [14,15]. Furthermore, securing a clean interface between the source/drain (S/D) electrodes and a TMDCs channel layer is another significant issue towards high-performance device demonstrations [16–19]. Here, we report a melt blown (MB) fiber-assisted solvent-free lithography method for fabrication of field-effect transistors (FETs). The resulting electrical behaviors of TMDCs-based FETs are thoroughly compared with those of devices fabricated using a conventional photolithography process.

#### 2. Materials and Methods

TMDCs-based FETs were fabricated on a thermally oxidized 285 nm-thick  $SiO_2/p^+$  silicon substrate. Silicon substrate was ultrasonically cleaned by sequentially immersing in acetone, methyl alcohol, and isopropyl alcohol each for 15 min. Polydimethylsiloxane (PDMS) stamps were used to exfoliate and transfer 2D semiconductor active channels to a designated place. To fabricate PDMS stamps, base resin and cross-linker (Sylgard 184, Dow Corning) solutions were mixed with a 10:1 volume ratio, and trapped-air bubbles were removed by degassing in a vacuum for 20 min. The solution was then poured onto a cleaned silicon wafer mold and thermally cured on a hot plate in ambient condition at 423 K for 1 h.

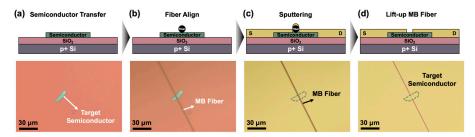

Figure 1 shows a non-lithographic micro-scaled device fabrication process using an MB fiber-based shadow mask. First of all, 2D TMDC semiconductors were mechanically exfoliated and transferred on a silicon substrate by a PDMS-based direct imprinting method, as shown in Figure 1a. In Figure 1b, an MB fiber-based shadow mask was aligned and subsequently transferred onto a targeted TMDC nanoflake under an optical microscope (OM) to define micropatterned S/D electrodes. The MB fiber-based shadow mask consisted of a punched PDMS frame and a selected MB fiber with an average diameter of  $\sim 1.5 \,\mu m$ . The suspending MB fiber was attached on the bottom side of the punched PDMS stamp (see Figure S1 with further details of MB fiber-based shadow mask technique in the Supplementary Materials (SM) section). The MB fiber could be efficiently attached at the 2D TMDC semiconductors on a silicon substrate due to its strong electrostatic force. Figure 1c,d shows a metal S/D electrodes patterning using a DC magnetron sputtering system, and we named this process as the "lift-up" method. By lifting-up the MB fiber-based shadow mask, a narrow gap between S/D electrodes (channel length) was formed with a distance corresponding to the diameter of a used MB fiber. This method is a straightforward way to form micro-scaled S/D electrodes without PR-casting and thermal curing process, and it can effectively reduce the whole process steps and the cost compared to the conventional photolithography. Based on this approach, WSe<sub>2</sub> and the MoS<sub>2</sub>-based PMOS and NMOS devices were fabricated with Pt (50 nm) and Ti/Au (25 nm/25 nm) as S/D electrodes, respectively.

**Figure 1.** The non-lithographic micro-scaled device fabrication flow steps; (**a**) 2D transition-metaldichalcogenides (TMDC) transferring on the silicon substrate; (**b**) melt-blown (MB) fiber alignment on the target TMDC nanoflake; (**c**) metal sputtering; (**d**) lifting-up MB fiber for S/D electrodes formation.

#### 3. Results and Discussion

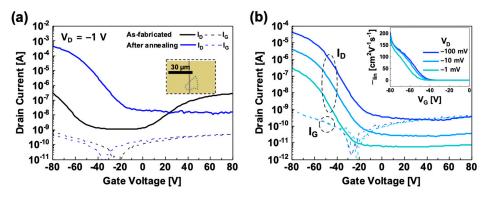

Figure 2 shows drain current-gate voltage ( $I_D$ - $V_G$ ) transfer characteristic curves of a WSe<sub>2</sub>-based PMOS transistor. As shown in Figure 2a, the as-fabricated WSe<sub>2</sub> PMOS shows an ambipolar behavior, and both drain ON current ( $I_{ON}$ ) levels in p-type and n-type regions ( $I_{ON,p}$  and  $I_{ON,n}$ ) were ~0.3 µA at a drain voltage ( $V_D$ ) of -1 V (black line). After a post-annealing process (423 K for 1 h in ambient air), the WSe<sub>2</sub> PMOS shows a strong p-type property, while the n-type characteristic is suppressed (blue line). The thermally annealed WSe<sub>2</sub> PMOS shows excellent  $I_{ON,p}$  of ~-0.4 mA at  $V_D$  of -1 V, which is ~10<sup>3</sup> times higher  $I_{ON,p}$  than the as-fabricated device at the same bias conditions. It implies that the post-annealing process in an ambient condition forms an atomically thin tungsten oxides ( $WO_x$ ) layer, having a p-type electrical characteristic on the surface of WSe<sub>2</sub> nanoflake, and it can be understood as a p-doping process at the WSe<sub>2</sub> channel surface [20–23]. Figure 2b shows  $I_D$ - $V_G$  transfer characteristic curves and linear mobility ( $\mu_{lin}$ ) plot (inset) at  $V_D$  of -1 mV, -10 mV, and -100 mV. The  $\mu_{lin}$  was calculated by using the following equation:

$$\mu_{lin} = \left(\frac{dI_D}{dV_G}\right) \left(\frac{L}{WC_{OX}|V_D|}\right)$$

where,  $C_{OX}$  is the capacitance of SiO<sub>2</sub> gate insulator, W and L are the width and the length of the FET channel, respectively. From this equation, the maximum linear mobility ( $\mu_{lin,max}$ ) of our WSe<sub>2</sub> PMOS was calculated as ~205 cm<sup>2</sup>/V·s at  $V_D$  of -100 mV. Moreover, another WSe<sub>2</sub> PMOS also showed excellent  $\mu_{lin,max}$  of ~244 cm<sup>2</sup>/V·s, as shown in Figure S2 in Supplementary Materials. As shown in Figure 2b, the  $I_D$  of our WSe<sub>2</sub> PMOS is proportionally increased by the  $V_D$  variation. This result can be a strong evidence that our non-lithographic fabrication method provides a high-quality Ohmic contact between the WSe<sub>2</sub> and Pt S/D electrodes. As a result, we can successfully achieve the high-performance WSe<sub>2</sub> PMOS device with excellent  $\mu_{lin,max}$ .

**Figure 2.** (a) Transfer characteristic curves of the WSe<sub>2</sub> p-type metal-oxide-semiconductor (PMOS) before (as-fabricated) and after the post-annealing process at  $V_D$  of -1 V (W/L = 10); (b) Transfer characteristic curves and linear mobility plot (inset) of the post-annealed WSe<sub>2</sub> PMOS at  $V_D$  of -1 mV, -10 mV, and -100 mV.

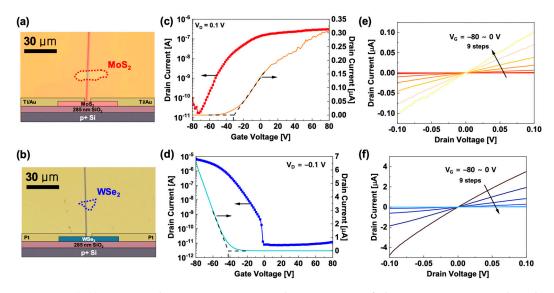

In addition to the WSe<sub>2</sub>-based PMOS device, an n-type MoS<sub>2</sub> nanoflake-based NMOS device was investigated in a similar manner. Figure 3a,b shows schematics of device structures and OM images of an MoS<sub>2</sub> NMOS and an annealed WSe<sub>2</sub> PMOS on 285 nm-thick SiO<sub>2</sub>/p<sup>+</sup> silicon substrate, respectively. Figure 3c,d show  $I_D$ - $V_G$  transfer characteristics of each device. The scattered symbol and solid line display the semi-logarithmic and linear  $I_D$ , respectively. The MoS<sub>2</sub> NMOS shows  $I_{ON}/I_{OFF}$  ratio of ~2 × 10<sup>4</sup>, a threshold voltage ( $V_{th}$ ) of ~-32.6 V, and  $I_{ON}$  of ~0.3 µA at  $V_D$  = 0.1 V, while the WSe<sub>2</sub> PMOS shows higher  $I_{ON}/I_{OFF}$  ratio of ~10<sup>6</sup>,  $V_{th}$  of ~-42.1 V and higher  $I_{ON}$  of ~-6.5 µA at  $V_D$  = -0.1 V. Figure 3e,f show the  $I_D$ - $V_D$  output characteristic curves of the MoS<sub>2</sub> NMOS and WSe<sub>2</sub> PMOS for a  $V_G$  range of -80 V to 0 V with +10 V step increment. Both output curves clearly show excellent ohmic contact behaviors of the MoS<sub>2</sub>/Ti-Au contact and the WSe<sub>2</sub>/Pt contact within the linear operation region.

**Figure 3.** (**a**,**b**) Device schematic structures and OM images of the MoS<sub>2</sub> n-type metal-oxidesemiconductor (NMOS) and the WSe<sub>2</sub> PMOS; (**c**,**d**) Transfer characteristic curves of the MoS<sub>2</sub> NMOS and the WSe<sub>2</sub> PMOS; (**e**,**f**) Output characteristic curves of the MoS<sub>2</sub> NMOS and the WSe<sub>2</sub> PMOS, respectively.

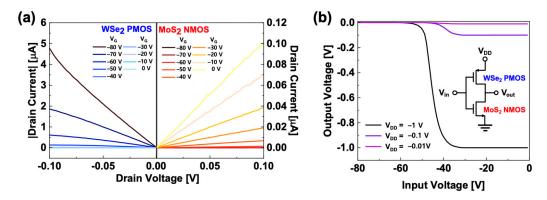

Based on the PMOS and NMOS devices, a CMOS inverter circuit application was implemented, and  $I_D$ - $V_D$  output characteristics curves of PMOS and NMOS FETs are displayed in Figure 4a (see Figure S3 with further details of load-line analysis in the Supplementary Materials section). The MoS<sub>2</sub> NMOS and WSe<sub>2</sub> PMOS were used as a load and a driver transistor, respectively, because the MoS<sub>2</sub> NMOS and WSe<sub>2</sub> PMOS showed negative  $V_{th}$ . Moreover, the WSe<sub>2</sub> PMOS had better electrical performances, such as higher  $I_D$  and linear hole mobility, than those of the MoS<sub>2</sub> NMOS device. Figure 4b shows the voltage transfer characteristic (VTC) curves of our CMOS inverter circuit device, and the transition voltage is ~-42 V, which is well-matched with  $V_{th}$  of WSe<sub>2</sub> PMOS driver transistor. The inset of Figure 4b shows our CMOS inverter circuit diagram by connecting with the MoS<sub>2</sub> NMOS and WSe<sub>2</sub> PMOS through an Au wire-bonding technique. To the best of our knowledge, this is the first demonstration of a 2D nanomaterial-based CMOS inverter circuit application through fully dried fabrication processes.

**Figure 4.** (a) Output characteristics curves of the WSe<sub>2</sub> field-effect transistors (FET) (driver) and MoS<sub>2</sub> FET (load) for complementary metal-oxide-semiconductor (CMOS) inverter circuit application; (b) VTC curves of our CMOS inverter circuit device at  $V_{DD}$  of -0.01 V, -0.1 V, and -1 V. The inset is the circuit diagram.

## 4. Conclusions

We demonstrated a solvent-free device fabrication method using an MB fiber-based shadow mask to minimize high-temperature and/or solvent-induced chemical degradation of semiconducting materials. This process effectively reduces the entire process protocols and the cost compared to the conventional photolithography. Moreover, the pattern size is easily tunable based on the diameter of the MB fiber (~1.5 µm). As a result, our WSe<sub>2</sub> PMOS shows excellent electrical performances, such as  $\mu_{lin,max}$  of 205 cm<sup>2</sup>/V·s,  $I_{ON}$  of ~-40 µA, and  $I_{ON}/I_{OFF}$  ratio of ~2 × 10<sup>5</sup> at  $V_D = -0.1$  V, because this approach provides a high-quality interface between the semiconductor active channel and the metal S/D electrode. Lastly, we successfully achieved the CMOS inverter circuit demonstrations consisted of a WSe<sub>2</sub> PMOS as a driver and an MoS<sub>2</sub> NMOS as a load transistor. This micro-scaled shadow masking process exhibits a promising key technique to unlock the unlimited potential of materials for future advanced electronics.

**Supplementary Materials:** The following are available online at http://www.mdpi.com/2072-666X/11/12/1091/s1, Figure S1: MB fiber-based shadow masking technique, Figure S2: Transfer characteristic curves and linear mobility plot of another WSe<sub>2</sub> PMOS, Figure S3: The load-line analysis for CMOS inverter circuit.

**Author Contributions:** Conceptualization, J.K. and Y.T.L.; experiment, M.L.; data analysis, M.L. and Y.T.L.; writing—original draft preparation, M.L., J.K., and Y.T.L.; writing—review and editing, M.L., J.K., and Y.T.L.; supervision, J.K. and Y.T.L. All authors have read and agreed to the published version of the manuscript.

Funding: This research was funded by Inha University, Grant INHA-63025-01.

Conflicts of Interest: The authors declare no conflict of interest.

### References

- 1. Xia, Y.; Whitesides, G.M. Soft Lithography. Angew. Chem. Int. Ed. 1998, 37, 550–575. [CrossRef]

- 2. Qin, D.; Xia, Y.; Whitesides, G.M. Soft lithography for micro- and nanoscale patterning. *Nat. Protoc.* **2010**, *5*, 491–502. [CrossRef] [PubMed]

- 3. Sirringhaus, H.; Kawase, T.; Friend, R.H.; Shimoda, T.; Inbasekaran, M.; Wu, W.; Woo, E.P. High-Resolution Inkjet Printing of All-Polymer Transistor Circuits. *Science* **2000**, *290*, 2123–2126. [CrossRef] [PubMed]

- 4. Noguchi, Y.; Sekitani, T.; Someya, T. Printed shadow masks for organic transistors. *Appl. Phys. Lett.* 2007, *91*, 133502. [CrossRef]

- 5. Muyres, D.V.; Baude, P.F.; Theiss, S.; Haase, M.; Kelley, T.W. Polymeric aperture masks for high performance organic integrated circuits. *J. Vac. Sci. Technol. A* **2004**, *22*, 1892. [CrossRef]

- 6. Briseno, A.L.; Mannsfeld, S.C.B.; Ling, M.M.; Liu, S.; Tseng, R.J.; Reese, C.; Roberts, M.E.; Yang, Y.; Wudl, F.; Bao, Z. Patterning organic single-crystal transistor arrays. *Nature* **2006**, 444, 913–917. [CrossRef]

- 7. Yin, C.; Wang, X.; Chen, Y.; Li, D.; Lin, T.; Sun, S.; Shen, H.; Du, P.; Sun, J.; Meng, X.; et al. A ferroelectric relaxor polymer-enhanced p-type WSe<sub>2</sub> transistor. *Nanoscale* **2018**, *10*, 1727–1734. [CrossRef]

- 8. Allain, A.; Kis, A. Electron and Hole Mobilities in Single-Layer WSe<sub>2</sub>. ACS Nano 2014, 8, 7180–7185. [CrossRef]

- 9. Movva, H.C.P.; Rai, A.; Kang, S.; Kim, K.; Fallahazad, B.; Taniguchi, T.; Watanabe, K.; Tutuc, E.; Banerjee, S.K. High-Mobility Holes in Dual-Gated WSe<sub>2</sub> Field-Effect Transistors. *ACS Nano* **2015**, *9*, 10402–10410. [CrossRef]

- 10. Fang, H.; Chuang, S.; Chang, T.C.; Takei, K.; Takahashi, T.; Javey, A. High-Performance Single Layered WSe<sub>2</sub> p-FETs with Chemically Doped Contacts. *Nano Lett.* **2012**, *12*, 3788–3792. [CrossRef]

- Krasnozhon, D.; Lembke, D.; Nyffeler, C.; Leblebici, Y.; Kis, A. MoS<sub>2</sub> Transistors Operating at Gigahertz Frequencies. *Nano Lett.* 2014, 14, 5905–5911. [CrossRef] [PubMed]

- 12. Desai, S.B.; Seol, G.; Kang, J.-S.; Fang, H.; Battaglia, C.; Kapadia, R.; Ager, J.W.; Guo, J.; Javey, A. Strain-Induced Indirect to Direct Bandgap Transition in Multilayer WSe<sub>2</sub>. *Nano Lett.* **2014**, *14*, 4592–4597. [CrossRef] [PubMed]

- Liu, H.; Neal, A.T.; Ye, P.D. Channel Length Scaling of MoS<sub>2</sub> MOSFETs. ACS Nano 2012, 10, 8563–8569. [CrossRef] [PubMed]

- 14. Yun, H.; Lee, S.; Jung, D.; Lee, G.; Park, J.; Kwan, O.J.; Lee, D.J.; Park, C.Y. Removal of photoresist residues and healing of defects on graphene using H<sub>2</sub> and CH<sub>4</sub> plasma. *Appl. Surf. Sci.* **2019**, *463*, 802–808. [CrossRef]

- Liang, J.; Xu, K.; Toncini, B.; Bersch, B.; Jariwala, B.; Lin, Y.C.; Robinson, J.; Fullerton-Shirey, S.K. Impact of Post-Lithography Polymer Residue on the Electrical Characteristics of MoS<sub>2</sub> and WSe<sub>2</sub> Field Effect Transistors. *Adv. Mater. Interfaces* 2019, 6, 1801321. [CrossRef]

- Liu, H.; Si, M.; Najmaei, S.; Neal, A.T.; Du, Y.; Ajayan, P.M.; Lou, J.; Ye, P.D. Statistical Study of Deep Submicron Dual-Gated Field-Effect Transistors on Monolayer Chemical Vapor Deposition Molybdenum Disulfide Films. *Nano Lett.* 2013, *13*, 2640–2646. [CrossRef]

- 17. Das, S.; Chen, H.-Y.; Penumatcha, A.V.; Appenzeller, J. High Performance Multilayer MoS<sub>2</sub> Transistors with Scandium Contacts. *Nano Lett.* **2013**, *13*, 100–105. [CrossRef]

- Xu, Y.; Cheng, C.; Du, S.; Yang, J.; Yu, B.; Luo, J.; Yin, W.; Li, E.; Dong, S.; Ye, P.; et al. Contacts between Two- and Three-Dimensional Materials: Ohmic, Schottky, and p–n Heterojunctions. *ACS Nano* 2016, 10, 4895–4919. [CrossRef]

- Allain, A.; Kang, J.; Banerjee, K.; Kis, A. Electrical contacts to two-dimensional semiconductors. *Nat. Mater.* 2005, 14, 1195–1205. [CrossRef]

- Seo, J.; Cho, K.; Lee, W.; Shin, J.; Kim, J.-K.; Kim, J.; Pak, J.; Lee, T. Effect of Facile p-Doping on Electrical and Optoelectronic Characteristics of Ambipolar WSe<sub>2</sub> Field-Effect Transistors. *Nanoscale Res. Lett.* 2019, 14, 313. [CrossRef]

- Liu, B.; Ma, Y.; Zhang, A.; Chen, L.; Abbas, A.N.; Liu, Y.; Shen, C.; Wan, H.; Zhou, C. High-Performance WSe<sub>2</sub> Field-Effect Transistors via Controlled Formation of In-Plane Heterojunctions. *ACS Nano* 2016, 10, 5153–5160. [CrossRef] [PubMed]

- Yamamoto, M.; Dutta, S.; Aikawa, S.; Nakaharai, S.; Wakabayashi, K.; Fuhrer, M.S.; Ueno, K.; Tsukagoshi, K. Self-Limiting Layer-by-Layer Oxidation of Atomically Thin WSe<sub>2</sub>. *Nano Lett.* 2015, *15*, 2067–2073. [CrossRef] [PubMed]

- 23. Yamamoto, M.; Nakaharai, S.; Ueno, K.; Tsukagoshi, K. Self-Limiting Oxides on WSe<sub>2</sub> as Controlled Surface Acceptors and Low-Resistance Hole Contacts. *Nano Lett.* **2016**, *16*, 2720–2727. [CrossRef] [PubMed]

**Publisher's Note:** MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations.

© 2020 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).