Article

# Design and Investigation of the High Performance Doping-Less TFET with Ge/Si<sub>0.6</sub>Ge<sub>0.4</sub>/Si Heterojunction

Tao Han, Hongxia Liu \*D, Shupeng Chen \*, Shulong Wang and Wei Li

Key Laboratory for Wide-Bandgap Semiconductor Materials and Devices of Education, The School of Microelectronics, Xidian University, Xi'an 710071, China; taohan 373@gmail.com (T.H.); slwang@xidian.edu.cn (S.W.); li20101467@163.com (W.L.)

\* Correspondence: hxliu@mail.xidian.edu.cn (H.L.); spchen@xidian.edu.cn (S.C.)

Received: 10 June 2019; Accepted: 24 June 2019; Published: 24 June 2019

**Abstract:** A high performance doping-less tunneling field effect transistor with  $Ge/Si_{0.6}Ge_{0.4}/Si$  heterojunction (H-DLTFET) is proposed in this paper. Compared to the conventional doping-less tunneling field effect transistor (DLTFET), the source and channel regions of H-DLTFET respectively use the germanium and  $Si_{0.6}Ge_{0.4}$  materials to get the steeper energy band, which can also increase the electric field of source/channel tunneling junction. Meanwhile, the double-gate process is used to improve the gate-to-channel control. In addition, the effects of Ge content, electrode work functions, and device structure parameters on the performance of H-DLTFET are researched in detail, and then the above optimal device structure parameters can be obtained. Compared to the DLTFET, the simulation results show that the maximum on-state current, trans-conductance, and output current of H-DLTFET are all increased by one order of magnitude, whereas the off-state current is reduced by two orders of magnitude, so the switching ratio increase by three orders of magnitude. At the same time, the cut-off frequency and gain bandwidth product of H-DLTFET increase from 1.75 GHz and 0.23 GHz to 23.6 GHz and 4.69 GHz, respectively. Therefore, the H-DLTFET is more suitable for the ultra-low power integrated circuits.

**Keywords:** DLTFET; on-state current; subthreshold swing; frequency characteristics

## 1. Introduction

The performance of integrated circuits (ICs) has been greatly improved with the size of the metal oxide semiconductor field effect transistors (MOSFETs) continues to decrease, while the MOSFETs are more susceptible to the short channel effects and quantum effects [1–3]. The MOSFETs based on the physical mechanism of thermal electron excitation have the subthreshold swing (SS) limit of 60 mV/Dec, the smaller switching ratio, the higher off-state current and the larger power consumption at room temperature, which cannot meet the requirements of the ultra-low power ICs [4,5]. The performance and power consumption of the MOSFETs are severely degraded when the threshold voltage of the device is reduced [6]. Therefore, it is necessary to explore the new low-power electronic devices with the smaller SS and higher switching ratio.

In recent years, many scholars have conducted extensive research on various new materials, new structures, and new physical mechanisms of device work [7–9]. Different from the MOSFETs, the working mechanism of tunneling field effect transistors (TFETs) is based on the quantum effect of electron Band-To-Band Tunneling (BTBT). The TFETs have the lower off-state leakage current, higher robustness of the short channel effect and faster switching speed, which is compatible with CMOS processes [10,11]. The TFET can break the SS limit of 60 mV/Dec, which can obtain the better device performance and lower static power consumption under the lower voltage operating conditions [12]. At the same time, it can also effectively improve circuit performance and reduce circuit

Micromachines 2019, 10, 424 2 of 11

power consumption, which can make it a potential device in the ultra-low power ICs [13]. However, the on-state current of the conventional silicon based TFET is smaller. The reason is that the carrier tunneling quality and the forbidden band width are so larger that the electrons tunneling probability is smaller. Meanwhile, the SS of TFET cannot also reach the ideal value due to the non-ideal effects, such as the complex process of ultra-steep PN junction. To improve the on-state current and SS of TFETs, it is necessary to further increase the gate-to-channel control by the new materials and processes [14–16].

A high performance doping-less tunneling field effect transistor with Ge/Si<sub>0.6</sub>Ge<sub>0.4</sub>/Si heterojunction (H-DLTFET) is proposed in this paper. Compared to the conventional DLTFET, the source and channel regions of the H-DLTFET respectively use the germanium and Si<sub>0.6</sub>Ge<sub>0.4</sub> materials. To make the energy band becomes steeper, source region use the narrow bandgap semiconductor material germanium, which can also effectively improve the electric field of source/channel tunneling junction. The electrons from the valence band of source region are easier to tunnel into the conduction band of channel region, which can increase the on-state current effectively [17]. The channel region uses Si<sub>0.6</sub>Ge<sub>0.4</sub> material to improve the channel carrier mobility. Meanwhile, the SS and frequency characteristics of H-DLTFET can be greatly improved. Besides, the dual gate process is used to improve the gate-to-channel control, which can effectively reduce the adverse effects of short channel effects [18]. Meanwhile, the stronger gate control can provide the higher saturation current density and lower off-state leakage current [19]. The main research contents of this paper are as follows: First, the simulation structure and models of DLTFET and H-DLTFET are introduced. Next, the input and output characteristics of DLTFET and H-DLTFET are analyzed. Then, the working mechanism of H-DLTFET is described. Afterwards, effects of Ge content, electrode work function, and structure parameters on the performance of H-DLTFET are researched systematically. Subsequently, the C-V and frequency characteristics of DLTFET and H-DLTFET are compared. Finally, the simulation results show that the H-DLTFET has the greater potential in the low-power ICs.

# 2. Device Structure and Models

To improve the on-state current and SS of conventional DLTFET, the differences of H-DLTFET are that the germanium and  $\rm Si_{0.6}Ge_{0.4}$  materials are used in the source and channel regions, respectively. Then, the gate-to-channel control capability can be improved by enhancing the coupling between gate and back-gate. Finally, the H-DLTFET can obtain the higher on-state current by adjusting the length and height of effective channel tunneling region.

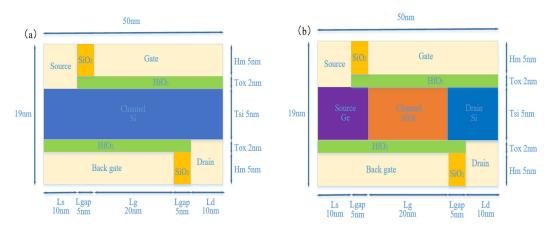

Figure 1a,b respectively show the schematic of the conventional DLTFET and the new proposed H-DLTFET. The specific parameters are as follows: channel thickness  $H_c = 5$  nm; gate oxide thickness  $T_{ox} = 2$  nm; the length of source region ( $L_s$ ), gap region ( $L_{gap}$ ), channel region ( $L_g$ ), and drain region ( $L_d$ ) are 10 nm, 5 nm, 20 nm, and 10 nm, respectively. Meanwhile, the doping concentration and type of  $L_s$ ,  $L_{gap}$ ,  $L_g$ , and  $L_d$  are  $1 \times 10^{18}$  cm<sup>-3</sup> and n-type, respectively. Besides, the work functions of gate, source, drain, and back-gate electrodes are respectively 4 eV, 5.3 eV, 4.2 eV, and 5.1 eV.

All simulation results in this paper are based on the SILVACO TCAD simulation software (Santa Clara University, Santa Clara, CA, USA). It is known that the spatial distribution variation of band structure and the narrowing effect of forbidden band width have an effect on the non-local Band-To-Band tunneling probability of carriers [20]. Due to the existence of traps, the Shockley-Read-Hall composite and the non-local Band-To-Band tunneling models are used in this paper. The Lombardi mobility model is also considered to accurately calculate the effects of acoustic phonon scattering and surface roughness on the mobility of carriers [21]. In addition, there are also included the Fermi-Dirac statistics and the Band-Gap Narrowing model, which can be explained by the presence of heavily doped regions.

Micromachines **2019**, 10, 424 3 of 11

Figure 1. The schematic of (a) conventional DLTFET, (b) new proposed H-DLTFET.

## 3. Discussion of Simulation Results

# 3.1. The Input Characteristics

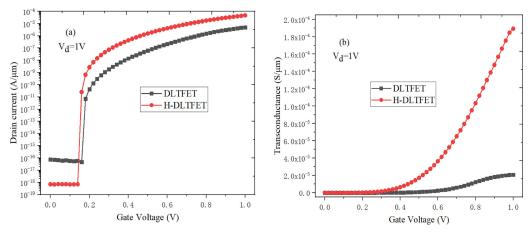

Figure 2a shows the transfer characteristics of DLTFET and H-DLTFET. The minimum off-state leakage currents of DLTFET and H-DLTFET are respectively  $7.46\times10^{-17}$  A/µm and  $7.14\times10^{-19}$  A/µm, whereas the maximum on-state currents of DLTFET and H-DLTFET are  $5.03\times10^{-6}$  A/µm and  $4.71\times10^{-5}$  A/µm, respectively. The off-state current of H-DLTFET decreases by two orders of magnitude compared with the conventional DLTFET. And the on-state current and switching ratio are respectively increased by an order of magnitude and three orders of magnitude at the same operating voltage. The reason is that a large number of electron-hole pairs from source region can tunnel into the channel, and the tunneling current would increase exponentially with the electric field. However, the electrons of channel center are depleted and the on-state current is saturated when gate voltage continues to increase. Meanwhile, the average SS and point SS of H-DLTFET respectively decrease from 41.5 mV/Dec and 4 mV/Dec to 15.7 mV/Dec and 2.6 mV/Dec. It can be concluded that the H-DLTFET have the larger on-state current, higher switching ratio and smaller SS than that of DLTFET, so it has the greater potential in the ultra-low power ICs.

Figure 2. (a) Transfer characteristic, (b) Trans-conductance of DLTFET and H-DLTFET.

The trans-conductance  $(g_m)$  is an important characterization parameter of frequency characteristics, which can determine the intrinsic gain of semiconductor devices. Figure 2b shows the  $g_m$  value of DLTFET and H-DLTFET as a function of gate voltage. The  $g_m$  can be calculated by the following Equation (1) [22]:

$$g_m = dI_{DS}/dV_{GS} \tag{1}$$

Micromachines **2019**, 10, 424 4 of 11

The  $g_m$  value mainly depends on the output leakage current, and the faster the increase rate of output leakage current is, the larger the  $g_m$  is. The  $g_m$  values of DLTFET and H-DLTFET increase with the gate voltage increases. This is because the barrier width of tunneling junction decreases, the tunneling electrons increase, and the output leakage current increases gradually. It can be seen from Figure 2b that the  $g_m$  values of DLTFET and H-DLTFET are respectively  $2.07 \times 10^{-5}$  S/ $\mu$ m and  $1.89 \times 10^{-4}$  S/ $\mu$ m. Due to the higher on-state current, the maximum  $g_m$  value of H-DLTFET can be increased by an order of magnitude.

## 3.2. The Output Characteristics

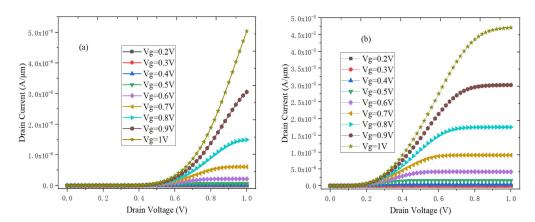

Figure 3a,b respectively show the output characteristics of DLTFET and H-DLTFET under the different gate voltages. The output currents of DLTFET and H-DLTFET can be divided into the exponential growth region and the saturation region. The output current would increase to the saturation value when the drain-source voltage is greater than the saturation pinch-off voltage. At the same time, there is no change in the tunneling barrier width. Besides, the output current would increase when the gate voltage increase. The reason is that the energy band of tunneling junction could be steeper, and the BTBT distance decrease with the gate voltage increases. The maximum output currents of DLTFET and H-DLTFET are respectively  $5.03 \times 10^{-6}$  A/ $\mu$ m and  $4.71 \times 10^{-5}$  A/ $\mu$ m. The output current of H-DLTFET can be increased by an order of magnitude compared with the DLTFET, so the H-DLTFET has the higher saturation output current.

Figure 3. The output characteristics of (a) DLTFET, (b) H-DLTFET.

# 3.3. The Operating Mechanism of H-DLTFET

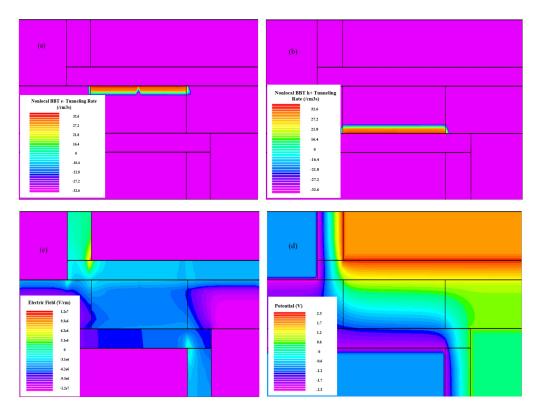

Figures 4 and 5 respectively illustrate the operating mechanism of H-DLTFET. Figure 4a,b respectively show the electron BTBT and hole BTBT efficiencies of the H-DLTFET channel under the on-state condition. It can be found that the e-BTBT region occurs near the channel top, and the h-BTBT region is mainly concentrated on the channel bottom. The line tunneling current is formed in the overlapping region between gate and back gate, where the electric field is parallel to the e- and h-BTBT tunneling directions [23]. In addition, the point tunneling also exists in H-DLTFET, which can be explained by the higher BTBT efficiency of the source-channel tunneling junction. The reason the tunneling current increase is that the area of the line tunneling is larger than that of the point tunneling. The electric field and potential distributions of H-DLTFET are respectively shown in Figure 4c,d. Due to the higher electric field and potential of the source-channel tunneling junction, electrons from the electron doped source region and the channel bottom region are more easily absorbed by the drain region, which would result in the higher on-state current [24].

Micromachines **2019**, 10, 424 5 of 11

**Figure 4.** (a) e-BTBT rate; (b) h-BTBT rate; (c) Electric field; and (d) Potential distribution of the H-DLTFET.

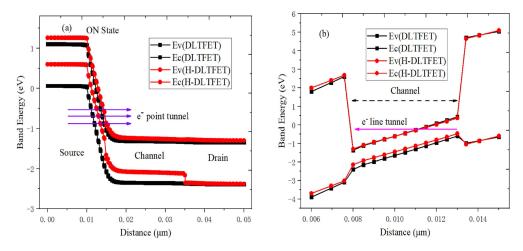

**Figure 5.** On-state energy band of DLTFET and H-DLTFET (**a**) from source to drain; (**b**) from channel top to channel bottom.

Figure 5a,b respectively show the on-state energy band of DLTFET and H-DLTFET under the different position. It can be observed from Figure 5a that the energy band at the source-channel tunneling junction of H-DLTFET is more curved than that of DLTFET, so it has the narrower tunneling barrier width. The electrons from source region can tunnel to the channel region easily, which is largely dependent on the tunneling barrier width [25]. Besides, the line tunneling current of DLTFET and H-DLTFET can also be confirmed by the on-state energy band from top channel to bottom channel, as shown in Figure 5b. Since the valence band of the channel bottom can be aligned with the conduction band of the channel top, many electrons from the channel bottom can tunnel to the channel top, thereby forming the tunneling current.

Micromachines **2019**, 10, 424 6 of 11

## 3.4. Effect of the Device Parameters on the Performance of H-DLTFET

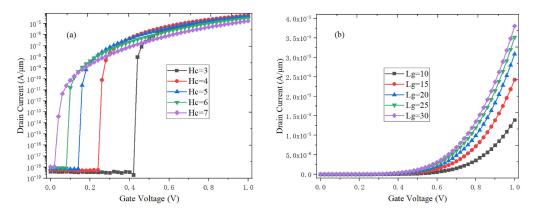

In Figure 6a, the channel electric field coupling effect between gate and back gate is weakened when the channel thickness (Hc) increase. Meanwhile, the electric field, electronic tunneling probability and on-state current of channel are all reduced. Figure 6b shows the effect of channel length (Lg) on the transfer characteristics. The barrier width of the tunneling junction becomes less susceptible to the drain voltage with the Lg increases, the line tunneling area and the electron tunneling number increase, thereby increasing the on-state current of H-DLTFET. However, the on-state current rises slowly and the preparation process becomes complicated when the channel length exceeds 20 nm [26,27]. It can be concluded that the optimal Hc and Lg are 5 nm and 20 nm, respectively.

**Figure 6.** Effect of device parameters on the transfer characteristics of H-DLTFET (**a**) channel thickness *Hc*, (**b**) channel length *Lg*.

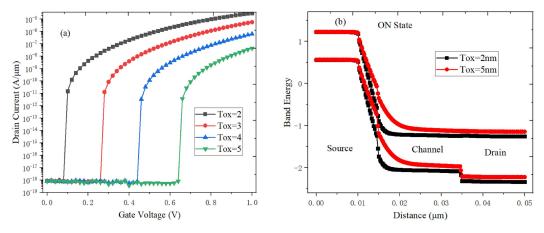

In Figure 7a, both the gate voltage and electric field required for the point tunneling would increase when the gate dielectric thickness ( $T_{ox}$ ) increases. At the same time, the electric field at the interface between the gate oxide dielectric and channel is weakened. The on-state current increases from  $4.4 \times 10^{-8}$  A/µm to  $3.1 \times 10^{-5}$  A/µm, and the switching ratio is almost increased by three orders of magnitude when  $T_{ox}$  decrease from 5 nm to 2 nm. Figure 7b shows the energy band of the source-channel tunneling junction at the different  $T_{ox}$ . As the  $T_{ox}$  decreases, the energy band becomes steeper. Both the electron BTBT probability and the tunneling area are increased, and the gate-to-channel control capability increases, so the on-state current can be effectively improved. In a word, the optimal  $T_{ox}$  is 2 nm.

Figure 7. Effect of gate oxide thickness on (a) transfer characteristics, (b) on-state energy band.

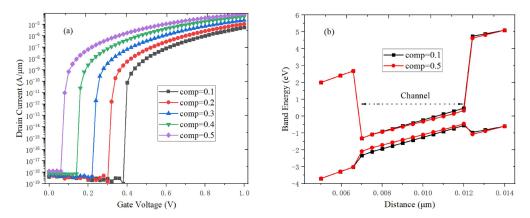

It can be found by observing Figure 8a that the on-state tunneling current increases with the germanium content of  $Si_{1-x}Ge_x$  material increases. This is because the germanium material can provide the smaller electron tunneling quality [28]. The number of tunneling electrons increase, and the

Micromachines **2019**, 10, 424 7 of 11

band gap becomes narrower when the germanium content increases, which can improve the e-BTBT probability and SS characteristics of H-DLTFET. As shown in Figure 8b, the energy band width becomes narrower, and the energy band becomes steeper with the germanium content increases, which result in the higher e-BTBT probability. The H-DLTFET can obtain the relatively smaller off-state current and the larger on-state current when the optimal Ge content is 0.4. Therefore, the channel of H-DLTFET uses the  $Si_{0.6}Ge_{0.4}$  material.

Figure 8. Effect of germanium content on (a) transfer characteristics; (b) on-state energy band.

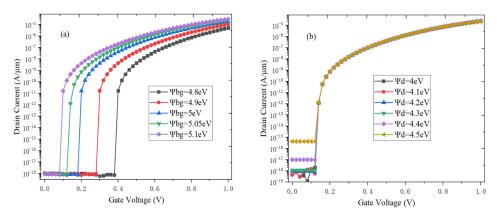

In Figure 9a, the on-state current increases and the transfer characteristic curve shifts to the left when the back-gate work function increases. The reason is that a large amount of holes are accumulated in the channel bottom when the back-gate has the higher work function. It can be seen from Figure 9b that the channel barrier height decreases with the drain work function increases, which would result in the higher carrier number and off-state current. The optimal drain work function is 4.2 eV. As shown in Figure 9c, the coupling capability between double gate and channel becomes stronger when the gate work function decreases, so the electric field of drain region increases. The electrons from the valence band of channel region can easily pass through the narrow barrier to the drain region to form the tunneling current [29].

**Figure 9.** Effect of work function (**a**) back gate  $\Psi bg$ ; (**b**) drain  $\Psi d$ ; (**c**) gate  $\Psi g$  on the transfer characteristics of H-DLTFET.

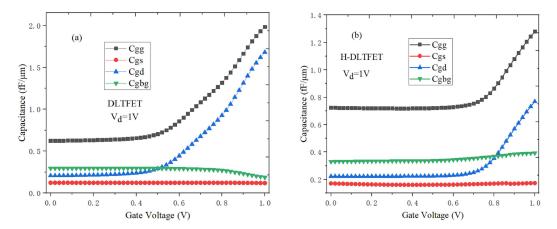

## 3.5. The C-V Characteristics

The gate capacitance ( $C_{gg}$ ) is an important indicator for evaluating the frequency characteristics [30]. Figure 10a,b respectively show the C-V characteristics of DLTFET and H-DLTFET at the operating frequency f = 1 MHz. The  $C_{gg}$  mainly includes the gate-drain capacitance ( $C_{gd}$ ), gate-source capacitance ( $C_{gs}$ ) and gate-back gate capacitance ( $C_{gbg}$ ) [31]. It can be seen from Figure 10 that the  $C_{gd}$  increases exponentially with the gate voltage increases. The reason is that the tunneling barrier width decreases

Micromachines **2019**, 10, 424

when the gate voltage increases, and the inversion layer extending from drain region to source region can be formed. The  $C_{gs}$  is mainly composed of parasitic capacitance, and the order of magnitude is small relative to the  $C_{gd}$  under the inversion layer, which is weakly affected by the bias voltage. Therefore, the  $C_{gg}$  is mainly determined by the  $C_{gd}$  at the high gate voltage. Almost all electrons of H-DLTFET can be collected by the drain region immediately, and the channel electron concentration is lower, which would result in the smaller  $C_{gg}$  and  $C_{gd}$ . It can be seen from Figure 10 that the  $C_{gg}$  and  $C_{gd}$  of H-DLTFET respectively decrease from 1.98 fF/ $\mu$ m and 1.68 fF/ $\mu$ m to 1.28 fF/ $\mu$ m and 0.77 fF/ $\mu$ m compared with the conventional DLTFET, so the H-DLTFET has the better frequency characteristics.

Figure 10. The C-V characteristic of (a) DLTFET; (b) H-DLTFET.

## 3.6. The Frequency Characteristics

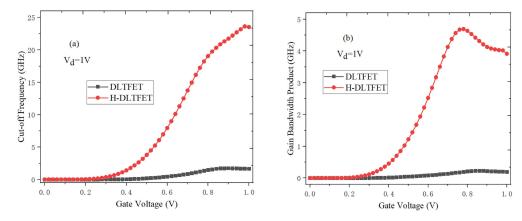

As an important indicator, the cut-off frequency is used to evaluate the frequency characteristics of electronic devices. It can be obtained by the ratio of gm to  $C_{gg}$ , and the specific calculation formula is shown in Equation (2) [32].

$$f_T = \frac{g_m}{2\pi C_{gs} \sqrt{1 + 2C_{gd}/C_{gs}}} \approx \frac{g_m}{2\pi (C_{gs} + C_{gd})} = \frac{g_m}{2\pi C_{gg}}$$

(2)

In Figure 11a, the cut-off frequency increases when the gate voltage increases. This is because the on-state current and  $g_m$  value increase with the electronic BTBT efficiency increases. However, the cut-off frequency has no change or even decreases when the gate voltage continues to increase to the high gate voltage. This is due to the increase of  $C_{gg}$  and the decrease of  $g_m$ , which is caused by the mobility degradation. In addition, the cut-off frequency of H-DLTFET is much larger than that of DLTFET, which can be explained by the smaller  $C_{gg}$  of H-DLTFET. The larger the  $g_m$  value is, the higher the cut-off frequency is.

Micromachines **2019**, 10, 424 9 of 11

Figure 11. (a) Cut-off frequency, (b) Gain bandwidth product of DLTFET and H-DLTFET.

The gain bandwidth product is another important indicator in the analysis of frequency characteristics, which can be calculated by the Equation (3) [33,34].

$$GWB = g_m / 2\pi 10C_{gd} \tag{3}$$

It can be seen from Figure 11b that the gain bandwidth product of H-DLTFET is significantly higher than that of DLTFET. Due to the increase of  $g_m$ , the gain bandwidth product initially increases as the gate voltage increases. However, the gain bandwidth product decreases when the gate voltage is greater than 0.8 V. This is because the common impact between the mobility degradation and the parasitic capacitance. In addition, the overall trend of gain bandwidth product as a function of gate voltage is consistent with the cut-off frequency. Compared to the conventional DLTFET, the cut-off frequency and gain bandwidth product of H-DLTFET respectively increase from 1.75 GHz and 0.23 GHz to 23.6 GHz and 4.69 GHz. Therefore, the H-DLTFET has the better frequency characteristics.

#### 4. Conclusions

A high performance H-DLTFET is constructed and studied in this paper. Compared to the traditional DLTFET, the differences of H-DLTFET are that the source and channel regions respectively use the narrow band gap semiconductor germanium material and the high carrier mobility Si<sub>0.6</sub>Ge<sub>0.4</sub> material, the electric field of source/channel tunneling junction increases and the energy band becomes steeper. At the same time, the dual gate process can improve the gate-to-channel control capability. In addition, the effects of germanium content, electrode work function, and device structure parameters on the performance of H-DLTFET are analyzed systematically, and then the above optimal parameters can be obtained to optimize the overall performance of H-DLTFET. Compared to the conventional DLTFET, the simulation results show that the on-state current and switching ratio of H-DLTFET can respectively increase by one order of magnitude and three orders of magnitude, and the off-state current is reduced by two orders of magnitude at the same operating voltage. At the same time, both the maximum  $g_m$  and output current are increased by an order of magnitude. The average SS and point SS of H-DLTFET respectively decrease from 41.5 mV/Dec and 4 mV/Dec to 15.7 mV/Dec and 2.6 mV/Dec. And the  $C_{gg}$  and  $C_{gd}$  of H-DLTFET are also decreased from 1.98 fF/ $\mu$ m and 1.68 fF/ $\mu$ m to 1.28 fF/μm and 0.77 fF/μm, respectively. Meanwhile, the cut-off frequency and gain bandwidth product of H-DLTFET respectively increase from 1.75 GHz and 0.23 GHz to 23.6 GHz and 4.69 GHz. Therefore, the H-DLTFET is more suitable for the ultra-low power integrated circuits.

**Author Contributions:** Conceptualization and writing—original draft preparation, T.H.; methodology, S.W.; validation, S.C.; writing—review and editing, H.L. and W.L.; funding acquisition, H.L.

**Funding:** This research was funded by the National Natural Science Foundation of China (Grant No. U1866212), the Foundation for Fundamental Research of China (Grant No. JSZL2016110B003), the Major Fundamental Research Program of Shaanxi (Grant No. 2017ZDJC-26), the Innovation Foundation of Radiation Application

Micromachines **2019**, 10, 424

(Grant No.KFZC2018040206), and the Fundamental Research Funds for the Central Universities (Grant No. 20101196741). It was also supported by the Shanghai Aerospace Science and Technology Innovation Fund, the Fundamental Research Funds for the Central Universities, and the Innovation Fund of Xidian University.

**Conflicts of Interest:** The authors declare no conflicts of interest.

## References

- 1. Dash, S.; Mishra, G.P. A new analytical threshold voltage model of cylindrical gate tunnel FET (CG-TFET). *Superlattices Microstruct.* **2015**, *86*, 211–220. [CrossRef]

- 2. Singh, D.; Pandey, S.; Nigam, K.; Sharma, D.; Yadav, D.S.; Kondekar, P. A charge-plasma-based dielectric-modulated junctionless TFET for biosensor label-free detection. *IEEE Trans. Electron Devices* **2016**, 64, 271–278. [CrossRef]

- 3. Chauhan, S.S.; Sharma, N. Impact of Spacer-Gate Engineered Workfunction on the Performance of Dopingless TFET. *J. Nanoelectron. Optoelectron.* **2018**, *13*, 1200–1203. [CrossRef]

- 4. Damrongplasit, N.; Kim, S.H.; Liu, T.J.K. Study of random dopant fluctuation induced variability in the raised-Ge-source TFET. *IEEE Electron Device Lett.* **2013**, *34*, 184–186. [CrossRef]

- 5. Raad, B.R.; Nigam, K.; Sharma, D.; Kondekar, P.N. Performance investigation of bandgap, gate material work function and gate dielectric engineered TFET with device reliability improvement. *Superlattices Microstruct*. **2016**, *94*, 138–146. [CrossRef]

- Yadav, S.; Sharma, D.; Chandan, B.V.; Aslam, M.; Soni, D.; Sharma, N. A novel hetero-material gate-underlap electrically doped TFET for improving DC/RF and ambipolar behaviour. Superlattices Microstruct. 2018, 117, 9–17. [CrossRef]

- 7. Loan, S.A.; Alharbi, A.G.; Rafat, M. Ambipolar leakage suppression in electron–hole bilayer TFET: Investigation and analysis. *J. Comput. Electron.* **2018**, *17*, 977–985.

- 8. Anand, S.; Sarin, R.K. Gate misalignment effects on analog/RF performance of charge plasma-based doping-less tunnel FET. *Appl. Phys. A* **2017**, *123*, 413. [CrossRef]

- 9. Tanaka, C.; Adachi, K.; Fujimatsu, M.; Hokazono, A.; Kondo, Y.; Kawanaka, S. Implementation of TFET SPICE model for ultra-low power circuit analysis. *IEEE J. Electron Devices Soc.* **2016**, 4, 273–277. [CrossRef]

- 10. Cecil, K.; Singh, J. Influence of Germanium source on dopingless tunnel-FET for improved analog/RF performance. *Superlattices Microstruct.* **2017**, *101*, 244–252. [CrossRef]

- 11. Anand, S.; Sarin, R.K. An analysis on ambipolar reduction techniques for charge plasma based tunnel field effect transistors. *J. Nanoelectron. Optoelectron.* **2016**, *11*, 543–550. [CrossRef]

- 12. Yadav, S.; Madhukar, R.; Sharma, D.; Aslam, M.; Soni, D.; Sharma, N. A new structure of electrically doped TFET for improving electronic characteristics. *Appl. Phys. A* **2018**, *124*, 517. [CrossRef]

- 13. Revelant, A.; Villalon, A.; Wu, Y.; Zaslavsky, A.; Le Royer, C.; Iwai, H.; Cristoloveanu, S. Electron-hole bilayer TFET: Experiments and comments. *IEEE Trans. Electron Devices* **2014**, *61*, 2674–2681. [CrossRef]

- 14. Lahgere, A.; Panchore, M.; Singh, J. Dopingless ferroelectric tunnel FET architecture for the improvement of performance of dopingless n-channel tunnel FETs. *Superlattices Microstruct.* **2016**, *96*, 16–25. [CrossRef]

- 15. Chen, S.; Wang, S.; Liu, H.; Li, W.; Wang, Q.; Wang, X. Symmetric U-shaped gate tunnel field-effect transistor. *IEEE Trans. Electron Devices* **2017**, *64*, 1343–1349. [CrossRef]

- 16. Bagga, N.; Sarkar, S.K. An analytical model for tunnel barrier modulation in triple metal double gate TFET. *IEEE Trans. Electron Devices* **2015**, *62*, 2136–2142. [CrossRef]

- 17. Han, T.; Liu, H.; Chen, S.; Wang, S.; Li, W. A Doping-Less Tunnel Field-Effect Transistor with Si<sub>0.6</sub>Ge<sub>0.4</sub> Heterojunction for the Improvement of the On–Off Current Ratio and Analog/RF Performance. *Electronics* **2019**, *8*, 574. [CrossRef]

- 18. Lattanzio, L.; De Michielis, L.; lonescu, A.M. The electron–hole bilayer tunnel FET. *Solid-State Electron*. **2012**, 74, 85–90. [CrossRef]

- 19. Padilla, J.L.; Alper, C.; Medina-Bailón, C.; Gámiz, F.; lonescu, A.M. Assessment of pseudo-bilayer structures in the heterogate germanium electron-hole bilayer tunnel field-effect transistor. *Appl. Phys. Lett.* **2015**, *106*, 262102. [CrossRef]

- 20. Ghosh, B.; Akram, M.W. Junctionless tunnel field effect transistor. *IEEE Electron Device Lett.* **2013**, *34*, 584–586. [CrossRef]

Micromachines **2019**, 10, 424

21. Kao, K.H.; Verhulst, A.S.; Vandenberghe, W.G.; Sorée, B.; Magnus, W.; Leonelli, D.; Groeseneken, G.; De Meyer, K. Optimization of gate-on-source-only tunnel fets with counter-doped pockets. *IEEE Trans. Electron Devices* **2012**, *59*, 2070–2077. [CrossRef]

- 22. Asthana, P.K.; Goswami, Y.; Basak, S.; Rahi, S.B.; Ghosh, B. Improved performance of a junctionless tunnel field effect transistor with a Si and SiGe heterostructure for ultra low power applications. *RSC Adv.* **2015**, *5*, 48779–48785. [CrossRef]

- 23. Kim, S.W.; Kim, J.H.; Liu, T.J.K.; Choi, W.Y.; Park, B.G. Demonstration of L-shaped tunnel field-effect transistors. *IEEE Trans. Electron Devices* **2016**, 63, 1774–1778. [CrossRef]

- 24. Rahi, S.B.; Asthana, P.; Gupta, S. Heterogate junctionless tunnel field-effect transistor: Future of low-power devices. *J. Comput. Electron.* **2016**, *16*, 33–38. [CrossRef]

- 25. Li, W.; Liu, H.; Wang, S.; Chen, S. Reduced Miller capacitance in U-shaped channel tunneling FET by introducing heterogeneous gate dielectric. *IEEE Electron Device Lett.* **2017**, *38*, 403–406. [CrossRef]

- 26. Raushan, M.A.; Alam, N.; Siddiqui, M.J. Performance Enhancement of Junctionless Tunnel Field Effect Transistor Using Dual-k Spacers. *J. Nanoelectron. Optoelectron.* **2018**, *13*, 912–920. [CrossRef]

- 27. Wadhwa, G.; Raj, B. Label Free Detection of Biomolecules Using Charge-Plasma-Based Gate Underlap Dielectric Modulated Junctionless *TFET. J. Electron. Mater.* **2018**, 47, 4683–4693. [CrossRef]

- 28. Raushan, M.A.; Alam, N.; Akram, M.W.; Siddiqui, M.J. Impact of asymmetric dual-k spacers on tunnel field effect transistors. *J. Comput. Electron.* **2018**, *17*, 756–765. [CrossRef]

- 29. Rahi, S.B.; Ghosh, B.; Bishnoi, B. Temperature effect on hetero structure junctionless tunnel FET. *J. Semicond.* **2015**, *36*, 034002. [CrossRef]

- 30. Singh, G.; Amin, S.I.; Anand, S.; Sarin, R.K. Design of Si0.5Ge0.5 based tunnel field effect transistor and its performance evaluation. *Superlattices Microstruct.* **2016**, *92*, 143–156. [CrossRef]

- 31. Anand, S.; Amin, S.I.; Sarin, R.K. Analog performance investigation of dual electrode based doping-less tunnel FET. *J. Comput. Electron.* **2016**, *15*, 94–103. [CrossRef]

- 32. Bagga, N.; Dasgupta, S. Surface potential and drain current analytical model of gate all around triple metal TFET. *IEEE Trans. Electron Devices* **2017**, *64*, 606–613. [CrossRef]

- 33. Chandan, B.V.; Nigam, K.; Sharma, D. Junctionless based dielectric modulated electrically doped tunnel FET based biosensor for label-free detection. *Micro N. Lett.* **2018**, *13*, 452–456. [CrossRef]

- 34. Naik, V.; Chauhan, S.S. Si0.5Ge0.5 Single and Hetero-gate dielectric doping-less tunnel FETs. In Proceedings of the IEEE International Conference on Communication and Signal Processing (ICCSP), Melmaruvathur, India, 6–8 April 2016; pp. 635–638.

© 2019 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).