Article

# Discontinuous Space Vector PWM Strategy for Three-Phase Three-Level Electric Vehicle Traction Inverter Fed Two-Phase Load

Guozheng Zhang <sup>1</sup>, Yuwei Wan <sup>1</sup>, Zhixin Wang <sup>2</sup>, Le Gao <sup>3</sup>, Zhanqing Zhou <sup>4</sup>, and Qiang Geng <sup>1,\*</sup>

- <sup>1</sup> School of Electrical Engineering and Automation, Tiangong University, Tianjin 300387, China; zhanggz@tju.edu.cn (G.Z.); wanyuwei.tiangong@gmail.com (Y.W.)

- <sup>2</sup> Weichai New Energy Co., Ltd., Weifang 261061, China; wangzx@weichai.com

- <sup>3</sup> Weichai Power Co., Ltd., Weifang 261061, China; gaole@weichai.com

- <sup>4</sup> School of Artificial Intelligence, Tiangong University, Tianjin 300387, China; zhzhq@tju.edu.cn

- \* Correspondence: gengqiang@tju.edu.cn; Tel.: +86-1382-020-8856

Received: 13 December 2019; Accepted: 12 March 2020; Published: 14 March 2020

Abstract: Discontinuous pulse width modulation (DPWM) strategies are usually adopted to reduce the switching loss and output current ripple of three-phase three-level traction inverters under three-phase load conditions. However, if there is a short circuit in any arbitrary phase or the inverter is used to feed a two-phase load, the output performance of conventional DPWM strategies will be deteriorated. Here, four improved DPWM (IDPWM) strategies for three-phase three-level neutral-point-clamped (NPC) traction inverter fed two-phase load are proposed. Unlike three-phase load conditions, the phase angle and the amplitude of each basic voltage vector in the space vector diagram are modified under two-phase load conditions. Consequently, sectors are re-divided and duty cycles of basic vectors during synthesis are recalculated. Clamping intervals of each phase for the four type discontinuous PWM (DPWM) strategies are rearranged according to the modified space vector diagram; then, the proposed DPWM strategies can be obtained. Compared with the conventional DPWM strategies, the output current waveform quality of the proposed strategy is significantly improved. Meanwhile, the amplitude of the neutral-point voltage ripple is also reduced.

Keywords: three-level inverter; two-phase load; discontinuous pulse width modulation

## 1. Introduction

Multilevel inverters are more and more widely being used for not only high-voltage and medium-voltage applications, but also low-voltage applications because of significantly high output waveform quality and low dV/dt [1–3]. Due to the low stress to switching devices, switching loss and switching noise are reduced. Electric vehicles (EVs) and plug-in hybrid EVs are put forward to replace the traditional fuel vehicle due to the unpredictable crude oil futures prices and increasingly stringent vehicle emission standards all over the world. In EV applications, the standard two-level six-switch inverter is usually used as the traction inverter [4]. On one hand, the switching frequency of the inverter needs to be increased so as to reduce the size of passive component. Correspondingly, the switching loss of the inverter is relatively high. Furthermore, with the increase of power and voltage level, the switching frequency is limited. A three-level inverter could effectively reduce the switching loss without loss of output waveform quality. On the other hand, conventional two-level inverters do not have any fault-tolerant ability; instead, the vehicle's powertrain loses controllability and might have to stall. Thus, additional switches need to be paralleled to mitigate this, which increases the overall cost of the electric vehicle. Three-level inverters can realize fault-tolerant operation with additional

advantages of lower common mode voltage, higher power density enhancement, and lower stress of the switches. Thus, three-level inverters could be under consideration for vehicle traction applications.

There are three main types of topology for three-level inverters: cascade H-bridge (CHB) [5], flying capacitor (FC) [6], and neutral-point-clamped (NPC) [7]. Among them, NPC three-level inverters play a dominant role in industrial applications. The modulation strategies of three-level inverters can be divided into continuous pulse width modulation (CPWM) and discontinuous pulse width modulation (DPWM), in accordance with the following condition, that is, whether there are discontinuous intervals in the modulation signal. The switching loss of three-level traction inverters can be considerably reduced by the use of DPWM. For this reason, DPWM is one of the preferred modulation strategies applied in EV applications. Moreover, the output performance of DPWM is better than CPWM under higher modulation index condition [8].

The traditional DPWM strategies (namely, DPWM0–DPWM3) for three-phase NPC three-level inverters were first proposed in [9]. According to the power factor, the appropriate strategy can be selected from DPWM0-DPWM3 to reduce the switching loss. In recent years, DPWM strategies have gradually shown their advantages against conventional CPWM strategies. A sector subdivision DPWM strategy was proposed in [8], and the discontinuous intervals are arranged according to the evaluation index of average current ripple vector. The output waveform quality of the proposed strategy is better than the conventional CPWM and DPWM0–DPWM3. In [10], a DPWM strategy was proposed to control the neutral-point voltage ripple and reduce the switching loss; the discontinuous intervals are distributed according to the polarity of neutral-point voltage. An adjustable DPWM strategy was presented in [11]; the discontinuous intervals are changed with the variation of power factor so as to reduce the switching loss in the whole power factor range. However, these strategies are only suitable for three-phase inverter fed three-phase load. If any arbitrary phase of three-phase load is short-circuited or the three-phase inverter is adopted to feed a two-phase load, the output current harmonic distortion and the amplitude of neutral-point voltage ripple will be increased significantly [12]. For EV application, it is necessary for the vehicle to keep driving stably in the short period when the motor experiences a single phase fault, therefore the modulation strategy needs to be reconsidered to adapt the operation conditions mentioned above.

The continuous modulation strategy for analog and digital implementation for a three-phase two-level inverter fed two-phase induction motor can be found in [13–15]. Discontinuous modulation strategy for three-phase two-level inverter fed two-phase load was first proposed by Tomaselli et al. [12]. Based on the analysis above, a discontinuous modulation strategy for three-phase two-level inverter fed two-phase load was proposed to reduce the switching loss and current ripple [16]. A generalized discontinuous modulation strategy for unbalanced two-phase loads was proposed in [17]. The switching loss could be effectively reduced for the full power factor range. A discontinuous modulation strategy for both balanced and unbalanced two-phase loads is proposed in [18]. Duty cycles of three-phase were recalculated to optimize the switching sequences. The switching loss could be significantly reduced in both situations. Although the discontinuous modulation strategy for a three-phase two-level inverter fed two-phase load has been well established, the strategy for a three-phase three-level inverter has not been discussed yet.

In this paper, the amplitude and phase angle of basic voltage vectors of three-level inverter fed two-phase load are modified, the sectors are re-divided, and duty cycles of basic vectors during synthesis are recalculated. Clamping intervals of each phase for the four types of DPWM strategies are rearranged according to the modified space vector diagram; then, the improved DPWM strategies can be obtained. The principle of DPWM under three-phase load condition is explained in detail in Section 2. The modification process of basic vectors and the expressions of duty cycle of basic vectors synthesizing the reference vector under two-phase load condition are presented in Section 3. In Section 4, the proposed improved DPWMs (IDPWM)s are validated through extensive experimental results in the whole modulation index range, with a constant voltage to frequency (V/f) control. The conclusions are presented in Section 5.

#### 2. Discontinuous Pulse Width Modulation (DPWM) under Three-Phase Load Condition

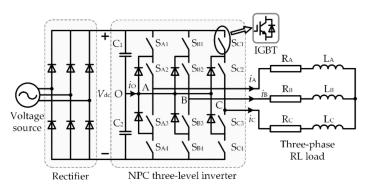

For a three-phase NPC three-level inverter (as shown in Figure 1), the four switching devices of each phase-leg can generate three switching states, namely P, O, and N (Table 1); so there are altogether  $3^3 = 27$  switching state combinations for a three-phase three-level inverter. According to Equation (1), each switching state combination corresponds to one basic vector in the space vector diagram:

$$V_n = v_A e^{j0} + v_B e^{j\frac{2\pi}{3}} + v_C e^{j\frac{4\pi}{3}}, n = 0, 1, 2, \dots, 18.$$

(1)

**Figure 1.** The topology of the neutral-point-clamped (NPC) three-level inverter fed three-phase Resistance-Inductance (RL) load. (Insulated Gate Bipolar Transistor (IGBT)).

| Switching State | S <sub>A1</sub> | S <sub>A2</sub> | S <sub>A3</sub> | S <sub>A4</sub> |

|-----------------|-----------------|-----------------|-----------------|-----------------|

| Р               | 1               | 1               | 0               | 0               |

| О               | 0               | 1               | 1               | 0               |

| Ν               | 0               | 0               | 1               | 1               |

Table 1. Definition of switching states for phase A.

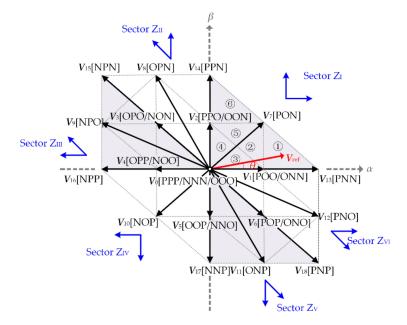

As shown in Figure 2, basic vectors can be categorized into four types (zero vector  $V_0$ , small vector  $V_1-V_6$ , medium vector  $V_7-V_{12}$  and large vector  $V_{13}-V_{18}$ ) according to their amplitudes. There are three switching state combinations corresponding to zero vector, and there are two switching state combinations corresponding to each small vector. Taking large vectors as the boundaries, the space vector diagram can be divided into six sectors  $Z_I-Z_{VI}$ , and each sector can be further divided into six small triangles (1-6). The nearest three basic vectors are usually used to synthesize the reference vector  $V_{ref}$ . Basic vectors used to synthesize  $V_{ref}$  in each triangle of sector  $Z_I$  are listed in Table 2. The situation in other sectors can be obtained in the same manner.

Table 2. Basic vectors used to synthesize  $V_{ref}$  in each triangle of sector  $Z_{I.}$

| Small Triangle | Basic Voltage Vector                                                                       |

|----------------|--------------------------------------------------------------------------------------------|

| 1              | <i>V</i> <sub>1</sub> [POO/ONN], <i>V</i> <sub>7</sub> [PON], <i>V</i> <sub>13</sub> [PNN] |

| (2) and (5)    | $V_1$ [POO/ONN], $V_2$ [PPO/OON], $V_7$ [PON]                                              |

| (3) and (4)    | V <sub>0</sub> [PPP/OOO/NNN], V <sub>1</sub> [POO/ONN], V <sub>2</sub> [PPO/OON]           |

| 6              | <i>V</i> <sub>2</sub> [PPO/OON], <i>V</i> <sub>7</sub> [PON], <i>V</i> <sub>14</sub> [PPN] |

Figure 2. The space vector diagram of the NPC three-level inverter fed three-phase load.

For four basic types of conventional DPWMs, that is DPWM0–DPWM3 [9], switching sequences used to synthesize  $V_{ref}$  in sector  $Z_I$  are shown in Table 3. The switching sequences of other sectors can be obtained according to sector and vector symmetry. By the use of the volt-second balance principle, the duty cycles of the basic vectors synthesizing the reference vector can be achieved. If the reference vector  $V_{ref}$  is located in triangle ① of sector  $Z_I$ , then  $V_1$ ,  $V_7$ , and  $V_{13}$  will be used to synthesize  $V_{ref}$ , yielding:

$$\begin{cases} \mathbf{V}_{ref} = \mathbf{V}_{13}d_1 + \mathbf{V}_7d_2 + \mathbf{V}_1d_0 \\ 1 = d_1 + d_2 + d_0 \end{cases},$$

(2)

where  $d_1$ ,  $d_2$ , and  $d_0$  are duty cycles of basic vectors  $V_1$ ,  $V_7$ , and  $V_{13}$ , respectively. The duty cycles of the nearest three vectors used to synthesize  $V_{ref}$  in each triangle of sector  $Z_I$  are shown in Table 4.

**Table 3.** Switching sequences of discontinuous pulse width modulation (DPWM): DPWM0–DPWM3 in sector Z<sub>I</sub> Reproduced with permission from [19].

| θ          | Triangle | DPWM0       | DPWM1       | DPWM2       | DPWM3       |

|------------|----------|-------------|-------------|-------------|-------------|

|            | 1        | POO⇔PON⇔PNN | POO⇔PON⇔PNN | ONN↔PNN↔PON | ONN↔PNN↔PON |

| [0, π/6)   | 2        | PPO⇔POO⇔PON | PPO⇔POO⇔PON | ONN↔OON↔PON | ONN↔OON↔PON |

|            | 3        | POO⇔PPO⇔PPP | POO⇔PPO⇔PPP | OON↔ONN↔NNN | OON↔ONN↔NNN |

|            | 4        | OON↔ONN↔NNN | POO→PPO→PPP | OON↔ONN↔NNN | POO→PPO→PPP |

| [π/6, π/3) | 5        | ONN↔OON↔PON | PPO⇔POO⇔PON | ONN↔OON↔PON | PPO⇔POO⇔PON |

|            | 6        | OON⇔PON⇔PPN | PPO→PPN→PON | OON↔PON↔PPN | PPO→PPN→PON |

Table 4. Duty cycles of basic voltage vectors used to synthesize the reference voltage vector.

| Triangle    | $d_1$                                 | $d_2$                                                       | $d_0$                                                  |

|-------------|---------------------------------------|-------------------------------------------------------------|--------------------------------------------------------|

| 1           | $V_{13}: 2m \sin(\pi/3 - \theta) - 1$ | $V_7$ : $2m \sin \theta$                                    | $V_1: 2[1 - m\sin(\pi/3 + \theta)]$                    |

| (2) and (5) | $V_1$ : $1 - 2m\sin\theta$            | $V_2: 2m \sin(\theta - \pi/3) + 1$                          | $V_7: 2m \sin(\pi/3 + \theta) - 1$                     |

| (3) and (4) | $V_1$ : $2m\sin(\pi/3 - \theta)$      | $V_2$ : $2m \sin \theta$                                    | $V_0: 1 - 2m\sin(\pi/3 + \theta)$                      |

| 6           | $V_{14}$ : $2m\sin\theta - 1$         | <i>V</i> <sub>7</sub> : 2 <i>m</i> sin ( $\pi/3 - \theta$ ) | <i>V</i> <sub>2</sub> : 2[1 – $msin(\pi/3 + \theta)$ ] |

In Table 4, *m* is the modulation index and  $m = \sqrt{3}V_{\text{ref}}/V_{\text{dc}}$ . As shown in Table 3, in the first half or the second half of sector  $Z_{\text{I}}$ , the switching state of one of the three phases is always P or N.

This phase is defined as the clamping phase and the switching state is defined as the clamping state. For example, the switching state of phase A is P in sector  $Z_I$  when DPWM1 is adopted, therefore the clamping phase is phase A and the clamping state is P in  $Z_I$ . The clamping phase and clamping state of DPWM0–DPWM3 are listed in Table 5. For example, A [P] means that the clamping phase is A and the clamping state is P, and C [N] means that the clamping phase is C and the clamping state is N.

| Sector            | θ                | DPWM0 | DPWM1 | DPWM2 | DPWM3 |

|-------------------|------------------|-------|-------|-------|-------|

| ZI                | [0, π/6)         | A [P] | A [P] | C [N] | C [N] |

| 1                 | [π/6,<br>π/3)    | C [N] | A [P] | C [N] | A [P] |

| $Z_{\mathrm{II}}$ | [π/3,<br>π/2)    | C [N] | C [N] | B [P] | B [P] |

|                   | [π/2,<br>2π/3)   | B [P] | C [N] | B [P] | C [N] |

| Z <sub>III</sub>  | [2π/3,<br>5π/6)  | B [P] | B [P] | A [N] | A [N] |

|                   | [5π/6, π)        | A [N] | B [P] | A [N] | B [P] |

| $Z_{IV}$          | $[\pi, 7\pi/6)$  | A [N] | A [N] | C [P] | C [P] |

|                   | [7π/6,<br>4π/3)  | C [P] | A [N] | C [P] | A [N] |

| $Z_{\rm V}$       | [4π/3,<br>3π/2)  | C [P] | C [P] | B [N] | B [N] |

|                   | [3π/2,<br>5π/3)  | B [N] | C [P] | B [N] | C [P] |

| $Z_{\rm VI}$      | [5π/3,<br>11π/6) | B [N] | B [N] | A [P] | A [P] |

|                   | [11π/6,<br>2π)   | A [P] | B [N] | A [P] | B [N] |

Table 5. Clamping phase and clamping state of DPWM0–DPWM3.

## 3. DPWM under Two-Phase Load Condition

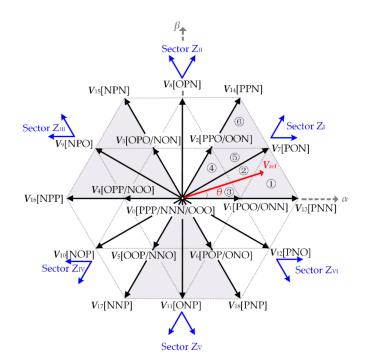

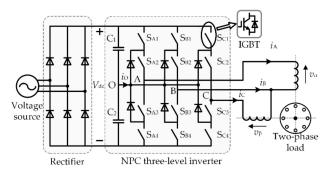

When three-level inverters are used to drive two-phase loads, the amplitude and the phase angle of the basic vector are changed. If the switching sequence and the duty cycle of DPWMs under three-phase load conditions are still adopted, the output performance of the inverter will be deteriorated. Thus, the space vector diagram under two-load conditions needs to be modified. Taking the output of phase B directly connecting to the neutral-point O as an example (as shown in Figure 3), the expression of the basic voltage vector  $V'_n$  is shown in Equation (3):

$$V'_n = v_\alpha + v_\beta e^{j\frac{\pi}{2}}, n = 0, 1, 2, \dots, 18.$$

(3)

Figure 3. The topology of the NPC three-level inverter fed two-phase load.

According to Equation (3), the space vector diagram of the three-level inverter under two-phase load condition can be obtained, as shown in Figure 4. As can be seen, the amplitude and phase angle of each basic vector are both changed. The whole space vector diagram can still be divided into six sectors. Unlike three-phase load conditions, sectors are no longer equally divided. As can be seen in Figure 4, intervals of sector  $Z_I$  and  $Z_{IV}$  are  $\pi/2$ , while intervals of sector  $Z_{II}$ ,  $Z_{VI}$  and  $Z_{VI}$  are  $\pi/4$ . Each sector can also be divided into six triangles.

Figure 4. The space vector diagram of the NPC three-level inverter fed two-phase load.

The reference vector is still synthesized by the nearest three vectors, so that Equation (2) is still stable. However, the amplitude and the phase angle of basic vectors are changed, so that duty cycles of the nearest three vectors used to synthesize  $V_{ref}$  in each triangle of sector  $Z_I$  need to be recalculated, which are listed in Table 6.

Table 6. Duty cycles of basic voltage vectors used to synthesize the reference voltage vector.

| Triangle    | $d_1$                                 | <i>d</i> <sub>2</sub>           | $d_0$                                 |

|-------------|---------------------------------------|---------------------------------|---------------------------------------|

| 1           | $V_{13}$ : $\sqrt{2}m'\cos\theta - 1$ | $V_7$ : $\sqrt{2}m'\sin\theta$  | $V_1: 2 - 2m' \cos{(\theta - \pi/4)}$ |

| (2) and (5) | $V_1: 1 - \sqrt{2m' \sin\theta}$      | $V_2: 1 - \sqrt{2m'\cos\theta}$ | $V_7: 2m'\cos(\theta - \pi/4) - 1$    |

| (3) and (4) | $V_1: \sqrt{2m'\cos\theta}$           | $V_2$ : $\sqrt{2}m'\sin\theta$  | $V_0: 1 - 2m'\cos{(\theta - \pi/4)}$  |

| 6           | $V_{14}$ : $\sqrt{2}m'\sin\theta - 1$ | $V_7: \sqrt{2m'\cos\theta}$     | $V_2: 2 - 2m'\cos(\theta - \pi/4)$    |

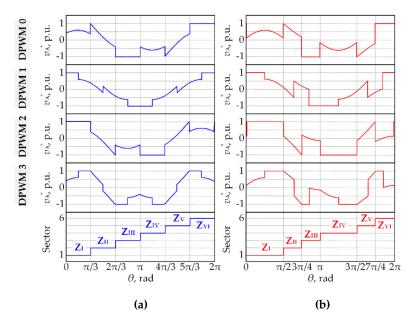

In Table 6,  $m' = \sqrt{2V_{\text{ref}}/V_{\text{dc}}}$ . The four types of discontinuous modulation strategies under two-phase load conditions are named as IDPWM0–IDPWM3. The switching sequences of IDPWM0–IDPWM3 are consistent with DPWM0–DPWM3 (Table 3). However, clamping intervals are changed with the variation of basic vectors. The modulation waves of phase A for DPWM0–DPWM3 and IDPWM0–IDPWM3 are shown in Figure 5a,b, respectively.

**Figure 5.** Modulation signals of DPWM0–DPWM3 and IDPWM0–IDPWM3: (**a**) DPWM0–DPWM3 (**b**) IDPWM0–IDPWM3. (Note: IDPWM corresponds to improved DPWM).

The realization of IDPWM0-IDPWM3 can be divided into the following steps:

- 1) Sector and triangle judgement: m' and  $\theta$  are used to determine in which sector ( $Z_I-Z_{VI}$ ) and triangle (1–6) the reference vector  $V_{ref}$  is located.

- 2) Switching sequence selection: The switching sequence used to synthesize reference vector  $V_{ref}$  can be selected according to Table 3.

- 3) Duty cycle calculation: According to Equation (2), the duty cycles  $d_1$ ,  $d_2$ , and  $d_0$  corresponding to three basic vectors can be determined.

- 4) PWM generation: The switching signal of each phase could be generated according to the switching sequence and duty cycles.

#### 4. Experimental Verification

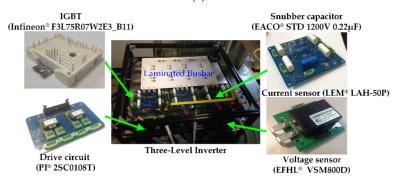

DPWM0–DPWM3 and IDPWM0–IDPWM3 are tested on the experimental prototype of the neutral-point-clamped three-level inverter fed two-phase load shown in Figure 6. Parameters of the experimental prototype are list in Table 7. The model of the proposed IDPWM is built using MATLAB/Simulink. The input and output signals of the model are then connected to the I/O block of the Real Time Interface (RTI) blockset embedded in Simulink. Next, code generation is used to generate the C code of the proposed IDPWM. The code is then debugged and downloaded into DS1007 through dSPACE ControlDesk. Then, the switch signals of the power switches of three-level inverter can be generated by the digital output interface of DS1007.

It is worth mentioning that the DC-link of the inverter is powered by two series connected DC regulated power supplies (rated output voltage: 60 V, rated output current: 15 A), so the DC-link voltage is set to 80 V. For conventional two-level inverters adopted in EV applications, the range of switching frequency is 4–15 kHz, while for three-level inverters, the switching frequency could be even lower than that of two-level inverters to maintain the same output performance, so the switching frequency is set to 2 kHz in the experiment.

(a)

(b)

**Figure 6.** The experimental prototype of the neutral-point-clamped three-level inverter: (**a**) the overall experimental prototype; (**b**) the main components of the NPC three-level inverter.

| Parameter                       | Unit | Value |

|---------------------------------|------|-------|

| dc-link voltage V <sub>dc</sub> | V    | 80    |

| dc-link capacitor $C_1, C_2$    | μF   | 1000  |

| switching frequency $f_{sw}$    | kHz  | 2     |

| Load resistance R               | Ω    | 10    |

| Load inductance L               | mH   | 40    |

Table 7. Parameters of the experimental prototype.

## 4.1. Output Waveform Quality

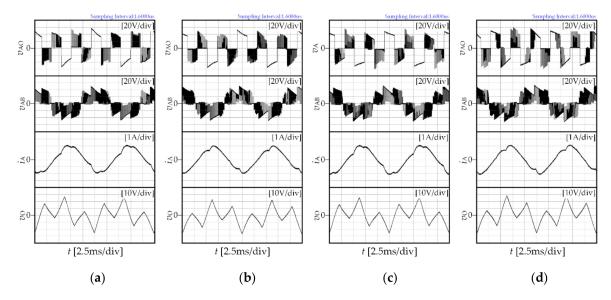

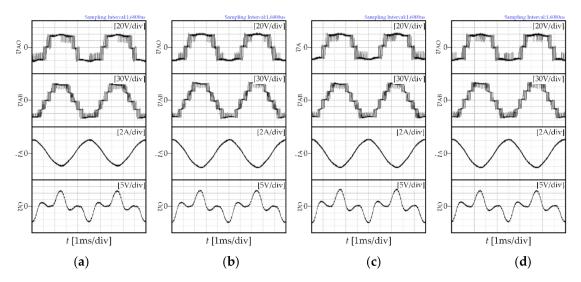

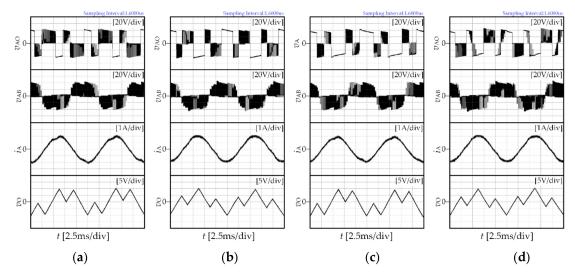

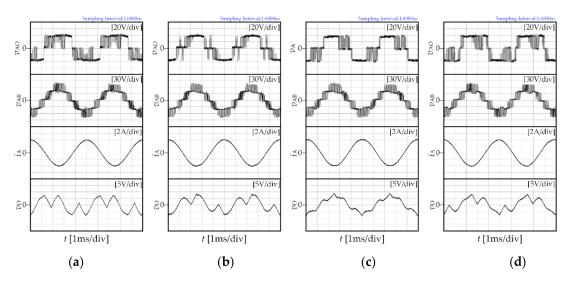

Experimental waveforms of output phase voltage  $v_{AO}$ , output line voltage  $v_{AB}$ , output current  $i_A$  and neutral-point voltage ripple  $v_O$  for DPWM0–DPWM3 and IDPWM0–IDPWM3 under two-phase load conditions when m' = 0.3 and m' = 0.8 are presented in Figures 7–10, respectively.

As can be seen from Figures 7 and 8, due to the low frequency oscillation in the neutral-point, the output voltages of DPWM0–DPWM3 are deteriorated under two-phase load conditions. As a result, the performance of the output current is poor. By the use of IDPWM0–IDPWM3, the basic vectors are modified and the duty cycles are recalculated so that the distortion of output voltage is reduced. Consequently, the performance of the output current is improved, as shown in Figures 9 and 10.

**Figure 7.** Experimental results of DPWM0–DPWM3 under two-phase load conditions when m' = 0.3: (a) DPWM0; (b) DPWM1; (c) DPWM2 (d) DPWM3.

**Figure 8.** Experimental results of DPWM0–DPWM3 under two-phase load conditions when m' = 0.8: (a) DPWM0; (b) DPWM1; (c) DPWM2 (d) DPWM3.

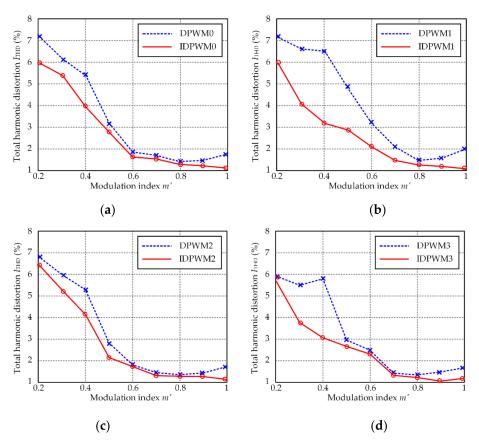

By using the fast fourier transformation (FFT) analysis tool in MATLAB, the total harmonic distortion of the output current ( $I_{THD}$ ) in the whole modulation range can be calculated on the basis of experimental results. Then variations of  $I_{THD}$  with the change of modulation index m' for DPWM0–DPWM3 and IDPWM0–IDPWM3 can be obtained, which are illustrated in Figure 11. For IDPWM1,  $I_{THD}$  is always considerably lower than that of DPWM1 in the whole modulation range, and  $I_{THD}$  is decreased by about 50% at most. While for IDPWM0, IDPWM2, and IDPWM3, the improvement is significant in the lower ( $m' \le 0.5$ ) and higher ( $m' \ge 0.8$ ) modulation range.

**Figure 9.** Experimental results of IDPWM0–IDPWM3 under two-phase load conditions when m' = 0.3: (a) IDPWM0; (b) IDPWM1; (c) IDPWM2 (d) IDPWM3.

**Figure 10.** Experimental results of IDPWM0–IDPWM3 under two-phase load conditions when m' = 0.8: (a) IDPWM0; (b) IDPWM1; (c) IDPWM2 (d) IDPWM3.

#### 4.2. Neutral-Point Voltage Ripple

From Figures 7 and 9, when m' = 0.3, the amplitude of the neutral-point voltage ripple for DPWM0–DPWM3 is 20–30 V. While for IDPWM0–IDPWM3, the amplitude is 10 V, the neutral-point voltage ripple is reduced by about 33–50% so that the suppression effect of neutral-point voltage ripple is obvious under lower modulation index conditions. As can be seen in Figures 8 and 10, when m' = 0.8, the amplitude of the neutral-point voltage ripple for DPWM0–DPWM3 is 12–15 V. While for IDPWM0–IDPWM3, the amplitude is 7–10 V. The suppression of neutral-point voltage ripple still works.

In conclusion, the output waveform quality of the inverter can be improved by IDPWM0–IDPWM3 under two-phase loads conditions, and the improvement is significant in lower and higher modulation range. Moreover, the neutral-point voltage ripple can also be suppressed by IDPWM0–IDPWM3 in the whole modulation range, and the suppression effect is remarkable under the lower modulation condition.

**Figure 11.** Variations of *I*<sub>THD</sub> with the change of *m*′ for DPWM0–DPWM3 and IDPWM0–IDPWM3: (a) DPWM0 and IDPWM0; (b) DPWM1 and IDPWM1; (c) DPWM2 and IDPWM2; (d) DPWM3 and IDPWM3.

### 5. Conclusions

Based on the conventional discontinuous PWM strategies for three-level traction inverter fed three-phase load, four improved discontinuous strategies under two-phase load conditions are proposed in this paper. The basic voltage vectors are modified and the duty cycles are re-calculated. Experimental results show that the output performance of the proposed strategies are better than that of the conventional strategies. Meanwhile, amplitudes of neutral-point voltage ripple for the proposed strategies are also lower than those of the conventional strategies.

**Author Contributions:** Conceptualization, G.Z. and Q.G.; methodology, G.Z., Z.W. and L.G.; software, Y.W.; validation, Y.W.; formal analysis, Z.Z.; writing—original draft preparation, Z.Z.; writing—review and editing, Z.W. and L.G.; funding acquisition, G.Z. and Q.G. All authors have read and agreed to the published version of the manuscript.

**Funding:** This research was funded by "The Youth Fund Project of National Natural Science Foundation of China, grant number 51807140" and "The Major Project of the Science & Technology Development Fund of Tianjin Education Commission for Higher Education, grant number 2019ZD09".

Conflicts of Interest: The authors declare no conflict of interest.

### References

- 1. Antonio, V.C.; Montero-Robina, P.; Umbría, F.; Cuesta, F.; Gordillo, F. Integrated control and modulation for three-level NPC rectifiers. *Energies* **2019**, *12*, 1641.

- 2. Li, P.; Zhang, L.; Ouyang, B.; Liu, Y. Nonlinear effects of three-level neutral-point clamped inverter on speed sensorless control of induction motor. *Energies* **2019**, *8*, 402. [CrossRef]

- 3. Jun, E.; Kwak, S. A highly efficient single-phase three-level neutral point clamped (NPC) converter based on predictive control with reduced number of commutations. *Energies* **2018**, *11*, 3524. [CrossRef]

- 4. Oto, Y.; Noguchi, T.; Fauziah, M.B. Experimental Verification of Fault Tolerant Operation Focusing on DC-Bus Battery Failure in Dual Inverter Motor Drive. *World Electr. Veh. J.* **2019**, *10*, 65. [CrossRef]

- 5. Mao, W.; Zhang, X.; Hu, Y.; Zhao, T.; Wang, F.; Li, F.; Cao, R. A research on cascaded H-bridge module level photovoltaic inverter based on a switching modulation strategy. *Energies* **2018**, *12*, 1851. [CrossRef]

- 6. Wei, C.; Yuan, X.; Zhou, J.; Wang, K.; Zhang, Y.; Wu, X. Voltage jump suppression and capacitor voltage fluctuation analysis for a four-level hybrid flying capacitor T-type converter. *Energies* **2018**, *12*, 698. [CrossRef]

- Hammami, M.; Rizzoli, G.; Mandrioli, R.; Grandi, G. Capacitors voltage switching ripple in three-phase three-level neutral point clamped inverters with self-balancing carrier-based modulation. *Energies* 2018, 11, 3244. [CrossRef]

- 8. Zhang, G.; Wei, B.; Gu, X.; Li, X.; Zhou, Z.; Chen, W. Sector Subdivision Based SVPWM Strategy of Neutral-Point-Clamped Three-Level Inverter for Current Ripple Reduction. *Energies* **2019**, *12*, 2734. [CrossRef]

- 9. Brucker, T.; Holmes, D. Optimal pulse-width modulation for three-level inverters. *Ieee Trans. Power Electron.* **2005**, *20*, 82–89. [CrossRef]

- Jiang, W.; Li, L.; Wang, J.; Ma, M.; Zhai, F.; Li, J. A Novel Discontinuous PWM Strategy to Control Neutral Point Voltage for Neutral Point Clamped Three-Level Inverter With Improved PWM Sequence. *Ieee Trans. Power Electron.* 2019, *34*, 9329–9341. [CrossRef]

- 11. Sarbani, M.; Santu, K.G.; Subrata, B. An Improved Adjustable Modulation Strategy for Three-Level NPC Inverters ConsideringDynamic Loading Applications. *IEEE Trans. Ind. Appl.* **2019**, *55*, 3915–3925.

- Tomaselli, L.C.; Lazzarin, T.B.; Martins, D.C.; Barbi, I. Application of the Vector Modulation in the Symmetrical Two-phase Induction Machine Drive. In In Proceedings of the 2005 IEEE 36th Power Electronics Specialists Conference, Recife, Brazil, 12–16 June 2005; pp. 1253–1258.

- Charumit, C.; Kinnares, V. Analogue space vector modulator for two-phase loads using a three-leg voltage source inverter. In In Proceedings of the 2008 IEEE International Conference on Robotics and Biomimetics, Bangkok, Thailand, 22–25 February 2009; pp. 1607–1612.

- 14. Charumit, C.; Kinnares, V. Carrier-based unbalanced phase voltage space vector PWM strategy for asymmetrical parameter type two-phase induction motor drives. *Trans. Electr. Power Syst. Res.* 2009, 79, 1127–1135. [CrossRef]

- 15. Kinnares, V.; Charumit, C. Modulating functions of space vector PWM for three-leg VSI fed unbalanced two-phase induction motors. *IEEE Trans. Power Electron.* **2009**, *24*, 1135–1139. [CrossRef]

- 16. Charumit, C.; Kinnares, V. Discontinuous SVPWM techniques of three-leg VSI-fed balanced two-phase loads for reduced switching losses and current ripple. *Ieee Trans. Power Electron.* **2015**, *30*, 2191–2204. [CrossRef]

- 17. Srirattanawichaikul, W. A generalized switching function-based discontinuous space vector modulation technique for unbalanced two-phase three-leg inverters. *Turk. J. Elec. Eng. Comp. Sci.* **2019**, 27, 1157–1171. [CrossRef]

- Charoensuksirikul, S.; Kumsuwan, Y. Discontinuous SVM technique for three-leg VSI fed balanced/unbalanced two-phase loads. In In Proceedings of the 2018 International Power Electronics Conference (IPEC-Niigata 2018-ECCE Asia), Niigata, Japan, 20–24 May 2018; pp. 2113–2120.

- Xia, C.; Zhang, G.; Yan, Y.; Gu, X.; Shi, T.; He, X. Discontinuous space vector PWM strategy of neutral-point-clamped three-level inverters for output current ripple reduction. *Ieee Trans. Power Electron.* 2017, 32, 5109–5121. [CrossRef]

© 2020 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).