Article

# Hysteresis in Lanthanide Aluminum Oxides Observed by Fast Pulse CV Measurement

Chun Zhao <sup>1,†</sup>, Ce Zhou Zhao <sup>1,2,\*</sup>, Qifeng Lu <sup>1</sup>, Xiaoyi Yan <sup>1,2</sup>, Stephen Taylor <sup>1</sup> and Paul R. Chalker <sup>3</sup>

- Department of Electrical Engineering and Electronics, University of Liverpool, Liverpool L69 3GJ, UK; E-Mails: chun.zhao@liverpool.ac.uk (C.Z.); qifeng@liverpool.ac.uk (Q.L.); xiaoyi.yan10@student.xjtlu.edu.cn (X.Y.); s.taylor@liverpool.ac.uk (S.T.)

- Department of Electrical and Electronic Engineering, Xi'an Jiaotong-Liverpool University, Suzhou 215123, China

- <sup>3</sup> Department of Materials Science and Engineering, University of Liverpool, Liverpool L69 3GH, UK; E-Mail: pchalker@liverpool.ac.uk

- † Present address: Nano & Advanced Materials Institute, Hong Kong University of Science and Technology, Hong Kong; E-Mail: garyzhao@ust.hk.

- \* Author to whom correspondence should be addressed; E-Mail: cezhou.zhao@xjtlu.edu.cn or cezhou@liverpool.ac.uk; Tel.: +86-512-8816-1408.

External Editor: Durga Misra

Received: 15 January 2014; in revised form: 29 September 2014 / Accepted: 8 October 2014 /

Published: 13 October 2014

**Abstract:** Oxide materials with large dielectric constants (so-called high-*k* dielectrics) have attracted much attention due to their potential use as gate dielectrics in Metal Oxide Semiconductor Field Effect Transistors (MOSFETs). A novel characterization (pulse capacitance-voltage) method was proposed in detail. The pulse capacitance-voltage technique was employed to characterize oxide traps of high-*k* dielectrics based on the Metal Oxide Semiconductor (MOS) capacitor structure. The variation of flat-band voltages of the MOS structure was observed and discussed accordingly. Some interesting trapping/detrapping results related to the lanthanide aluminum oxide traps were identified for possible application in Flash memory technology. After understanding the trapping/detrapping mechanism of the high-*k* oxides, a solid foundation was prepared for further exploration into charge-trapping non-volatile memory in the future.

**Keywords:** high-*k* dielectrics; lanthanide aluminum oxides; pulse capacitance-voltage (CV); oxide traps

#### 1. Introduction

If SiO<sub>2</sub> gate dielectric thickness is reduced below 1.4 nm, the resulting high gate leakage current levels due to electron tunneling effects become unacceptable for device reliability [1,2]. The decreasing sizes in complementary metal oxide semiconductor (CMOS) transistor technology required the replacement of SiO<sub>2</sub> with gate dielectrics that have a high dielectric constant (high-k) [3,4]. The equivalent oxide thickness (EOT) is the thickness of SiO<sub>2</sub> gate oxide needed to obtain the same gate capacitance as that obtained with thicker high-k dielectrics. Thicker equivalent oxide thickness, to reduce the leakage current of gate oxides, was obtained by introducing the high-k dielectric into real applications from 45 nm node technology. In recent years, various high-k gate dielectrics have been investigated to find suitable alternative materials [5-12]. Significant progress has been made on the screening and selection of high-k gate dielectrics, understanding their physical properties, and their integration into CMOS technology [13-20]. Now it is recognized that a large family of oxide-based materials emerges as candidates to replace SiO<sub>2</sub> gate dielectrics in advanced CMOS applications [21-26]. Among them are cerium oxide CeO<sub>2</sub> [27], cerium zirconate CeZrO<sub>4</sub> [28], gadolinium oxide Gd<sub>2</sub>O<sub>3</sub> [29], erbium oxide Er<sub>2</sub>O<sub>3</sub> [30], neodymium oxide Nd<sub>2</sub>O<sub>3</sub> [31], aluminum oxide Al<sub>2</sub>O<sub>3</sub> [32], lanthanum aluminum oxide LaAlO<sub>3</sub> [33], lanthanum oxide La<sub>2</sub>O<sub>3</sub> [34], yttrium oxide Y<sub>2</sub>O<sub>3</sub> [35], tantalum pentoxide Ta<sub>2</sub>O<sub>5</sub> [36], titanium dioxide TiO<sub>2</sub> [37], zirconium dioxide ZrO<sub>2</sub> [38], lanthanum doped zirconium oxide  $La_xZr_{1-x}O_{2-\delta}$  [39], hafnium oxide HfO<sub>2</sub> [40], HfO<sub>2</sub>-based oxides La<sub>2</sub>Hf<sub>2</sub>O<sub>7</sub> [41], Ce<sub>x</sub>Hf<sub>1-x</sub>O<sub>2</sub> [42], hafnium silicate HfSi<sub>x</sub>O<sub>v</sub> [43], and rare-earth scandates LaScO<sub>3</sub> [44], GdScO<sub>3</sub> [45], DyScO<sub>3</sub> [46], and SmScO<sub>3</sub> [47]. Excellent device results have been obtained using La<sub>2</sub>O<sub>3</sub> gate dielectric layers ( $k \sim 27$ ). with a 3.3 nm thick La<sub>2</sub>O<sub>3</sub> layer giving a SiO<sub>2</sub> EOT as low as 0.48 nm, together with very low leakage currents [48]. However, La<sub>2</sub>O<sub>3</sub> is chemically unstable and is easily converted to La(OH)<sub>3</sub> on reaction with ambient water. LaAlO<sub>3</sub> combines the advantages of the high permittivity of La<sub>2</sub>O<sub>3</sub> with the chemical and thermal stability of Al<sub>2</sub>O<sub>3</sub>. LaAlO<sub>3</sub> has a permittivity of 22–27, a large band gap (6.2 eV), and high band offsets on Si (1.8 eV for electrons and 3.2 eV for holes). Equivalent SiO<sub>2</sub> thicknesses as low as 0.9–1.1 nm have therefore been achieved using LaAlO<sub>3</sub>. Recently, to enhance the thermal stability is the incorporation of aluminum (Al) to develop innovative multifunctional advanced lanthanide aluminates-based ceramics, NdAlO<sub>3</sub> [49]. They remain amorphous up to high temperatures, leading to a large reduction in leakage current relative to poly-crystalline Nd<sub>2</sub>O<sub>3</sub> films during CMOS processing. Therefore, the lanthanide aluminates, MAlO<sub>3</sub> (M~La, Nd), are promising high-k materials for next generation CMOS applications.

The rapid growth of Flash memory technology has been motivated by the continuous downscaling of memory cells [50,51]. Starting from the advanced technology generation for charge-trapping Flash devices, the spacing between two adjacent gates became too narrow to arrange the metal gate to overlap the floating gate vertically in minimum feature-sized standard cells [52,53]. The introduction of high-k materials into floating-gate Flash memory has been proposed as a potential solution [54–56].

A fundamental understanding of the trap mechanism in new dielectric materials was critical for write/erase, retention and endurance properties of Flash memory [57–59]. Therefore, new ideas and approaches are required. These include: Negative-Bias Temperature Instability (NBTI), NBTI lifetime prediction, fast reliability screening and charge pumping techniques. These measurement techniques are required to understand of the underlying science of these dielectrics. Reliability degradation, defect loss, slowdown, and device lifetime enhancement, energy and spatial distribution, electron trapping and interface states, time-dependent defect variation were actively investigated for the high-*k* dielectrics for several years.

Prior to this paper, many novel measurement approaches were proposed for the next generation Flash memory since 2005 [60–68]. Various significant findings related to traps within the gate oxides were also reported [69–72]. In this paper, a novel electrical characterization of Metal Oxide Semiconductor (MOS) capacitance: pulse capacitance-voltage (CV), was proposed in detail. The accuracy and reliability of the pulse CV testing system was comprehensively verified and examined, and shown to be a powerful measurement method for dielectric characterization of high-*k* materials. Large hysteresis effects caused by oxide traps were observed in lanthanide aluminum oxides, which was critical for the development of the charge-trapping Flash memory in the future.

# 2. Experimental Section

High-k dielectrics, LaAlO<sub>3</sub>, NdAlO<sub>3</sub> thin films, were deposited on n-type Si (100) substrates using liquid injection atomic layer deposition (ALD), carried out on an Aixtron AIX 200FE AVD reactor (Aixtron, Herzogenrath, Germany) fitted with the "Trijet" liquid injector system. The LaAlO<sub>3</sub> thin films grown by ALD are all La deficient, with the La:Al ratio varying from 0.50 to 0.61 over the growth temperature range of 160–300 °C. As gas phase reactions are absent in ALD, the precursor is likely to remain intact until reaching the growth surface. It is therefore unsurprising that there is little variation in the La: Al ratio, although the reason for the La deficiency in the thin films is not known. The thickness of the LaAlO<sub>3</sub> thin film grown by ALD is 28 nm. Near stoichiometric NdAlO<sub>3</sub> thin films were grown by utilizing the single-source precursor [NdAl(OPri)6(PriOH)]2. Selected thin films were subjected to high-temperature (750–950 °C) post-deposition annealing (PDA) in pure nitrogen (N<sub>2</sub>) ambient for 60 s. Subsequently, a post-metallization forming gas anneal (FGA) was carried out at 400 °C for 30 min using H<sub>2</sub>:N<sub>2</sub> in the ratio 1:9, together with a control as-deposited sample. The high-k thickness and a thin native oxide interlayer, adjacent to the silicon substrate, changed from 11 and 1.5 nm, respectively, to 10.4 and 2.5 nm, respectively, after 950 °C PDA. This could be due to inter-diffusion of oxygen between SiO<sub>2</sub> and NdAlO<sub>3</sub>. Here, NdAlO<sub>3</sub> thin films samples discussed in the manuscript was after PDA. A thermal SiO<sub>2</sub> sample was grown using dry oxidation at 1100 °C to provide a comparison with the high-k stacks. MOS capacitors were fabricated by thermal evaporation of Au gates through a shadow mask with an effective area of  $4.9 \times 10^{-4}$  cm<sup>2</sup>. The backside contact of selected Si wafers was cleaned with a buffer HF solution and subsequently a 200 nm thickness of Al film was deposited on it by thermal evaporation.

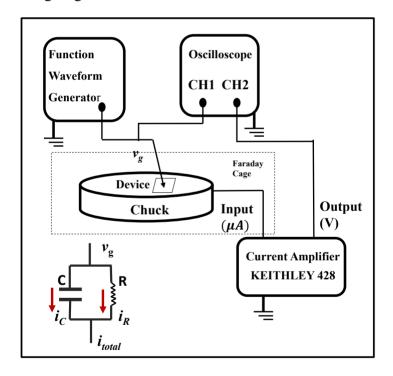

The pulse CV measurement system was developed and implemented to probe the MOS capacitor sample with high-k thin film, and its system structure chart is shown in Figure 1. We used a functional/arbitrary waveform generator to input a pulse voltage waveform ( $v_g$ ) for the sample. The related current through the sample ( $i_{total}$ ) was fed into a current amplifier and then was amplified as an

output voltage signal ( $v_{\text{CH2}}$ ). Channel two of the oscilloscope was used to track the output voltage, while the input pulse voltage waveform was monitored in channel one. There was no specific requirement for the oscilloscope model. Here, the DG1302 oscilloscope was employed. In terms of functional/arbitrary waveform generator, DG3061 (RIGOL, Beijing, China)/DG2041 (RIGOL)/HP8110 (Agilent, Santa Clara, CA, USA) could be implemented to produce pulse voltage. The Keithley 428 current amplifier (Keithley, Cleveland, OH, USA) was selected for the pulse CV measurement system. The symbol diagram of an under-testing device is also modeled in the inset of Figure 1. For MOS capacitor samples with the high-k thin film, we could make it simple as the parallel combination of a capacitor (C) and a resistor (R). Accordingly, the current flowing through the capacitor and resistor are  $i_C$  and  $i_R$ , respectively. Details are discussed in the following section.

**Figure 1.** Pulse capacitance-voltage (CV) measurement system structure chart. A functional/arbitrary waveform generator was implemented to generate the voltage pulse waveform. The current through the under-testing device was fed into a current amplifier and then was amplified as an output voltage signal. An oscilloscope was used to monitor the input and output voltage signals.

### 3. Results and Discussion

In order to verify the working principle behind the pulse CV measurement system, firstly, a discrete commercial ceramic capacitor with a near infinite resistance value was used to replace the MOS capacitor sample shown in Figure 1. The value of the capacitance component was below 1000 pF. Via the relation between voltage and current, the following formula is derived:

$$i_C(t) = \frac{v_{\text{CH2}}(t)}{A} = C \cdot \frac{dv_g(t)}{dt} \tag{1}$$

where  $v_{\text{CH2}}$  is the output voltage of the current amplifier (recoded by channel two of the oscilloscope).  $v_g$  is the input voltage of the sample. A is an amplification factor of the current amplifier and C is the capacitance value of the device under test. Re-arranging,  $v_{\text{CH2}}$  could be obtained:

$$v_{\rm CH2}(t) = A \cdot C \cdot \frac{dv_g(t)}{dt} \tag{2}$$

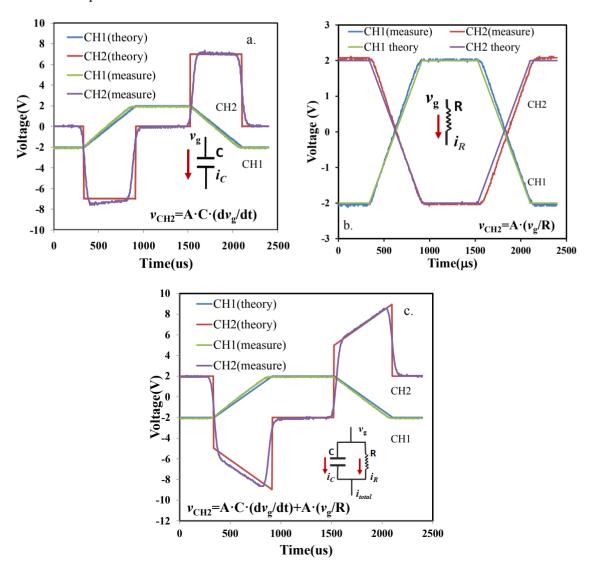

Based on the formula above, the theoretical  $v_{\text{CH2}}$  could be calculated as a reference to compare the measurement results. In Figure 2a, the measurement results from channel one (green) and channel two (purple) of the oscilloscope are presented. Following the derived formula, we plotted the theory data for channel one (blue) and channel two (red). Obviously, it was observed that the theory data fitted well with measurement results.

**Figure 2.** (a) Voltage (V) *versus* time ( $\mu$ s) of a discrete capacitor. (b) Voltage (V) *versus* time ( $\mu$ s) of a discrete resistor. (c) Voltage (V) *versus* time ( $\mu$ s) of a discrete capacitance parallel with a discrete resistance. CH1 denotes the input voltage waveform ( $\nu_g$ ), while CH2 represents the output voltage waveform ( $\nu_{CH2}$ ). Theory curves were presented based on formula calculation. Measurement data were recorded by channel 1 and channel 2 of the oscilloscope.

A discrete resistor with a resistance value *R* as the under testing device to replace the discrete commercial ceramic capacitor was then investigated. The current flowing through the resistor was given:

$$i_R(t) = \frac{v_{\text{CH2}}(t)}{A} = \frac{v_g(t)}{R} \tag{3}$$

$$v_{\text{CH2}}(t) = A \cdot \frac{v_{g(t)}}{R} \tag{4}$$

The comparison between theory and measurement is demonstrated in Figure 2b. Like the result of the discrete capacitance, we found the theory and measurement had an impressive consistency.

Finally, the parallel combination of the discrete capacitor and the discrete resistor was merged. The related formula was updated as:

$$i_{\text{total}}(t) = \frac{v_{\text{CH2}}(t)}{A} = i_C(t) + i_R(t) = C \cdot \frac{dv_g(t)}{dt} + \frac{v_g(t)}{R}$$

(5)

$$v_{\text{CH2}}(t) = A \cdot C \cdot \frac{dv_g(t)}{dt} + A \cdot \frac{v_g(t)}{R}$$

(6)

In Figure 2c, it was found that the theoretical calculation agreed well with measurement data. In summary, the working principle in terms of the pulse CV measurement system is mainly attributed to the current flowing through the device under test. In this paper, the measurement of MOS capacitance with parasitic resistance (usually the value was above 2  $M\Omega$ ) was the key issue.

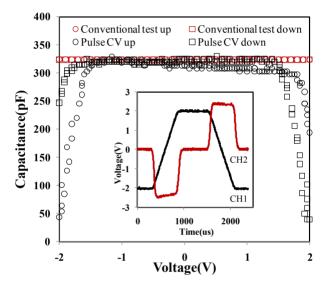

Before considering a MOS capacitance, the extracted capacitance data from a discrete capacitor should be fully understood. As an example, we tested a 330 pF discrete capacitor. From Equation (2) and an inset in Figure 3, the extracted CV graphs are shown in Figure 3, where we place the original voltage-time (VT) graphs as the inset. Pulse CV up/down (black) means that the CV results were extracted from the rise/fall edge of the input pulse on channel 1 in the inset. Before utilizing the pulse CV technique, a conventional CV test was commonly carried out via Agilent4275/4284 LCR meter (Agilent, Santa Clara, CA, USA). The related CV results (red) are presented in Figure 3. In the conventional test, up/down means the measurement starting from low/high to high/low voltage. The comparison was also made between the conventional test and the pulse CV measurement as shown in Figure 3. Besides high accuracy superposition, the CV curves from the pulse CV measurement need a rise to reach the true capacitance value within the voltage range from -2 to -1.5 V. Similarly, a fall from the true capacitance value was also observed within the range of 1.5–2 V. The phenomenon was mainly due to the response time of the oscilloscope and the capacitance charging and discharging issues. In consequence, the middle part of the full CV curves was preferred, which reflected the actual capacitance value of the discrete capacitor, like -1.5–1.5 V within the range of -2–2 V.

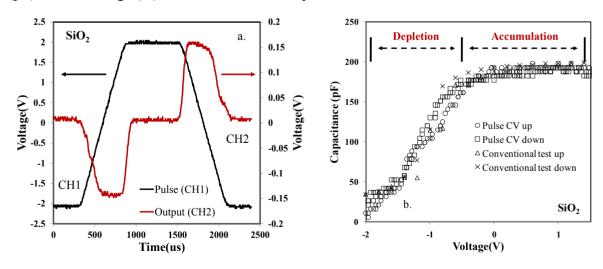

After the comparison between the conventional and pulse CV test for a discrete commercial ceramic capacitor, a thermal oxide (SiO<sub>2</sub>) MOS capacitor sample was investigated. Figure 4a shows the original VT data from both channel one and channel two of the oscilloscope. Calculated from the Equation (6), the related CV results are given in Figure 4b. Similarly, a conventional CV test was employed to compare with the new pulse CV technique. From Figure 4b, vertically the pulse CV and conventional CV results matched consistently. There was no variation either in accumulation or depletion region. Furthermore, horizontally there was no clear shift for the pulse and conventional CV test. This is because there were no significant traps located in the oxide layer of the thermal SiO<sub>2</sub> MOS system.

Therefore, it should be the case that no flat-band voltage shift was observed. In other words, the fast (pulse CV) and slow (conventional test) CV measurements were expected to be the same, which was supported by our finding shown in Figure 4b. It can be concluded that the pulse CV system is suitable for MOS capacitance measurement. This provides a convincing basis for investigation of more complicated MOS capacitors with high-*k* thin films.

**Figure 3.** Capacitance (pF) *versus* voltage (V) of a discrete capacitor. Inset: Voltage (V) *versus* time ( $\mu$ s) of a discrete capacitor using the pulse CV measurement. CH2 was used to extract the capacitance value. Conventional test up and pulse CV up:  $\nu_g$  forward from -2 to +2 V (the up trace). Conventional test down and pulse CV down:  $\nu_g$  backward from +2 to -2 V (the down trace).

**Figure 4.** (a) Voltage (V) *versus* time (μs) of a thermal SiO<sub>2</sub> MOS sample. (b) Capacitance (pF) *versus* voltage (V) of the SiO<sub>2</sub> MOS sample.

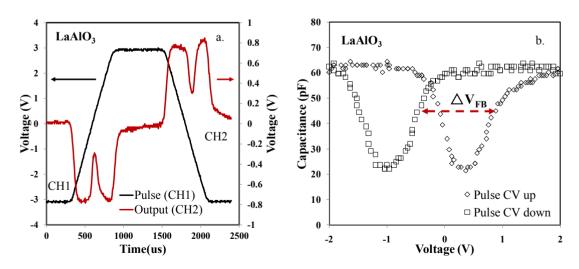

The high-k thin film of LaAlO<sub>3</sub> was now under research. The MOS capacitor samples with LaAlO<sub>3</sub> were probed using pulse CV technique. The VT results are shown in Figure 5a. Unlike the discrete capacitor and the SiO<sub>2</sub> MOS capacitors introduced before, there were two distinct peaks in channel two in the up (forward from -3 to +3 V) and down (backward from +3 to -3 V) trace of the input pulse,

respectively. When we did the extraction based on Equation (6) into CV results in Figure 5b, the distinct peaks indicated that a strong inversion occurred when frequency is low. The capacitance density in the accumulation region was  $1.27 \times 10^5 \text{ pF} \cdot \text{cm}^{-2}$ , when the electric field within the oxide is  $7.14 \times 10^7 \,\mathrm{V \cdot m^{-1}}$ . In the inversion region, an inversion layer exists at the silicon surface. In response to the low frequency analog continuous (AC) signal, inversion layer charges can be supplied and removed quickly enough to respond to changes with the gate AC signal voltage, and incremental charge is effectively added or subtracted at the surface of substrate. Most importantly, it was found that a clear horizontal voltage shift happened between the up and down trace. The shift was around 1.3 V. However, only a horizontal voltage shift of 0.4 V was observed in the same samples from the conventional CV test. It was proved that the pulse CV technique was more accurate to track traps in oxides, avoiding trapped electrons/holes recovering/detrapping within the testing time interval of the conventional CV test. The obvious horizontal voltage shift was induced by trapping and detrapping of electrons/holes between the up and down trace of channel one in Figure 5a. When the positive voltage (+3 V) is forced on the metal side, net positive charges induce a negative shift of the C-V curve. While, if a negative voltage (-3 V) is applied on the metal side, net negative charges cause a positive shift of the C-V curve. As a discussion, a possible explanation is that the shifts might be related to as-grown positive charges and as-grown electron traps. It was reported that there are as-grown fixed positive charges (oxygen vacancies) and as-grown electron traps in high-k oxides [57,73–75]. If both as-grown positive charges and as-grown electron traps in high-k oxides have a high energy level, when  $V_g < 0$ , the as-grown positive charges are compensated by electrons, which come from the metal gate and trapped into the as-grown traps; while when  $V_g > 0$ , electrons are detrapped to the metal gate through tunneling, which causes that (1) the net charges in the oxide are positive and then (2) the CV curve negatively shifts.

**Figure 5.** (a) Voltage (V) *versus* time (μs) of A LaAlO<sub>3</sub> sample. (b) Capacitance (pF) *versus* voltage (V) of the LaAlO<sub>3</sub> sample. In the pulse CV test, considerable flat-band voltage shift was observed.

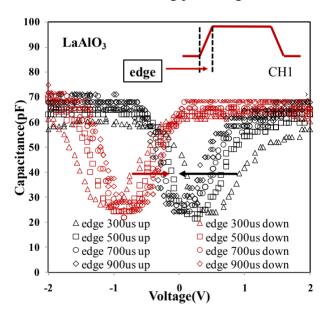

The impact of testing time on the horizontal shift of the CV curve was considered. In the pulse CV technique, edge time for both rise and fall of the voltage pulse was critical to estimate the trap density located in the oxide. The single pulse CV technique described in the paper can be used to accurately measure the charging-induced flat-band voltage shift. Furthermore, a two-pulse CV technique was

developed to measure the flat-band voltage shift caused by discharging the traps in dielectrics [63]. The rising and falling slopes of a pulse signal applied to the gate will give rise to a displacement current proportional to the capacitance and the pulse ramp rate (see Equation (1)). Less edge time means less test time among each voltage biases. The rise edge time is shown in the inset of Figure 6. When the edge time was increased to a relatively large value (~10 s), the test process of the pulse CV was equal to the conventional CV test carried out via a LCR meter. In Figure 6, it was observed that the flat-band voltage shift was narrowed with increasing edge time and it indicates that the flat-band voltage shift is partially recovered during the edge time of the pulse. Trapped electrons/holes recovering were sensitive to time. Therefore, the time-dependent trapping/detrapping should be probed by short edge time in the pulse CV measurement, which corresponds to shallower traps (traps at a high energy level within oxide), at least within the timescale considered here. While for the larger value of the edge time, the transient shift of the flat-band voltage shift is attributed to slow electron trapping/detrapping. It is also noted that all the ramp-down traces in Figure 6 are almost overlapped, suggesting that the total trapping level changes little during each charging process (positive bias induced). Similar results have been observed and confirmed by using the conventional CV measurement.

**Figure 6.** Capacitance (pF) *versus* voltage (V) of a LaAlO<sub>3</sub> sample. The variation of flat-band voltage was decreased with increasing pulse edge time.

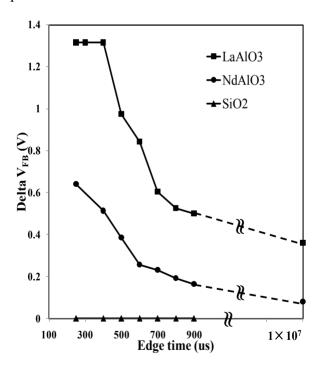

In order to figure out how edge time determines the flat-band voltage shift, two high-k materials (LaAlO<sub>3</sub> and NdAlO<sub>3</sub>) plus a thermal oxide were tested, as shown in Figure 7. By adjusting the edge time, the time-dependent trapping/detrapping was tracked correspondingly. Also, it provided a solution to estimate the entire density of net trapped charges within the oxide under specific edge time. For both high-k materials, variations of flat-band voltage were reduced with longer edge time. Due to the hardware limit of the waveform generator, the longest edge time was rated at 900  $\mu$ s. When the edge time reached  $1 \times 10^7$  s (10  $\mu$ s), the pulse CV method was supposed to be a type of conventional CV test. The data obtained via a LCR meter are also shown in Figure 7. It was found that for LaAlO<sub>3</sub> the variation of the flat-band voltage remained a constant when edge time is less than 400  $\mu$ s, which means that the entire density of the net trapped charges within the dielectric was measured if edge time is below 400  $\mu$ s. This is

because, once all as-grown electron traps were filled,  $V_{FB}$  would not shift further. The effective trapped charge density now is  $1.04 \times 10^{12}$  cm<sup>-2</sup> (=  $C_{ox}\Delta V_{FB}/q$ , where  $\Delta V_{FB} = 1.31$  V and  $C_{ox} = 1.27 \times 10^5$  pF·cm<sup>-2</sup> is the capacitance density in the accumulation region).  $\Delta V_{FB}$  did not return to its fresh value (0.4 V) even under 900 us of edge time, indicating that some electrons are still trapped within the high-k layer. From Figure 7, it was observed that traps of LaAlO<sub>3</sub> measured by the conventional CV method were less than 31% of the total trapping. Trapping is dominated by the high-k layer, which cannot be probed by charge pumping. The charging within 100 s is about 30% of the total, which will be missed if the slow quasi-dc techniques were used. In terms of NdAlO<sub>3</sub>,  $\Delta V_{FB}$  was recorded at 0.64 V as the largest value under the edge time of 200  $\mu$ s, with trap density of 1.14  $\times$  10<sup>12</sup> cm<sup>-2</sup> (where  $\Delta V_{FB} = 0.64$  V and  $C_{ox} = 2.86 \times 10^5 \,\mathrm{pF \cdot cm^{-2}}$ ). Similar to LaAlO<sub>3</sub>, the curve trend was also plotted downward and  $\Delta V_{FB}$  was close to the fresh value measured using the conventional CV technique. Within the edge time range of 400–700 µs, the slope rate of LaAlO<sub>3</sub> decreased more significantly than NdAlO<sub>3</sub>, which indicated that trapped electron detrapping was more sensitive to time. It is noted for NdAlO<sub>3</sub>,  $\Delta V_{FB}$  did not saturate even at the fastest testing speed of the pulse (200 µs). The entire density of net trapped charges shall be captured using a rapider pulse generator and higher measurement resolution. Concerning thermal oxide, there was no flat-band voltage variation under various edge times, which was also supported by the measurement shown in Figure 4b.

**Figure 7.** Variation of flat-band voltage (V) with different edging time (μs) of NdAlO<sub>3</sub>, LaAlO<sub>3</sub> and SiO<sub>2</sub> samples.

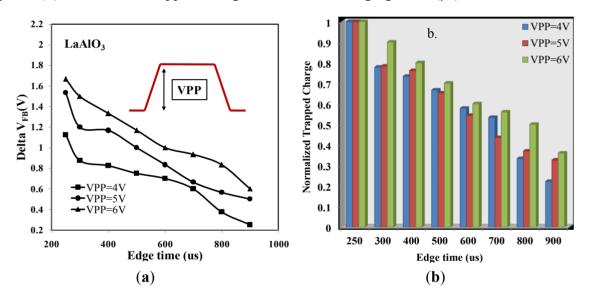

Finally, the variation of  $V_{PP}$  was investigated for LaAlO<sub>3</sub>, where  $V_{PP}$  denoted the peak to peak voltage of the pulse. When  $V_{PP}$  was 4 V, the pulse started from -2 to 2 V. The definition of  $V_{PP}$  could also be referred in the inset of Figure 8a. The relationship between  $\Delta V_{FB}$  and edge time under different  $V_{PP}$  levels was indicated in Figure 8a. It was observed that with stronger  $V_{PP}$  stress, the  $\Delta V_{FB}$  remained at a higher level. In all cases,  $\Delta V_{FB}$  almost linearly depends on  $V_{PP}$  and reaches a value of 1.67 V at a high voltage ( $V_{PP} = 6$  V), denoting a rather strong trapping process in the dielectric stacks. The effective trapped

charge density is  $1.33 \times 10^{12}$  cm<sup>-2</sup> (where  $\Delta V_{FB} = 1.67$  V and  $C_{ox} = 1.27 \times 10^5$  pF·cm<sup>-2</sup>), as  $V_{PP}$  equals to 6 V and edge time at 250 µs. Electron traps with deeper energy levels may exist in the bulk of the high-k layer, which can only be charged with larger gate bias. Slower ramp rates would cause more detrapping during the CV measurements, while higher ramp rates were limited by the trans-amplifier's bandwidth. Figure 8b shows the remaining traps during various edge times after taking the pre-existing traps into account. The pre-existing traps are time-independent and also termed as the whole traps. The normalized trapped charge and bar diagram are implemented in Figure 8b.

In general, following the procedure of the pulse CV test, it would be more convincing to characterize the trapping/detrapping mechanism of the electrons/holes in the high-*k* materials, which would be used for the development of the next generation non-volatile memory.

**Figure 8.** (a) Variation of Flat-band Voltage (V) with Different Edging Time (μs) of The LaAlO<sub>3</sub>, Samples under different VPP level. VPP denotes peak to peak voltage of the pulse. (b) Normalized Trapped Charge with Different Edging Time (μs).

# 4. Conclusions

In this paper, we have introduced a novel electrical characterization for MOS capacitors with high-*k* materials: pulse CV measurement. Different from the conventional CV test, the pulse CV technique could complete the whole test within 1 ms. By using the new technique, the testing time (edge time) and the bias/stress time (width time) could be easily adjusted. Compared to thermal oxides, MOS capacitors with high-*k* materials (like LaAlO<sub>3</sub> and NdAlO<sub>3</sub>) showed the intrinsic time-dependent trapping/detrapping mechanism via the pulse CV measurement. Various observations concerning the variation of flat-band voltage were discussed accordingly. After understanding the trapping/detrapping mechanism of the high-*k* oxides, the pulse CV technique might be a solid foundation for further exploration into charge-trapping, non-volatile memory based on high-*k* oxides in the coming future.

## Acknowledgments

This research was funded in part from the Engineering and Physical Science Research Council of UK under the grant EP/D068606/1, the National Natural and Science Foundation of China under the

grant no. 60976075 and 11375146, the Suzhou Science and Technology Bureau of China under the grant SYG201007 and SYG201223, and the Jiangsu Provincial Science and Technology Supporting Program under the grant BK2012636.

#### **Author Contributions**

Chun Zhao drafted the manuscript. Qifeng Lu and Xiaoyi Yan performed the experiment and extracted the data. Ce Zhou Zhao monitored and led the whole research project. Stephen Taylor and Paul R Chalker participated in the discussions. All of the authors read and approved the final manuscript.

#### **Conflicts of Interest**

The authors declare no conflict of interest.

#### References

- 1. Hoffman, J.; Pan, X.; Reiner, J.W.; Walker, F.; Han, J.P.; Ahn, C.H.; Ma, T.P. Ferroelectric field effect transistors for memory applications. *Adv. Mater.* **2010**, *22*, 2957–2961.

- 2. Wang, M.; He, W.; Ma, T.P. Electron tunneling spectroscopy study of traps in high-*k* gate dielectrics: Determination of physical locations and energy levels of traps. *Appl. Phys. Lett.* **2005**, *86*, doi:10.1063/1.1924893.

- 3. Zhu, W.J.; Han, J.-P.; Ma, T.P. Mobility measurement and degradation mechanisms of MOSFETs made with ultrathin high-*k* dielectrics. *IEEE Trans. Electron Devices* **2004**, *51*, 98–105.

- 4. Zhu, W.J.; Ma, T.P.; Tamagawa, T.; Kim, J.; Di, Y. Current transport in metal/hafnium oxide/silicon structure. *IEEE Electron Device Lett.* **2002**, *23*, 97–99.

- 5. Zhao, Y. Design of higher-*k* and more stable rare earth oxides as gate dielectrics for advanced CMOS devices. *Materials* **2012**, *5*, 1413–1438.

- 6. Tao, J.; Zhao, C.Z.; Zhao, C.; Taechakumput, P.; Werner, M.; Taylor, S.; Chalker, P.R. Extrinsic and intrinsic frequency dispersion of high-*k* materials in capacitance-voltage measurements. *Materials* **2012**, *5*, 1005–1032.

- 7. Reynolds, G.J.; Kratzer, M.; Dubs, M.; Felzer, H.; Mamazza, R. Electrical properties of thin-film capacitors fabricated using high temperature sputtered modified barium titanate. *Materials* **2012**, *5*, 644–660.

- 8. Suzuki, M. Comprehensive study of lanthanum aluminate high-dielectric-constant gate oxides for advanced CMOS devices. *Materials* **2012**, *5*, 443–477.

- 9. Reynolds, G.J.; Kratzer, M.; Dubs, M.; Felzer, H.; Mamazza, R. Sputtered modified barium titanate for thin-film capacitor applications. *Materials* **2012**, *5*, 575–589.

- 10. Miyata, N. Study of direct-contact HfO<sub>2</sub>/Si interfaces. *Materials* **2012**, *5*, 512–527.

- 11. Kidalov, S.V.; Shakhov, F.M. Thermal conductivity of diamond composites. *Materials* **2009**, *2*, 2467–2495.

- 12. Zhao, C.; Zhao, C.Z.; Werner, M.; Taylor, S.; Chalker, P.R. Dielectric relaxation of high-*k* oxides. *Nanoscale Res. Lett.* **2013**, *8*, doi:10.1186/1556-276X-8-456.

13. Zhao, C.; Zhao, C.Z.; Werner, M.; Taylor, S.; Chalker, P.R.; King, P. Grain size dependence of dielectric relaxation in cerium oxide as high-*k* layer. *Nanoscale Res. Lett.* **2013**, *8*, doi:10.1186/1556-276X-8-172.

- 14. Zhao, C.; Zhao, C.Z.; Tao, J.; Werner, M.; Taylor, S.; Chalker, P.R. Dielectric relaxation of lanthanide-based ternary oxides: Physical and mathematical models. *J. Nanomater.* **2012**, 2012, doi:10.1155/2012/241470.

- 15. Zhao, C.; Zhao, C.Z.; Werner, M.; Taylor, S.; Chalker, P.R. Advanced CMOS gate stack: Present research progress. *ISRN Nanotechnol.* **2012**, 2012, doi:10.5402/2012/689023.

- 16. Zhao, C.Z.; Werner, M.; Taylor, S.; Chalker, P.R.; Jones, A.C.; Zhao, C. Dielectric relaxation of la-doped zirconia caused by annealing ambient. *Nanoscale Res. Lett.* **2011**, *6*, doi:10.1007/s11671-010-9782-z.

- 17. Taechakumput, P.; Zhao, C.Z.; Taylor, S.; Werner, M.; Chalker, P.R.; Gaskell, J.M.; Aspinall, H.C.; Jones, A.C.; Chen, S.S. Thermal stability of neodymium aluminates high-*k* dielectric deposited by liquid injection MOCVD using single-source heterometallic alkoxide precursors. *J. Nanomater*. **2012**, *2012*, doi:10.1155/2012/891079.

- 18. Zhao, C.Z.; Taylor, S.; Werner, M.; Chalker, P.R.; Murray, R.T.; Gaskell, J.M.; Jones, A.C. Dielectric relaxation of lanthanum doped zirconium oxide. *J. Appl. Phys.* **2009**, *105*, doi:10.1063/1.3078038.

- 19. Zhao, C.Z.; Taylor, S.; Werner, M.; Chalker, P.R.; Gaskell, J.M.; Jones, A.C. Frequency dispersion and dielectric relaxation of La<sub>2</sub>Hf<sub>2</sub>O<sub>7</sub>. *J. Vac. Sci. Technol. B* **2009**, *27*, 333–337.

- 20. Zhao, C.Z.; Taylor, S.; Werner, M.; Chalker, P.R.; Potter, R.J.; Gaskell, J.M.; Jones, A.C. High-*k* materials and their response to gamma ray radiation. *J. Vac. Sci. Technol. B Microelectron. Nanometer Struct.* **2009**, *27*, 411–415.

- 21. Werner, M.; King, P.J.; Hindley, S.; Romani, S.; Mather, S.; Chalker, P.R.; Williams, P.A.; van den Berg, J.A. Atomic layer deposition of Ti-HfO<sub>2</sub> dielectrics. *J. Vac. Sci. Technol. A* **2013**, *31*, doi:10.1116/1.4748570.

- 22. Mather, S.; Sedghi, N.; Althobaiti, M.; Mitrovic, I.Z.; Dhanak, V.; Chalker, P.R.; Hall, S. Low EOT GeO<sub>2</sub>/Al<sub>2</sub>O<sub>3</sub>/HfO<sub>2</sub> on Ge substrate using ultrathin Al deposition. *Microelectron. Eng.* **2013**, *109*, 126–128.

- 23. King, P.J.; Werner, M.; Chalker, P.R.; Jones, A.C.; Aspinall, H.C.; Basca, J.; Wrench, J.S.; Black, K.; Davies, H.O.; Heys, P.N. Effect of deposition temperature on the properties of CeO<sub>2</sub> films grown by atomic layer deposition. *Thin Solid Films* **2011**, *519*, 4192–4195.

- 24. Chalker, P.R.; Marshall, P.A.; King, P.J.; Dawson, K.; Romani, R.; Williams, P.A.; Ridealgh, J.; Rosseinsky, M.J. Atomic layer deposition of germanium-doped zinc oxide films with tuneable ultraviolet emission. *J. Mater. Chem.* **2012**, *22*, 12824–12829.

- 25. Yan, L.; Xu, Z.L.; Grygiel, C.; McMitchell, S.R.C.; Suchomel, M.R.; Bacsa, J.; Clark, J.H.; Niu, H.J.; Romani, S.; Palgrave, R.G.; *et al.* SrHf(0.67)Ti(0.33)O(3) high-*k* films deposited on Si by pulsed laser deposition. *Appl. Phys. A Mater. Sci. Process.* **2011**, *104*, 447–451.

- 26. Moram, M.A.; Zhang, Y.; Joyce, T.B.; Holec, D.; Chalker, P.R.; Mayrhofer, P.H.; Kappers, M.J.; Humphreys, C.J. Structural properties of wurtzitelike ScGaN films grown by NH<sub>3</sub>-molecular beam epitaxy. *J. Appl. Phys.* **2009**, *106*, 113533:1–113533:6.

27. Aspinall, H.C.; Bacsa, J.; Jones, A.C.; Wrench, J.S.; Black, K.; Chalker, P.R.; King, P.J.; Marshall, P.; Werner, M.; Davies, H.O.; Odedra, R. Ce(IV) complexes with donor-functionalized alkoxide ligands: Improved precursors for chemical vapor deposition of CeO<sub>2</sub>. *Inorg. Chem.* **2011**, *50*, 11644–11652.

- 28. Gross, M.S.; Ulla, M.A.; Querini, C.A. Catalytic oxidation of diesel soot: New characterization and kinetic evidence related to the reaction mechanism on K/CeO<sub>2</sub> catalyst. *Appl. Catal. A* **2009**, *360*, 81–88.

- 29. Pan, T.M.; Liao, C.S.; Hsu, H.H.; Chen, C.L.; Lee, J.D.; Wang, K.T.; Wang, J.C. Excellent frequency dispersion of thin gadolinium oxide high-*k* gate dielectrics. *Appl. Phys. Lett.* **2005**, *87*, 262908:1–262908:3.

- 30. Liu, C.H.; Pan, T.M.; Shu, W.H.; Huang, K.C. Physical and electrical properties of Ti-doped Er<sub>2</sub>O<sub>3</sub> films for high-*k* gate dielectrics. *Electrochem. Solid-State Lett.* **2007**, *10*, 54–57.

- 31. Anthony, J.; Aspinall, H.C.; Chalker, P.R.; Potter, R.J.; Manning, T.D.; Loo, Y.F.; O'Kane, R.; Gaskell, J.M.; Smith, L.M. MOCVD and ALD of high-*k* dielectric oxides using Alkoxide precursors. *Chem. Vapor Depos.* **2006**, *12*, 83–98.

- 32. Adamopoulos, G.; Thomas, S.; Bradley, D.D.; McLachlan, M.A.; Anthopoulos, T.D. Low-voltage ZnO thin-film transistors based on Y<sub>2</sub>O<sub>3</sub> and Al<sub>2</sub>O<sub>3</sub> high-*k* dielectrics deposited by spray pyrolysis in air. *Appl. Phys. Lett.* **2011**, *98*, 123503:1–123503:3.

- 33. Lu, X.B.; Liu, Z.G.; Zhang, X.; Huang, R.; Zhou, H.W.; Wang, X.P.; Nguyen, B.Y. Investigation of high-quality ultra-thin LaAlO<sub>3</sub> films as high-*k* gate dielectrics. *J. Phys. D Appl. Phys.* **2003**, *36*, doi:10.1088/0022-3727/36/23/027.

- 34. Gougousi, T.; Kelly, M.J.; Terry, D.B.; Parsons, G.N. Properties of La-silicate high-*k* dielectric films formed by oxidation of La on silicon. *J. Appl. Phys.* **2003**, *93*, 1691–1696.

- 35. Mahata, C.M.; Bera, K.; Das, T.; Mallik, S.; Hota, M.K.; Majhi, B.; Verma, S.; Bose, P.K.; Maiti, C.K. Charge trapping and reliability characteristics of sputtered Y<sub>2</sub>O<sub>3</sub> high-*k* dielectrics on N- and S-passivated germanium. *Semicond. Sci. Technol.* **2009**, *24*, doi:10.1088/0268-1242/24/8/085006.

- 36. Pan, T.M.; Lei, T.F.; Chao, T.S.; Chang, K.L.; Hsieh, K.C. High quality ultrathin CoTiO<sub>3</sub> high-*k* gate dielectrics. *Electrochem. Solid-State Lett.* **2000**, *3*, 433–434.

- 37. Kim, S.K.; Kim, K.M.; Kwon, O.S.; Lee, S.W.; Jeon, C.B.; Park, W.Y.; Hwang, C.S.; Jeong, J. Structurally and electrically uniform deposition of high-*k* TiO<sub>2</sub> thin films on a Ru electrode in three-dimensional contact holes using atomic layer deposition. *Electrochem. Solid-State Lett.* **2005**, 8, F59–F62.

- 38. Adamopoulos, G.; Thomas, S.; Wöbkenberg, P.H.; Bradley, D.D.; McLachlan, M.A.; Anthopoulos, T.D. High-mobility low-voltage ZnO and Li-doped ZnO transistors based on ZrO<sub>2</sub> high-*k* dielectric grown by spray pyrolysis in ambient air. *Adv. Mater.* **2011**, *23*, 1894–1898.

- 39. Gaskell, J.M.; Jones, A.C.; Chalker, P.R.; Werner, M.; Aspinall, H.C.; Taylor, S.; Taechakumput, P.; Heys, P.N. Deposition of lanthanum zirconium oxide high-*k* films by liquid injection ALD and MOCVD. *Chem. Vapor Depos.* **2007**, *13*, 684–690.

- 40. Gutowski, M.; Jaffe, J.E.; Liu, C.L.; Stoker, M.; Hegde, R.I.; Rai, R.S.; Tobin, P.J. Thermodynamic stability of high-*k* dielectric metal oxides ZrO<sub>2</sub> and HfO<sub>2</sub> in contact with Si and SiO<sub>2</sub>. *Appl. Phys. Lett.* **2002**, *80*, 1897–1899.

41. Dimoulas, A.; Vellianitis, G.; Mavrou, G.; Apostolopoulos, G.; Travlos, A.; Wiemer, C.; Fanciulli, M.; Rittersma, Z.M. La<sub>2</sub>Hf<sub>2</sub>O<sub>7</sub> high-*k* gate dielectric grown directly on Si (001) by molecular-beam epitaxy. *Appl. Phys. Lett.* **2004**, *85*, 3205–3207.

- 42. Gang, H.; Deng, B.; Sun, Z.Q.; Chen, X.S.; Liu, Y.M.; Zhang, L.D. CVD-derived Hf-based High-k Gate Dielectrics. *Crit. Rev. Solid State Mater. Sci.* **2013**, *38*, 235–261.

- 43. Watanabe, H.; Saitoh, M.; Ikarashi, N.; Tatsumi, T. High-quality HfSixOy gate dielectrics fabricated by solid phase interface reaction between physical-vapor-deposited metal-Hf and SiO<sub>2</sub> underlayer. *Appl. Phys. Lett.* **2004**, *85*, 449–451.

- 44. Darbandy, G.; Ritzenthaler, R.; Lime, F.; Garduño, I.; Estrada, M.; Cerdeira, A.; Iñiguez, B. Analytical modeling of direct tunneling current through gate stacks for the determination of suitable high-*k* dielectrics for nanoscale double-gate MOSFETs. *Semicond. Sci. Technol.* **2011**, *26*, doi:10.1088/0268-1242/26/4/045002.

- 45. Myllymäki, P.; Roeckerath, M.; Putkonen, M.; Lenk, S.; Schubert, J.; Niinistö, L.; Mantl, S. Characterization and electrical properties of high-*k* GdScO<sub>3</sub> thin films grown by atomic layer deposition. *Appl. Phys. A* **2007**, *88*, 633–637.

- 46. Chan, K.C.; Lee, P.F.; Li, D.F.; Dai, J.Y. Memory characteristics and the tunneling mechanism of Au nanocrystals embedded in a DyScO<sub>3</sub> high-*k* gate dielectric layer. *Semicond. Sci. Technol.* **2011**, *26*, doi:10.1088/0268-1242/26/2/025015.

- 47. Milanov, A.P.; Xu, K.; Cwik, S.; Parala, H.; de los Arcos, T.; Becker, H.W.; Devi, A. Sc<sub>2</sub>O<sub>3</sub>, Er<sub>2</sub>O<sub>3</sub>, and Y<sub>2</sub>O<sub>3</sub> thin films by MOCVD from volatile guanidinate class of rare-earth precursors. *Dalton Trans.* **2012**, *41*, 13936–13947.

- 48. Gaskell, J.M.; Jones, A.C.; Aspinall, H.C.; Przybylak, S.; Chalker, P.R.; Black, K.; Davies, H.O.; Taechakumput, P.; Taylor, S.; Critchlow, G.W. Liquid injection ALD and MOCVD of lanthanum aluminate using a bimetallic alkoxide precursor. *J. Mater. Chem.* **2006**, *16*, 3854–3860.

- 49. Gaskell, J.M.; Przybylak, S.; Jones, A.C.; Aspinall, H.C.; Chalker, P.R.; Black, K.; Potter, R.J.; Taechakumput, P.; Taylor, S. Deposition of Pr- and Nd-aluminate by liquid injection MOCVD and ALD using single-source heterometallic alkoxide precursors. *Chem. Mater.* **2007**, *19*, 4796–4803.

- 50. Ma, T.P.; Han, J.P. Why is nonvolatile ferroelectric memory field-effect transistor still elusive? *IEEE Electron Device Lett.* **2002**, *23*, 386–388.

- 51. She, M.; King, T.J.; Hu, C.M.; Zhu, W.J.; Luo, Z.J.; Han, J.P.; Ma, T.P. JVD silicon nitride as tunnel dielectric in p-channel flash memory. *IEEE Electron Device Lett.* **2002**, *23*, 91–93.

- 52. Lee, C.H.; Hur, S.H.; Shin, Y.C.; Choi, J.H.; Park, D.G.; Kim, K. Charge-trapping device structure of dielectric for high-density flash memory. *Appl. Phys. Lett.* **2005**, *86*, doi:10.1063/1.1897431.

- 53. Lee, C.H.; Park, K.C.; Kim, K. Charge-trapping memory cell of SiO<sub>2</sub>/SiN/high-*k* dielectric Al<sub>2</sub>O<sub>3</sub> with TaN metal gate for suppressing backward-tunneling effect. *Appl. Phys. Lett.* **2005**, 87, 073510:1–073510:3.

- 54. Zhang, G.; Wang, L.K.; Won, J.Y.; Li, M.F. Spatial distribution of charge traps in a SONOS-type Flash memory using a high-*k* trapping layer. *IEEE Trans. Electron Devices* **2007**, *54*, 3317–3324.

- 55. You, H.W.; Cho, W.J. Charge trapping properties of the HfO<sub>2</sub> layer with various thicknesses for charge trap flash memory applications. *Appl. Phys. Lett.* **2009**, *96*, 093506:1–093506:3.

- 56. Lu, C.Y.; Hsieh, K.Y.; Liu, R. Future challenges of flash memory technologies. *Microelectron. Eng.* **2009**, *86*, 283–286.

57. Zhao, C.Z.; Zhang, J.F.; Groeseneken, G.; Degraeve, R. Hole-traps in silicon dioxides—Part II: Generation mechanism. *IEEE Trans. Electron Devices* **2004**, *51*, 1274–1280.

- 58. Zhao, C.Z.; Zhang, J.F. Effects of hydrogen on positive charges in gate oxides. *J. Appl. Phys.* **2005**, 97, doi:10.1063/1.1882771.

- 59. Zhao, C.Z.; Zhang, J.F.; Zahid, M.B.; Groeseneken, G.; Degraeve, R.; de Gendt, S. Impact of gate materials on positive charge formation in HfO<sub>2</sub>/SiO<sub>2</sub> stacks. *Appl. Phys. Lett.* **2006**, *89*, doi:10.1063/1.2220484.

- 60. Young, C.D.; Zeitzoff, P.; Brown, A.; Bersuker, G.; Lee, B.H.; Hauser, J.R. Intrinsic mobility evaluation of high-*k* gate dielectric transistors using pulsed I<sub>d</sub>-V<sub>g</sub>. *IEEE Electron Device Lett.* **2005**, 26, 586–589.

- 61. Bersuker, G.; Zeitzoff, P.; Sim, J.H.; Lee, B.H.; Choi, R.; Brown, G.; Young, C.D. Mobility evaluation in transistors with charge-trapping gate dielectrics. *Appl. Phys. Lett.* **2005**, *87*, doi:10.1063/1.1995956.

- 62. Puzzilli, G.; Govoreanu, B.; Irrera, F.; Rosmeulenb, M.; van Houdt, J. Characterization of charge trapping in SiO<sub>2</sub>/Al<sub>2</sub>O<sub>3</sub> dielectric stacks by pulsed C-V technique. *Microelectron. Reliab.* **2007**, *47*, 508–512.

- 63. Zhang, W.D.; Govoreanu, B.; Zheng, X.F.; Aguado, D.R.; Rosmeulen, M.; Blomme, P.; Zhang, J.F.; van Houdt, J. Two-pulse C-V: A new method for characterizing electron traps in the bulk of SiO<sub>2</sub>/high-*k* dielectric stacks. *IEEE Electron Device Lett.* **2008**, *29*, 1043–1046.

- 64. Zheng, X.F.; Zhang, W.D.; Govoreanu, B.; Aguado, D.R.; Zhang, J.F.; van Houdt, J. Energy and spatial distributions of electron traps throughout SiO<sub>2</sub>/Al<sub>2</sub>O<sub>3</sub> stacks as the IPD in flash memory application. *IEEE Trans. Electron Devices* **2010**, *57*, 288–296.

- 65. Zheng, X.F.; Zhang, W.D.; Govoreanu, B.; Zhang, J.F.; van Houdt, J. A new multi-pulse technique for probing electron trap energy distribution in high-kappa materials for Flash memory application. *IEEE Trans. Electron Devices* **2010**, *57*, 2484–2492.

- 66. ManjulaRani, K.N.; Ramgopal Rao, V.; Vasi, J. A new method to characterize border traps in submicron transistors using hysteresis in the drain current. *IEEE Trans. Electron Devices* **2003**, *50*, 973–979.

- 67. Degraeve, R.; Cho, M.; Govoreanu, B.; Kaczer, B.; Zahid, M.B.; van Houdt, J.; Jurczak, M.; Groeseneken, G. Trap spectroscopy by charge injection and sensing (TSCIS): A quantitative electrical technique for studying defects in dielectric stacks. In Proceedings of the IEEE International Electron Devices Meeting (IEDM), San Francisco, CA, USA, 15–17 December 2008.

- 68. Sun, X.; Xu, N.; Xue, F.; Alian, A.; Andrieu, F.; Nguyen, B.Y.; Poiroux, T.; Faynot, O.; Lee, J.; Cui, S.; Ma, T.P. AC transconductance: A novel method to characterize oxide traps in advanced FETs without a body contact. In Proceedings of the IEEE International Electron Devices Meeting IEDM, San Francisco, CA, USA, 10–13 December 2012.

- 69. Zheng, X.F.; Robinson, C.; Zhang, W.D.; Zhang, J.F.; Govoreanu, B.; van Houdt, J. Electron trapping in HfAlO high-kappa stack for Flash memory applications: An origin of V<sub>th</sub> window closure during cycling operations. *IEEE Trans. Electron Devices* **2011**, *58*, 1344–1351.

- 70. Benbakhti, B.; Zhang, J.F.; Ji, Z.; Zhang, W.; Mitard, J.; Kaczer, B.; Groeseneken, G.; Hall, S.; Chalker, P.; Robertson, J. Characterization of electron traps in Si-capped Ge MOSFETs with HfO<sub>2</sub>/SiO<sub>2</sub> gate stack. *IEEE Electron Device Lett.* **2012**, *33*, 1681–1683.

71. Duan, M.; Zhang, J.F.; Ji, Z.; Zhang, W.; Kaczer, B.; de Gendt, S.; Groeseneken, G. Defect loss: A new concept for reliability of MOSFETs. *IEEE Electron Device Lett.* **2012**, *33*, 480–482.

- 72. Tang, B.; Robinson, C.; Zhang, W.D.; Zhang, J.F.; Degraeve, R.; Blomme, P.; Toledano-Luque, M.; van den Bosch, G.; Govoreanu, B.; van Houdt, J. Read and pass disturbance in the programmed states of floating gate flash memory cells with high-*k* interpoly gate dielectric stacks. *IEEE Trans. Electron Devices* **2013**, *60*, 2261–2267.

- 73. Zhao, C.Z.; Zahid, M.B.; Zhang, J.F.; Groeseneken, G.; Degraeve, R.; de Gendt, S. Threshold voltage instability of *p*-channel metal-oxide-semiconductor field effect transistors with hafnium based dielectrics. *Appl. Phys. Lett.* **2007**, *90*, 143502:1–143502:3.

- 74. Zhang, J.F.; Zhao, C.Z.; Zahid, M.B.; Groeseneken, G.; Degraeve, R.; de Gendt, S. An assessment of the location of as-grown electron traps in HfO<sub>2</sub>/HfSiO stacks. *IEEE Electron Device Lett.* **2006**, *27*, 817–820.

- 75. Zhao, C.Z.; Zhang, J.F.; Chang, M.H.; Peaker, A.R.; Hall, S.; Groeseneken, G.; Pantisano, L.; de Gendt, S.; Heyns, M. Stress-induced positive charge in hf-based gate dielectrics: Impact on device performance and a framework for the defect. *IEEE Trans. Electron Device* **2008**, *55*, 1647–1655.

- © 2014 by the authors; licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution license (http://creativecommons.org/licenses/by/4.0/).