Article

# Low-Frequency Noise-Based Mechanism Analysis of Endurance Degradation in $Al/\alpha TiO_x/Al$ Resistive Random Access Memory Devices

Jung-Kyu Lee \*, Juyeong Pyo and Sungjun Kim \*

Division of Electronics and Electrical Engineering, Dongguk University, Seoul 04620, Republic of Korea \* Correspondence: jungkyu0712@gmail.com or lemoneia@naver.com (J.-K.L.); sungjun@dongguk.edu (S.K.)

**Abstract:** In this work, we analyze a resistive switching random access memory (RRAM) device with the metal–insulator–metal structure of  $Al/\alpha TiO_x/Al$ . The transport mechanism of our RRAM device is trap-controlled space-charge limited conduction, which does not change during the endurance test. As the number of resistive switching (RS) cycles increases, the current in the low-resistance state (LRS) does not change significantly. In contrast, degradation in the high-resistance state (HRS) is noticeably evident. According to the RS cycle, the current shift fits well with the stretched-exponential equation. The normalized noise power spectral density  $(S_i/I^2)$  measured in the HRS is an order of magnitude higher than that in the LRS owing to the difference in the degree of trap occupancy, which is responsible for the transition of resistance states. During the consecutive RS, the  $S_i/I^2$  in the HRS rapidly decreases for approximately 100 cycles and then saturates. In contrast, in the LRS, the  $S_i/I^2$  does not change significantly. Here we propose a model associated with the endurance degradation of the experimental device, and the model is verified with a 1/f noise measurement.

**Keywords:** resistive switching; RRAM; Al/ $\alpha$ TiO<sub>x</sub>/Al; degradation; low-frequency noise; noise power spectral density; 1/f noise

# updates

check for

Citation: Lee, J.-K.; Pyo, J.; Kim, S. Low-Frequency Noise-Based Mechanism Analysis of Endurance Degradation in Al/ $\alpha$ TiO<sub>x</sub>/Al Resistive Random Access Memory Devices. *Materials* **2023**, *16*, 2317. https://doi.org/10.3390/ma16062317

Academic Editor: Rene A. Castro Arata

Received: 1 February 2023 Revised: 6 March 2023 Accepted: 9 March 2023 Published: 14 March 2023

Copyright: © 2023 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

# 1. Introduction

To apply information and communication technology such as artificial intelligence, augmented reality, virtual reality, and self-driving to our daily life, data are expected to be generated three times more than the current level [1–3]. In addition, as services, including telecommuting, web conferences, and streaming, have proliferated around the globe due to COVID-19, data usage will increase further. According to the statistics from international data corporations, the total amount of global data is expected to reach 175 ZB by 2025 [3]. Hence, if the demand for memory performance and capacity surges due to the explosive increase in data, the "memory wall" between the NAND flash and dynamic random access memory (DRAM), which are the current major memory technologies, will also reach an extreme [4–6]. Therefore, to solve the "memory wall" caused by the performance gap between the DRAM and NAND flash memory, there is an increasing need for universal memory that can implement the functions of storage memory (high density and non-volatile) and working memory (high speed) at the same time [1,7]. In recent decades, resistive switching random access memory (RRAM) has received much attention as an emerging non-volatile memory (NVM) technology because of CMOS-compatible materials, simple cell structure, good scalability (<10 nm), low switching current (~nA), and 3D integration [8–10]. In addition, recently, in advanced computing technologies for neuromorphic systems, RRAM has also attracted great attention as one of the promising candidates for synaptic electronics for the hardware implementation of artificial neural networks owing to its non-volatility, repeatable analog switching with good precision, and the potential for large-scale integration with the crossbar array structure [11–13]. Although great progress has been made recently, research on RRAM still faces some significant challenges, such as the broad distribution

Materials 2023, 16, 2317 2 of 9

of the switching parameters (V<sub>forming</sub>, V<sub>set</sub>, V<sub>reset</sub>, R<sub>HRS</sub>, and R<sub>LRS</sub>), retention failure, and endurance degradation [14–16]. These issues with the device reliability stem from intrinsic variability because the resistive switching (RS) mechanism of RRAM itself is fundamentally stochastic. Consequently, a prerequisite to the successful application of RRAM is understanding the underlying physical mechanism associated with the reliability issues in RRAM. Chen et al. reported the physical mechanisms of endurance degradation in transition metal oxide-RRAM [17]. Three failure modes were experimentally identified: (1) resistive window (RW) collapse with decreased R<sub>HRS</sub> (high resistance) and increased R<sub>LRS</sub> (low resistance), (2) sudden stochastic RESET failure, and (3) gradual loss of the RW with a steady decrease in R<sub>HRS</sub>. Unfortunately, applying the mechanism associated with endurance failure behaviors is restricted to the filamentary RRAM. Therefore, a systematic study on the mechanism of endurance degradation in the interfacial RRAM is required, but little research has been conducted so far. It has already been verified in previous studies that low-frequency noise (LFN) measurements can be used as a useful tool for analyzing RRAM, such as the nature and information of the traps, the current transport, and the RS mechanism [18-21]. In this work, we investigate the physical mechanism of endurance degradation in an Al/ $\alpha$ TiO<sub>x</sub>/Al interfacial RRAM device by using the LFN measurement. The RS phenomenon of the  $\alpha TiO_x$  was reported by Argall in 1986 [22]. Since then, there have been many studies on the RS mechanism related to the NVM applications [23–25]. Recently, Jang et al. reported a learning-rate modulable and reliable TiO<sub>x</sub> memristor array for robust, fast, and accurate neuromorphic computing [13]. In particular, interfacial RRAMs have the forming-free and gradual set/reset characteristics, which can reduce additional power consumption and are advantageous for the symmetry/linearity of conductivity changes, unlike filament RRAMs [26-30]. Therefore, our study on the degradation mechanism analysis for the optimization of Al/ $\alpha$ TiO<sub>x</sub>/Al interfacial RRAM is a very valuable work. The result of the noise analysis can be direct evidence of the physical origin of the endurance failure because its characteristic is utilized to analyze the internal physics of electronics at the defect level [31,32].

# 2. Materials and Methods

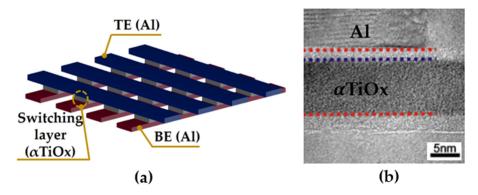

Figure 1a shows the schematic structure of our experimental device. We fabricated the interfacial RRAM device with the metal–insulator–metal structure of Al/ $\alpha$ TiO $_x$ /Al to investigate the physical mechanism of endurance degradation. The fabrication process is described as follows. A TiO $_x$  film with a thickness of ~8 nm was deposited on a 50 nm thick Al/SiO $_2$ /Si substrate by a plasma-enhanced atomic layer deposition at a substrate temperature of 180 °C. Titanium tetra-iso-propoxide (TTIP) and oxygen plasma were used as the Ti and oxygen precursors, respectively. The 50 nm thick aluminum bottom and top electrodes were deposited by a thermal evaporation method, forming cross-bar-type structures using a shadow mask with a line width of 60  $\mu$ m, as shown in Figure 1a. Figure 1b shows the cross-sectional transmission electron microscopy (TEM) image of the cell used in experiments.

A Keysight B1500A semiconductor parameter analyzer was employed to measure the RS characteristics of the fabricated RRAM devices. The LFN characteristics were analyzed with a low-noise current amplifier (SR570) and a signal analyzer (35670A). The voltage applied to the TiN layer was supplied using a B1500A system. The output current of the RRAM device was connected to the SR570 system, converting the current fluctuation into a voltage fluctuation. The 35670A system converted the dynamic signal from the SR570 system to a power spectral density. The noise floor of our measurement system was measured to be  $\sim 10^{-24}$  A<sup>2</sup>/Hz, which was much lower than the device noise. This guaranteed that the noise power spectral densities measured in this work were not affected by the noise floor of the measurement system.

Materials 2023, 16, 2317 3 of 9

**Figure 1.** (a) The simple structure and (b) the cross-sectional TEM image of the fabricated Al/ $\alpha TiO_x/Al$  RRAM device.

# 3. Results

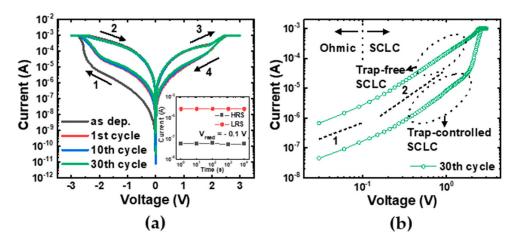

Figure 2a shows the I–V characteristics of the fabricated Al/ $\alpha$ TiO<sub>x</sub>/Al RRAM device for the initial and 30 cycles. The bias sweep sequence is indicated by the arrows. When the voltage was swept from 0 V to the negative voltage direction, the device transitioned from a high-resistance state (HRS) to a low-resistance state (LRS) above the set voltage (SET process). The LRS was held up to about 2 V during the positive voltage sweep and then switched back to the HRS above the reset voltage (RESET process). As shown in Figure 2a, the device exhibited gradual set/reset characteristics that did not show abrupt current changes. A compliance current of 1 mA was applied to protect the device from dielectric breakdown. In our device, if a positive voltage was applied to the initial cell, no switching occurred, and the device permanently broke down. That is, it showed SET operation at negative voltage and RESET operation at positive voltage. These asymmetric operation characteristics of Al/ $\alpha$ TiO<sub>x</sub>/Al devices can be explained by asymmetric interface formation [33]. When referring to the classification criteria of RRAM devices, our device can be classified as an interfacial RRAM device in which no conductive filament or localized path is formed within the dielectric [34,35]. The inset of Figure 2a shows the retention characteristics. Our device maintained the HRS and LRS without significant state change for 10<sup>4</sup> s, which guaranteed the reliability of the LFN measurements. To clarify the current transport mechanism in both the HRS and LRS, the I-V curve at the 30th cycle is replotted on a double-logarithmic scale in Figure 2b. Referring to the linear guidelines in Figure 2b, the conduction mechanism of the device can be understood by using the space-charge limited conduction (SCLC) model [36,37]. The trap-controlled SCLC can be divided into two regions. In the low-field region, the conduction mechanism was dominated by the thermally generated free electrons in the dielectric film (Ohmic conduction, I  $\propto$  V). If the applied field intensity exceeded the critical value, the density of free electrons injected from the electrode gradually exceeded the equilibrium concentration, and excess electrons accumulated in the space between the two electrodes. Consequently, the space charge started to limit the total current flow (SCLC, I  $\propto$  V<sup>m</sup>, m > 2). Jeong et al. proposed the RS mechanism of the Al/ $\alpha$ TiO<sub>x</sub>/Al RRAM device [23]. In the HRS, oxygen ions are accumulated near the top interface due to redox reactions, which increases the barrier at the interface. Although bulk  $\alpha TiO_x$  has relatively high conductivity due to internal oxygen vacancies, the overall current is determined by the interface. In contrast, in the LRS, the barrier near the top interface decreases due to the drift of oxygen ions caused by the set process (positive bias). In addition, the concentration of oxygen vacancies in the bulk  $\alpha TiO_x$ decreases, which makes the  $\alpha \text{TiO}_x$  layer more insulating.

Materials **2023**, 16, 2317 4 of 9

**Figure 2.** (a) The I–V characteristics of the fabricated Al/ $\alpha$ TiO<sub>x</sub>/Al interfacial RRAM devices for the initial and 30 cycles. The arrows indicate the direction of the voltage sweep. The inset shows the retention characteristics. (b) The double-logarithmic plot of the I–V curve at the 30th cycle.

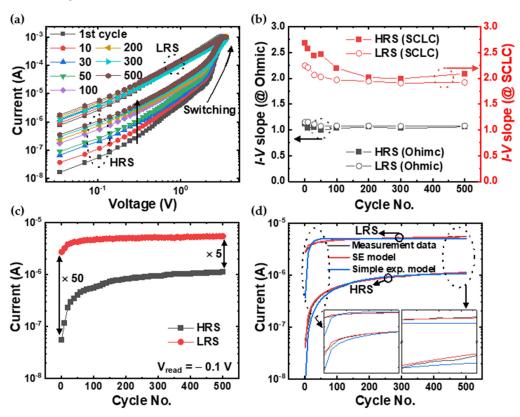

Switching endurance, which tells how often a memory device can switch between cell states without degradation, is one of the most important figures of merit for a memory device [38]. From this point of view, developing a technique to analyze the degradation mechanism of RRAM devices is a very good direction for RRAM optimization. Figure 3a shows the double-logarithmic plot of the I-V characteristics (HRS to LRS) for 500 DC cycles. While the current variation in the LRS was insignificant, the degradation in the HRS was noticeably clear. The change in the trend of the I-V curve, which gradually changed in one direction, was clearly different from the cycle-to-cycle variability due to the stochastic nature of the RS phenomenon [39-41]. To analyze the progressive RW collapse of the device, we first verified whether the current transport followed the SCLC mechanism well along the endurance cycle. Figure 3b shows the slopes of the I–V curves in Ohmic and the SCLC region according to the RS cycle. According to the RS cycle, the Ohmic region's slope was almost constant at 1 in both resistance states. However, the slope of the SCLC region changed to 2.7, 2.57, and 2.2 at the first, 10th, and 100th periods, respectively, and then converged to 2 in the HRS. According to the SCLC theory [36,37], the slope of the I–V curve in the double logarithmic plot is expected to be 2 for a discrete trap distribution (I  $\propto$  V<sup>2</sup>) and greater than 2 for an exponential trap distribution (I  $\propto$  V<sup>m+1</sup>, m > 1). So, it can be seen that the conduction mechanism does not change according to the RS cycle. In addition, the decrease in the slope with consecutive RS cycles suggests electric-field-induced charge trapping in the oxide. According to the trap-controlled SCLC model [24,25], SCLC arises if the current through the bulk solid becomes limited by the buildup of charge injected from the electrode. If the applied voltage is raised to a threshold value, at which point the number of charge carriers injected at the electrode becomes equivalent to the number of thermally generated ones in the bulk, the injected carriers are sufficient to fully fill the trap states, resulting in a rapid increment of the current. The degradation of our experimental RRAM device is closely related to this SCLC mechanism. Namely, certain traps whose energy levels are far below the conduction band (deep traps) are likely to fail to release the trapped charge carriers during the reset process. Consequently, the repetitive RS process could induce a more effective filling-up of the deep traps and prevent their effective detrapping during the subsequent reset process. Figure 3c shows the endurance characteristic in both resistance states at the read voltage of 0.1 V. At the early stage of the RS cycle, the current increased exponentially and reached saturation with an almost linear shape. To describe the relaxation of out-of-equilibrium disordered systems that do not obey a simple exponential law, a stretched exponential (SE) function is widely used [42-44]. This model is defined as  $f(x) = e^{-x^{\beta}}$ , where x is the independent variable (here x is the cycle number), and  $\beta$  is the stretched exponent between 0 and 1. Figure 3d shows the results of the simple exponential (blue line) and the SE models (red line) fitting. The fitted results were more

Materials 2023, 16, 2317 5 of 9

consistent with the SE function at the beginning and end of the curves as shown in the insets of Figure 3d.

**Figure 3.** (a) The double-logarithmic plot of the I–V characteristics (HRS to LRS) for 500 DC cycles. (b) The change in slopes of the I–V curves in Ohmic (black) and the SCLC (red) region according to the RS cycle. (c) The endurance characteristic in both the HRS and LRS at the read voltage of 0.1 V. The initial on/off ratio of about 50 decreases to 5 after 500 DC cycles. (d) The fitting results for simple exponential (blue line) and SE function (red line). Insets show enlarged graphs at the beginning (left) and end (right) of the curves.

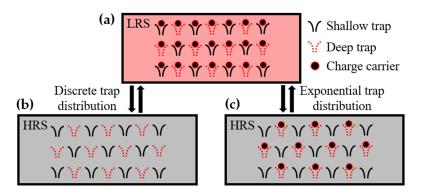

Based on these results, we propose a mechanism for the endurance degradation in  $Al/\alpha TiO_x/Al$  interfacial RRAM devices as shown in Figure 4. When assuming a discrete trap distribution, the process of filling/emptying all traps is repeated during the RS cycle, as shown in Figure 4a,b, and no RS degradation occurs. However, when assuming exponential trap distribution, the deep traps filled with electrons during the set process do not release electrons during the reset process (Figure 4c), consequently reducing the resistance at the HRS. Our understanding of the RS degradation mechanism can be well supported by subsequent LFN measurements. This is because the change in the trap density is directly related to the noise level [45,46].

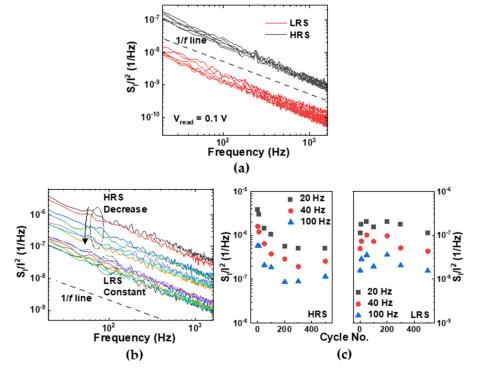

Figure 5a shows the normalized noise power spectral density  $(S_i/l^2)$  for several devices measured at 0.1 V in both the HRS and LRS. The  $S_i/l^2$  was proportional to  $1/f^\gamma$ , with  $\gamma \sim 1$  for both states in most cells, which means that the LFN characteristic in Al/ $\alpha$ TiO<sub>x</sub>/Al RRAM devices also obeyed the classical 1/f noise theory in both states (see dotted line in the inset of Figure 5a) [47]. The normalized noise power measured in the HRS was an order of magnitude higher than that in the LRS. The difference in noise levels in the different resistance states can be analyzed based on our model illustrated in Figure 4. Considering that the degree of trap occupancy was responsible for the transition of resistance states, the magnitude of the  $S_i/l^2$  in the LRS was reduced because all trap sites were filled by free electrons. In contrast, in the HRS, the electron flow was obstructed by the noise source, such as Columbic scattering caused by empty trap sites, which consequently increased the noise level [48]. Figure 5b shows the  $S_i/l^2$  in both the HRS and LRS according

Materials **2023**, 16, 2317 6 of 9

to the RS cycle at the same read bias. The  $S_{\rm i}/I^2$  in the LRS did not change significantly with an increase in the number of cycles, while the  $S_{\rm i}/I^2$  in the HRS gradually decreased. Figure 5c shows the value of the  $S_{\rm i}/I^2$  with increasing cycle numbers at the frequencies 20, 40, and 100 Hz. In the HRS, because certain traps did not release the electrons during the reset process and thus induced a decrease in the trap density, the  $S_{\rm i}/I^2$  rapidly decreased for approximately 100 cycles and then saturated. In contrast, in the LRS, the  $S_{\rm i}/I^2$  did not change significantly. Namely, the reduction of the trap, which was the scattering center of the charge carrier [48], caused a decrease in the  $S_{\rm i}/I^2$ . This result shows that the mechanism of the endurance degradation in Al/ $\alpha$ TiO<sub>x</sub>/Al RRAM, proposed from the measured degradation characteristics and the SCLC theory, was consistent with the LFN measurement results.

**Figure 4.** Schematic illustration explaining the physical mechanism of endurance degradation in  $Al/\alpha TiO_x/Al$  interfacial RRAM device. (a) LRS after the SET process, in which all traps are filled by the charge carriers. (b) HRS after the RESET process, in which all traps are emptied when assuming the discrete trap distribution. (c) HRS after the RESET process when assuming the exponential trap distribution. Certain traps do not release the charge carriers during the RESET process.

**Figure 5.** (a) The  $S_i/I^2$  for several devices in both the HRS and LRS at 0.1 V. (b) The  $S_i/I^2$  in both the HRS and LRS according to the RS cycle at the same read bias. (c) The change in the  $S_i/I^2$  according to the RS cycle in both the HRS (left) and LRS (right) at the frequencies 20, 40, and 100 Hz.

Materials **2023**, 16, 2317 7 of 9

### 4. Conclusions

In conclusion, we investigated the physical mechanism of the endurance degradation in Al/ $\alpha$ TiO<sub>x</sub>/Al interfacial RRAM devices using the LFN measurements. The gradual RW collapse of the device was distinctly different from the abrupt RW failure of the filamentary RRAM. During the endurance test, the current transport mechanism maintained the SCLC, but the trap distribution was changed from a discrete distribution to an exponential distribution. In addition, the stretched-exponential equation was efficiently applied in fitting the current shift according to the RS cycle. The  $S_i/l^2$  measured in the HRS was an order of magnitude higher than that in the LRS because of the difference in the degree of trap occupancy. From the degradation characteristic and LFN measurement, we proposed a mechanism of endurance degradation related to the electric field-induced charge trapping. The proposed model was well supported by the 1/f noise measurement according to the RS cycle, which showed that LFN measurement can be a valuable analytical tool to clarify the physical mechanism associated with the RS phenomenon of RRAM devices. Overall, this study demonstrates the usability of LFN measurements in producing direct evidence of the physical mechanism underlying the RS degradation phenomenon, which can facilitate the development of RRAM devices.

**Author Contributions:** Conceptualization, J.-K.L.; formal analysis, J.-K.L.; funding acquisition, S.K.; investigation, J.-K.L. and J.P.; resources, S.K.; supervision, S.K.; writing—original draft, J.-K.L.; writing—review and editing, S.K. and J.P. All authors have read and agreed to the published version of the manuscript.

**Funding:** Korea Institute of Energy Technology Evaluation and Planning (KETEP) grant funded by the Republic of Korea government (MOTIE) under Grant 20224000000020.

Institutional Review Board Statement: Not applicable.

**Informed Consent Statement:** Not applicable. **Data Availability Statement:** Not applicable.

**Conflicts of Interest:** The authors declare no conflict of interest.

## References

- 1. Molas, G.; Nowak, E. Advances in Emerging Memory Technologies: From Data Storage to Artificial Intelligence. *Appl. Sci.* **2021**, 11, 11254. [CrossRef]

- 2. Ishimaru, K. Future of Non-Volatile Memory-From Storage to Computing-. In Proceedings of the IEEE International Electron Devices Meeting (IEDM), San Francisco, CA, USA, 7–11 December 2019; pp. 1.3.1–1.3.6. [CrossRef]

- 3. Yang, J.Q.; Zhou, T.; Han, S.T. Functional Applications of Future Data Storage Devices. *Adv. Electron. Mater.* **2021**, 7, 2001181. [CrossRef]

- 4. Wulf, W.A.; Mckee, S.A. Hitting the Memory Wall: Implications of the Obvious. *Appear. Comput. Archit. News* **1995**, 23, 20–24. [CrossRef]

- 5. Cristal, A.; Santana, O.J.; Cazorla, F.; Galluzzi, M.; Ramirez, T.; Pericas, M.; Valero, M. Kilo-instruction processors: Overcoming the memory wall. *IEEE Micro* **2005**, 25, 48–57. [CrossRef]

- 6. Efnusheva, D.; Cholakoska, A.; Tentov, A. A Survey of Different Approaches for Overcoming the Processor-Memory Bottleneck. *Int. J. Comput. Sci. Inf. Technol.* **2017**, *9*, 151–163. [CrossRef]

- 7. Endoh, T.; Koike, H.; Ikeda, S.; Hanyu, T.; Ohno, H. An Overview of Nonvolatile Emerging Memories—Spintronics for Working Memories. *IEEE J. Emerg. Sel. Top. Circuits Syst.* **2016**, *6*, 109–119. [CrossRef]

- 8. Govoreanu, B.; Kar, G.S.; Chen, Y.Y.; Paraschiv, V.; Kubicek, S.; Fantini, A.; Radu, I.P.; Goux, L.; Clima, S.; Degraeve, R.; et al.  $10 \times 10 \text{ nm}^2 \text{ Hf/HfO}_x \text{ Crossbar Resistive RAM with Excellent Performance, Reliability and Low-Energy Operation. In Proceedings of the IEEE International Electron Devices Meeting (IEDM), Washington, DC, USA, 5–7 December 2011; pp. 31.6.1–31.6.4. [CrossRef]$

- 9. Raghavan, N.; Pey, K.L.; Li, X.; Liu, W.H.; Wu, X.; Bosman, M.; Kauerauf, T. Very Low Reset Current for an RRAM Device Achieved in the Oxygen-Vacancy-Controlled Regime. *IEEE Electron Device Lett.* **2011**, 32, 716–718. [CrossRef]

- Khan, R.; Ilyas, N.; Shamim, M.Z.M.; Khan, M.I.; Sohail, M.; Rahman, N.; Khan, A.A.; Khang, S.N.; Khangh, A. Oxide-based resistive switching-based devices: Fabrication, influence parameters and applications. *J. Mater. Chem. C* 2021, 9, 15755–15788.

[CrossRef]

- 11. Ha, H.; Pyo, J.; Lee, Y.; Kim, S. Non-Volatile Memory and Synaptic Characteristics of TiN/CeO<sub>x</sub>/Pt RRAM Devices. *Materials* **2022**, *15*, 9087. [CrossRef]

Materials **2023**, 16, 2317 8 of 9

12. Ielmini, D. Brain-inspired computing with resistive switching memory (RRAM): Devices, synapses and neural networks. *Microelectron. Eng.* **2018**, 190, 44–53. [CrossRef]

- 13. Jang, J.; Gi, S.; Yeo, I.; Choi, S.; Jang, S.; Ham, S.; Lee, B.; Wang, G. A Learning-Rate Modulable and Reliable TiO<sub>x</sub> Memristor Array for Robust, Fast, and Accurate Neuromorphic Computing. *Adv. Sci.* **2022**, *9*, 2201117. [CrossRef]

- Akbari, M.; Kim, M.K.; Kim, D.; Lee, J.S. Reproducible and reliable resistive switching behaviors of AlO<sub>X</sub>/HfO<sub>X</sub> bilayer structures with Al electrode by atomic layer deposition. RSC Adv. 2017, 7, 16704–16708. [CrossRef]

- 15. Choi, S.; Lee, J.; Kim, S.; Lu, W.D. Retention failure analysis of metal-oxide based resistive memory. *Appl. Phys. Lett.* **2014**, 105, 113510. [CrossRef]

- 16. Kang, J.F.; Huang, P.; Chen, Z.; Zhao, Y.D.; Liu, C.; Han, R.Z.; Liu, L.F.; Liu, X.Y.; Wang, Y.Y.; Gao, B. Physical understanding and optimization of resistive switching characteristics in oxide-RRAM. In Proceedings of the 46th European Solid-State Device Research Conference (ESSDERC), Lausanne, Switzerland, 12–15 September 2016; pp. 154–159. [CrossRef]

- 17. Chen, B.; Lu, Y.; Gao, B.; Fu, Y.H.; Zhang, F.F.; Huang, P.; Chen, Y.S.; Liu, L.F.; Liu, X.Y.; Kang, J.F.; et al. Physical Mechanisms of Endurance Degradation in TMO-RRAM. In Proceedings of the IEEE International Electron Devices Meeting (IEDM), Washington, DC, USA, 5–7 December 2011; pp. 12.3.1–12.3.4. [CrossRef]

- 18. Lee, J.K.; Lee, J.W.; Park, J.; Chung, S.W.; Roh, J.S.; Hong, S.J.; Cho, I.W.; Kwon, H.I.; Lee, J.H. Extraction of trap location and energy from random telegraph noise in amorphous TiO<sub>x</sub> resistance random access memories. *Appl. Phys. Lett.* **2011**, *98*, 143502. [CrossRef]

- Lee, J.K.; Jung, S.; Park, J.; Chung, S.W.; Roh, J.S.; Hong, S.J.; Cho, I.H.; Kwon, H.I.; Park, C.H.; Park, B.G.; et al. Accurate analysis

of conduction and resistive-switching mechanisms in double-layered resistive-switching memory devices. *Appl. Phys. Lett.* 2012,

101, 103506. [CrossRef]

- 20. Lee, D.; Lee, J.; Jo, M.; Park, J.; Siddik, M.; Hwang, H. Noise-Analysis-Based Model of Filamentary Switching ReRAM with ZrOx/HfOx Stacks. *IEEE Electron. Device Lett.* **2011**, 32, 964–966. [CrossRef]

- 21. Maccaronio, V.; Crupi, F.; Procel, L.M.; Goux, L.; Simoen, E.; Trojman, L.; Miranda, E. DC and low-frequency noise behavior of the conductive filament in bipolar HfO<sub>2</sub>-based resistive random access memory. *Microelectron. Eng.* **2013**, *107*, 1–5. [CrossRef]

- 22. Abgall, F. Switching phenomena in titanium oxide thin films. Solid-State Electron. 1986, 11, 535–541. [CrossRef]

- 23. Jeong, H.Y.; Lee, J.Y.; Ryu, M.K.; Choi, S.Y. Bipolar resistive switching in amorphous titanium oxide thin film. *Phys. Status Solidi Rapid Res. Lett.* **2010**, *1*, 28–30. [CrossRef]

- Jeong, H.Y.; Kim, S.K.; Lee, J.Y.; Choi, S.Y. Role of Interface Reaction on Resistive Switching of Metal/Amorphous TiO<sub>2</sub>/Al RRAM Devices. J. Electrochem. Soc. 2011, 158, H979–H982. [CrossRef]

- 25. Jeong, H.Y.; Kim, S.K.; Lee, J.Y.; Choi, S.Y. Impact of amorphous titanium oxide film on the device stability of Al/TiO<sub>2</sub>/Al resistive memory. *Appl. Phys. A* **2011**, 102, 967–972. [CrossRef]

- 26. Moon, K.; Lim, S.; Park, J.; Sung, C.; Oh, S.; Woo, J.; Lee, J.; Hwang, H. RRAM-based synapse devices for neuromorphic systems. *Faraday Discuss.* **2019**, 213, 421. [CrossRef] [PubMed]

- 27. Wang, T.Y.; Meng, J.L.; Li, Q.X.; Chen, L.; Zhu, H.; Sun, Q.Q.; Ding, S.J.; Zhang, D.W. Forming-free flexible memristor with multilevel storage for neuromorphic computing by full PVD technique. *J. Mater. Sci. Technol.* **2021**, *60*, 21–26. [CrossRef]

- 28. Pandey, V.; Adiba, A.; Ahmad, T.; Nehla, P.; Munjal, S. Forming-free bipolar resistive switching characteristics in Al/Mn<sub>3</sub>O<sub>4</sub>/FTO RRAM device. *J. Phys. Chem. Solids* **2022**, *165*, 110689. [CrossRef]

- 29. Adiba, A.; Pandey, V.; Ahmad, T.; Nehla, P.; Munjal, S. Multilevel resistive switching with negative differential resistance in Al/NiO/ZnFe<sub>2</sub>O<sub>4</sub>/ITO ReRAM device. *Phys. B* **2023**, *654*, 414742. [CrossRef]

- 30. Pandey, V.; Adiba, A.; Nehla, P.; Munjal, S.; Ahmad, T. Bipolar resistive switching with multiple intermediate resistance states in Mn<sub>3</sub>O<sub>4</sub> thin film. *Mater. Today Commun.* **2023**, *34*, 105484. [CrossRef]

- 31. Choi, S.S.; Choi, A.R.; Yang, J.W.; Hwang, Y.W.; Cho, D.H.; Shim, K.H. Comparative study of low frequency noise and hot-carrier reliability in SiGe PD SOI pMOSFETs. *Appl. Surf. Sci.* 2008, 254, 6190–6193. [CrossRef]

- 32. Ciofi, C.; Neri, B. Low-frequency noise measurements as a characterization tool for degradation phenomena in solid-state devices. J. Phys. D Appl. Phys. 2000, 30, R199–R216. [CrossRef]

- 33. Jeong, H.Y.; Lee, J.Y.; Choi, S.Y.; Kim, J.W. Microscopic origin of bipolar resistive switching of nanoscale titanium oxide thin films. *Appl. Phys. Lett.* **2009**, *95*, 162108. [CrossRef]

- 34. Kumar, D.; Aluguri, R.; Chand, U.; Tseng, T.Y. Metal oxide resistive switching memory: Materials, properties and switching mechanisms. *Ceram. Int.* **2017**, *43*, S547–S556. [CrossRef]

- 35. Bagdzevicius, S.; Maas, K.; Boudard, M.; Burriel, M. Interface-type resistive switching in perovskite materials. *J. Electroceram.* **2017**, 39, 157–184. [CrossRef]

- 36. Zhang, P.; Ang, Y.S.; Garner, A.L.; Valfells, A.; Luginsland, J.W.; Ang, L.K. Space–charge limited current in nanodiodes: Ballistic, collisional, and dynamical effects. *J. Appl. Phys.* **2021**, *129*, 100902. [CrossRef]

- 37. Kwan, C.P.; Street, M.; Mahmood, A.; Echtenkamp, W.; Randle, M.; He, K.; Nathawat, J.; Arabchigavkani, N.; Barut, B.; Yin, S.; et al. Space-charge limited conduction in epitaxial chromia films grown on elemental and oxide-based metallic substrates. *AIP Adv.* **2019**, *9*, 055018. [CrossRef]

- 38. Lee, M.J.; Lee, C.B.; Lee, D.S.; Lee, S.R.; Chang, M.; Hur, J.H.; Kim, Y.B.; Kim, C.J.; Seo, D.H.; Seo, S.; et al. A fast, high-endurance and scalable non-volatile memory device made from asymmetric Ta<sub>2</sub>O<sub>5-x</sub>/TaO<sub>2-x</sub> bilayer structures. *Nat. Mater.* **2011**, *10*, 625–630. [CrossRef] [PubMed]

Materials **2023**, 16, 2317 9 of 9

39. Huang, C.Y.; Jieng, J.H.; Jang, W.Y.; Lin, C.H.; Tseng, T.Y. Improved Resistive Switching Characteristics by Al<sub>2</sub>O<sub>3</sub> Layers Inclusion in HfO<sub>2</sub>-Based RRAM Devices. *ECS Solid State Lett.* **2013**, *2*, P63–P65. [CrossRef]

- 40. Jin, S.; Kwon, J.D.; Kim, Y. Statistical Analysis of Uniform Switching Characteristics of Ta<sub>2</sub>O<sub>5</sub>-Based Memristors by Embedding In-Situ Grown 2D-MoS<sub>2</sub> Buffer Layers. *Materials* **2021**, *14*, 6275. [CrossRef] [PubMed]

- 41. Loy, D.J.J.; Dananjaya, P.A.; Chakrabarti, S.; Tan, K.H.; Chow, S.C.W.; Toh, E.H.; Lew, W.S. Oxygen Vacancy Density Dependence with a Hopping Conduction Mechanism in Multilevel Switching Behavior of HfO<sub>2</sub>-Based Resistive Random Access Memory Devices. *ACS Appl. Electron. Mater.* **2020**, *2*, 3160–3170. [CrossRef]

- 42. Lukichev, A. Physical meaning of the stretched exponential Kohlrausch function. Phys. Lett. A 2019, 383, 2983–2987. [CrossRef]

- 43. Sangwan, V.K.; Lee, H.S.; Bergeron, H.; Balla, I.; Beck, M.E.; Chen, K.S.; Hersam, M.C. Multi-terminal memtransistors from polycrystalline monolayer molybdenum disulfide. *Nature* **2018**, *554*, 500–504. [CrossRef]

- 44. Lee, J.K.; Chung, H.J.; Heo, J.; Seo, S.; Cho, I.H.; Kwon, H.I.; Lee, J.H. Reliability of bottom-gate graphene field-effect transistors prepared by using inductively coupled plasma-chemical vapor deposition. *Appl. Phys. Lett.* **2011**, *98*, 193504. [CrossRef]

- 45. Jeong, K.S.; Yun, H.J.; Kim, Y.M.; Yang, S.D.; Lee, S.Y.; Kim, Y.S.; Lee, H.D.; Lee, G.W. Investigation of the Gate Bias Stress Instability in ZnO Thin Film Transistors by Low-Frequency Noise Analysis. *Jpn. J. Appl. Phys.* **2013**, *52*, 04CF04. [CrossRef]

- 46. Fung, T.C.; Baek, G.; Kanickib, J. Low frequency noise in long channel amorphous In–Ga–Zn–O thin film transistors. *J. Appl. Phys.* **2010**, *108*, 074518. [CrossRef]

- 47. Hooge, F.N. 1/f noise sources. IEEE Trans. Electron Devices 1994, 41, 1926–1935. [CrossRef]

- 48. Lordi, V.; Erhart, P.; Aberg, D. Charge carrier scattering by defects in semiconductors. Phys. Rev. B 2010, 81, 235204. [CrossRef]

**Disclaimer/Publisher's Note:** The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content.