# Article OFF-State Leakage Suppression in Vertical Electron–Hole Bilayer TFET Using Dual-Metal Left-Gate and N<sup>+</sup>-Pocket

Hu Liu <sup>1,2,\*</sup>, Wenting Zhang <sup>1</sup>, Zaixing Wang <sup>1</sup>, Yao Li <sup>1</sup> and Huawei Zhang <sup>1</sup>

- <sup>1</sup> School of Electronic and Information Engineering, Lanzhou Jiaotong University, Lanzhou 730070, China

- <sup>2</sup> Key Laboratory of Opto-Technology and Intelligent Control, Ministry of Education,

Lanzhou Jiaotong University, Lanzhou 730070, China

Correspondence: liuhu626@163.com

**Abstract:** In this paper, an  $In_{0.53}Ga_{0.47}As$  electron-hole bilayer tunnel field-effect transistor (EHBT-FET) with a dual-metal left-gate and an N<sup>+</sup>-pocket (DGNP-EHBTFET) is proposed and systematically studied by means of numerical simulation. Unlike traditional transverse EHBTFETs, the proposed DGNP-EHBTFET can improve device performance without sacrificing the chip density, and can simplify the manufacturing process. The introduction of the dual-metal left-gate and the N<sup>+</sup>-pocket can shift the point-tunneling junction and adjust the energy band and the electric field in it, aiming to substantially degrade the OFF-state current ( $I_{OFF}$ ) and maintain good ON-state performance. Moreover, the line tunneling governed by the tunneling-gate and the right-gate can further regulate and control  $I_{OFF}$ . By optimizing various parameters related to the N<sup>+</sup>-pocket and the gate electrodes, DGNP-EHBTFET's  $I_{OFF}$  is reduced by at least four orders of magnitude, it has a 75.1% decreased average subthreshold swing compared with other EHBTFETs, and it can maintain a high ON-state current. This design greatly promotes the application potential of EHBTFETs.

**Keywords:** tunnel field-effect transistor; OFF-state leakage suppression; electron-hole bilayer; line tunneling

# 1. Introduction

As the feature size enters the nanoscale and continues to shrink, the increasing static power consumption in metal-oxide-semiconductor field-effect transistors (MOSFETs) places restrictions on the development of integrated circuits. To continue Moore's law, the static power consumption of devices must be further reduced. Limited by the injection mechanism of thermal emission for MOSFETs, an effective method to solve this problem is to develop steep subthreshold swing (SS) devices. One of the mainstream switching devices with steep SS, the tunneling field-effect transistor (TFET) [1–3], has the potential to achieve a low operating voltage by overcoming the thermally limited SS of 60 mV/decade by utilizing tunneling as a switching mechanism, and has attracted extensive attention due to its low-power-consumption feature. Si-based TFETs can take advantage of the existing semiconductor design and manufacturing infrastructure, and has thus become the research mainstream of TFETs. However, a low ON-state current  $(I_{ON})$  caused by the inherent material properties of silicon restricts the practical commercial use of TFETs. Therefore, various TFETs with novel materials or structures have emerged to improve  $I_{ON}$ , such as nanowire TFETs [4–6], heterojunction TFETs [6–10], dopingless and junctionless TFETs [4,9,11–15], line-tunneling (LT) TFETs [15–23], two-dimensional material TFETs [24–26], etc. Among them, an electron–hole bilayer TFET (EHBTFET) [15,18–23] based on LT can boost  $I_{ON}$  due to having a larger tunneling region, and has been developed in recent years.

To conserve the total momentum in tunneling, III-V direct band gap materials do not have to involve phonons, which is more beneficial to the improvement of TFET performance than an indirect band gap semiconductor material such as silicon. By analyzing TFETs

Citation: Liu, H.; Zhang, W.; Wang, Z.; Li, Y.; Zhang, H. OFF-State Leakage Suppression in Vertical Electron–Hole Bilayer TFET Using Dual-Metal Left-Gate and N<sup>+</sup>-Pocket. *Materials* 2022, *15*, 6924. https:// doi.org/10.3390/ma15196924

Academic Editor: Alexander A. Lebedev

Received: 21 August 2022 Accepted: 1 October 2022 Published: 6 October 2022

**Publisher's Note:** MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations.

**Copyright:** © 2022 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https:// creativecommons.org/licenses/by/ 4.0/). related to III-V materials in previous publications [9,11,14], it is confirmed that InGaAs is one of the candidate materials suitable for the design of N-type TFETs. In particular, In<sub>0.53</sub>Ga<sub>0.47</sub>As has a low effective electron mass, a narrow band gap, ultra-high electron mobility, and lattice matching with InP substrate, which has been widely used in the lowpower-consumption applications [27,28]. Similarly, it can be employed as the bulk material of EHBTFETs to further improve  $I_{ON}$  [29,30]. Nevertheless, the band-to-band tunneling leakage in the OFF-state caused by point tunneling (PT) in In0.53Ga0.47As-based EHBTFETs can result in a higher OFF-state current ( $I_{OFF}$ ) compared with Si-based ones, which will increase SS so as to increase the static power consumption of devices. To circumvent this issue, Alper et al. [31] have proposed a novel EHBTFET where counterdoping is carried out in the underlap regions. However, to maintain the same  $I_{ON}$ , the gate voltage ( $V_{gs}$ ) needs to be increased to 2.6 V, which is unfavorable for low-power-consumption applications. To obtain low *I*<sub>OFF</sub>, another technique [32] can be employed, that is, the high-K dielectric pocket is inserted into the underlap regions near the source and the drain regions, but it is only applicable to EHBTFETs with a transverse structure. The I<sub>ON</sub> of transverse EHBTFETs directly depends on the gate overlap area, which will restrict the reduction in the lateral size of the device. In addition, the manufacturing process of transverse EHBTFETs is complicated, which will cause a reduction in the product yield rate in fabrication.

In this paper, an  $In_{0.53}Ga_{0.47}As$  EHBTFET with a dual-metal left-gate and an N<sup>+</sup>-pocket (DGNP-EHBTFET) is proposed to effectively solve the aforementioned problem. The proposed DGNP-EHBTFET has a vertical structure, which can improve  $I_{ON}$  by enlarging the gate overlap region in the vertical direction without sacrificing the chip density. Meanwhile, the realization of the asymmetric double-gate structure in DGNP-EHBTFET does not need the transfer substrate technique used in transverse EHBTFETs, thereby simplifying the manufacturing process. The introduction of the dual-metal left-gate can not only make the PT junction deviate from the gate overlap region, but also adjust the electric field profiles at the tunneling junction, both of which are conducive to reducing  $I_{OFF}$ . The N<sup>+</sup>-pocket inserted into the gate underlap region near the drain can regulate and control the tunneling energy range and the tunneling distance of PT, which is beneficial to further decreasing  $I_{OFF}$  but can maintain a good  $I_{ON}$ . Moreover,  $I_{OFF}$  is also affected by LT that is governed by the work-function of the tunneling-gate and the right-gate. Until now, since there are relatively few studies on the OFF-state leakage suppression of vertical EHBTFETs, it is necessary for the device mechanism of the proposed novel structure to be revealed.

This paper is organized as follows. Section 2 introduces the device structures, the related physical parameters and models, and the manufacturing process. The operating mechanism, the direct current (DC) characteristics for the three EHBTFETs, as well as the effects of the N<sup>+</sup>-pocket and the work-function of the gate electrodes on DGNP-EHBTFET are thoroughly investigated in Section 3. Finally, Section 4 briefly summarizes the present studies.

# 2. Devices Structure and Simulation Methods

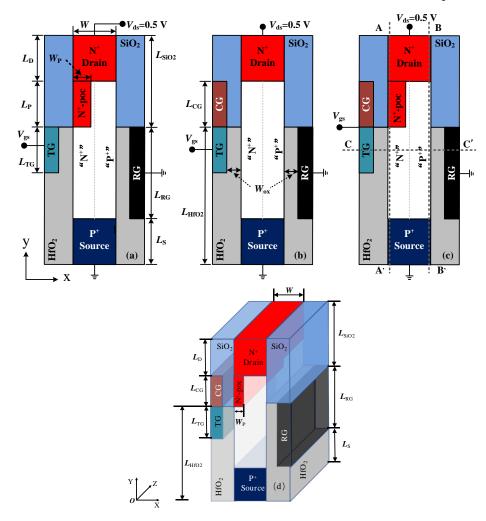

To better reveal the device mechanism of the proposed DGNP-EHBTFET, two other EHBTFETs are introduced in this paper: (1) an  $In_{0.53}Ga_{0.47}As$  EHBTFET with a dualmetal left-gate (DG-EHBTFET) and (2) an  $In_{0.53}Ga_{0.47}As$  EHBTFET with an N<sup>+</sup>-pocket (NP-EHBTFET). Cross-sectional views of these three vertical-structure EHBTFETs and a 3D schematic of DGNP-EHBTFET are shown in Figure 1, and the corresponding structural parameters are listed in Table 1.

For these three EHBTFETs, the structural parts are the same except for the left-gate and the channel region connected to the drain region. The left-gates of DG-EHBTFET and DGNP-EHBTFET are composed of a tunneling-gate (TG) and a control-gate (CG) tied directly, while that of NP-EHBTFET is only TG, and the N<sup>+</sup>-pocket connected with the drain region only exists in NP-EHBTFET and DGNP-EHBTFET. Based on the charge plasma concept [33,34], chromium with a work-function of 4.5 eV [35] is employed as TG to form an electron layer in the left-side channel near TG (i.e., the "N" region in Figure 1), and rhenium formed at a specified pressure and temperature (work-function = 5.5 eV) [36] can be picked as the grounded right-gate (RG) to create a hole layer in the right-side channel near RG (i.e., "P" region in Figure 1), so as to provide conditions for LT parallel to the gate electric field. To enhance electron tunneling and effectively suppress gate leakage and the ambipolar current, a HfO<sub>2</sub>/SiO<sub>2</sub> heterogate dielectric is adopted in the proposed EHBTFET, which is widely used in TFETs [9,11,14]. Moreover, P-type doping with a concentration of  $1 \times 10^{19}$  cm<sup>-3</sup> is carried out in the source region, while N-type doping with a concentration of  $1 \times 10^{19}$  cm<sup>-3</sup> and  $2 \times 10^{19}$  cm<sup>-3</sup> is performed in the drain region and the N<sup>+</sup>-pocket, respectively. Except for the source, the drain, and the N<sup>+</sup>-pocket regions, the other parts of the channel are intrinsic. In simulations, some key material parameters for In<sub>0.53</sub>Ga<sub>0.47</sub>As—the band gap, heavy-hole effective mass, light-hole effective mass, and electron effective mass—are 0.751 eV, 0.457  $m_0$ , 0.052  $m_0$ , and 0.042  $m_0$ , respectively [30,37].

**Figure 1.** Cross sectional views of (**a**) NP-EHBTFET; (**b**) DG-EHBTFET; and (**c**) DGNP-EHBTFET. (**d**) A 3D schematic of DGNP-EHBTFET. Cutlines A–A' and B–B' are located at 0.5 nm on the right side of the left-gate dielectric and the left side of the right-gate dielectric, respectively, and cutline C–C' is located in the middle of the tunneling-gate.

The Silvaco Atlas 2D numerical simulation platform is used for all device simulations. To more accurately model the tunneling process, the non-local band-to-band (BTBT) tunneling model is adopted, which considers the spatial variation in the energy bands. The Lombardi mobility model with a remote coulomb scattering term is employed to account for the mobility degradation that occurs inside the inversion layers. Considering that the introduction of the HfO<sub>2</sub> dielectric will generate a large number of traps at the HfO<sub>2</sub>/InGaAs interface, we adopt the trap-assisted tunneling model in simulations, and a single donor trap level is assumed near

the valence band with an interface trap density of  $1 \times 10^{13}$  cm<sup>-2</sup> eV<sup>-1</sup>. The limitation of this approach is that it cannot reflect the effect of the midlevel position of traps, which may overor under-estimate *SS* and *I*<sub>OFF</sub>. In light of the quantum confinement effect in a thin channel layer, we adopt the density gradient model. Additionally, the Shockley–Read–Hall and Auger recombination models, drift-diffusion current transport model, bandgap-narrowing models, Fermi–Dirac carrier statistics, and Schenk oxide-tunneling model are included in the simulations. For these three EHBTFETs, corresponding physical quantities used for revealing some physical mechanisms can be extracted along cutlines A–A', B–B', and C–C' (see dotted lines in Figure 1c), respectively. During data processing, *I*<sub>OFF</sub> and *I*<sub>ON</sub> are extracted from the transfer characteristic curves in the OFF-state ( $V_{gs} = 0$  V and  $V_{ds} = 0.5$  V) and ON-state ( $V_{gs} = 1$  V and  $V_{ds} = 0.5$  V), respectively.

| Parameters                                   | Value  |  |  |

|----------------------------------------------|--------|--|--|

| Bulk material width (W)                      | 6 nm   |  |  |

| N <sup>+</sup> -pocket width ( $W_p$ )       | 2 nm   |  |  |

| $N^+$ -pocket length ( $L_p$ )               | 50 nm  |  |  |

| Drain length $(L_{\rm D})^{-1}$              | 50 nm  |  |  |

| Source length ( $L_{\rm S}$ )                | 50 nm  |  |  |

| Tunneling-gate length ( $L_{TG}$ )           | 50 nm  |  |  |

| Control-gate length ( $L_{CG}$ )             | 50 nm  |  |  |

| Right-gate length ( $L_{RG}$ )               | 100 nm |  |  |

| $HfO_2$ length ( $L_{HfO2}$ )                | 150 nm |  |  |

| $SiO_2$ length ( $L_{SiO2}$ )                | 100 nm |  |  |

| Dielectric width near gate $(W_{ox})$        | 2 nm   |  |  |

| Tunneling-gate work-function ( $\Phi_{TG}$ ) | 4.5 eV |  |  |

| Control-gate work-function ( $\Phi_{CG}$ )   | 5.0 eV |  |  |

| Right-gate work-function ( $\Phi_{\rm RG}$ ) | 5.5 eV |  |  |

Table 1. Device structure parameters used in simulations.

The proposed DGNP-EHBTFET can be manufactured by state-of-the-art process technology. A brief process flow for obtaining DGNP-EHBTFET is as follows. In stage (1), the  $In_{0.53}Ga_{0.47}As$  epitaxial layer is grown vertically on InP substrate using the molecular-beam epitaxy technique. P<sup>+</sup>-source, N<sup>+</sup>-pocket, and N<sup>+</sup>-drain are formed via ion implantation. Then, the epitaxial layer is etched using reactive ion etching or inductively coupled plasma etching in stage (2). To obtain the required N<sup>+</sup>-pocket and channel width, the key process focuses on the accurate design of the mask pattern. In stage (3), HfO<sub>2</sub> can be deposited using the atomic layer deposition technique, followed by the etching of dielectrics and metal electrode deposition in stage (4). Finally, SiO<sub>2</sub> deposition is carried out in stage (5). Moreover, to reduce the interface trap in real operation, good quality of the HfO<sub>2</sub>/InGaAs interface should be possessed, which can be realized through adoption of the Al<sub>2</sub>O<sub>3</sub>/HfO<sub>2</sub> stack and the assurance of a good manufacturing process [38,39].

## 3. Results and Discussion

#### 3.1. Operating Mechanism of Three EHBTFETs

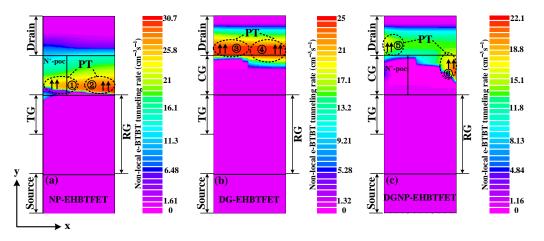

The operating mechanisms of NP-EHBTFET, DG-EHBTFET, and DGNP-EHBTFET can be interpreted using the non-local e-BTBT tunneling rate. For a clear explanation, we simulate the non-local e-BTBT tunneling rates for these three EHBTFETs from the perspective of vertical tunneling and lateral tunneling, respectively, with the results are shown in Figures 2 and 3. Figure 2 shows the vertical non-local e-BTBT tunneling rate in the OFF-state. It is observed that vertical tunneling (see black arrows) appears above the gate overlap region between TG and RG for NP-EHBTFET (see black dotted circles ① and ②). It is because of the existence of N<sup>+</sup>-pocket that the energy band of this region bends downward, so as to provide conditions for vertical tunneling. As shown in Figure 2b, the CG in DG-EHBTFET can induce holes in its right-side region, which forms a PN junction between this region and the drain region, and eventually results in vertical tunneling

in black dotted circles ③ and ④. Figure 2c shows that the vertical tunneling of DGNP-EHBTFET mainly occurs in black dotted circles ⑤ and ⑥, and its non-local e-BTBT tunneling rate is lower than that of NP-EHBTFET and DG-EHBTFET. Thus, it can be seen that the simultaneous introduction of the CG and N<sup>+</sup>-pocket in DGNP-EHBTFET contributes to the suppression of vertical tunneling in the OFF-state. This is mainly due to their regulation of electron and hole concentrations in the gate underlap region near the drain. Since there is no lateral tunneling in these EHBTFETs in the OFF-state, it is concluded that vertical tunneling dominates in this state.

**Figure 2.** Contour plots of the vertical non-local e-BTBT tunneling rate for (**a**) NP-EHBTFET; (**b**) DG-EHBTFET; and (**c**) DGNP-EHBTFET, in the OFF-state.

**Figure 3.** Contour plots of the vertical non-local e-BTBT tunneling rate for (**a**) NP-EHBTFET; (**b**) DG-EHBTFET; and (**c**) DGNP-EHBTFET, in the ON-state. Contour plots of the lateral non-local e-BTBT tunneling rate for (**d**) NP-EHBTFET; (**e**) DG-EHBTFET; and (**f**) DGNP-EHBTFET, in the ON-state.

It is observed from Figure 3 that the distribution ranges of vertical tunneling for these three EHBTFETs (see green dotted circles in Figure 3a–c) are basically the same in the ON-state, which is due to the fact that  $V_{gs}$  applied to TG turns on electron tunneling in the left side of the source and the gate overlap region near RG. As shown in Figure 3d–f, since the TG and RG are the same for these three EHBTFETs, an identical electron–hole bilayer can be induced in the gate overlap region. In the ON-state, electrons tunnel from the valence band of the hole layer into the conduction band of the electron layer under the action of  $V_{gs}$ . Therefore, lateral tunneling (see white arrows in Figure 3d–f) also exists in these three EHBTFETs. Through comparison, we can see that the region available for vertical tunneling is only a few nanometers wide, so can be named PT, while that for lateral tunneling covers the entire gate overlap region (50 nm in length), so can be named LT. Combining the non-local e-BTBT tunneling rate of these two types of tunneling, it follows that LT dominates in the ON-state but PT does in the OFF-state.

#### 3.2. Comparison of DC Performance among Three EHBTFETs

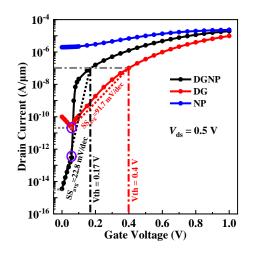

To compare DC performance, the transfer characteristics of DG-EHBTFET, NP-EHBTFET, and DGNP-EHBTFET are calculated and plotted in Figure 4. It is found from the figure that the  $I_{\text{OFF}}$  of the proposed DGNP-EHBTFET is  $3.54 \times 10^{-15}$  A/µm, which is about four and nine orders of magnitude lower than that of DG-EHBTFET and NP-EHBTFET ( $9.9 \times 10^{-11}$  A/µm and  $1.97 \times 10^{-6}$  A/µm), respectively. The  $I_{\text{ON}}$  of DGNP-EHBTFET is close to  $1.92 \times 10^{-5}$  A/µm, almost the same magnitude as that of NP-EHBTFET but higher than that of DG-EHBTFET. Therefore, the maximum  $I_{\text{ON}}/I_{\text{OFF}}$  can be obtained by DGNP-EHBTFET, and its value is  $5.42 \times 10^{9}$ .

Figure 4. Transfer characteristics of DG-EHBTFET, NP-EHBTFET, and DGNP-EHBTFET.

The tunneling current depends on the tunneling probability ( $P_{tun}$ ), which can be expressed as Equation (1) [14]

$$P_{\text{tun}} \propto \exp\left(-\frac{4\lambda\sqrt{2m*E_{\text{g}}^{3/2}}}{3|e|\hbar(E_{\text{g}}+\Delta\varphi)}\right) = \exp\left(-\frac{4\sqrt{2m*E_{\text{g}}^{3/2}}}{3|e|\hbar E}\right)$$

$$= \exp\left(-\frac{4\sqrt{2m*E_{\text{g}}^{3/2}}}{3|e|\hbar(E_{\text{g}}+\Delta\varphi)}\sqrt{\frac{\varepsilon_{\text{sem}}}{\varepsilon_{\text{die}}}t_{\text{sem}}t_{\text{die}}}\right)$$

(1)

where  $\Delta \varphi$  is the energy range used for carrier tunneling, *E* is the electric field, *m*<sup>\*</sup> is the effective carrier mass,  $\lambda$  is the tunneling distance,  $E_g$  is the band gap, and  $\varepsilon_{die}$ ,  $\varepsilon_{sem}$ ,  $t_{die}$ , and  $t_{sem}$  are the permittivity and the thickness of the dielectric and the bulk material, respectively. Since  $P_{tun}$  is closely related to  $\Delta \varphi$  and *E*, we can interpret the difference between  $I_{OFF}$  and  $I_{ON}$  for these three EHBTFETs based on them.

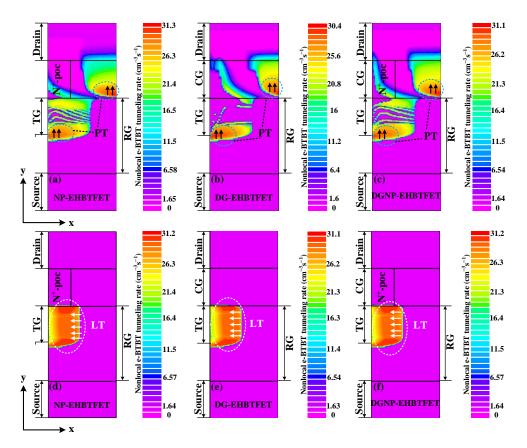

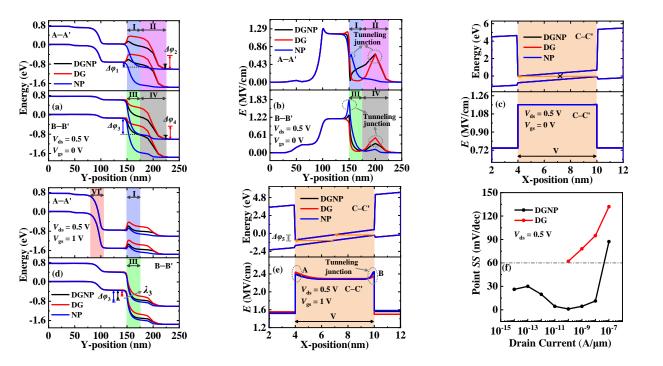

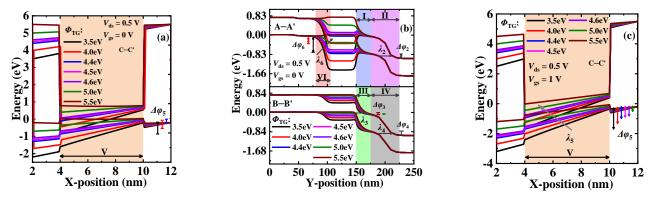

Figure 5 shows the energy band and the electric field profiles extracted along cutlines A–A', B–B', and C–C, respectively, in the OFF- and ON-states. To explain the physical

mechanism more clearly, six regions (i.e., regions I to VI) are defined in the figures of this paper. This is because two kinds of tunneling mechanisms (PT and LT) exist in these three EHBTFETs, which occur in different regions based on different devices and states (see Figures 2 and 3). As shown in Figure 5a, in the OFF-state, PT in NP-EHBTFET occurs in regions I and III, while that in DG- and DGNP-EHBTFETs occurs in regions II and IV. This is because the alignment of the conduction band and the valence band in these regions makes the energy range  $\Delta \varphi$  (named  $\Delta \varphi_1$  to  $\Delta \varphi_6$  in regions I to VI, respectively) that is available for carrier tunneling exist in regions I and III of NP-EHBTFET and regions II and IV of the other two EHBTFETs, respectively. Actually, the position of  $\Delta \varphi$  in DG-EHBTFET and DGNP-EHBTFET is different from that in NP-EHBTFET because the introduction of the control-gate CG lifts the energy band near it so as to shift the tunneling junction to the right. Moreover, for DGNP-EHBTFET, the simultaneous introduction of the CG and the N<sup>+</sup>-pocket can optimize its energy band profiles in four regions, which makes it have the narrowest  $\Delta \varphi$ . For further analysis, the electric field profiles in the OFF-state are calculated and plotted in Figure 5b. Since tunneling cannot occur in the regions without  $\Delta \varphi$ , we only compare *E* at the tunneling junctions of the four regions (see dotted circles in Figure 5b). It is observed that E at the tunneling junction of regions I and II is basically the same, but is very different in regions III and IV, so it can be inferred that the difference in  $P_{tun}$  mainly depends on *E* in regions III and IV. Obviously, DGNP-EHBTFET possesses the lowest *E* of the tunneling junction. The lower the *E* and the narrower the  $\Delta \varphi$ , the lower the *P*<sub>tun</sub> of DGNP-EHBTFET that can be obtained, according to Equation (1). Furthermore, in the OFF-state, the energy band and the electric field profiles based on LT are also calculated, as shown in Figure 5c. It is found that the identical *Es* exist in the region V for these three EHBTFETs, which can be explained by Equation (2), expressed as

$$E = \frac{E_{\rm g} + \Delta\varphi}{\lambda} = \frac{E_{\rm g} + \Delta\varphi}{\sqrt{\frac{\varepsilon_{\rm sem}}{\varepsilon_{\rm die}}t_{\rm sem}t_{\rm die}}}$$

(2)

**Figure 5.** (a) Energy band profiles along A–A' and B–B' in the OFF-state; (b) electric field profiles along A–A' and B–B' in the OFF-state; (c) energy band and electric field profiles along C–C' in the OFF-state; (d) energy band profiles along A–A' and B–B' in the ON-state; (e) energy band and electric field profiles along C–C' in the ON-state; and (f) point *SS* versus drain current for EHBTFETs.

Since the gate overlap region for these three EHBTFETs has the same dielectric and bulk materials, the same  $t_{\text{die}}$ ,  $t_{\text{sem}}$ ,  $\varepsilon_{\text{die}}$ ,  $\varepsilon_{\text{sem}}$ , and  $E_{\text{g}}$  are possessed in this region. Moreover, Figure 5c shows that there is no  $\Delta \varphi$  available for LT. According to Equation (2), the same *E* should exist in region V. Although there is *E* in region V,  $\Delta \varphi$  is absent; thus, no LT appears. It is thus clear that PT is dominant in the OFF-state, eventually resulting in DGNP-EHBTFET with the lowest  $I_{\text{OFF}}$ .

To investigate  $I_{ON}$ , the energy band profiles in the ON-state are calculated and shown in Figure 5d. It is seen that PT occurs in regions III and VI simultaneously because the applied  $V_{gs}$  bends down the energy bands in both regions. Due to the existence of CG, the energy bands of DG-EHBTFET are lifted obviously in regions I and III. The elevated energy band in region I hinders the tunneling electrons drifting to the drain, while that in region III reduces  $\Delta \varphi_3$  and increases  $\lambda_3$  so as to directly weaken the carrier tunneling, both of which lead to a reduction in the ION of DG-EHBTFET. Since the introduction of the N<sup>+</sup>-pocket can lower the energy bands in regions I and III, a high I<sub>ON</sub> can be maintained in DGNP-EHBTFET like in NP-EHBTFET. In the ON-state, the existence of  $\Delta \varphi$  (see  $\Delta \varphi_5$ in Figure 5e) enhances the *E* of LT, which is consistent with the result in Equation (2). However, unlike *E* in the OFF-state, *E* in regions A and B (see dotted circles in Figure 5e) in the ON-state further increases. This is because PT also affects the *E* of LT in the gate overlap region. It is observed from Figure 5d that the raised energy band in region I of DG-EHBTFET causes a large number of tunneling electrons from region VI to concentrate in the gate overlap region near TG, eventually resulting in the highest *E* in its region A. However, the existence of the N<sup>+</sup>-pocket bends the energy band downward in region III for NP-EHBTFET and DGNP-EHBTFET, which is more conducive to the accumulation of holes in the gate overlap region near RG, leading to a higher presence of E in region B (i.e., tunneling junction) of these two EHBTFETs. The higher the E, the higher the  $I_{ON}$  that can be obtained. Therefore, the *I*<sub>ON</sub> of three EHBTFETs results in the aforementioned results.

The average subthreshold swing  $(SS_{avg})$  is obtained using Equation (3) [9,14]

$$SS_{\text{avg}} = (V_{\text{th}} - V_{\text{OFF}}) / (\log I_{\text{Vth}} - \log I_{\text{VOFF}}),$$

(3)

where the subthreshold voltage ( $V_{\text{th}}$ ) represents  $V_{\text{gs}}$  at which the drain current ( $I_{\text{ds}}$ ) equals 0.1  $\mu$ A/ $\mu$ m (i.e.,  $I_{Vth}$ ),  $V_{OFF}$  is  $V_{gs}$  at which  $I_{ds}$  begins to increase with  $V_{gs}$ , and  $I_{VOFF}$  is the corresponding  $I_{ds}$  when  $V_{gs} = V_{OFF}$ . It is found from Figure 4 that neither the  $V_{th}$  nor  $SS_{avg}$  of NP-EHBTFET can be extracted because NP-EHBTFET has been turned on in the OFF-state. Thus, only the values of  $SS_{avg}$  and  $V_{th}$  for DG-EHBTFET and DGNP-EHBTFET are compared here. The V<sub>th</sub> and SS<sub>avg</sub> of DGNP-EHBTFET are 0.17 V and 22.8 mV/decade, respectively, which are reduced by 57.5% and 75.1%, respectively, compared with DG-EHBTFET. Moreover, DGNP-EHBTFET exhibits V<sub>OFF</sub> and I<sub>VOFF</sub> values approaching 0 V and  $3.54 \times 10^{-15}$  A/µm, respectively, lower than those of DG-EHBTFET. In particular, its  $I_{\text{VOFF}}$  is four orders of magnitude lower than that of DG-EHBTFET, which is because PT, known from the previous analysis, is dominant in the OFF-state. For these two EHBTFETs, LT begins to operate when  $V_{gs}$  is applied to the left-gate, and its influence on  $I_{ds}$  starts to exceed PT when  $V_{gs} > 0.06$  V (see  $I_{ds}$  distortion in the purple circles in Figure 4). Since the introduction of the N<sup>+</sup>-pocket can enhance the built-in electric field in the electron-hole bilayer so as to boost the  $P_{tun}$  of LT,  $I_{Vth}$  can be achieved under lower  $V_{th}$  for DGNP-EHBTFET, which is consistent with the results in Figure 4. As a result, a smaller difference between  $V_{\text{th}}$  and  $V_{\text{OFF}}$  and a greater one between  $I_{\text{Vth}}$  and  $I_{\text{VOFF}}$  exists in DGNP-EHBTFET, leading to a lower  $SS_{avg}$  in it. Point SS at each  $I_{ds}$  is expressed as  $dV_{gs}/d(\log I_{ds})$ . To clearly exhibit the change in SS, point SS values are extracted from the transfer characteristic curves and plotted in Figure 5f. Note that the point SS values of NP-EHBTFET cannot be extracted, and the reason is the same as for  $SS_{avg}$  extraction. It is observed from the figure that the proposed DGNP-EHBTFET has steeper point SS when  $V_{gs} < V_{th}$ , and its minimum point SS is as low as 1.1 mV/decade. Based on above analyses, DGNP-EHBTFET possesses better DC performance.

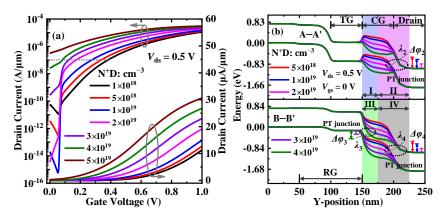

# 3.3. Effect of N<sup>+</sup>-Pocket on DGNP-EHBTFET

Figure 6a shows the transfer characteristics of DGNP-EHBTFET with the N<sup>+</sup>-pocket having a different N-type doping concentration (N<sup>+</sup>D). It is found from the figure that  $I_{OFF}$ decreases first, and then, increases with the increase in N<sup>+</sup>D, and achieves the minimum value at N<sup>+</sup>D = 2 × 10<sup>19</sup> cm<sup>-3</sup>. To interpret the variation in  $I_{OFF}$ , the energy band profiles in the OFF-state are calculated and shown in Figure 6b. It is observed from  $\Delta \varphi$  that PT appears in regions II and IV when  $N^+D \le 2 \times 10^{19}$  cm<sup>-3</sup> while the same occurs in region III when N<sup>+</sup>D > 2 × 10<sup>19</sup> cm<sup>-3</sup>. With the increase in N<sup>+</sup>D, both  $\Delta \varphi_2$  and  $\Delta \varphi_4$  decrease but  $\Delta \varphi_3$  increases. Though  $P_{\text{tun}}$  can be reduced by narrowing  $\Delta \varphi$  to obtain a lower  $I_{\text{OFF}}$ ,  $\lambda$ (named  $\lambda_1$  to  $\lambda_6$  in regions I to VI, respectively) should also be taken into account according to Equation (1). Unlike  $\lambda$  in region III, those in regions II and IV increase with N<sup>+</sup>D, and their lengths are greater. Hence, one can see that the maximum  $\lambda$  and the minimum  $\Delta \varphi$ simultaneously exist when N<sup>+</sup>D =  $2 \times 10^{19}$  cm<sup>-3</sup>, thereby resulting in the minimum P<sub>tun</sub> based on Equation (1), eventually obtaining the minimum  $I_{OFF}$ . In fact, the change in the trend of  $I_{OFF}$  is dependent on the position of the PT junction (see black dotted circles in Figure 6b). Since CG can induce holes in the top gate underlap region, PN junctions available for tunneling (i.e., the PT junction in regions II and IV) can be created between this region and the drain region. With there is an increase in  $N^+D$ , the increasing electrons in the top gate underlap region bend the energy band downward so as to reduce the aligned energy range for tunneling, eventually degrading  $I_{OFF}$ . When N<sup>+</sup>D > 2 × 10<sup>19</sup> cm<sup>-3</sup>, the PT junction shifts to region III because a new PN junction is formed by electron accumulation in the top gate underlap region and hole accumulation in the gate overlap region near RG. With the further increase in  $N^+D$ , more electrons gather in the top gate underlap region, which enlarges  $\Delta \varphi$  so as to promote the electron tunneling. Therefore,  $I_{OFF}$  exhibits an increasing trend. Moreover, further investigation reveals that there is basically no impact of the variation in N<sup>+</sup>D on LT in the OFF-state. With the increase in N<sup>+</sup>D,  $I_{ON}$  values exhibit a similar trend of linear increase and are in the same order of magnitude, which is because the electric field at the LT junction is slightly adjusted with the change in  $N^+D$  on the basis of the same electron-hole bilayer. It can also be found from Figure 6a that the lower the  $V_{gs}$ , the greater the influence of N<sup>+</sup>D on  $I_{ds}$ . This is because at low  $V_{gs}$ , LT mainly depends on the built-in electric field in the electron-hole bilayer, which can be enhanced with an increase in N<sup>+</sup>D. A stronger built-in electric field will cause a higher  $P_{tun}$  of LT so as to turn on DGNP-EHBTFET more easily. Therefore, with the increase in N<sup>+</sup>D, V<sub>th</sub> takes on a linear decreasing trend, except that it cannot be extracted when N<sup>+</sup>D =  $5 \times 10^{19}$  cm<sup>-3</sup>.  $I_{ON}/I_{OFF}$ exhibits the opposite trend to  $I_{\rm OFF}$ , and approaches the maximum value of  $5.42 \times 10^9$  at  $N^+D = 2 \times 10^{19} \text{ cm}^{-3}$ . Benefiting from the minimum  $I_{VOFF}$  and the low  $V_{th}$ , the minimum  $SS_{avg}$  is reached when N<sup>+</sup>D = 2 × 10<sup>19</sup> cm<sup>-3</sup>. As a result, the optimal device performance can be obtained at N<sup>+</sup>D =  $2 \times 10^{19}$  cm<sup>-3</sup>.

**Figure 6.** (a) Transfer characteristics and (b) energy band profiles along A–A' and B–B' in the OFF-state, for DGNP-EHBTFET with N<sup>+</sup>D =  $5 \times 10^{18} \sim 4 \times 10^{19}$  cm<sup>-3</sup>.

Next, the influence of the width of the N<sup>+</sup>-pocket ( $W_p$ ) on the DC performance is studied. Figure 7a shows the transfer characteristic curves of DGNP-EHBTFET at  $W_p = 1 \sim 4$  nm, from which various DC parameters such as  $I_{OFF}$ ,  $V_{th}$ ,  $SS_{avg}$ , etc., can be extracted. By compromising these extracted parameters, it follows that DGNP-EHBTFET possesses the optimal DC performance at  $W_p = 2$  nm. Meanwhile, it is found that Figures 7a and 6a have the same change trend in different cases, which is because  $W_p$  and N<sup>+</sup>D have identical mechanisms of influence on DGNP-EHBTFET. For example, it is observed from Figure 7b that PT occurs in regions II and IV when  $W_p \leq 2$  nm, while it occurs in region III when  $W_p > 2$  nm. Similarly, DGNP-EHBTFET is of the maximum  $\lambda$  and the minimum  $\Delta \varphi$  at  $W_p = 2$  nm, which makes it have the minimum  $I_{OFF}$  under this condition. As shown in Figure 7c, the energy bands in regions I and III gradually bend downward with the increase in  $W_p$ , which promotes the drift of tunneling electrons in region VI and the tunneling of electrons in region III, respectively. However, a slight influence of  $W_p$  on LT is dominant in the ON-state; thus,  $I_{ON}$  increases with  $W_p$  but has the same order of magnitude.

**Figure 7.** (a) Transfer characteristics; (b) energy band profiles along A–A' and B–B' in the OFFstate; and (c) energy band profiles along A–A' and B–B' in the ON-state, for DGNP-EHBTFET with  $W_p = 1 \sim 4$  nm.

### 3.4. Effect of Gate Work-Function on DGNP-EHBTFET

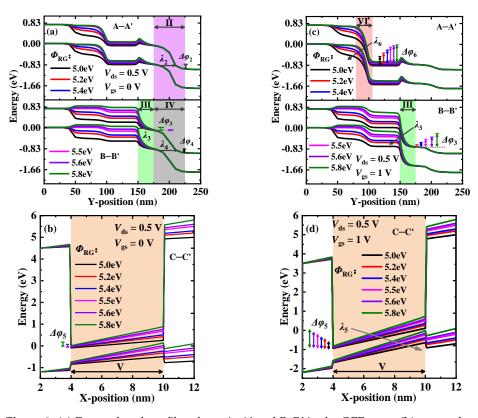

Here, we investigate the effect of the work-functions of the right-gate RG, the tunnelinggate TG, and the control-gate CG (i.e.,  $\Phi_{\rm RG}$ ,  $\Phi_{\rm TG}$ , and  $\Phi_{\rm CG}$ , respectively) on DGNP-EHBTFET, respectively. Table 2 shows the extracted parameters at  $\Phi_{RG} = 5.0 \times 5.8$  eV. It is found that  $I_{\text{OFF}}$  maintains a relatively low value at  $\Phi_{\text{RG}} \leq 5.5$  eV, but boosts sharply by six orders of magnitude with the further increase in  $\Phi_{RG}$ , which can be seen in the energy band profiles. As shown in Figure 8a, PT occurs in regions II and IV is exactly the same under different  $\Phi_{\rm RG}$  levels. Moreover, because the hole concentration near RG increases with  $\Phi_{RG}$  so as to lift the energy bands in region III, PT can also take place in this region when  $\Phi_{\rm RG} > 5.5$  eV. Since narrow  $\Delta \varphi$  and wide  $\lambda$  exist in these tunneling regions, the effect of  $\Phi_{\rm RG}$  on PT is insignificant in the OFF-state. Furthermore, it is observed from Figure 8b that LT is opened in region V when  $\Phi_{RG} > 5.5$  eV. According to the changing trend of  $I_{OFF}$ , it can be concluded that when  $\Phi_{\text{RG}} > 5.5$  eV, the rapid increase in  $I_{\text{OFF}}$  is mainly caused by LT. Figure 8c,d show the energy band profiles in the ON-state regarding PT and LT, respectively. It is seen that with the decrease in  $\Phi_{\rm RG}$ ,  $\Delta \phi$  reduces but  $\lambda$  increases in regions III, V, and VI, particularly when  $\Phi_{RG}$  = 5.0 eV, and there is no tunneling in region III. Therefore,  $I_{ON}$ shows a monotonic decreasing trend with the reduction in  $\Phi_{RG}$  and achieves the minimum value at  $\Phi_{RG}$  = 5.0 eV. Both SS<sub>avg</sub> and V<sub>th</sub> cannot be extracted at  $\Phi_{RG}$  = 5.0 eV as DGNP-EHBTFET is still turned off, even when  $V_{gs} = 1.0$  V. Note that parameters that cannot be extracted in this paper are all represented by N/A. Moreover, with the increase in  $\Phi_{RG}$ ,  $I_{\rm ON}/I_{\rm OFF}$  represents a trend of increasing first, and then, decreasing, and  $V_{\rm th}$  exhibits the opposite trend to I<sub>ON</sub>. By comparing these parameters, we assume that DGNP-EHBTFET can maintain better device performance when  $\Phi_{\rm RG}$  = 5.5 eV.

**Figure 8.** (a) Energy band profiles along A–A' and B–B' in the OFF-state; (b) energy band profiles along C–C' in the OFF-state; (c) energy band profiles along A–A' and B–B' in the ON-state; and (d) energy band profiles along C–C' in the ON-state, for DGNP-EHBTFET with  $\Phi_{RG} = 5.0 \sim 5.8$  eV.

| $\Phi_{ m RG}$ (eV) | I <sub>OFF</sub> (A/μm) | I <sub>ON</sub> (A/µm) | I <sub>ON</sub> /I <sub>OFF</sub> | $V_{\rm th}$ (V) | $SS_{ m avg}$ (mV/dec) |

|---------------------|-------------------------|------------------------|-----------------------------------|------------------|------------------------|

| 5.0                 | $1.50	imes10^{-19}$     | $1.87 	imes 10^{-8}$   | $1.25 	imes 10^{11}$              | N/A              | N/A                    |

| 5.2                 | $1.15 	imes 10^{-18}$   | $1.20 	imes 10^{-6}$   | $1.04 	imes 10^{12}$              | 0.52             | 30.7                   |

| 5.4                 | $2.59	imes10^{-17}$     | $5.79 	imes 10^{-6}$   | $2.24 	imes 10^{11}$              | 0.32             | 33.4                   |

| 5.5                 | $3.54	imes10^{-15}$     | $1.92 	imes 10^{-5}$   | $5.42 	imes 10^9$                 | 0.17             | 22.8                   |

| 5.6                 | $2.58	imes10^{-9}$      | $2.87 	imes 10^{-5}$   | $1.11 	imes 10^4$                 | 0.14             | 88.1                   |

| 5.8                 | $5.16 	imes 10^{-9}$    | $4.30 	imes 10^{-5}$   | $8.33 \times 10^3$                | 0.11             | 85.4                   |

**Table 2.** Extracted parameters from transfer characteristic curves at  $\Phi_{RG}$  = 5.0~5.8 eV.

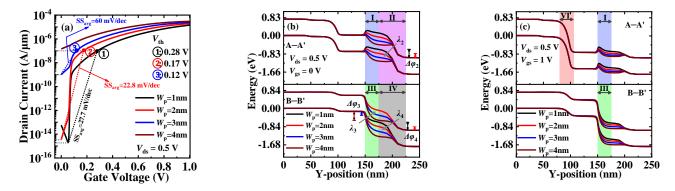

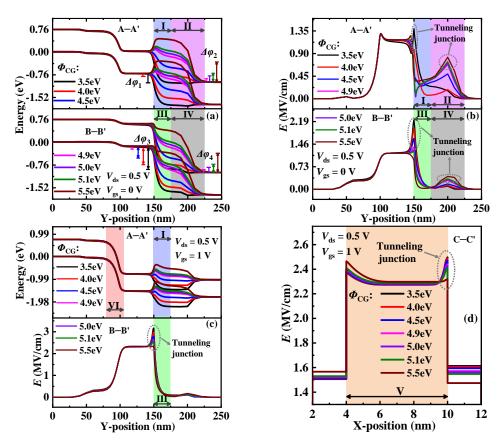

Table 3 lists the parameters extracted from the transfer characteristic curves at different  $\Phi_{\text{TG}}$  levels. It is found that with the increase in  $\Phi_{\text{TG}}$ ,  $I_{\text{OFF}}$  decreases first, and then, increases, and obtains the minimum value when  $\Phi_{TG}$  = 4.5 eV. To explain in detail, the energy band profiles of LT and PT are calculated. As shown in Figure 9a, when  $\Phi_{TG}$  < 4.5 eV, the accumulation of a large number of electrons near TG opens LT in the OFF-state; thus, the  $I_{OFF}$  values are much higher than that in other cases. In addition, with the increase in  $\Phi_{TG}$ ,  $\Delta \varphi_5$  decreases and  $\lambda_5$  increases, resulting in a gradual reduction in  $I_{OFF}$ . When  $\Phi_{\rm TG} \ge 4.5$  eV,  $I_{\rm OFF}$  is dependent on PT, which makes it have a substantial reduction. Since  $\Phi_{\text{TG}}$  just affects the carrier concentration of the gate overlap region (i.e., region V), only the energy bands in this region and the regions connected to it will be adjusted with the change in  $\Phi_{TG}$ . It is observed from Figure 9b that the energy bands in region III lift with the increase in  $\Phi_{TG}$ , and a new PT appears in this region when  $\Phi_{TG} > 4.6$  eV; therefore,  $I_{\rm OFF}$  begins to increase obviously. It is found from Figure 9c that when  $\Phi_{\rm TG}$  < 5.5 eV, LT is dominant in the ON-state, and I<sub>ON</sub> shows a slowly decreasing trend with increasing  $\Phi_{\rm TG}$  based on the variation in  $\Delta \varphi_5$  and  $\lambda_5$ . It is worth noting that only PT exists when  $\Phi_{\text{TG}}$  = 5.5 eV, and it appears in regions I and III (not shown). As a result, the minimum

$I_{\rm ON}$  is obtained at this  $\Phi_{\rm TG}$ . Furthermore, the optimal values of  $I_{\rm ON}/I_{\rm OFF}$  and  $SS_{\rm avg}$  can be obtained at  $\Phi_{\rm TG}$  = 4.5 eV. Comprehensive analysis shows that  $\Phi_{\rm TG}$  = 4.5 eV is the best choice for DGNP-EHBTFET.

**Figure 9.** (a) Energy band profiles along C–C' in the OFF-state; (b) energy band profiles along A–A' and B–B' in the OFF-state; and (c) energy band profiles along C–C' in the ON-state, for DGNP-EHBTFET with  $\Phi_{TG}$  = 3.5~5.5 eV.

| Table 3. Extracted | parameters from transfer | characteristic curves at | $\Phi_{TG} = 3.5 \sim 5.5 \text{ eV}.$ |

|--------------------|--------------------------|--------------------------|----------------------------------------|

|--------------------|--------------------------|--------------------------|----------------------------------------|

| $\Phi_{ m TG}$ (eV) | I <sub>OFF</sub> (A/µm) | $I_{\rm ON}$ (A/ $\mu$ m) | I <sub>ON</sub> /I <sub>OFF</sub> | $V_{\rm th}$ (V) | SS <sub>avg</sub> (mV/dec) |

|---------------------|-------------------------|---------------------------|-----------------------------------|------------------|----------------------------|

| 3.5                 | $1.64 	imes 10^{-7}$    | $2.19	imes10^{-5}$        | $1.34 	imes 10^2$                 | N/A              | N/A                        |

| 4.0                 | $7.87	imes10^{-8}$      | $2.11	imes10^{-5}$        | $2.68 	imes 10^2$                 | 0.02             | 192.3                      |

| 4.4                 | $7.90	imes10^{-9}$      | $1.99	imes10^{-5}$        | $2.52 \times 10^3$                | 0.12             | 108.9                      |

| 4.5                 | $3.54	imes10^{-15}$     | $1.92 	imes 10^{-5}$      | $5.42 	imes 10^9$                 | 0.17             | 22.8                       |

| 4.6                 | $8.51	imes10^{-15}$     | $1.81 	imes 10^{-5}$      | $2.13 	imes 10^9$                 | 0.24             | 33.9                       |

| 5.0                 | $1.03	imes10^{-13}$     | $9.93	imes10^{-6}$        | $9.64	imes10^7$                   | 0.48             | 80.2                       |

| 5.5                 | $6.86 	imes 10^{-13}$   | $3.43 	imes 10^{-6}$      | $5.00 	imes 10^6$                 | 0.51             | 98.8                       |

Further, the influence of  $\Phi_{CG}$  on DGNP-EHBTFET is examined, and parameters related to DC performance are extracted and listed in Table 4. As shown in Figure 10a, since the variation in  $\Phi_{CG}$  can adjust the energy band profiles in regions I to IV, the region where PT appears varies with  $\Phi_{CG}$ . Because tunneling only exists in the regions with  $\Delta \varphi$ , we only compare E at the tunneling junction to explain the changing trend of  $I_{OFF}$ . As shown in Figure 10b, when  $\Phi_{CG}$  < 4.5 eV, high *E* exists simultaneously at the tunneling junction of regions I and III, which results in a high I<sub>OFF</sub> and turns on DGNP-EHBTFET in the OFF-state. When  $\Phi_{CG} > 4.5$  eV, *E* at the tunneling junction of regions II and IV increases with  $\Phi_{CG}$ , and there is also high *E* at the tunneling junction of region III at  $\Phi_{CG} = 4.9$  eV. As a result,  $I_{OFF}$  decreases first, and then, increases, and achieves the minimum  $I_{OFF}$  at  $\Phi_{\rm CG}$  = 5.0 eV. It is observed from Figure 10c that PT in region VI is insensitive to the change in  $\Phi_{CG}$ , but the energy band in region I elevates with the increase in  $\Phi_{CG}$ ; especially when  $\Phi_{CG} > 4.5$  eV it begins to hinder the drift of the tunneling electrons, eventually degrading device performance in the ON-state. Moreover, with the increase in  $\Phi_{CG}$ , *E* in the tunneling junction of region III gradually weakens, which reduces the  $P_{tun}$  of PT. As shown in Figure 10d, the varying trend of E at the LT junction of region V is the same as that in region III, thereby lowering the  $P_{tun}$  of LT with increasing  $\Phi_{CG}$ . Therefore,  $I_{ON}$  decreases with the increase in  $\Phi_{CG}$ , which is consistent with the results in Table 4. Furthermore, by comparison of the extracted parameters in Table 4, it follows that DGNP-EHBTFET can obtain optimal device performance only when  $\Phi_{CG} = 5.0$  eV.

**Figure 10.** (a) Energy band profiles along A–A' and B–B' in the OFF-state; (b) electric field profiles along A–A' and B–B' in the OFF-state; (c) energy band profiles along A–A' and electric field profiles along B–B', in the ON-state; and (d) electric field profiles along C–C' in the ON-state, for DGNP-EHBTFET with  $\Phi_{CG} = 3.5 \sim 5.5$  eV.

| $\Phi_{ m CG}$ (eV) | I <sub>OFF</sub> (A/μm) | $I_{\rm ON}$ (A/ $\mu$ m) | $I_{\rm ON}/I_{\rm OFF}$ | $V_{\rm th}$ (V) | SS <sub>avg</sub> (mV/dec) |

|---------------------|-------------------------|---------------------------|--------------------------|------------------|----------------------------|

| 3.5                 | $1.47 	imes 10^{-5}$    | $4.57 	imes 10^{-5}$      | $3.11 	imes 10^0$        | N/A              | N/A                        |

| 4.0                 | $3.43	imes10^{-6}$      | $3.79	imes10^{-5}$        | $1.10 	imes 10^1$        | N/A              | N/A                        |

| 4.5                 | $9.13	imes10^{-8}$      | $2.90 	imes 10^{-5}$      | $3.18 	imes 10^2$        | 0.02             | 506                        |

| 4.9                 | $4.39	imes10^{-12}$     | $2.13	imes10^{-5}$        | $4.85 	imes 10^6$        | 0.14             | 32.1                       |

| 5.0                 | $3.54	imes10^{-15}$     | $1.92 	imes 10^{-5}$      | $5.42 	imes 10^9$        | 0.17             | 22.8                       |

| 5.1                 | $4.96	imes10^{-15}$     | $1.68 	imes 10^{-5}$      | $3.39 	imes 10^9$        | 0.23             | 31.5                       |

| 5.5                 | $7.04 	imes 10^{-10}$   | $6.37 	imes 10^{-6}$      | $9.05 	imes 10^3$        | 0.52             | 105                        |

**Table 4.** Extracted parameters from transfer characteristic curves at  $\Phi_{CG}$  = 3.5~5.5 eV.

# 4. Conclusions

In conclusion, an  $In_{0.53}Ga_{0.47}As$  electron-hole bilayer TFET with a dual-metal left-gate and an N<sup>+</sup>-pocket is proposed and investigated in detail using the Silvaco Atlas 2D numerical simulation platform. The numerical simulations demonstrate that the simultaneous introduction of the control-gate and the N<sup>+</sup>-pocket for the proposed DGNP-EHBTFET can optimize the energy band profiles in the tunneling regions so as to substantially degrade the OFF-state current and maintain good ON-state performance. Further, the impact of the N<sup>+</sup>-pocket on DGNP-EHBTFET is investigated, and the results show that both N<sup>+</sup>D and  $W_p$  focus on the adjustment of the tunneling energy range and the tunneling distance of PT, thereby mainly affecting  $I_{OFF}$ . By compromise of the extracted various parameters, the optimal DC performance can be obtained when N<sup>+</sup>D = 2 × 10<sup>19</sup> cm<sup>-3</sup> and  $W_p$  = 2 nm. Considering the change in  $\Phi_{RG}$  and  $\Phi_{TG}$ , it is observed that both can control LT and PT through the regulation of the carrier concentration in the overlap region, and comprehensive analysis illustrates that only when  $\Phi_{RG} = 5.5 \text{ eV}$  and  $\Phi_{TG} = 4.5 \text{ eV}$  can good device performance be maintained. Furthermore, the investigation shows that the variation in  $\Phi_{CG}$  can not only change the electric field of the tunneling junction, but it can also regulate and control the drift of tunneling electrons. The results show that  $\Phi_{CG} = 5.0 \text{ eV}$  is the best choice for better DC performance. This paper focuses on revealing the OFF-state leakage suppression mechanism and optimizing the device parameters, without considering the static and dynamic behavior of the proposed DGNP-EHBTFET. In view of their importance, we will put emphasis on this aspect in our next work.

Author Contributions: Conceptualization, H.L., W.Z., Z.W., Y.L. and H.Z.; methodology, H.L. and W.Z.; software, H.L.; validation, Z.W. and H.L.; formal analysis, W.Z. and H.L.; investigation, Y.L. and H.L.; resources, H.Z. and H.L.; data curation, H.L.; writing—original draft preparation, H.L. and W.Z.; writing—review and editing, H.L. and Z.W.; visualization, H.L. and W.Z.; supervision, H.L.; project administration, H.L.; funding acquisition, H.L. and Y.L. All authors have read and agreed to the published version of the manuscript.

**Funding:** This research was funded by the National Natural Science Foundation of China (Grant No. 62264008), the Natural Science Foundation of Gansu Province (Grant No. 21JR7RA320), the Project of Construction of a strong Province with Intellectual Property Rights (Grant No. 20ZSCQ006), the Youth Program of the National Natural Science Foundation of China (Grant No. 61905102), and the Gansu Youth Science and Technology Fund Program (Grant No. 20JR5RA385).

Institutional Review Board Statement: Not applicable.

Informed Consent Statement: Not applicable.

**Data Availability Statement:** The data presented in this study are available on request from the corresponding author.

Conflicts of Interest: The authors declare no conflict of interest.

## References

- 1. Boucart, K.; Ionescu, A.M. Double-gate tunnel fet with high-κ gate dielectric. *IEEE Trans. Electron. Devices* 2007, 54, 1725–1733. [CrossRef]

- 2. Ghosh, B.; Akram, M.W. Junctionless tunnel field effect transistor. IEEE Electron. Device Lett. 2013, 34, 584–586. [CrossRef]

- Kumar, M.J.; Janardhanan, S. Doping-less tunnel field effect transistor: Design and investigation. *IEEE Trans. Electron. Devices* 2013, 60, 3285–3290. [CrossRef]

- 4. Kumar, N.; Raman, A. Performance Assessment of the Charge-Plasma-Based Cylindrical GAA Vertical Nanowire TFET with Impact of Interface Trap Charges. *IEEE Trans. Electron. Devices* **2019**, *66*, 4453–4460. [CrossRef]

- 5. Gupta, A.K.; Raman, A.; Kumar, N. Design and Investigation of a Novel Charge Plasma-Based Core-Shell Ring-TFET: Analog and Linearity Analysis. *IEEE Trans. Electron. Devices* **2019**, *66*, 3506–3512. [CrossRef]

- 6. Choi, Y.; Hong, Y.; Ko, E.; Shin, C. Optimization of double metal-gate InAs/Si heterojunction nanowire TFET. *Semicond. Sci. Technol.* **2020**, *35*, 075024. [CrossRef]

- Misra, R.; Singh, K.; Kumar, M.; Rastogi, R.; Kumar, A.; Dubey, S. An Ultra-Low-Power Black Phosphorus (B-Ph)/Si Heterojunction Dopingless-Tunnel FET (HD-TFET) with Enhanced Electrical Characteristics. *Superlattices Microstruct.* 2021, 149, 106752. [CrossRef]

- Tripathy, M.R.; Singh, A.K.; Samad, A.; Chander, S.; Baral, K.; Singh, P.K.; Jit, S. Device and Circuit-Level Assessment of GaSb/Si Heterojunction Vertical Tunnel-FET for Low-Power Applications. *IEEE Trans. Electron. Devices* 2020, 67, 1285–1292. [CrossRef]

- Liu, H.; Yang, L.A.; Jin, Z.; Hao, Y. An In<sub>0.53</sub>Ga<sub>0.47</sub>As/In<sub>0.52</sub>Al<sub>0.48</sub>As Heterojunction Dopingless Tunnel FET with a Heterogate Dielectric for High Performance. *IEEE Trans. Electron. Devices* 2019, *66*, 3229–3235. [CrossRef]

- 10. Pindoo, I.A.; Sinha, S.K.; Chander, S. Improvement of Electrical Characteristics of SiGe Source Based Tunnel FET Device. *Silicon* **2021**, *13*, 3209–3215. [CrossRef]

- 11. Liu, H.; Yang, L.A.; Chen, Y.; Jin, Z.; Hao, Y. Performance enhancement of the dual-metal gate In<sub>0.53</sub>Ga<sub>0.47</sub>As dopingless TFET by using a platinum metal strip insertion. *Jpn. J. Appl. Phys.* **2019**, *58*, 104001. [CrossRef]

- 12. Gedam, A.; Acharya, B.; Mishra, G.P. Junctionless Silicon Nanotube TFET for Improved DC and Radio Frequency Performance. *Silicon* 2021, *13*, 167–178. [CrossRef]

- 13. Raad, B.R.; Tirkey, S.; Sharma, D.; Kondekar, P. A new design approach of dopingless tunnel fet for enhancement of device characteristics. *IEEE Trans. Electron. Devices* 2017, 64, 1830–1836. [CrossRef]

- 14. Liu, H.; Yang, L.A.; Zhang, H.W.; Zhang, B.T.; Zhang, W.T. An In<sub>0.53</sub>Ga<sub>0.47</sub>As/In<sub>0.52</sub>Al<sub>0.48</sub>As/In<sub>0.53</sub>Ga<sub>0.47</sub>As double heterojunction junctionless TFET. *Jpn. J. Appl. Phys.* **2021**, *60*, 074001. [CrossRef]

- 15. Xu, H.F.; Han, X.F.; Sun, W. Design and investigation of dopingless double-gate line tunneling transistor: Analog performance, linearity, and harmonic distortion analysis. *Chin. Phys. B* **2020**, *29*, 108502. [CrossRef]

- 16. Ghosh, P.; Bhowmick, B. Investigation of Electrical Characteristics in a Ferroelectric L-Patterned Gate Dual Tunnel Diode TFET. *IEEE Trans. Ultrason. Ferroelectr. Freq. Control* 2020, 67, 2440–2444. [CrossRef]

- Xie, H.W.; Liu, H.X.; Han, T.; Li, W.; Chen, S.P.; Wang, S.L. TCAD Simulation of a Double L-shaped gate Tunnel Field Effect Transistor with covered source–channel. *Micro Nano Lett.* 2020, 15, 272–276. [CrossRef]

- Ahangari, Z. Performance investigation of steep-slope core-shell nanotube indium nitride electron-hole bilayer tunnel field effect transistor. *Appl. Phys. A Mater. Sci. Process.* 2019, 125, 405. [CrossRef]

- Kim, S.; Choi, W.Y.; Park, B.G. Vertical-Structured Electron-Hole Bilayer Tunnel Field-Effect Transistor for Extremely Low-Power Operation with High Scalability. *IEEE Trans. Electron. Devices* 2018, 65, 2010–2015. [CrossRef]

- Padilla, J.L.; Medina-Bailon, C.; Alper, C.; Gamiz, F.; Ionescu, A.M. Confinement-induced InAs/GaSb heterojunction electron–hole bilayer tunneling field-effect transistor. *Appl. Phys. Lett.* 2018, 112, 182101. [CrossRef]

- Masoudi, A.; Ahangari, Z.; Fathipour, M. Performance optimization of a nanoscale GaSb P-channel electron-hole bilayer tunnel field effect transistor using metal gate workfunction engineering. *Mater. Res. Express* 2019, *6*, 096311. [CrossRef]

- Padilla, J.L.; Medina-Bailon, C.; Marquez, C.; Sampedro, C.; Donetti, L.; Gamiz, F.; Ionescu, A.M. Gate Leakage Tunneling Impact on the InAs/GaSb Heterojunction Electron-Hole Bilayer Tunneling Field-Effect Transistor. *IEEE Trans. Electron. Devices* 2018, 65, 4679–4686. [CrossRef]

- Ahangari, Z. Design and performance optimization of thin film tin monoxide (SnO)/silicon electron–hole bilayer tunnel field-effect transistor. J. Comput. Electron. 2020, 19, 1485–1493. [CrossRef]

- 24. Shamloo, H.; Goharrizi, A.Y. Performance study of tunneling field effect transistors based on the graphene and phosphorene nanoribbons. *Micro Nanostruct.* 2022, *169*, 207336. [CrossRef]

- Jiang, X.; Shi, X.; Zhang, M.; Wang, Y.; Zhang, D.W. A symmetric tunnel field-effect transistor based on mos2/black phosphorus/mos2 nanolayered heterostructures. ACS Appl. Nano Mater. 2019, 2, 5674–5680. [CrossRef]

- Jiao, X.; Jia, J.; Shen, L.; Ju, J.; Lee, S. Tunneling field effect transistor integrated with black phosphorus-mos2 junction and ion gel dielectric. *Appl. Phys. Lett.* 2017, 110, 033103.

- Iida, R.; Kim, S.H.; Yokoyama, M.; Taoka, N. Planar-type In<sub>0.53</sub>Ga<sub>0.47</sub>As channel band-to-band tunneling metal-oxidesemiconductor field-effect transistors. J. Appl. Phys. 2011, 110, 124505. [CrossRef]

- Ahn, D.H.; Yoon, S.H.; Takenaka, M.; Takagi, S. Effects of HfO<sub>2</sub>/Al<sub>2</sub>O<sub>3</sub> gate stacks on electrical performance of planar In<sub>x</sub>Ga<sub>1-x</sub>As tunneling field-effect transistors. *Appl. Phys. Express* 2017, *10*, 084201. [CrossRef]

- 29. Seo, J.H.; Yoon, Y.J.; Cho, S.; Kang, I.M.; Lee, J.H. Design optimization and analysis of ingaas/inas/ingaas heterojunction-based electron hole bilayer tunneling fets. *J. Nanosci. Nanotechnol.* **2019**, *19*, 6070–6076. [CrossRef]

- Alper, C.; Palestri, P.; Padilla, J.L.; Ionescu, A.M. The Electron-Hole Bilayer TFET: Dimensionality Effects and Optimization. *IEEE Trans. Electron. Devices* 2016, 63, 2603–2609. [CrossRef]

- 31. Alper, C.; Palestri, P.; Padilla, J.L.; Ionescu, A.M. Underlap counterdoping as an efficient means to suppress lateral leakage in the electron–hole bilayer tunnel FET. *Semicond. Sci. Technol.* **2016**, *31*, 045001. [CrossRef]

- Loan, S.A.; Alharbi, A.G.; Rafat, M. Ambipolar leakage suppression in electron–hole bilayer TFET: Investigation and analysis. J. Comput. Electron. 2018, 17, 977–985.

- Sahu, C.; Singh, J. Charge-Plasma Based Process Variation Immune Junctionless Transistor. IEEE Electron. Device Lett. 2014, 35, 411–413. [CrossRef]

- 34. Hueting, R.J.E.; Rajasekharan, B.; Salm, C.; Schmitz, J. The Charge Plasma P-N Diode. *IEEE Electron. Device Lett.* 2008, 29, 1367–1369. [CrossRef]

- 35. Lide, D.R. CRC Handbook of Chemistry and Physics, 89th ed.; Taylor and Francis: New York, NY, USA, 2008; p. 12.

- Kawano, H.; Takahashi, T.; Tagashira, Y.; Mine, H.; Moriyama, M. Work function of refractory metals and its dependence upon working conditions. *Surf. Sci.* 1999, 146, 105–108. [CrossRef]

- Vurgaftman, I.; Meyer, J.R.; Ram-Mohan, L.R. Band parameters for III–V compound semiconductors and their alloys. *J. Appl. Phys.* 2001, *89*, 5815–5875. [CrossRef]

- Suzuki, R.; Taoka, N.; Yokoyama, M.; Lee, S.; Kim, S.H.; Hoshii, T.; Yasuda, T.; Jevasuwan, W.; Maeda, T.; Ichikawa, O.; et al. 1-nm-capacitance-equivalent-thickness HfO<sub>2</sub>/Al<sub>2</sub>O<sub>3</sub>/InGaAs metal-oxide-semiconductor structure with low interface trap density and low gate leakage current density. *Appl. Phys. Lett.* 2012, 100, 132906. [CrossRef]

- Zhao, H.; Chen, Y.; Wang, Y.; Zhou, F.; Xue, F.; Lee, J. InGaAs Tunneling Field-Effect-Transistors with Atomic-Layer-Deposited Gate Oxides. *IEEE Trans. Electron. Devices* 2011, 58, 2990–2995. [CrossRef]