# Article Grid-Tied Single-Phase Integrated Zeta Inverter for Photovoltaic Applications

Anderson Aparecido Dionizio <sup>1</sup>, Leonardo Poltronieri Sampaio <sup>1,\*</sup>, Sérgio Augusto Oliveira da Silva <sup>1</sup> and Sebastián de Jesús Manrique Machado <sup>2</sup>

- <sup>1</sup> Electrical Engineering Department, Federal University of Technology—Paraná, Cornélio Procópio 86300-000, PR, Brazil; dionizio@alunos.utfpr.edu.br (A.A.D.); augus@utfpr.edu.br (S.A.O.d.S.)

- <sup>2</sup> Electrical Engineering Department, Federal University of Technology—Paraná, Apucarana 86812-460, PR, Brazil; sebastiand@utfpr.edu.br

- \* Correspondence: sampaio@utfpr.edu.br

**Abstract:** Recently, the development of integrated inverters for photovoltaic systems has been widely performed to reduce overall system size, costs, and losses. Thus, integrated inverters have emerged as a prominent solution for replacing two-stage power conversion composed of a step-up converter and a voltage source inverter. Thereby, this paper proposes an integrated inverter topology for single-phase grid-tied photovoltaic systems. The proposed power converter, called a Single-Phase Integrated Zeta Inverter (SP-IZI), can boost the input voltage and inject a sinusoidal and regulated current into the mains with low harmonic distortion. The SP-IZI is based on integrating modified DC-DC Zeta converters, designed and controlled to operate in a discontinuous conduction mode, and presents similarities with the Modified Zeta Inverter (MZI). In this way, this paper compares the main parameters of both topologies and provides a complete study of the SP-IZI, involving both quantitative and qualitative studies as well as a small signals analysis. The feasibility and functionality of the proposed SP-IZI inverter are presented and evaluated through experimental results, which demonstrate that the SP-IZI presents the following advantages compared to the MZI: (i) the voltage in coupling capacitors is 13% lower; (ii) voltage stresses in switches and diodes are 40% lower; and (iii) static gain is similar to the traditional Zeta converter.

**Keywords:** DC-AC power conversion; integrated inverter; integrated zeta inverter; photovoltaic systems; zeta converter

## 1. Introduction

Research and technological development involving renewable energies have been growing considerably in the past years [1–4]. This growth is mainly motivated by the necessity of expanding electricity generation and distribution by employing technologies that cause less environmental impact than traditional energy sources, such as those based on fossil fuels and mineral coal [3,5]. In this way, regulatory agencies are fundaments in regulating, inspecting, and promoting environmentally friendly electrical energy sources [6,7].

Particularly, photovoltaic (PV) systems can be widely used in various commercial/ residential and industrial applications. However, PV panels present low efficiency, about 27% in the more efficient structures. Different materials have been used in PV panel building in the last years, reaching higher efficiency [8].

On the other hand, these sources produce direct current (DC) power, so it cannot be directly integrated into the conventional AC utility grid. Hence, it is necessary to make adequate the level and waveform of their voltages to achieve proper uses. Thus, the conditioning of this energy source can be performed using electronics-based power topologies to achieve DC-DC and DC-AC conversion [9–16].

Citation: Dionizio, A.A.; Sampaio, L.P.; da Silva, S.A.O.; Machado, S.d.J.M. Grid-Tied Single-Phase Integrated Zeta Inverter for Photovoltaic Applications. *Energies* 2023, *16*, 3622. https://doi.org/ 10.3390/en16093622

Academic Editor: Kyeong-Hwa Kim

Received: 3 April 2023 Revised: 19 April 2023 Accepted: 20 April 2023 Published: 22 April 2023

**Copyright:** © 2023 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https:// creativecommons.org/licenses/by/ 4.0/). Traditionally, a step-up DC-DC converter is associated with the voltage source inverter is performed to interface the PV system to the mains. This setup is characterized as a double-stage power conversion and is widely employed due to its simplicity. However, as disadvantages, this kind of conversion may present reduced efficiency, as well as a higher weight and size once a higher number of electrical and electronic components are needed [9,11,17–21].

Techniques to decrease issues in the DC-DC converter were proposed in [22,23]. In Refs. [22,23], a topology was suggested for PV applications that use multiple input sources and a single output; then, the circuit can operate with failure in some input sources. In addition, the converter structure can supply a higher or lower voltage in its output than the inputs. In Ref. [24], current and voltage oscillations in a PV generation connected to a single-phase utility grid were analyzed. The initial approach to reduce the oscillations is by using huge decoupling capacitors. However, an average current mode control is proposed for double-stage power conversion, reducing the second-order harmonic propagation.

A microinverter used to interface a PV module into the utility grid has been proposed in [25], which is deployed by the cascade association of a DC-DC flyback converter to the full-bridge inverter. Similarly, an association of an isolated DC-DC Zeta converter with multiple outputs, each connected to a voltage source inverter, is proposed in [26].

On the other hand, major research has been conducted to overcome the disadvantages mentioned above in the field of single-stage power conversion topologies [11–21]. The main advantage of the integrated inverter is its ability to perform the boost of the input PV voltage and simultaneously provide a regulated and controlled AC voltage or current in its output. Furthermore, in most cases, the integrated topologies employ fewer components and/or present a distinct topology configuration that leads to lower weight, size, and losses. However, combining the power stages and the presence of non-minimum phase characteristics can lead to significant difficulties in voltage and/or current control [27–29].

In Ref. [30], a submodule based on an isolated Ćuk converter has been proposed. The system analyzed includes a marine energy source, PV generation, battery storage, AC grid, and vessel supply. The main goal is to decrease dependence on fossil fuels in the shipping industry. The converter topology allows for bidirectional power flow and output voltage to be higher or lower than the input, as well as providing galvanic isolation.

In Ref. [31], an integrated topology based on a Zeta inverter is also proposed and designed to operate in continuous conduction mode (CCM) or discontinuous conduction mode (DCM). A feedback controller associated with a feedforward control loop and repetitive control was proposed to deal with different system dynamics once the converter operates in CCM and DCM. An integrated converter topology based on a DC-DC Cuk converter presenting galvanic isolation and the capability to perform high voltage gains is proposed in [32]. On the other hand, the power converters presented in [33,34] have reduced switching devices. In Ref. [33], a microinverter is proposed based on the isolated DC-DC Zeta inverter. In Ref. [34], an inverter is shown derived from the Cuk and Watkins-Johnson converter, which minimizes the problems related to parasite capacitances; it can operate either grid-tied or autonomously (off-grid). In addition, a buck-boost dual-legintegrated step-up inverter for the AC microgrid is proposed in [35]. In this case, during one switching period, the topology presents four operation stages in each stage operation, where two switches are turned on while the other two remain turned off. Nevertheless, the inverter design can be complex. Considering the traditional step-up DC-DC converters, in Ref. [27], a family of integrated inverters is presented. This family of integrated inverters works with the same number of switching devices compared to the traditional two-stage power converters.

To improve the traditional boost inverter, a dual-input dual-buck inverter with integrated boost converters is proposed in [36]. The topology uses two integrated boost converters and two inverters' legs. Once the topology works symmetrically, an integrated boost and an inverter leg are used in the positive half-cycle output. In contrast, the other part of the topology is accountable for operating in the negative half-cycle. In addition, integrated inverters also can be employed for three-phase grid-tied PV applications, which can step-up the input voltage and inject a three-phase sinusoidal current into the mains. The power from the PV array is transferred equally to three-phase mains. Therefore, this topology is commonly employed for higher power levels when compared with single-phase systems [21,27,37,38].

More recently, new topologies have been proposed, such as the Modified Zeta Inverter (MZI) in [39,40], which is based on the modified DC-DC Zeta converter. The MZI presents three operation stages during each switching period. However, its third stage differs from the conventional DC-DC converters operating at DCM. The currents through the input inductors from MZI present three steps. First, the current starts at zero and grows linearly to the peak value. In the second, it decreases linearly to zero. In the third, it is kept at zero.

On the other hand, the current through the output inductor acts as CCM. The current starts at a minimum value in the first operation stage and grows linearly to the maximum. After, the current decreases and reach the minimum value at the end of the switching period. Besides the distinct third operation stage, compared to conventional DC-DC converters, the voltages across some elements—such as the power switches, diodes, and coupling capacitors—can be higher and not easily determined.

This paper proposes an integrated inverter topology able to interface the PV array and the single-phase mains. The proposed topology combines the modified DC-DC Zeta converters, and is called a Single-Phase Integrated Zeta Inverter (SP-IZI). The SP-IZI can perform both the input voltage boosting and inject a sinusoidal current into the mains with low total harmonic distortion (THD). The entire analysis and development of the proposed SP-IZI are evaluated and validated from experimental results.

This paper is organized as follows: Section 2 describes the functionality, operation, and modeling of the proposed SP-IZI, while Section 3 compares the main differences between the proposed SP-IZI and the MZI. Section 4 presents and discusses the results obtained from experimental results. Finally, Section 5 presents the conclusions.

#### 2. Functionality, Operation, and Modeling of the Proposed SP-IZI

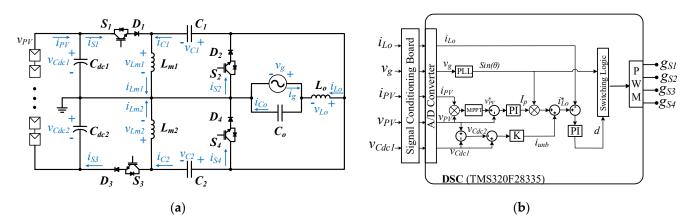

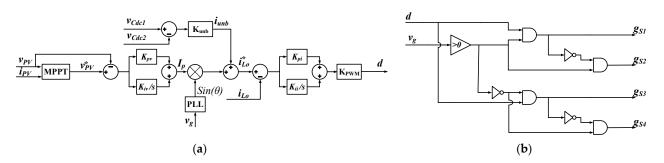

As mentioned earlier, the proposed inverter can connect the PV array to the singlephase mains through an integrated converter topology. The system can simultaneously perform the DC PV-voltage boost while injecting a sinusoidal current into the mains by extracting the maximum energy available at the PV array, as illustrated in Figure 1.

Figure 1. Scheme of the SP-IZI circuit: (a) electrical circuit; (b) control diagram block.

The SP-IZI is built by integrating modified DC-DC Zeta converters, each operating in a semi-cycle of the utility grid. The topology is designed to work in discontinuous conduction mode (DCM). In this operation mode, the static gain is linear. Thus, the proportional–integral controller gains can be easily tuned. The SP-IZI injects an active and synchronized current into the single-phase utility grid, attending to power quality standards and requirements [41,42]. The SP-IZI is controlled by employing a multiloop

control, in which the inner control loop regulates the injected current into the grid and is designed with a higher bandwidth than the outer loop. In contrast, the voltage control loop is set to be slower than the current control loop. It is responsible for maintaining the PV array voltage according to the reference provided by the MPPT algorithm. The SP-IZI control, the MPPT, and the PLL algorithms are addressed in Section 2.7.

# 2.1. Operation of the SP-IZI

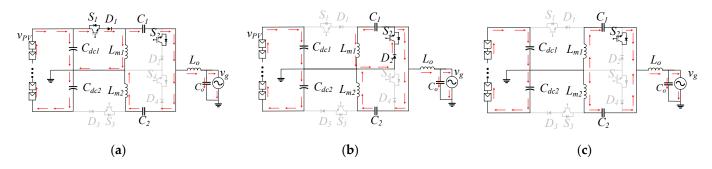

The SP-IZI has three stages of operation during a switching period. In a simplified way, the division of the half-cycles of the utility grid voltage allows the topology to present the same operation stages as the traditional DC-DC Zeta converter. Figure 2 illustrates the three operation stages of the SP-IZI circuit.

**Figure 2.** SP-IZI operation stages for the positive half-wave cycle of the mains: (a)  $D_a T_s$ ; (b)  $D_b T_s$ ; (c)  $D_c T_s$ .

Analyzing the positive half-wave cycle and disregarding the component losses, the switch  $S_1$  is turned on in the first stage of operation ( $D_a T_s$ ), and the switch  $S_2$  is turned on during the entire positive half-wave cycle, but in this stage of operation, it is not sending current through the diode  $D_2$ , which is placed in series with switch  $S_2$ .

The voltage across the inductor  $L_{m1}$  is equal to the voltage across the capacitor  $C_{dc1}$ . Ideally, it represents half of the *PV* voltage amplitude  $(v_{PV}/2)$ . At the same time, the inductor  $L_{m2}$  voltage is equal to half of the *PV* array voltage plus the sum of the voltage across the capacitors  $C_1$  and  $C_2$ , such that  $v_{Lm2} = v_{Cdc1} + v_{C1} - v_{C2}$ . When  $v_{C1} = v_{C2}$ , the voltage across the inductor  $L_{m2}$  is equal to  $v_{Cdc1}$ . Furthermore, the output inductor  $(L_o)$  presents a voltage equivalent to the sum of the voltages across the capacitor  $C_{dc1}$ , capacitor  $C_1$ , and capacitor  $C_o$ , such as  $v_{Lo} = v_{Cdc1} + v_{C1} - v_{Co}$ . The current flowing through the capacitor  $C_1$  is the sum of the currents that flow through the inductors  $L_{m2}$  and  $L_o$ . The current through the capacitor  $C_2$  is equal to the inductor  $L_{m2}$  current for the entire positive half-cycle of the grid. This operating stage can be seen in Figure 2a.

The second operation stage  $(D_b T_s)$  initiates when the switch  $S_1$  is turned off. Thus, the accumulated energy in the inductor  $L_{m1}$  is transferred to the capacitor  $C_1$  through the switch  $S_2$  and diode  $D_2$ .

The voltage across the inductor  $L_{m1}$  is the same as that of the capacitor  $C_1$  ( $v_{Lm1} = -v_{C1}$ ). The energy accumulated in the inductor  $L_{m2}$  is transferred to the capacitor  $C_2$ . Thus, the voltage across the inductor  $L_{m2}$  is the same as that of the capacitor  $C_2$  ( $v_{Lm2} = -v_{C2}$ ). Since the voltages across capacitors  $C_1$  and  $C_2$  are equivalent, the inductors  $L_{m1}$  and  $L_{m2}$  will be magnetized with the same ratio in  $D_a T_s$  and proportionally demagnetized in  $D_b T_s$ . For  $D_b T_s$ , the current through the capacitor  $C_1$  is the same as in inductor  $L_{m1}$ . The voltage across the inductor  $L_o$  is equal to that of the capacitor  $C_o$  ( $v_{Lo} = -v_{Co}$ ). This stage is visualized in Figure 2b.

The third stage ( $D_c T_s$ ) starts when the currents through the inductors  $L_{m1}$  and  $L_{m2}$  decrease to their minimum values, and the sum of their currents cannot polarize the diode  $D_2$  to operate in conduction mode. At this moment occurs the current change between the inductors. All the diodes are blocked in this stage, causing the current to flow only through the passive elements. Hence, the voltage across the inductors is nearly null, resulting in

voltage equality between the capacitors  $C_1$  and  $C_2$ . This operation stage is visualized in Figure 2c.

By driving the switches  $S_3$  and  $S_4$ , the operation analysis of the SP-IZI for the negative half-cycle of the grid voltage is performed similarly to the operation of the converter in the positive half-cycle.

#### 2.2. Static Gain of SP-IZI Structure

From the description of the SP-IZI operation, it is possible to derive the voltage equation of the inductor  $L_{m1}$  during one switching period. Knowing the average voltage in the inductor is null in steady-state, the following relationship can be obtained:

$$V_{Lm1_{av}} = V_{dc1}D_a - V_{C1}D_b + (V_{C2} - V_{C1} + V_{Lm2})D_c = 0$$

<sup>(1)</sup>

The average voltage across the inductor  $L_{m2}$  is null and calculated as follows:

$$V_{Lm2_{av}} = (V_{dc1} + V_{C1} - V_{C2})D_a - V_{C2}D_b + (V_{Lm1} - V_{C1} + V_{C2})D_c = 0$$

(2)

As analog from (1) and (2), the average voltage in the inductor  $L_0$  is derived as:

$$V_{Lo_{av}} = (V_{Cdc1} + V_{C1} - V_{Co})D_a - V_{Co}D_b + (V_{Lm2} + V_{C2} - V_{Co})D_c = 0$$

(3)

Equaling (1)–(3), the result is that the average voltages across the three capacitors are the same, i.e.,  $V_{C1} = V_{C2} = V_{C0}$ . Analyzing the third operation stage, the sum of the voltages across the inductors  $L_{m1}$  and  $L_{m2}$  is equal to the sum of the voltages across the coupling capacitors  $V_{Lm1} - V_{Lm2} = V_{C1} - V_{C2}$ , resulting in equality between  $L_{m1}$  and  $L_{m2}$  voltages. In this stage, the output inductor voltage also can be described as the sum of the voltages across the inductor  $L_{m1}$  and capacitors  $C_1$  and  $C_0$ , resulting in  $V_{L0} = V_{Lm1} + V_{C1} - V_{C0}$ . Since the average voltages in these capacitors are equal, the absolute voltages in  $L_{m1}$  and  $L_0$  must be nearly the same in the third operation stage. Therefore, the voltages across the three inductors in this stage are ideally null.

In the operation stage  $D_cT_s$ , considering the voltages across the inductors are null, the operation stages  $D_aT_s$  and  $D_bT_s$  can be related by:

$$V_{Cdc1}D_a = V_{C1}D_b \tag{4}$$

In the charging interval ( $D_a$ ), the current through the switch  $S_1$  is the sum of the three inductors' currents. As mentioned, the average voltages across the capacitors present the same value. Consequently, all inductors are charged with half of the input voltage during this stage.

The current through the switch  $S_1$  flows only in the first operation stage. Considering the charge of the inductor, the average value of this current is calculated as follows:

$$I_{S1_{av}} = \frac{I_p D_a T_s}{2} = \frac{V_{cdc1} D_a 2 T_s}{2} \left(\frac{1}{L_{eq}}\right)$$

(5)

where  $I_p$  is the current peak in the semiconductors and  $L_{eq}$  is the parallel association of the inductors  $L_{m1}$ ,  $L_{m2}$ , and  $L_o$ .

In Ref. [43], a converter modeling approach that uses an effective resistance ( $R_e$ ) to represent the processed power was proposed. The power dissipated on this resistance is equivalent to the output power. In the SP-IZI, this power can be calculated by the product to half input voltage, or ideally  $V_{cdc1}$ , and the average current through the switch  $S_1$ . Thus,  $R_e$  is defined as:

$$R_e = \frac{2L_{eq}}{D_a^2 T_s} \tag{6}$$

The proposed topology acts as an integrated inverter, injecting current into the utility grid. Therefore, the balance of power can be expressed as:

$$P_{in} = P_{out} = \frac{V_{cdc1}^2}{R_e} = \frac{V_g^2 P_{out}}{v_g^2}$$

(7)

The static gain is the relation between the output and input voltages, considering the voltage peak of the utility grid ( $V_p$ ); using (6) and (7), the static gain as expressed as:

$$G_e = V_p \sqrt{\frac{1}{2R_e P_{out}}} = V_p D_a \sqrt{\frac{1}{4L_{eq} P_{outf_s}}}$$

(8)

where  $f_s$  is the switching frequency.

The voltage across the capacitor  $C_1$  is nearly equal to the utility grid. Therefore, using (4) and (8), the second operation stage is determined as:

$$D_b = \frac{\sqrt{4P_{out}L_{eq}f_s}}{V_p} \tag{9}$$

## 2.3. Waveforms Concerning the Utility Grid

The SP-IZI operates as an integrated inverter that performs the interface between a PV array and the single-phase utility grid. The output current of SP-IZI is controlled to guarantee that a sinusoidal current is injected into the grid. Hence, each switching device of SP-IZI presents distinct modulation. Figure 3a shows the commutation signals used in SP-IZI for the entire grid voltage period.

**Figure 3.** Waveforms for one period of the utility grid: (**a**) gate signals for the switches; (**b**) currents through the inductors; (**c**) voltages across the capacitors.

The voltage across the capacitor  $C_1$  presents the same value as the utility grid but with some voltage ripple. Similarly, the capacitor  $C_2$  also presents the same grid voltage waveform grid. Figure 3c shows the voltage waveforms of the capacitors  $C_1$  and  $C_2$  and the utility grid voltage waveform.

Considering the equal voltage across the capacitors  $C_1$  and  $C_2$ , the resulting inductors'  $L_{m1}$  and  $L_{m2}$  voltages are the same. Thus, in each switching period, both inductors are magnetized and demagnetized with the same intensity, presenting the same current ripple.

On the other hand, during the whole positive half-wave cycle of the utility grid, the currents through the inductor  $L_{m2}$  and capacitor  $C_2$  are the same, and the average capacitor current is null. Consequently, the average  $L_{m2}$  current also is null at this half-wave cycle. By symmetry of the topology, the average  $L_{m1}$  current is null at the negative half-wave

cycle. Figure 3b presents the current waveforms of the inductors for a complete utility grid period.

#### 2.4. State-Space Model for the Inner Control Loop

Using the generalized switch-averaging modeling approach, the equations for the internal control loop in state-space is derived. The corresponding equations for the outer control loop are obtained, taking into account the power balance between the extracted PV array power and the injected power into the mains. Once the equations are obtained, the SP-IZI is analyzed for the operation in conjunction with the adopted MPPT and PLL algorithms.

During each switching period, the SP-IZI has three operating stages,  $D_a T_s$ ,  $D_b T_s$ , and  $D_c T_s$ . Due to the symmetric operation of the proposed inverter, the same behavior for the positive half-wave cycle is equivalent to what occurs in the negative half-cycle. In this way, it is possible to simplify the converter structure for analysis such as the one acting in a half-cycle. It is noticed that, during a switching period, the current is divided between the inductors  $L_{m1}$  and  $L_{m2}$ , as compared to a conventional Zeta converter, where this current flows through the inductor  $L_m$ , which is equivalent to a parallel association of  $L_{m1}$  and  $L_{m2}$ . Once both inductors present the same inductance, it is possible to write  $L_m = \frac{L_{m1}}{2}$ . The current is also divided between capacitors  $C_1$  and  $C_2$ , resulting in the coupling capacitor  $(C_a)$  for the conventional Zeta converter. The capacitor  $C_a$  is assumed to be the parallel between  $C_1$  and  $C_2$ , and if  $C_1 = C_2$ , the equivalent capacitor is equivalent to  $C_a = 2C_1$ .

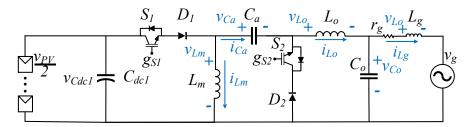

The average state-space model is widely employed for modeling dynamic systems by its simplicity. The state-space model can be obtained for the static converters operating in both CCM and DCM [43–47]. The SP-IZI presents the behavior as very close to the conventional Zeta converter operating in DCM. Thus, converter modeling is adopted as an equivalent model for the SP-IZI. The utility grid,  $v_g$ , can be represented as an input system in the matrix "*B*" in the state-space modeling. The voltage across the capacitor  $C_{dc1}$  also can be considered an input in this matrix. Furthermore, the line inductance ( $L_g$ ) and resistance ( $r_g$ ) between the inverter and the utility are also taken into account. These considerations for converter modeling ensure a better system response. Thus, Figure 4 presents the equivalent model used in the SP-IZI modeling.

Figure 4. Equivalent circuit to the analysis of the SP-IZI.

In Ref. [33], the state matrix of the converter operating in DCM was adequate through a modification in the matrix concerning the inductor current to represent the system behavior in discontinuous operation.

In addition, a generalized switch-averaging technique is adopted in [31,47], which is associated with the average state-space model to overcome the problems of representing the dynamical characteristics of the converter operating in DCM.

The employed modeling is based on the linearization of the state variables around the quiescent operating point, in which small oscillations are considered in the mean value. Hence, a generic variable  $\bar{x}$  is represented by a mean term (DC) plus a first-order AC term,  $\bar{x} = X + \hat{x}$ , with X representing the DC term and  $\hat{x}$  the AC term. There are considerations that the DC terms are much greater than the AC terms,  $|X|'' |\hat{x}|$  [43].

The average state-space model is initially adopted for modeling the SP-IZI according to Equation (6).

$$\dot{\overline{x}} = MA_m\overline{x} + B_m\overline{u} \tag{10}$$

where  $\overline{x}$  is the state vector,  $\overline{u}$  is the input vector,  $A_m$  is the average state matrix for a switching period,  $B_m$  is the average input matrix, and M is the corrected matrix to DCM. The corrected matrix M can be obtained for the state-space averaging model of the SP-IZI operating in DCM as follows:

$$M = \begin{bmatrix} \frac{1-D_b}{D_a} & 0 & 0 & 0 & 0\\ 0 & 1 & 0 & 0 & 0\\ 0 & 0 & 1 & 0 & 0\\ 0 & 0 & 0 & 1 & 0\\ 0 & 0 & 0 & 0 & 1 \end{bmatrix}$$

(11)

Performing the state-space averaging model and considering the adequacy matrix [see Equation (10)], the equivalent circuit representation for the SP-IZI presented in Figure 4 is determined as follows:

$$\begin{bmatrix} \dot{i}_{Lm} \\ \dot{i}_{Lo} \\ \dot{v}_{Ca} \\ \dot{\overline{v}}_{Co} \\ \dot{\overline{v}}_{Co} \\ \dot{\overline{t}}_{Lg} \end{bmatrix} \begin{bmatrix} 0 & 0 & a_1 & a_2 & 0 \\ 0 & 0 & a_3 & a_4 & 0 \\ \frac{D_b - D_b^2}{C_a D_a} & \frac{D_b - 1}{C_a} & 0 & 0 & 0 \\ 0 & \frac{1}{C_o} & 0 & 0 & \frac{-1}{C_o} \\ 0 & 0 & 0 & \frac{1}{L_g} & \frac{-r_g}{L_g} \end{bmatrix} \begin{bmatrix} \ddot{\overline{u}}_{Lm} \\ \bar{\overline{v}}_{Co} \\ \bar{\overline{u}}_{Lg} \end{bmatrix} + \begin{bmatrix} \frac{D_a}{L_m} & 0 \\ \frac{D_a}{L_o} & 0 \\ 0 & 0 \\ 0 & \frac{-1}{L_g} \end{bmatrix} \begin{bmatrix} \overline{\overline{v}}_{Cdc1} \\ \overline{\overline{v}}_g \end{bmatrix}$$

(12)

$$y = \begin{bmatrix} 0 & 1 & 0 & 0 & 0 \end{bmatrix} \begin{bmatrix} \bar{\overline{i}}_{Lm} \\ \bar{\overline{i}}_{Lo} \\ \overline{\overline{v}}_{Ca} \\ \overline{\overline{v}}_{Co} \\ \overline{\overline{i}}_{Lg} \end{bmatrix}$$

(13)

where  $a_1 = \frac{-(L_m + L_o)D_b - L_m D_c}{L_m (L_m + L_o)}$ ;  $a_2 = \frac{L_m D_c}{L_m + L_o}$ ;  $a_3 = \frac{(L_m + L_o)D_a - L_m D_c}{L_o (L_m + L_o)}$ ;  $a_4 = \frac{-(D_a + D_b)(L_m + L_o) - L_o D_c}{L_o (L_m + L_o)}$ ; and *y* represents the output vector.

If the equivalent circuit operates in CCM, the adequacy matrix has a unit value associated with eliminating the  $D_cT_s$  operation step, which results in an averaging model also valid for the operation in CCM.

By manipulating (12) and (13), it is possible to determine the transfer function that relates the current in the inductor  $L_0$  to the duty cycle as follows:

$$G_{id}(s) = \frac{\hat{i}_{Lo}(s)}{\hat{d}(s)} = C \left( s - MA_m + \frac{B_d k_s M C_m}{1 - k_s E_d} \right)^{-1} + \frac{B_d k_c}{1 - k_s E_d}$$

(14)

where  $k_s = [k_{id} k_{vs}]$  and the matrices  $B_d$  and  $E_d$  are defined in order to obtain the closed-loop system matrices as follows:

$$E_{d} = [C_{1} - C_{2}] \begin{bmatrix} \overline{i}_{Lm} \\ \overline{v}_{Lo} \\ \overline{v}_{Ca} \\ \overline{v}_{Co} \\ \overline{i}_{Lg} \end{bmatrix} + [E_{1} - E_{2}] \begin{bmatrix} \overline{v}_{Cdc1} \\ \overline{v}_{g} \end{bmatrix}$$

(15)

$$B_{d} = \left[A_{1} - \frac{D_{b}}{D_{b} + D_{c}}A_{2} - \frac{D_{c}}{D_{b} + D_{c}}A_{3}\right] \begin{bmatrix} \overline{i}_{Lm} \\ \overline{i}_{Lo} \\ \overline{v}_{Ca} \\ \overline{i}_{Lg} \end{bmatrix} + \left[B_{1} - \frac{D_{b}}{D_{b} + D_{c}}B_{2} - \frac{D_{c}}{D_{b} + D_{c}}B_{3}\right] \begin{bmatrix} \overline{v}_{Cdc1} \\ \overline{v}_{g} \end{bmatrix}$$

(16)

where  $A_1$ ,  $A_2$ , and  $A_3$  correspond to the respective state matrices for the passive elements during the operating stage  $D_a$ ,  $D_b$ , and  $D_c$ ;  $B_1$ ,  $B_2$ , and  $B_3$  are the input matrices

for the passive elements. The matrices  $C_1$  and  $C_2$  represent the output matrices of the generalized switch model, while  $E_1$  and  $E_2$  are the direct transition matrices of the generalized switch model. The matrix  $A_m$  is obtained by the operation stages averaging, i.e.,  $A_m = A_1D_a + A_2D_b + A_3D_c$ . The same procedure step is also valid for obtaining the matrix  $C_m$ , i.e.,  $C_m = C_1D_a + C_2D_b + C_3D_c$ .

# 2.5. Components Design

To guarantee the SP-IZI operates in DCM during all grid periods, the design of the components considers the voltage peak of the utility grid. However, the current injected into the grid presents a low ripple, and the output inductance is calculated as:

$$L_o = \frac{V_{cdc1} D_a T_s}{\Delta_{I_Lo} I_{Lo}} \tag{17}$$

where  $I_{Lo}$  is the average current during the voltage peak and  $\Delta_{I_{Lo}}$  is the maximum ripple allowed. The input inductors present a current ripple bigger than the average value and strongly influence the operation in the DCM. A maximum inductance can be obtained as follows:

$$L_{m1_{max}} = \frac{2V_p^2 L_0 (1 - 2D_a + D_a^2)}{4P_{out} L_o f_s - V_p^2 (1 - 2D_a + D_a^2)}$$

(18)

The output capacitance is calculated following a similar procedure commonly used for a buck converter and depends on the current and voltage ripple allowed, as obtained by:

$$C_o = \frac{\Delta_{I_{Lo}} I_{Lo}}{8 f_s \Delta_{V_{Co}} V_{Co}} \tag{19}$$

The coupling capacitances are designed in a range between two resonant frequencies,  $\omega r_{min}$  and  $\omega r_{max}$ . These capacitances are calculated as:

$$\frac{1}{2\omega r^2}\Big|_{\omega r=\omega r_{max}} < C_1 < \frac{1}{2\omega r^2}\Big|_{\omega r=\omega r_{min}}$$

(20)

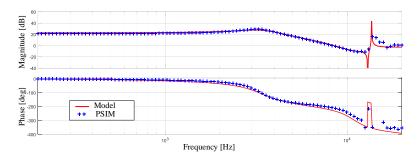

After the design of the components are combined, the modeling presented in (14) can obtain the frequency response, as shown in Figure 5. There is a high similarity between the model and the circuit simulated in the software PSIM.

Figure 5. Bode diagram of the model and the SP-IZI.

## 2.6. Modeling of the Outer Control Loop

The outer voltage control loop is modeled considering the energy conservation between the PV array and the utility grid. Ideally, the energy extracted from the PV array is the same as that injected into the grid. As the output of SP-IZI is sinusoidal, the active power can be determined through the voltage and current magnitude peaks,  $V_p$ and  $I_p$ , respectively. In this way, the power balance is defined as follows:

$$v_{PV}i_{Cdc1} = \frac{V_p I_p}{2} \tag{21}$$

Replacing  $i_{Cdc1}$  for the ratio between the voltage across the capacitor  $C_{dc1}$  and the Laplace transform of the capacitor, applying small-signal perturbations, and posteriorly disregarding second-order terms as well as the oscillation in the grid, it is possible to find the transfer function that relates the PV array voltage to the grid current by (22).

$$G_{vi}(s) = \frac{\hat{v}_{PV}(s)}{\hat{i}_{p}(s)} = \frac{V_{p}}{2V_{PV}C_{dc1}s}$$

(22)

## 2.7. MPPT and PLL Algorithm

As is well-known, the PV array presents non-linear characteristics curves (power versus voltage and current versus voltage). In addition, the PV array depends on the climate conditions, such as solar irradiance and temperature. Therefore, using algorithms to perform the maximum power point tracking (MPPT) is mandatory to extract the total available power at the PV array. Hence, this paper adopts the traditional Perturb and Observe (P and O) to reach the maximum available capacity of the PV array [48–52].

A non-autonomous adaptative filter AF- $\alpha\beta$ -pPLL technique is used in this paper for determining the synchronous unit vectors coordinates [sin( $\theta$ ) and cos( $\theta$ )], which is detailed in [53]. The AF is responsible for extracting the fundamental component of the grid voltage. The adopted AF- $\alpha\beta$ -pPLL is designed to deal with voltage disturbances, such as voltage sags/swells, voltage harmonics, phase-angle jumps, and frequency variations [53].

#### 2.8. SP-IZI Control

The control of the SP-IZI is performed by a multiloop control as follows: (i) an inner current control loop controls the injected current into the grid  $(i_{Lo})$ ; (ii) an outer voltage control loop controls the PV array ( $v_{pv}$ ); and (iii) a maximum power point tracking (MPPT) algorithm extracts the maximum power available at the PV array measuring the PV array voltage  $(v_{pv})$  and current  $(i_{pv})$ . Initially, the MPPT algorithm generates the reference voltage  $(v_{PV}^*)$  for the voltage control loop to extract the maximum PV array power. The voltage control loop's proportional-integral (PI) controller computes the peak current reference  $(I_p)$ needed to maintain the PV array voltage regulated at the reference provided by the MPPT. Thus, such peak current reference  $(I_p)$  is used to generate the current control loop's current reference  $(i_{lo}^*)$ , which is synchronized to the grid voltage  $(v_g)$  using a phase-locked-loop (PLL) technique, i.e., the peak current is multiplied by the sinusoidal ( $sin(\theta)$ ) vector. In addition, considering possible imbalance between the voltages over the input DC-bus capacitors ( $C_{dc1}$  and  $C_{dc2}$ ) can occur, a DC current ( $i_{unb}$ ) is associated with the sinusoidal current reference ( $I_p sin(\theta)$ ) to guarantee a balanced voltage between  $v_{Cdc1}$  and  $v_{Cdc2}$ . Finally, the current control loop's PI controller generates the duty cycle used in the switching logic to control the switching devices.

The proportional and integral gains of the PI controllers are tuned based on the procedure design proposed in [54]. The block diagram of the control diagram is presented in Figure 6a, while the block diagram of the signal logic adopted to control the switches of the SP-IZI is depicted in Figure 6b.

Figure 6. Block diagrams: (a) control diagram; (b) switching control logic.

#### 3. Comparison between the SP-IZI and the MZI

The proposed SP-IZI operates similarly to the integrated inverters called MZIs [39,40]. In addition, accordingly to the characteristics presented by the SP-IZI, the following advantages are obtained when compared to the MZI: (i) the static converter gain in DCM is identical to the traditional DC-DC Zeta converter; (ii) it presents reduced voltage stress over the switches and diodes; and (iii) it can operate in an off-grid mode for a different type of load.

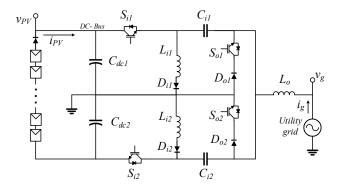

The MZI is based on the modified Zeta converter and controlled to inject a sinusoidal current into the utility grid. The topology operates in DCM. Therefore, a switching period is divided into three operation stages referred to as  $t_a$ ,  $t_b$ , and  $t_c$ . Figure 7 presents the MZI.

Figure 7. The electrical circuit of the MZI.

The diodes  $D_{i1}$  and  $D_{i2}$  in series with the inductors  $L_{i1}$  and  $L_{i2}$  prevent negative current during the third operation stage through the inductors mentioned. These diodes also prevent the current through all passive elements during the first and second stages, as in the SP-IZI.

According to the electrical circuit of the MZI and its operation, besides considering the peak amplitude of the grid, the gain of the inverter is determined as:

$$G_e = \frac{v_g}{V_{pv}} = \frac{D_a^2 + D_a D_b}{2D_b} \frac{D_a f_s L_i + D_a \sqrt{L_i^2 f_s^2 + \frac{2L_i V_p^2 f_s}{P_o}}}{4f_s L_i}$$

(23)

where  $D_a$  and  $D_b$  represent the respective first and second operation stages during the peak voltage of the grid,  $f_s$  is the switching frequency,  $L_i$  is the input inductance,  $V_p$  is the peak voltage of the grid, and  $P_o$  is the output power.

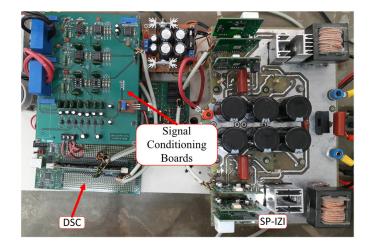

The voltage across the capacitors  $C_{i1}$  and  $C_{i2}$  are distinct between the MZI and the SP-IZI or the conventional Zeta converter. In the MZI, these voltages are related to the first operation stage. In the SP-IZI, the voltage of the intermediate capacitor is similar to that of the utility grid. The voltage across the intermediate capacitors to the MZI is determined as:

V

$$C_{Ci} = \frac{V_{pv}d_a}{2d_b} \tag{24}$$

According to (23), the first and second operation stages depend on the input inductance, switching frequency, grid voltage, and output power. Maintaining the output power and switching frequency as constant, in addition to considering the peak voltage of the utility grid, the voltages across the coupling capacitors (24) are related to the input inductance, in which lower values result in higher voltages. Conversely, high inductance values make the topology operate in CCM. Figure 8a presents the intermediate capacitors' average voltage dependence with the input inductance to the MZI and the voltage across the coupling capacitors to the SP-IZI.

**Figure 8.** Voltage dependence to the MZI: (**a**) coupling capacitor average voltage; (**b**) maximum voltage switches.

Consequently, the maximum voltages across the switches  $S_{i1}$  and  $S_{i2}$  in the proposed inverter, MZI, depend on the input inductance and the voltage across the coupling capacitors. Thus, the voltages across these switches are described as  $V_{Simax} = V_{Ci} + 2V_{PV}$ . Figure 8b shows the maximum voltage across the switches  $S_{i2}$  and  $S_{i2}$  to the MZI and the  $S_1$  and  $S_3$  to the SP-IZI.

In brief, the voltages across the semiconductors are higher in the MZI than in the SP-IZI, which causes limitations in the operation range and power losses during commutation. Table 1 compares the main parameters of the MZI and the SP-IZI.

Table 1. Comparison between the main parameters of MZI and SP-IZI.

| Parameters                                                 | MZI [39,40]                                                          | SP-IZI                                                             |

|------------------------------------------------------------|----------------------------------------------------------------------|--------------------------------------------------------------------|

| Maximum coupling<br>capacitors' voltage                    | $V_{Ci} = \frac{2V_g - V_{PV}D_a}{2D_a}$                             | $V_{Ci} = V_P$                                                     |

| Maximum switches voltage                                   | $V_{si} = 2V_{PV} + V_{Ci}$ $V_{so} = 0.5V_{PV} + V_{CI}$            | $V_{s1} = 0.5V_{pv} + V_p$ $V_{s2} = 0.5V_{PV} + V_p$              |

| Maximum diodes voltage                                     | $V_{Di} = -(1.5V_{PV} + V_{Ci})$<br>$V_{Do} = -(0.5V_{PV} + V_{Ci})$ | $V_{D1} = 0.5V_{PV} - V_P$ $V_{D3} = -(0.5V_{PV} + V_P)$           |

| RMS output inductor current<br>Input inductor peak current | $I_{Lo} = Po/\sqrt{2}V_P$ $I_{Lmp} = V_{PV}D_aT_S/2L_i$              | $I_{Lo} = Po/\sqrt{2}V_P$<br>$I_{Lmp} = V_{PV}D_aT_S/L_m - I_{Lo}$ |

Based on the equations and the operational description of the SP-IZI using the MPP power in standard test conditions (STC), the theoretical values from the RMS currents through the semiconductors and inductors are calculated. In addition, the maximum semiconductors' and intermediate capacitors' voltages are determined. The MZI is also evaluated for the same conditions. Table 2 shows the main parameters of the adopted PV module. The theoretical and practical implementation have assumed eight series-connected PV array panels achieving a maximum nominal power of 432 Wp. Therefore, Table 3 compares the theoretical RMS values of the MZI and SP-IZI.

| Parameters                          | Values |  |

|-------------------------------------|--------|--|

| Maximum power ( $P_{MAX}$ )         | 54 W   |  |

| Maximum power voltage ( $V_{MPP}$ ) | 17.4 V |  |

| Maximum power current ( $I_{MPP}$ ) | 3.11 A |  |

| Open-circuit voltage ( $V_{OC}$ )   | 21.7 V |  |

| Short-circuit current $(I_{SC})$    | 3.31 A |  |

Table 2. Main specifications of the Kyocera KC 50 module in STC.

Table 3. Comparison between the main values of MZI and SP-IZI operating in STC.

| D (                                     |                                                              |                                                          |

|-----------------------------------------|--------------------------------------------------------------|----------------------------------------------------------|

| Parameters                              | MZI [39,40]                                                  | SP-IZI                                                   |

| Maximum coupling<br>capacitors' voltage | 206.72 V                                                     | 180 V                                                    |

| Maximum switches voltage                | $V_{si} = 485.12 \text{ V}$<br>$V_{So} = 276.32 \text{ V}$   | $V_{s1} = 249.2 \text{ V}$<br>$Vs_2 = 249.2 \text{ V}$   |

| Maximum diodes voltage                  | $V_{Di} = -415.52 \text{ V}$<br>$V_{Do} = -276.72 \text{ V}$ | $V_{D1} = -249.2$<br>$V_{D3} = -110.4$ V                 |

| RMS output inductor current             | 3.439 A                                                      | 3.394 A                                                  |

| Average input inductor<br>current       | 3.11 A                                                       | 2.87 A                                                   |

| RMS input inductor current              | 7.14 A                                                       | 6.20 A                                                   |

| Average switches current                | $I_{si} = 3.11 \text{ A}$<br>Iso = 1.536 A                   | $I_{S1} = 3.09 \text{ A}$<br>$I_{S2} = 1.528 \text{ A}$  |

| RMS switches current                    | $I_{si} = 7.718 \text{ A}$<br>$I_{so} = 4.705 \text{ A}$     | $I_{S1} = 7.737 \text{ A}$<br>$I_{S2} = 5.237 \text{ A}$ |

| Average diodes current                  | $I_{Di} = 3.11 \text{ A}$<br>$I_{Do} = 1.536 \text{ A}$      | $I_{D1} = 3.09 \text{ A}$<br>$I_{D2} = 1.528 \text{ A}$  |

| RMS diodes current                      | $I_{Di} = 7.14 \text{ A}$<br>$I_{Do} = 4.705 \text{ A}$      | $I_{D1} = 7.737 \text{ A}$<br>$I_{D2} = 5.237 \text{ A}$ |

The SP-IZI presents current through all passive elements. Therefore, the semiconductors' currents are the sum of the inductors' currents, resulting in not much higher RMS values when compared to the MZI. Thus, these currents can cause conduction losses in the semiconductors. On the other hand, the currents through the inductors present lower values in SP-IZI.

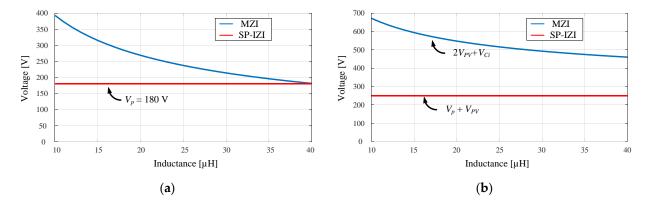

#### 4. Experimental Results

An experimental prototype was developed to evaluate the SP-IZI, as depicted in Figure 9. The experimental setup employs the discrete IGBT IRGP4650D (Infineon, Neubiberg, Germany) and 30ETH06 diodes (International Rectifier, El Segundo, CA, USA). The characteristics curves of the PV array were performed using a bidirectional PV array emulator IT6012C-800-50 (Itech, New Taipei City, Taiwan) in conjunction with the software SAS100L (Itech). The entire system was controlled using a digital signal controller (DSC), a TMS320F28335 (Texas Instruments, Dallas, TX, USA), in which the current and voltage quantities were measured by means of signal-conditioning boards that employ Hall-effect transducers (LEM, Geneva, Switzerland). The system's algorithms were embedded in the DSC. The experimental results were obtained by digital oscilloscope, the TPS2024 (Tektronix, Beaverton, OR, USA), while the power factor (PF) and total harmonic distortion were measured using the Power Quality Analyzer 43B (Fluke, Everett, WA, USA). Table 4 presents the main parameters employed in the experimental tests of the SP-IZI.

Figure 9. Experimental prototype of SP-IZI.

Table 4. Main SP-IZI parameters.

| Parameters                                       | SP-IZI                                               |

|--------------------------------------------------|------------------------------------------------------|

| The nominal utility RMS voltage                  | $V_o = 127 \text{ V}$                                |

| Nominal utility frequency                        | f = 60  Hz                                           |

| Switching frequency                              | $f_s = 50 \text{ kHz}$                               |

| Sampling frequency A/D converter                 | $f_a = 60 \text{ kHz}$                               |

| Input DC-Bus capacitance                         | $C_{dc1} = C_{dc2} = 4500 \ \mu F$                   |

| Nominal input DC-bus voltage                     | $v_{PV} = 146.26 \text{ V}$                          |

| Input inductive filter                           | $L_{m1} = L_{m2} = 60 \ \mu \text{H}$                |

| Output inductive filter                          | $L_{o} = 1.0 \text{ mH}$                             |

| Coupling capacitances                            | $C_1 = C_2 = 1.0 \ \mu F$                            |

| Nominal power                                    | P = 432  W                                           |

| Phase margin of the inner current control        | $P_{mi} = 76.8^{\circ}$                              |

| Crossover frequency of the inner current control | $f_{ci} = 1220 \text{ Hz}$                           |

| Phase margin of the outer voltage control        | $P_{mo} = 80^{\circ}$                                |

| Crossover frequency of the outer voltage control | $f_{co} = 10 \text{ Hz}$                             |

| PWM gain                                         | $K_{PWM} = 1/2999$                                   |

| Voltage PI controller gains                      | $K_{pv} = 0.2157;$<br>$K_{iv} = 1.1257$              |

| Current PI controller gains                      | $K_{pi} = 20.826;$<br>$K_{ii} = 1.5412 	imes 10^{6}$ |

| Unbalance gain                                   | $K_{unb} = 0.15$                                     |

| PLL PI controller gains                          | $K_{PPLL} = 423.4;$<br>$K_{iPLL} = 32234$            |

| Adaptive filter step size parameter (AF-pPLL)    | $\mu_{AF} = 0.007$                                   |

| Sampling time (AF-pPLL)                          | 60 kHz                                               |

| Adaptive filter gain (AF-pPLL)                   | $K_{AF} = 420$                                       |

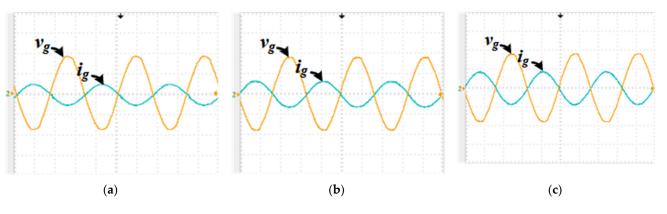

Firstly, the SP-IZI was evaluated for three different levels of solar irradiance employing the PV emulator, in which the PV array voltage was equal to 140 V. Hence, the peak amplitude of the inverter currents injected into the grid is described as follows: (i) Scenario 1: 2 A; (ii) Scenario 2: 3 A; and (iii) Scenario 3: 4.8 A.

Figure 10 shows the grid voltage and the current injected into the grid for the three evaluated scenarios. As noted, the grid-injected currents present sinusoidal waveforms in opposite-phase to the grid voltage for all the considered scenarios.

**Figure 10.** Experimental grid-injected current and grid voltage considering the three different scenarios (100 V/div, 5 A/div, 5 ms/div): (a) Scenario 1; (b) Scenario 2; (c) Scenario 3.

Figure 11 shows the total harmonic distortion (THD) for the three inverter currents shown in Figure 10. It can be observed that the SP-IZI currents are sinusoidal, meeting the requirements of the standards [41,42], i.e., the injected currents presented a maximum THD of around 3.3%, validating the feasibility and theoretical development of the proposed inverter.

**Figure 11.** THD of the current injected into the grid for the three evaluated scenarios: (**a**) Scenario 1; (**b**) Scenario 2; (**c**) Scenario 3.

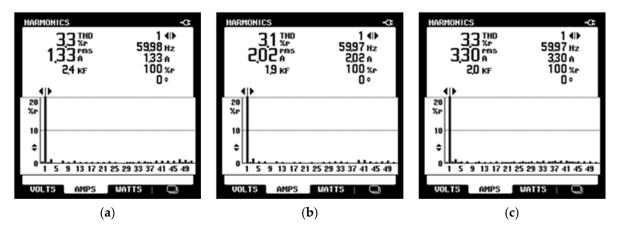

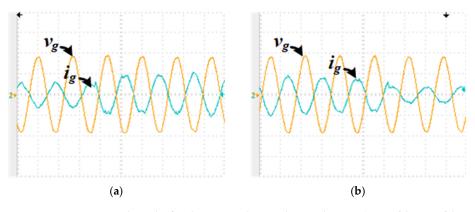

Figure 12 presents the dynamic performance of the SP-IZI considering changes in solar irradiance. The changes are performed from half of the power rate to nominal PV array power rate and vice versa (50% to 100% and 100% to 50%). As can be observed, the proposed SP-IZI acts very fast when abrupt solar irradiance changes occur.

The currents through the inductors  $L_{m1}$  and  $L_{m2}$  are presented in Figure 13a, while the voltages across the switches  $S_1$ ,  $S_2$ ,  $S_3$ , and  $S_4$  are presented in Figure 13b. It can be noted that the experimental results presented in Figure 12 can be compared and evaluated to the theoretical development shown in Figure 3. These results demonstrated that the proposed SP-IZI operates following the developed mathematical equations and that the inverter is feasible and reliable.

**Figure 12.** Experimental results for dynamic solar irradiance changes (100 V/div, 5 A/div, 10 ms/div): (a) transition from half to nominal PV array power rate; (b) transition from nominal to half of the PV array power rate.

**Figure 13.** Experimental results (200 V/div, 10 A/div, 2.5 ms/div): (**a**) grid voltage and the current through the inductors  $L_{m1}$  and  $L_{m2}$ ; (**b**) Voltages across the switches  $S_1$ ,  $S_2$ ,  $S_3$ , and  $S_4$ .

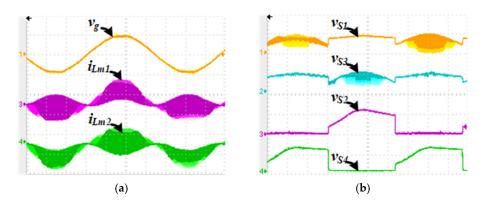

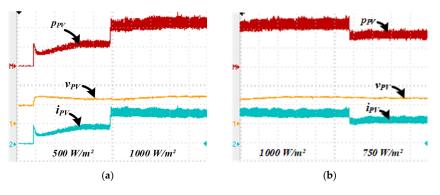

In STC, the performance of the P and O MPPT algorithm was evaluated considering the solar irradiance change from  $500 \text{ W/m}^2$  to  $1000 \text{ W/m}^2$  and from  $1000 \text{ W/m}^2$  to  $750 \text{ W/m}^2$ , as shown in Figure 14. As observed, the P and O MPPT technique used in the SP-IZI can reach the maximum power point and acts very fast during abrupt solar irradiance changes. In addition, Figure 14 shows that the PV array voltage is below 160 V in all cases, while the grid peak voltage is near 200 V [see Figure 13a]. This demonstrates that the proposed SP-IZI can boost the input voltage and, simultaneously, injects in the grid a sinusoidal and regulated current into the utility with low harmonic distortion, as discussed above. Hence, all such results demonstrate that the proposed converter is useful and suitable for PV applications.

**Figure 14.** Experimental results evaluating the P-and-O-based MPPT algorithm performance considering transitions in solar irradiance (100 V/div, 2 A/div, 200 W/div, 5 s/div): (**a**) 500 W/m<sup>2</sup> to 1000 W/m<sup>2</sup>; (**b**) 1000 W/m<sup>2</sup> to 750 W/m<sup>2</sup>.

# 5. Conclusions

This paper presented the implementation of an integrated inverter topology based on Zeta converters named SP-IZI. The proposed inverter increased the input voltage (PV array voltage) and injected a sinusoidal current into the grid with low total harmonic distortion.

The SP-IZI presented advantages compared to the MZI when both inverters were operating in DCM. The voltages across the semiconductors and coupling capacitors are lower and do not depend on the input inductance or the operation stages. The operation of the SP-IZI is similar to the conventional DC-DC Zeta converter, in which the third stage is well-defined. The SP-IZI presents the following advantages compared to the MZI: (i) the voltage in coupling capacitors is 13% lower; (ii) voltage stresses in switches and diodes are 40% lower; and (iii) static gain is similar to the traditional Zeta converter.

From the employed modeling technique, the SP-IZI transfer functions for the inner and outer control loops were derived. In addition, by the analysis of frequency response, it was possible to obtain the proportional and integral gains of the PI controllers.

Through experimental results, the effectiveness and feasibility of an SP-IZI were evaluated and demonstrated. In addition, simulation and experimental results corroborated the theoretical development.

As could be observed from the achieved results, the proposed SP-IZI can replace—with advantages—the traditional PV system constructed by the cascade association of a step-up DC-DC converter and a voltage source inverter.

# 6. Patents

This work resulted in a patent with the process number BR 10 2022 004213 6.

**Author Contributions:** A.A.D., L.P.S., S.A.O.d.S., and S.d.J.M.M. contributed equally to this paper. All authors have read and agreed to the published version of the manuscript.

**Funding:** The authors gratefully acknowledge the financial support from CNPq Brazil (Process 308620/2021-6 and 304707/2021-0) and the support from Coordination for the improvement of higher education personnel CAPES Brazil—financing code 001.

Data Availability Statement: Not applicable.

Conflicts of Interest: The authors declare no conflict of interest.

## References

- 1. Jurasz, J.; Canales, F.A.; Kies, A.; Guezgouz, M.; Beluco, A. A review on the complementarity of renewable energy sources: Concept, metrics, application and future research directions. *Sol. Energy* **2020**, *195*, 703–724. [CrossRef]

- Muttaqi, K.M.; Islam, R.; Sutanto, D. Future Power Distribution Grids: Integration of Renewable Energy, Energy Storage, Electric Vehicles, Superconductor, and Magnetic Bus. *IEEE Trans. Appl. Supercond.* 2019, 29, 1–5. [CrossRef]

- Alharbi, F.R.; Csala, D. GCC Countries' Renewable Energy Penetration and the Progress of Their Energy Sector Projects. *IEEE Access* 2020, *8*, 211986–212002. [CrossRef]

- Alshammari, M.; Duffy, M. Review of Single-Phase Bidirectional Inverter Topologies for Renewable Energy Systems with DC Distribution. *Energies* 2022, 15, 683. [CrossRef]

- Qazi, A.; Hussain, F.; Rahim, N.A.; Hardaker, G.; Alghazzawi, D.; Shaban, K.; Haruna, K. Towards Sustainable Energy: A Systematic Review of Renewable Energy Sources, Technologies, and Public Opinions. *IEEE Access* 2019, 7, 63837–63851. [CrossRef]

- Mateo, C.; Cossent, R.; Gómez, T.; Prettico, G.; Frías, P.; Fulli, G.; Meletiou, A.; Postigo, F. Impact of solar PV self-consumption policies on distribution networks and regulatory implications. *Sol. Energy* 2018, 176, 62–72. [CrossRef]

- Yang, D.; Li, W.; Yagli, G.M.; Srinivasan, D. Operational solar forecasting for grid integration: Standards, challenges, and outlook. Sol. Energy 2021, 224, 930–937. [CrossRef]

- Vodapally, S.N.; Ali, M.H. A Comprehensive Review of Solar Photovoltaic (PV) Technologies, Architecture, and Its Applications to Improved Efficiency. *Energies* 2022, 16, 319. [CrossRef]

- 9. Dogga, R.; Pathak, M.K. Recent trends in solar PV inverter topologies. Sol. Energy 2019, 183, 57–73. [CrossRef]

- Da Silva, S.A.O.; Sampaio, L.P.; de Oliveira, F.M.; Durand, F.R. Feed-forward DC-bus control loop applied to a single-phase grid-connected PV system operating with PSO-based MPPT technique and active power-line conditioning. *IET Renew. Power Gener.* 2017, 11, 183–193. [CrossRef]

- 11. Wollz, D.H.; da Silva, S.A.O.; Sampaio, L.P. Real-time monitoring of an electronic wind turbine emulator based on the dynamic PMSG model using a graphical interface. *Renew. Energy* **2020**, *155*, 296–308. [CrossRef]

- 12. Rocha, A.V.; Maia, T.A.C.; Filho, B.J.C. Improving the Battery Energy Storage System Performance in Peak Load Shaving Applications. *Energies* 2023, *16*, 382. [CrossRef]

- Ali Khan, M.Y.; Liu, H.; Yang, Z.; Yuan, X. A Comprehensive Review on Grid Connected Photovoltaic Inverters, Their Modulation Techniques, and Control Strategies. *Energies* 2020, 13, 4185. [CrossRef]

- 14. Khan, N.H.; Forouzesh, M.; Siwakoti, Y.P.; Li, L.; Kerekes, T.; Blaabjerg, F. Transformerless Inverter Topologies for Single-Phase Photovoltaic Systems: A Comparative Review. *IEEE J. Emerg. Sel. Top. Power Electron.* **2020**, *8*, 805–835. [CrossRef]

- Han, B.; Bai, C.; Lai, J.-S.; Kim, M. Control Strategy of Single-Phase Hybrid-Mode Cuk Inverter for LVRT Capability. *IEEE J. Emerg. Sel. Top. Power Electron.* 2020, *8*, 3917–3932. [CrossRef]

- Baier, C.R.; Villarroel, F.A.; Torres, M.A.; Perez, M.A.; Hernandez, J.C.; Espinosa, E.E. A Predictive Control Scheme for a Single-Phase Grid-Supporting Quasi-Z-Source Inverter and Its Integration With a Frequency Support Strategy. *IEEE Access* 2023, 11, 5337–5351. [CrossRef]

- Zapata, J.W.; Kouro, S.; Carrasco, G.; Renaudineau, H.; Meynard, T.A. Analysis of Partial Power DC–DC Converters for Two-Stage Photovoltaic Systems. *IEEE J. Emerg. Sel. Top. Power Electron.* 2019, *7*, 591–603. [CrossRef]

- Abdel-Rahim, O. Aswan University A New High Gain DC-DC Converter With Model-Predictive-Control Based MPPT Technique for Photovoltaic Systems. *CPSS Trans. Power Electron. Appl.* 2020, 5, 191–200. [CrossRef]

- 19. Darwish, A.; Alotaibi, S.; Elgenedy, M.A. Current-Source Single-Phase Module Integrated Inverters for PV Grid-Connected Applications. *IEEE Access* 2020, *8*, 53082–53096. [CrossRef]

- Khan, N.H.; Forouzesh, M.; Siwakoti, Y.P.; Li, L.; Blaabjerg, F. Switched Capacitor Integrated (2n + 1)-Level Step-Up Single-Phase Inverter. *IEEE Trans. Power Electron.* 2020, 35, 8248–8260. [CrossRef]

- Duong, T.-D.; Nguyen, M.-K.; Tran, T.-T.; Vo, D.-V.; Lim, Y.-C.; Choi, J.-H. Topology Review of Three-Phase Two-Level Transformerless Photovoltaic Inverters for Common-Mode Voltage Reduction. *Energies* 2022, 15, 3106. [CrossRef]

- Elrefaey, M.S.; Ibrahim, M.E.; Eldin, E.T.; Hegazy, H.Y.; El-Kholy, E.E.; Abdalfatah, S. Multiple-Source Single-Output Buck-Boost DC–DC Converter with Increased Reliability for Photovoltaic (PV) Applications. *Energies* 2023, 16, 216. [CrossRef]

- Saeed, M.; Rogina, M.R.; Rodríguez, A.; Arias, M.; Briz, F. SiC-Based High Efficiency High Isolation Dual Active Bridge Converter for a Power Electronic Transformer. *Energies* 2020, 13, 1198. [CrossRef]

- 24. Mohamadian, S.; Buccella, C.; Cecati, C. Average Current Mode Control of a DC–DC Boost Converter to Reduce the Decoupling Capacitance at the PV Array Output. *Energies* **2023**, *16*, 364. [CrossRef]

- 25. Feng, X.; Wang, F.; Wu, C.; Luo, J.; Zhang, L. Modeling and Comparisons of Aggregated Flyback Microinverters in Aspect of Harmonic Resonances with the Grid. *IEEE Trans. Ind. Electron.* **2019**, *66*, 276–285. [CrossRef]

- Nirmal Mukundan, C.M.; Jayaprakash, P. Realization of Cascaded H-Bridge Multilevel Inverter Based Grid Integrated Solar Energy System with Band Stop Generalized Integral Control. *IEEE Trans. Ind. Appl.* 2021, 57, 764–773.

- 27. De Brito, M.; Sampaio, L.; Melo, G.; Canesin, C.A. Three-phase tri-state buck–boost integrated inverter for solar applications. *IET Renew. Power Gener.* 2015, *9*, 557–565. [CrossRef]

- de Brito, M.A.G.; Sampaio, L.P.; Junior, L.G.; Godoy, R.B.; Canesin, C.A. New integrated Zeta and Cuk inverters intended for standalone and grid-connected applications. In Proceedings of the XI Brazilian Power Electronics Conference, Natal, Brazil, 11–15 September 2011; pp. 657–663.

- 29. Wu, W.; Ji, J.; Blaabjerg, F. Aalborg Inverter—A New Type of "Buck in Buck, Boost in Boost" Grid-Tied Inverter. *IEEE Trans. Power Electron.* 2015, 30, 4784–4793. [CrossRef]

- Darwish, A. A Bidirectional Modular Cuk-Based Power Converter for Shore Power Renewable Energy Systems. *Energies* 2023, 16, 274. [CrossRef]

- Han, B.; Jo, S.-W.; Kim, N.-G.; Lai, J.-S.; Kim, M. Bridgeless Hybrid-Mode Zeta-Based Inverter: Dynamic Modeling and Control. IEEE Trans. Power Electron. 2021, 36, 7233–7249. [CrossRef]

- 32. Han, B.; Jo, S.-W.; Kim, M.; Nguyen, D.A.; Lai, J.-S.J. Improved Odd-Harmonic Repetitive Control Scheme for Cuk-derived Inverter. *IEEE Trans. Power Electron.* 2022, *37*, 1496–1508. [CrossRef]

- Surapaneni, R.K.; Rathore, A.K. A Single-Stage CCM Zeta Microinverter for Solar Photovoltaic AC Module. *IEEE J. Emerg. Sel.* Top. Power Electron. 2015, 3, 892–900. [CrossRef]

- Gautam, V.; Kumar, A.; Sensarma, P. A novel single stage, transformerless PV inverter. In Proceedings of the 2014 IEEE International Conference on Industrial Technology (ICIT), Busan, Korea, 26 February–1 March 2014; pp. 907–912.

- Shawky, A.; Ahmed, M.; Orabi, M.; El Aroudi, A. Classification of Three-Phase Grid-Tied Microinverters in Photovoltaic Applications. *Energies* 2020, 13, 2929. [CrossRef]

- 36. Ali, A.I.M.; Takeshita, T.; Sayed, M.A. Three-Phase PWM Inverter for Isolated Grid-Connected Renewable Energy Applications. *Energies* **2021**, *14*, 3701. [CrossRef]

- Qin, L.; Hu, M.; Lu, D.D.-C.; Feng, Z.; Wang, Y.; Kan, J. Buck–Boost Dual-Leg-Integrated Step-Up Inverter with Low THD and Single Variable Control for Single-Phase High-Frequency AC Microgrids. *IEEE Trans. Power Electron.* 2018, 33, 6278–6291. [CrossRef]

- Yang, F.; Ge, H.; Yang, J.; Wu, H. Dual-Input Grid-Connected Photovoltaic Inverter with Two Integrated DC–DC Converters and Reduced Conversion Stages. *IEEE Trans. Energy Convers.* 2019, 34, 292–301. [CrossRef]

- Sampaio, L.P.; da Silva, S.A.O.; Costa, P.J.S. Integrated Zeta Inverter Applied in a Single-Phase Grid-Connected Photovoltaic System. In Proceedings of the 2019 IEEE 15th Brazilian Power Electronics Conference and 5th IEEE Southern Power Electronics Conference (COBEP/SPEC), Santos, Brazil, 1–4 December 2019; pp. 1–6.

- 40. Sampaio, L.P.; Costa, P.J.S.; da Silva, S.A.O. Modified zeta inverter intended for single-phase grid-tied photovoltaic system. *Sustain. Energy Technol. Assess.* 2022, 52, 102076. [CrossRef]

- IEEE Std 1547-2018; IEEE Standard for Interconnection and Interoperability of Distributed Energy Resources with Associated Electric Power Systems Interfaces Sponsored by the IEEE Standard for Interconnection and Interoperability of Distributed Energy Resources with Associate. IEEE: New York, NY, USA, 2018.

- 42. IEC 61727; Photovoltaic (PV) Systems—Characteristics of the Utility Interface. IEC: Geneva, Switzerland, 2004.

- 43. Mahdavi, J.; Emaadi, A.; Bellar, M.; Ehsani, M. Analysis of power electronic converters using the generalized state-space averaging approach. *IEEE Trans. Circuits Syst. I Regul. Pap.* **1997**, *44*, 767–770. [CrossRef]

- 44. Erickson, R.W. Fundamentals of Power Electronics, 1st ed.; Chapman & Hall: London, UK, 1997.

- 45. Ogata, K.; Brewer, J.W. Modern Control Engineering, 5th ed.; Prentice-Hall, Inc.: Hoboken, NJ, USA, 2009.

- 46. Sun, J.; Mitchell, D.; Greuel, M.; Krein, P.; Bass, R. Averaged modeling of PWM converters operating in discontinuous conduction mode. *IEEE Trans. Power Electron.* 2001, *16*, 482–492.

- Viero, R.C.; dos Reis, F.S. Dynamic modeling of a ZETA converter in DCM applied to low power renewable sources. In Proceedings

of the 2011 IEEE Energy Conversion Congress and Exposition, Phoenix, AZ, USA, 17–22 September 2011; pp. 685–691.

- Kollimalla, S.K.; Mishra, M.K. Variable Perturbation Size Adaptive P&O MPPT Algorithm for Sudden Changes in Irradiance. IEEE Trans. Sustain. Energy 2014, 5, 718–728.

- 49. Ahmed, J.; Salam, Z. A Modified P&O Maximum Power Point Tracking Method with Reduced Steady-State Oscillation and Improved Tracking Efficiency. *IEEE Trans. Sustain. Energy* **2016**, *7*, 1506–1515.

- Ahmed, J.; Salam, Z. An Enhanced Adaptive P&O MPPT for Fast and Efficient Tracking Under Varying Environmental Conditions. IEEE Trans. Sustain. Energy 2018, 9, 1487–1496.

- 51. Bhattacharyya, S.; Kumar, P.D.S.; Samanta, S.; Mishra, S. Steady Output and Fast Tracking MPPT (SOFT-MPPT) for P&O and InC Algorithms. *IEEE Trans. Sustain. Energy* **2021**, *12*, 293–302.

- Khodair, D.; Motahhir, S.; Mostafa, H.H.; Shaker, A.; El Munim, H.A.; Abouelatta, M.; Saeed, A. Modeling and Simulation of Modified MPPT Techniques under Varying Operating Climatic Conditions. *Energies* 2023, 16, 549. [CrossRef]

- 53. Bacon, V.D.; da Silva, S.A.O.; Campanhol, L.B.G.; Angélico, B.A. Stability analysis and performance evaluation of a single-phase phase-locked loop algorithm using a non-autonomous adaptive filter. *IET Power Electron.* **2014**, *7*, 2081–2092. [CrossRef]

- 54. Angélico, B.A.; Campanhol, L.B.; da Silva, S.A.O. Proportional–integral/proportional–integral-derivative tuning procedure of a single-phase shunt active power filter using Bode diagram. *IET Power Electron.* **2014**, *7*, 2647–2659. [CrossRef]

**Disclaimer/Publisher's Note:** The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content.