# **Comprehensive Study on Reduced DC Source Count: Multilevel Inverters and Its Design Topologies**

Kommoju Naga Durga Veera Sai Eswar <sup>1</sup>, Mohan Arun Noyal Doss <sup>1,\*</sup>, Pradeep Vishnuram <sup>1</sup>, Ali Selim <sup>2</sup>, Mohit Bajaj <sup>3,4</sup>, Hossam Kotb <sup>5</sup> and Salah Kamel <sup>2,6,\*</sup>

- <sup>1</sup> Department of Electrical and Electronics Engineering, SRM Institute of Science and Technology, Kattankulathur, Chennai 603203, India

- <sup>2</sup> Electrical Engineering Department, Faculty of Engineering, Aswan University, Aswan 81542, Egypt

- <sup>3</sup> Department of Electrical Engineering, Graphic Era (Deemed to be University), Dehradun 248002, India

- <sup>4</sup> Graphic Era Hill University, Dehradun 248002, India

- <sup>5</sup> Department of Electrical Power and Machines, Faculty of Engineering, Alexandria University, Alexandria 21544, Egypt

- <sup>6</sup> Applied Science Research Center, Applied Science Private University, Amman 11931, Jordan

- \* Correspondence: arunnoyal@gmail.com (M.A.N.D.); skamel@aswu.edu.eg (S.K.)

**Abstract:** Due to cutting-edge innovations in industry and academia, research is more centered around multilevel inverters (MLIs), which play a significant role in different high/medium voltage and high-power applications when contrasted with traditional inverters. Relative analysis of the reduced DC source count and switch inverter topologies highlight its significant benefits, which include control complexity, switch count, source count, reliability, efficiency, cost, voltage stress, total harmonic distortion (THD), and power quality. When switched-capacitor technology is deployed, it is seen that with the assistance of 14 switches, a 53 level result is accomplished, and the THD is just around 1.41%, which is kept up with as per the IEEE 519-2014 norms. Whenever cascaded MLI topology is employed, the inversion efficiency is more prominent, and is about 99.06%. Hence, this review focuses on a few of the late-evolved MLIs utilized, and the benefits and drawbacks for different topologies are examined. To assist with current modern research in this field and the decision of the proper inverter for various applications, a novel topology of an MLI can be planned later on. Different setups of MLIs have been exhaustively covered and reviewed.

**Keywords:** multilevel inverter (MLI); reduced component count; asymmetrical; pulse width modulation (PWM); photovoltaic (PV) systems; electric vehicles (EV)

## 1. Introduction

Because of the rise in population, and enterprises and to fulfill everyday needs, power generation has received enormous interest. To deliver electrical energy, many power plants have been entrenched for years. A total of 75% of the energy in India is created by of thermal power stations, which use fossil fuels and coal. Thus, it brings about an expansion in the carbon levels. This has a tremendous effect on atmospheric climatic conditions, which are changing daily. Utilizing environmentally friendly power from renewable energy conventional sources (RECS), predominantly solar and wind, creates a lot of interest in power generation in recent research. This will likewise build a more extensive scope of utilization in power electronics and power system regions, rather than a huge reliance on changing climatic circumstances [1]. The objective of this paper is to change one type of energy over to another form, either by a rectification or an inversion process. Essentially, a traditional voltage-fed inverter is utilized, which can create two-levels of voltage. The terms MLI was first used with the advent of the three-level converter in the late 20th century. Since multilevel inverters have more levels than standard versions, their power rating has improved, while their device count has decreased [2]. Buck-boost and Q-ZSIs-type

Citation: Eswar, K.N.D.V.S.; Doss, M.A.N.; Vishnuram, P.; Selim, A.; Bajaj, M.; Kotb, H.; Kamel, S. Comprehensive Study on Reduced DC Source Count: Multilevel Inverters and Its Design Topologies. *Energies* **2023**, *16*, 18. https:// doi.org/10.3390/en16010018

Academic Editors: Jagabar Sathik Mohammed and Yam P. Siwakoti

Received: 14 October 2022 Revised: 26 November 2022 Accepted: 9 December 2022 Published: 20 December 2022

**Copyright:** © 2022 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https:// creativecommons.org/licenses/by/ 4.0/). operations are more efficient compared to ordinary VSIs and CSIs [3]. In [4], the author discussed the main characteristic of the proposed interconnection system: it can provide power to the load even though one of its converters is under maintenance. To obtain a high voltage gain with less voltage stress on the switches, the cells are coupled in parallel for the LV bus, and in series for the HV bus.

For higher applications and high-power evaluations, MLIs are employed. An MLI is a setup in which the different variations of powered electronic devices are arranged and worked together with DC-connected voltages to deliver more significant levels of the waveform at the output side [5]. MLIs are liked because of their intrinsic benefits, for example, low switching pressure, low dv/dt rating across the switches, reliability, lower cost, reduced complexity, improved THD, and superior efficiency when used in applications [6]. For the most part, DC–DC gain converters are put into use for higher power applications, for example, solar PV systems, fuel cells, high discharge lights, electric power trains, high power density devices, induction engine drives, UPS, X-ray beams, medical equipment, auto applications, and so forth.

MLIs assume a significant role in renewable energy (RE) applications as well as in electric vehicles. As a result, MLIs employ advanced power semiconductor devices to develop a stepped waveform that seems to be near to a sine waveform. It is the ideal choice for generating vast output, mostly in SPV applications [7]. A novel hybrid MLI topology that integrates the concepts of hybrid and asymmetrical behavior is presented in work in [8]. The smaller number of devices and sources makes the architecture possible for applications linked to solar PV and motor drives. Authors in [9] developed a new MLI with symmetric and asymmetric structures, presented in this study. Asymmetric topologies employ a minimum switch count, while symmetric topologies demand equal DC source values. However, the switches in both structures experience multiple blocking voltages, lowering the losses. The author of the work [10] developed an MLI by employing stacked capacitors for three-phase four-wire grid supply systems. With inherent advantages such as high-power density, reliability in extended temperatures, and stable drop characteristics, it lacks in its cost for high voltage applications. The essential concept in EV works as such: it contains the battery which is fed to the inverter, followed by the motor, where it relies upon the sort of vehicle. This vital role is performed by the inverter alongside the controller [11]. By changing the duty cycles of the employed inverter, the result output can be controlled. Inverters likewise have a rise and impact in EV charging systems; they can either be a wired or a wireless system. Along these lines, different MLIs are planned by their applications [12]. A large portion of the EV's innovation is coordinated with the RES. This can be valuable for suitable systems while working in V2G operations, where the power flow ought to be bi-directional. These are additionally used to further develop the battery life, state of charge (SOC), and state of discharge (SOD).

The hybrid form of the MLI is another category. It typically consists of two sections. The staircase voltage is created in unidirectional polarity in the first section, referred to as level generation [13]. This is accomplished by combining the DC sources in a specific way to flip between levels. The second step involves switching the polarity, which results in a voltage across the positive and negative load. For this, an H-bridge inverter is typically employed [14]. In [15], the author referred to the DC voltage sources in this topology that can be linked in series to create all the additive combinations.

Additionally, they can be linked in parallel, increasing the required output voltage and current flexibility. The author referred to it as a switched series/parallel sources (SSPS) MLI. Series connected switching sources (SCSS) are a different architecture that has been discussed. In this work [16], a novel idea for generating new converter topologies and output voltage waveforms has the advantage of low harmonic content. The converter employs two orthogonal space vectors. The basic idea is founded on being able to produce 133 distinct output space vectors and to allow for stepwise RMS output voltage adjustment.

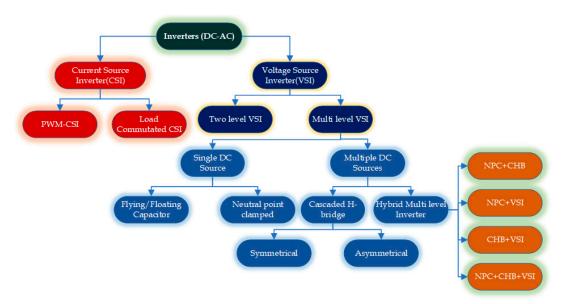

Classification of MLIs: Fundamentally, ordinary MLIs are characterized into three classifications, represented in Figure 1: the diode clamped (DC-MLI), the flying capacitor

type (FC-MLI), and the cascaded H-bridge type inverter (CHB-MLI). These are called classical inverters, where this kind of arrangement finds a use for switches that are straight forward and that correspond to their generating levels, resulting in complexity in the system [5]. Further arrangements are made for diminishing the switch count and making the structure a complex-free operation. Table 1 represents the merits and demerits of the classified topologies [6]. DC-MLI uses fewer DC voltage sources. However, it performs numerous tasks such as fault-tolerant analysis, is simple to use, and is essential in development. Yet because the available power is halved on the output side, it cannot be applied in high-voltage applications. In [11], FC-MLI shows many benefits. For example, a lower number of devices, and energy can be created by the power-dense capacitors for obtaining ripple-free voltage and the multiplying effect [11].

Figure 1. Classification of MLI.

CHB-MLI are classified into symmetrical and asymmetrical arrangements. To create a higher level of voltage, symmetrical arrangement is preferred, where the voltage of the DC source accommodated with each circuit is the same. Various magnitudes of voltage are given for creating asymmetrical configurations [17]. SC-MLI topology is created using available advantages in the cascaded and neutral point clamped MLIs, such as the low use of capacitors, switches, and diodes. It offers many benefits, such as boosting the output power and balancing the capacitor voltage.

Based on the preceding development in presumed converters, this review article makes an effort by providing an in-depth survey of all deduced converters currently used in the field of power semiconductor research. The following is a list of the review article's undertakings: (1) An overview of various determined converters is given, along with a discussion of how they differ from traditional converters. (2) Control methods used to operate the switches of the inferred converters are thoroughly explained.

The article is organized into four sections. The introduction and conclusion were explained better in Sections 1 and 4. A survey of various inferred converters is clarified, along with their operation and application point of view in Section 2. Section 3 clarifies various types of controllers exploits for working the inferred converters.

| Types of MLI<br>Configurations | Pros                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Cons                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |

|--------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Diode clamped<br>[18–23]       | <ul> <li>✓ They are used for rectification processes.</li> <li>✓ It tends to be deployed for high switching frequencies; therefore, switching operation is improved.</li> <li>✓ Capacitors can be charged with few input sources.</li> <li>✓ The method to control the circuit is straightforward.</li> <li>✓ Limited DC sources are required.</li> <li>✓ They are used for fault-tolerant operations.</li> </ul>                                                                                                                                                                            | <ul> <li>✓ It is challenging to balance the voltage in the circuit.</li> <li>✓ The switches present in the circuit share unequal voltages.</li> <li>✓ If there is a high output voltage level requirement, the number of diodes should be increased, i.e., no. of levels directly proportional to diodes.</li> <li>✓ Even if a high input source voltage is give the output voltage is halved due to the diode losses present in the circuit.</li> </ul>                                                                                                                                                                                                             |  |  |

| FC MLI<br>[19,20,23–26]        | <ul> <li>✓ Reduction in input DC components.</li> <li>✓ The level of the capacitor voltage is balanced.</li> <li>✓ The diode requirement is zero.</li> <li>✓ The flow of power can be controlled easily</li> <li>✓ Harmonics are reduced abruptly, with no need for extra usage of filters.</li> <li>✓ Transformer-less operation for high levels</li> </ul>                                                                                                                                                                                                                                 | <ul> <li>✓ The rating of the capacitor should be higl</li> <li>✓ The voltage balancing circuit, which is designed for the capacitor, is more complex.</li> <li>✓ Monitoring each capacitor voltage is difficult.</li> <li>✓ Losses are greater while transmitting real power.</li> <li>✓ Designing the circuit is more costly.</li> <li>✓ The estimation of pre-charging time is more complicated.</li> </ul>                                                                                                                                                                                                                                                        |  |  |

| CHB-MLI<br>[22,24,25,27,28]    | <ul> <li>✓ Due to the absence of diodes and capacitors, there is a huge reduction in the circuit component</li> <li>✓ Easy to design and control.</li> <li>✓ Voltage levels can be extended according to the required value.</li> <li>✓ In the cascaded H-bridge case, MLI bi-directional switches employed are fewer in number and operated for only particular levels. Therefore, stress is low across the switch.</li> <li>✓ Symmetrical and asymmetrical sources can be employed in both operations.</li> <li>✓ Electric shocks are prevented due to isolation in the circuit</li> </ul> | <ul> <li>✓ The output voltage is significantly lower.</li> <li>✓ To drive the circuits, more gating circuits are required.</li> <li>✓ This can be used only for specific applications where a separate DC source needed.</li> <li>✓ To obtain the maximum output, more DC sources are required.</li> <li>✓ When the bi-directional switch is employed for multiple levels for continuous operation, switch stress increases further, leading to switching losses and a reduction in efficiency</li> <li>✓ Complexity in the circuit, especially in asymmetrical configuration.</li> <li>✓ Different ratings of switches are needed for the configuration.</li> </ul> |  |  |

Table 1. Pros and Cons regarding different Multilevel Inverters.

# 2. Review of Derived Converters, Operation, and Applications

Since the utilization of multilevel inverters over the last many years, numerous alterations in the inverters have been performed with the usage of power electronic devices. For expanding the voltage levels in the inverter, the quantity of the switch count, the source count, and the components helped increase the circuit activity. This outcome results in different factors, such as increasing the circuit's complexity, increasing the weight and cost, stress across the switches, electromagnetic compatibility (EMC) and electromagnetic interference (EMI) issues, THD, and losses in the circuit. At long last, this prompts a decline in efficiency and impacts the nature of the power on the grid utilities/distribution systems. To decrease the previously mentioned drawbacks, the paper investigates the various topologies and their operation with the decreased part count. Right off the bat, in the year 1993, a decreased switch count was presented. For evaluating the operations of various topologies, asymmetrical and symmetrical arrangements are considered [11]. The main drawback of using a switched-capacitor is that it can produce only 5, 7, and 11 levels. Subsequently, planning an SC-MLI for more generating levels is a difficult task [28]. Due to the advantage of high switching operations and high voltage ratings, IGBT/MOSFET are used. Recently, wide band gap (WBG) semiconductors are also performing the operations for generating high levels. These also have low thermal conductivity and are highly stable during operation.

## 2.1. Operation of Derived Converters Based on DC Source Count

For easy understanding, Table 2 is framed, and the analysis of the derived converters is taken with respect to their DC source counts.

**Table 2.** Comparative analysis for different converters representing their switch counts, diodes, capacitors, inductors, DC source counts, number of levels generated, efficiency, THD, algorithm/controller used, and their applications.

| Ref No | Ns                                                               | Nd | N <sub>cap</sub> /N <sub>ind</sub> | N <sub>dc</sub> | Nl                                                                 | Efficiency<br>in (%) | THD                             | Algorithm/Contro<br>Used                                                    | ller Application                                                                          |

|--------|------------------------------------------------------------------|----|------------------------------------|-----------------|--------------------------------------------------------------------|----------------------|---------------------------------|-----------------------------------------------------------------------------|-------------------------------------------------------------------------------------------|

| [29]   | 14                                                               | 3  | 3                                  | 3               | 53                                                                 | 94.21                | 1.41                            | P&O                                                                         | SPV & EV                                                                                  |

| [30]   | 12                                                               | 0  | 0                                  | 6               | 35                                                                 | > 93                 | 1.90                            | FFS                                                                         | Low and Medium power factor loads                                                         |

| [31]   | 9                                                                | 2  | 0                                  | 5               | 23                                                                 | 93.06                | As per IEEE<br>standards        | FFS                                                                         | Industrial<br>Applications                                                                |

| [32]   | 10                                                               | 0  | 0                                  | 3               | 21                                                                 | 94.02                | 3.49                            | P&O-based<br>MPPT technique<br>is used                                      | SPV Energy Systems                                                                        |

| [15]   | 9                                                                | 3  | 7                                  | 6               | 17                                                                 | 98.05                | 3.88                            | SHE-PWM                                                                     | DEC                                                                                       |

|        | 11                                                               | 3  | 7                                  | 6               | 19                                                                 |                      |                                 | PD-PWM                                                                      | RES                                                                                       |

| [33]   | b]         10         0         3         15         As per IEEE |    | FFS and SF are                     | Medium and      |                                                                    |                      |                                 |                                                                             |                                                                                           |

|        | 12                                                               | 0  | 0                                  | 4               | 25                                                                 | 99.01                | standards<br><5%                | used                                                                        | High-power voltage<br>applications                                                        |

| [34]   | 6                                                                | 2  | 4/4                                | 2               | Higher level<br>of Voltages<br>(19 times<br>greater than<br>input) | 91                   | As per IEEE<br>standards<br><5% | Double-input<br>high DC–DC<br>topology is<br>employed                       | MPPT-based low and<br>medium power<br>applications and<br>Regenerative braking<br>in EV's |

| [35]   | 10                                                               | 4  | 4                                  | 6               | 17                                                                 | 93.02                | 2.57                            | SHE-PWM                                                                     | PV Systems                                                                                |

| [36]   | 10                                                               | 0  | 0                                  | 3               | 15                                                                 | >90                  | 3.50                            | Hybrid<br>Modulation                                                        | High-Speed<br>switching devices                                                           |

| [37]   | 10                                                               | 10 | 0                                  | 3               | 13                                                                 | 99.06                | 6.60                            | FFS                                                                         | SPV/RES                                                                                   |

| [38]   | 12                                                               | 4  | 4                                  | 1               | 13                                                                 | 95.29                | 5.74                            | FFS and HFS<br>Control loop<br>techniques                                   | RES                                                                                       |

| [39]   | 16                                                               | 2  | 4                                  | 2               | 13                                                                 | 94.18                | 3.26                            | FFS and HFS<br>control technique<br>is used along<br>with SHE               | SPV systems and drives                                                                    |

| [40]   | 9                                                                | 5  | 0                                  | 5               | 11                                                                 | >96                  | <4                              | Multi-carrier<br>level shifted<br>PWM strategy<br>with phase<br>disposition | Photo Voltaic<br>systems                                                                  |

Ns—Number of sources, Nd—Number of diodes, Ncap/Nind—Number of capacitors/inductors used, Ndc— Number of DC sources, Nl—Number of levels generated in topology.

# 2.1.1. Using Six DC Sources

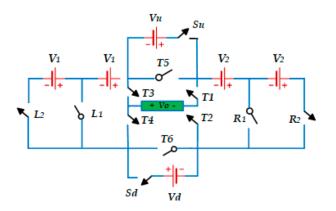

In [41], for *six* DC sources, the existing topology proposes 13-levels. In [42–44], the use of switches and the gate driver circuits are larger in number for a low level of steps in the output. This additionally causes the weight, size, and cost of the system to be more complicated. To avoid the disadvantages mentioned above, [30] created a structure that has eight unidirectional switches (*T*1, *T*2, *T*3, *T*4, *L*2, *R*2, *Su* and *Sd*), among which four are bidirectional (*L*1, *R*1, *T*5 and *T*6), which are shown in Figure 2.

Figure 2. 35-Level MLI.

To create the positive, negative, and zero levels, the switches rely upon the DC sources. The DC sources are chosen as upper and lower sources, where Vu = Vd = Vdc. In Figure 2, it may be seen that the left leg creates V1 = Vdc, and the sources in the right leg create V2 = 6Vdc. If the connections are made in this manner, we can generate 35 levels: 17 levels on the positive side and 17 on the negative side, and zero levels where the expense and size of the structure are diminished.

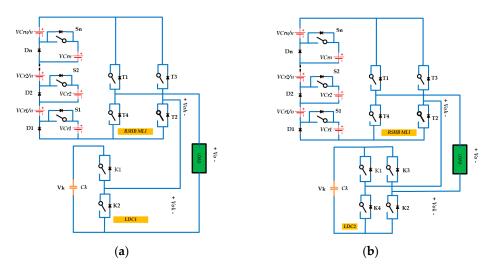

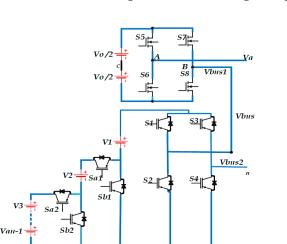

In [45,46], the authors involved discrete diodes in the circuit, which resulted in a more typical structure when contrasted with the traditional structure, topologies need just a few DC sources. In [47,48], they considered U-packed cells and the series connected switched capacitors. In any case, these have a few downsides, as it uses several part counts for producing the minimum output level. With a similar switch count, the proposed [15] topology creates more levels. It further includes a reduced switch H-bridge (RSHB) and LDC. The RSHB MLI profits with few units coupled to the H-bridge, where an H-bridge contains one switch and diode with two DC sources. By utilizing several units over and over in the circuit, for example, (1, 2, ..., n), it can produce 2n + 3 levels at the output. Switches and diodes in the circuit cannot be conducted all the while. On the other side, we consider, for one unit, the resulting voltage will be Vdc/n when the switch Sn is in OFF, where  $(Vcr1, Vcr2, \dots, Vcrn = Vdc)$ . When the switch *Sn* is turned ON, the result (Vrn) will be (Vdc + Vdc/n), where,  $(Vcr1/n, Vcr2/n, \dots Vcrn/n = Vdc)$ . In the proposed structure 1 from Figure 3a, it may be seen that PS2 has an LDC module which includes two switches (K1 and K2) and one capacitor (C). The two switches ought to be turned on alternatively to avoid heavy short circuits. In reference [32], to prevent the source from short-circuiting, the switches K1 and K2 in LDC1 should turn ON alternatingly. Additionally, K1 and K2 primarily function in the cycle's positive and negative halves, respectively. It is feasible to almost double the number of levels compared to the output produced by the RSHB MLI with just two more switches. Equivalent equations are (1)–(4) for the number of levels, sources/capacitors, and switches. The corresponding expressions are [32]:

Number of switch count (Nsw) = n + 6 (1)

Number of discrete diodes

$$(Ndd) = n$$

(2)

Number of DC sources/capacitors

$$(N_{dcs}) = 2n + 1$$

(3)

Number of levels  $(N_l) = 4n + 5$

In the proposed structure 2 from Figure 3b, it tends to be seen that the PS2 has an LDC module that involves four switches (K1, K2, K3 *and* K4) which are only a full H-bridge. The activity is the same as that of construction 1, yet in this, (K1 *and* K3) will be worked for the positive half cycle and (K2 *and* K4) will be worked for the negative half cycle. Generalized expressions for determining the component count in the PS2 are given as follows [32]:

Number of switch count

$$(N_{sw}) = n + 8$$

(5)

Number of discrete diodes

$$(N_{dd}) = n$$

(6)

Number of DC sources/capacitors

$$(N_{dcs}) = 2n + 1$$

(7)

Number of levels

$$(N_l) = 4n + 7$$

(8)

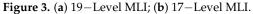

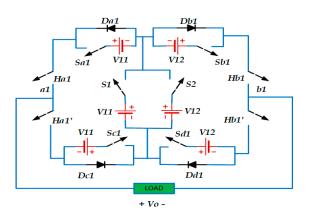

When contrasted with [49–52], the proposed [53] Figure 4 does not need an H-bridge even if it can create more levels; (*two 2Vdc*, 3vdc, and one 0.5Vdc) are given as input DC sources. (*Sa*1, *Sb*1, *Sc*1, *Sd*1) are the switches used to produce various levels of voltage for the result, which are implemented for boosting the voltage level. By providing complimentary switching operations, (*Ha*1, *Hb*1/) works during the positive half cycle and (*Hc*1, *Hd*1/) works during the negative half cycle. The switch voltage stress is limited by operating this way. The designed circuit is useful to lessen the total blocking voltage (TBV), and the overall performance of the ACCM MLI is improved successfully. The conduction and switching losses are all well determined, and they fundamentally rely upon the switching operation of the circuit.

Figure 4. 17–Level MLI.

(4)

# 2.1.2. Using Five DC Sources

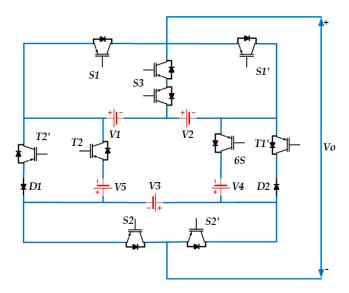

In [46,54–57], more DC sources with different magnitudes are chosen. In [56], the switches chosen were additionally more in number. The proposed [31] structure diminishes all of the disadvantages mentioned in the previous topologies. The design is made with a T-type and half-bridge inverter. An adjusted design was created, which is displayed in Figure 5. Out of nine, eight switching devices, named S1, S1', S2, S2', T1, T1', T2, T2', which are unidirectional, and switch S3 is unidirectional. The DC source sizes are unique and named as (V1 = V2, V3, V4 = V5). Because of the decreased switch count and the DC source, the blocking voltage is an additional benefit.

Figure 5. 23–Level MLI.

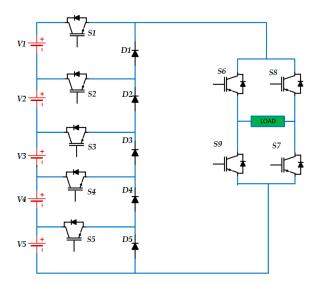

In [58–60], because of the adjustment of the temperature and irradiance in the created PV system, it brings about the open circuit voltages and the short circuit currents. By involving the MPPT controller in [40], this can be avoided. The converter configuration is kept up with stability even in disturbed load conditions. The designed topology is the change of the cascaded half-bridge MLI. The DC sources in Figure 6 are symmetrical where all the voltage sources are equivalent V1 = V2 = V3 = V4 = V5 = Vdc. For the level-generating part, the switches (S1 - S5) are alike, and for the polarity part (S6 - S9) are utilized in the H-bridge structure, where both operate at switching frequencies.

Figure 6. 11–Level MLI.

Modulation index (ma) for the reduced switch count is given by Equation (9), referred from [40], where *Vm* represents the amplitude of reference and *Vcr* represents the amplitude of carrier wave, and m relates to the number of levels

$$m_a = \left(\frac{2V_m}{V_{cr}(m-1)}\right) \tag{9}$$

# 2.1.3. Using Four DC Sources

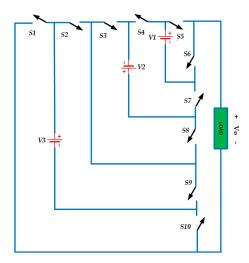

In [61], the construction works with 12 switches and creates a 17-level. When contrasted with [62], the TSV is kept up at 78. Cost and conversion efficiency are additionally an issue. For a similar switch count, the proposed topology [33] creates 25 levels, and the TSV is additionally 60. Reduced switching loss and cost are the main principles and advantages. Switches (S1 - S8) are unidirectional and one bidirectional switch (S9) is available in the circuit. Switches (S1 - S2), (S3 - S4), (S5 - S6), (S7 - S8) are paired in a complementary manner to avoid short circuits. The designed Figure 7 can be worked in two setups. Possibly, it very well may be symmetrical/asymmetrical. To have the circuit in a symmetrical setup, the voltages V1 and V2 should be equivalent to Vdc (V1 = V2 = Vdc). To acquire a similar circuit in the asymmetrical setup, the voltage magnitudes are different such that (V1 = Vdc) and (V2 = 3Vdc), thusly, the circuit performs. In a similar way to produce 25-level output, the structure needs to replace supply voltage source V1 with two configured voltage sources with the same magnitude. This is possible only with an asymmetrical configuration.

Figure 7. 25-Level MLI.

#### 2.1.4. Using Three DC Sources

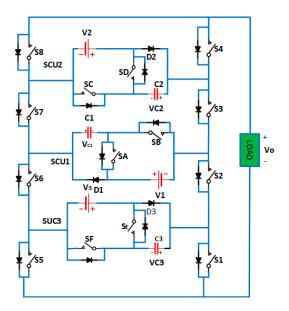

In [60], the part count per level and the TSV bring about a higher value. To further avoid the present circumstance in the MLIs, a new proposed [29] topology produces a 53-level result where a switched capacitor (SC) is placed at the front side alongside the H-bridge as shown in Figure 8. It boosts the voltage and makes the operation of capacitor charging and discharging simple. Utilizing many quantities of capacitors prompts an increment in the levels of the MLI. During ideal circumstances, capacitor *C*, which is at the front side of MLI, is charged to voltage *V*1 when it is associated with the corresponding DC source. Whenever the capacitor is made in series connection, it is discharged with regard to the load. At the point when the switch *S*2 is in conduction, the capacitor is charged for every half-cycle during  $Vo = \pm Vc1$ . During discharging mode, diode *D* and switch *S*2 will be in the *OFF* position. Capacitor *C* discharges while switch *S*1 is in conduction. The load currents are known with the help of *V*1 and *Vc*1 when it supplies energy to the load.

Figure 8. 53-Level MLI.

The cost factor relies upon many factors, for example, switch count, DC source count, total standing voltage (TSV), and the gate driver circuit. It is given by

Cost Factor (C.F) =

$$(N_s + N_{dk} + N_d + N_c + \alpha TSVpu) \times n$$

(10)

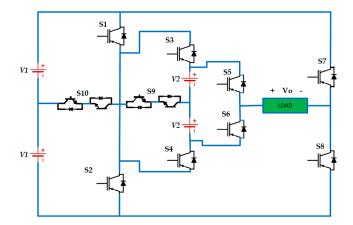

In [45,60,63–67], more gate driver circuits, switches, and DC sources are used for generating the resulting level. Along these lines, the TSV and cost work is less. Mentioned in [32], a proposed structure decreases the part count without diodes, capacitors, and inductors. Another design has been created, which is displayed in Figure 9. (V1, V2, V3) are utilized in this topology. Based on the switching operations, the output levels are obtained. Assuming the switching state is '1', it expresses that the switch is in conduction (ON state) and assuming that the switching state is '0' it implies that the switch is in (OFF) condition. To obtain the resulting voltage of 400 V, switches should be worked in various modes. Prior to that, voltages are opted based on a 1 : 2 : 7 proportion. In this way, it produces a voltage level of 40 V, 80 V, 280 V individually. It obstructs every one of the undesirable voltages, therefore, the cost of the design is decreased.

Figure 9. 21–Level MLI.

The total standing voltage is given by

$$TSV = 2(Vs1 + Vs3 + Vs5 + Vs7 + Vs9)$$

(11)

The current of 4 A is created at 400 V voltage level with the resistor value of 100  $\Omega$ . This topology has performed many tests with sudden disturbances for various loads, and it shows reliable results.

Number of switches

$$(N_s) = 2n + 2$$

(12)

Number of voltage levels

$$(N_l) = 7 \times n$$

(13)

Output voltage

$$(V_o) = 2n + 2 * Vdc$$

(14)

Cost factor (C.F) =

$$(N_s + N_{dk} + N_d + N_c + \alpha TSV pu) \times n$$

(15)

where, (Ns) is the number of switches present in the circuit, and (Ndk) is the driving board circuit. (Nd) and (Nc) indicate the number of diodes and capacitors. (TSV) is the total standing voltage and (n) demonstrates the number of DC sources used.

Fundamentally, losses are two types, conduction loss and switching loss.

Conduction loss

$$(P_{cl}) = [V_s + R_{si\beta}(t)]i(t)$$

(16)

Here (*Vs*) is the voltage drop, and (*Rs*) is the switch equivalent resistance.

In [65], the current design needs 28 and 36 switches for producing 11 and 15 levels. This shows the tremendous effect on design structure, and brings more conduction and switching losses. In [60], for the same hybrid topology, 16 switches are expected for the 15 level output. The proposed structure [36] employs a switched capacitor and an H-bridge circuit in the topology shown in Figure 10. It is apportioned into two sections. In the initial segment, it is a design with an H-bridge where the DC voltage is equivalent to Vo. Section 2 construction is an inverter where the voltage equivalents to *Vk.* The voltage source can utilise the example of exchanging capacitors. From this, we can comprehend that the simple switching circuit is placed in the front side (DC source) while (Sa - 1 - San - 1) and (Sb1 - Sbm - 1) are the operating switches that are associated in series. We can see that when Phase A is operated, switch Sb1 will be in ON state and the current passes through the switch, which brings about voltage V1. Consequently, it results (Vab = V1). The switches (Sa1 and Sb1) will be in conduction mode, therefore the remaining switches are OFF. Voltages (V1 and V2) are in series outcomes of Vab(Vab = V1 + V2). Later, switches (Sa1 and Sa2) are in ON state and different switches will be in OFF state, where the voltages (V1 and V3) are cascaded. This results in voltage as (Vab = V1 + V2 + V3). For example, conventional topology uses 12 switches for 11 level output. The introduced topology is basic in structure, reliable, and efficient for power applications. In the alteration of the introduced topology, we can create 21 levels with just 12 switches when the proportion of (Vo : Vk) is 1:3.

In [63,68,69], the device needs four DC sources for the 17-level. In [70,71], the MLI is designed by utilizing unidirectional switches. Hence, the gate driver circuit usage is greater. This outcome results in an expansion in part counts. The proposed design [37] uses just two DC sources and bi-directional switches, where just one gate driver circuit is put into service for the two bidirectional switches used in Figure 11. For voltage and current operations, unidirectional and bidirectional switches are utilized. Switches (*S1 and S2*), which are associated in the middle of the two-voltage source *V*1, need just one gate driver circuit. The voltage *V*2 is associated in the middle of the switch (*S3 and S4*), which changes the magnitude of operation. The modules associated in the circuit pairs are complementary switches (*S1 – S2*), (*S3 – S4*), (*S5 – S6*), (*S7 – S8*), which are not turned *ON* all the while. In the circuit, voltage sources are associated all the while, thus, it can further develop the voltage level.

Total Standing Voltage is given by

$$TSV = \sum_{x=1}^{2k+4} Sx$$

(17)

The voltage Vx is the blocking voltage at switch Sx

Figure 10. 15–Level MLI.

Sbm-

Figure 11. 13-Level MLI.

The reliability of the proposed structure is the major factor to be considered, and is calculated with the help of fault analysis.

# 2.1.5. Using Two DC Sources

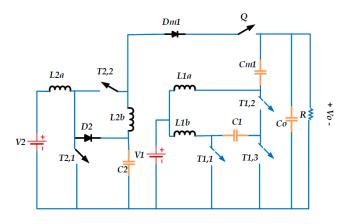

In [71], the device generates fewer levels. In [72], it requires N DC sources for the N level. In [73–75], because of the presence of pulsating input currents, this is not appropriate for different applications. The proposed [34] structure has less conduction loss because of low diode counts, and has a higher gain value. Figure 12 involves non-coupled inductors (*L1a*, *L1b*, *L2a*, *L2b*), capacitors (*C1*, *C2*, *Cm1*, *C0*), switches (*T1*, 1, *T1*, 2, *T1*, 3, *T2*, 1, *T2*, 2, *Q*), and diodes (*Dm1*, *D2*), and presents a fundamental dual topology. Here in the circuit, two voltage sources are named (*V1*) (either storable or non-storable) and (*V2*). Assuming the voltage source (*V1*) is storable, it can transfer energy or, in all likelihood, it can take from another source. At the point when the power flow is unidirectional, the component (*Q*) can be replaced by a diode. *Cm1* is used to further develop the voltage gain of the converter. In this topology, peak inverse voltage (*PIV*) assumes an imperative part, where it shows the tremendous effect on the switches, and subsequently the cost of the system is decreased. To avoid this condition, another new quantity is carried out, i.e., (*NPIV*), which is given by

$$NPIV = \left[ \left( \frac{PIV}{V_o} \right) \right] \tag{18}$$

Figure 12. Dual Input Topology.

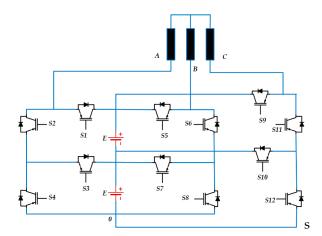

Ripple currents produced are due to inductors, which are directly proportional to the switching frequency. Further, this topology can be changed, and only 4n switches are utilized to create the higher level. This results in the output voltage being boosted to 19 times that of the input voltage. When contrasted with [76–87], the proposed topology [88,89] has a maximum efficiency of 99.06%. Unidirectional switches and DC sources accomplish the maximum output. Voltage DC sources are organized differently to obtain five-level results shown in Figure 13. The SKHI 10/12R gate driver circuit is connected to a heat sink, which lessens internal temperatures. Here 'E' represents the source voltage, Phases are represented with A, B, C. The switches in the Circuit are represented from (S1–S12) and finally 0 represents the reference/ground value.

Figure 13. 5-Level MLI.

#### 2.1.6. Using One DC Source

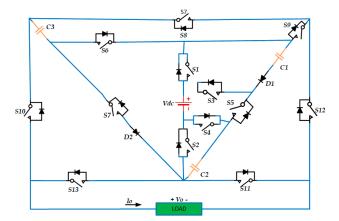

In [90–93] four capacitors find a use for a nine-level MLI. Because of the utilization of capacitors, inrush currents and voltage spikes across the diodes bring lower efficiency. Every one of the referenced drawbacks is changed in the [39], where it employs just three capacitors with one DC source. Figure 14 looks like an 'M'; thus, it is named an M-type switched capacitor MLI (MSCMLI). No H-bridge circuit is used. Out of 13, only 4 switches (S10 - S13) will be operated once in the fundamental cycle, and the excess switches (S6, S8, S9) will perform for the other method of operation. As such, the circuit will create all certain and negative levels in the result, which, accordingly, reduces the switching losses. The switches are matched to be integral (S1 - S3) and (S2 - S4) The level-1 is generated directly from the DC source and receives ( $\pm Vdc$ ), level-2 is obtained by adding the capacitor (C1) that turns the switch (S3) and receives the voltage ( $\pm 2Vdc$ ). The level-3 is delivered by adding the capacitors (C1) and (C2) and producing the ( $\pm 3Vdc$ ).

As such we can generate all levels. Where *Pl* represents the conduction loss, *Rint* denotes for the internal resistance

Conduction loss is given by

$$P_l = \frac{1}{2\pi} \int R_{int} I_c^2 d\omega t$$

(19)

Total Standing Voltage is given by  $TSV = \frac{TSV \text{ of all the indicidual switches}}{peak value of output}$  (20)

The cost factor is given by

$$CF = [N_{sw} + N_{dr} + N_d + N_c + \left(\delta * \frac{\text{TPSV}}{\text{Gain}}\right)](\frac{N_{dc}}{N_l})$$

(21)

*Nsw*—defines the number of switches used in the topology, *Ndr*—states the number of gate driver circuits,  $\frac{Ndc}{Nl}$ , represents the number of DC sources ratio to that of the number of voltage levels generated, *Nd* and *Nc* belong to the number of diodes and capacitors employed in the circuit.

Figure 14. 13-Level MLI.

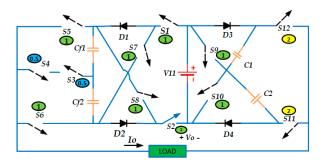

The switches used in the suggested structure [38] have only 10 switches compared to [94–97]. It engages just four self-capacitors, and every capacitor is boosted to three multiple times and generates higher levels with a short of one DC source, shown in Figure 15. In light of the switched capacitors, it is called cross-switched hybrid MLI, and is developed where the voltage is boosted to 1.5 times at the output side. The circuit is made with one DC source, with switches ranging from (S1 - S12), diodes (D1 - D4), and capacitors (C1, C2, Cf1, Cf2). Here, we additionally have the complementary switch sets as (S9, S10) and (S11, S12). By utilising the series-parallel balancing rule, capacitors present in the circuit are self-charged to Vm. Switches (S11 and S12) have the voltage stress as (2Vin); different switches will more often have voltage stress of just Vin. Capacitors (C1 and C2) have oneself charge capacity of Vin, and the excess capacitors (Cf1 and Cf2)have a value of 0.5*Vin*. In the proposed CHI, the primary level of the positive half cycle is  $(\pm 0.5Vin)$ , which is acquired by subtracting (Vcf1 and Vin). Similarly, the negative half cycle the capacitor C1 is in charging mode up to (-2Vin). The relevant equations for the respective circuit topology are stated in Equations (22)–(24). Where,  $f_s$ —is termed as the switching frequency,  $C_p$ —relates to parasitic capacitor at the blocking voltage  $V_B$ , and  $f_o$ defines the fundamental frequency

Switching loss is given by

$$P_l = \frac{1}{2} f_s C_p V_B^2$$

(22)

Ripple loss is given by

$$P_r = \frac{1}{2} f_o C \Delta V_c^2$$

(23)

where,  $I_0$  is the current referred-to output,  $V_{in}$  is the input voltage,  $V_d$  is the voltage drop of the diode,  $R_s$ —is the switch resistance,  $R_d$ —is the diode resistance,  $R_c$ —is the capacitor resistance.

Figure 15. 13–Level MLI.

The output frequencies are 50 Hz and 400 Hz, which can be used for high switching operations.

#### 2.2. MLI Design Based on the Application

The designed topologies are applied to various applications, some of which are mentioned below.

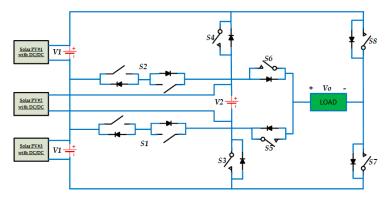

## 2.2.1. PV System Based/RES Applications

In [97], the FCML structure is intended to apply for lower voltage power switches. Accordingly, it has low ON resistance. To meet the utilization of 800 V, a three-stage AC/DC converter with GaN power semiconductors was developed with lesser losses. The scaling laws in the circuit show that it needs at least six levels to meet the load. These are primarily employed in aircraft motor drives. The effectiveness factor is additionally high when contrasted with different topologies. Ref. [98] uses the designed structure for charging station (CS) applications. The CS is planned where it coordinates the grid and the renewable energy source (RES). Power can sometimes be bidirectional, for this topology is intended to produce a three-level waveform among every leg and have a neutral point. When contrasted with a regular inverter, it lowers the filter circuits, voltage stresses, and unity power factors regardless of the functional model. It likewise balances the voltage across the capacitors. In [99], the 11-level is produced by SC-MLI, which delivers a voltage gain of 1.4 times more than the DC connect voltage appropriate for PV-based distribution systems. Ref. [100] refers to opto-isolation devices separating the voltage (either low/high) segments. The 1- $\varphi$ , 13-level H-bridge inverter, which handles photovoltaic applications where it lessens the THD and has low frequencies (650 Hz), improves the efficiency. A chip ARM regulator is utilized to accomplish high efficiency at 180 MHz.

## 2.2.2. Electric Vehicles (EV)

In [101], the multi-input multi-output DC converter structure is designed, which has the most reliable and efficient operation. Single-input multiple-output (SIMO) has voltage gain where it is high, continuous input current, and soft switching. This can be applied to isolated and non-isolated forms [102]. Supercapacitors work for high-power density applications. The DC converter structure is designed with two bidirectional switches, and the voltage is boosted without a transformer. DC link voltage is kept constant, which is fed to the motor. The capacitor can be charged/discharged during the buck and boost operation, proposing the usage of a seven level MLI, where every one of the switches is associated in series. This is done to decrease the switching losses concerning switching frequency. The THD results are 11%. It likewise lessens the strain on the switches. For each two-level, an IGBT/Diode switch is added. Blocking voltage is varied with the levels of clamping diodes. In [103], the NPC inverter builds effectiveness. The designed topology diminishes the weight on the switch, THD, and EMI. Overall, the quality of power is improved. In NPC-MLI is created with an independent DC source, which is utilized. It gives better power management while charging/discharging the battery [104]. To accomplish the objectives of the inverter, such as high-power density and low cost for traction drives, higher stable activity of the DC interface is required. By further developing the DC-link, EMI and voltage stress are the significant disadvantages. A [105], for lessening the size, weight, and filtering equipment of the multi-port converter, is created. This is particularly intended for electric vehicle applications with the utilization of hybrid energy storage systems. This builds the battery duration and the condition of charge level.

## 2.2.3. Motor Drive Applications

In [106], a cascaded T-Type multilevel inverter (CT2MLI) is proposed and applied to AC 415 V industrial application. In this, the converter shares a common emitter (CE) configuration. Along these lines, only one driver circuit is sufficient [107]. The designed topology is applied for PMSM drive applications. Where it works by double-level VSI for two and multilevel modes [108] by utilizing FCML structure in the inverter, the utilization of wideband gap (WBG) switches, and the exhibition of two-level 1200 V SiC switches, low voltage GaN HEMT switches accomplish 15.8 KW/dm<sup>3</sup> power density with an efficiency of 99.03%, and ML leg efficiency is noticed. It benefits 3-phase variable speed drives [109]. The designed converter uses eight switches, and is named the eight switches bridge converter (ESBC). This works to drive the brushless direct current motor (BLDCM), where the motor phases become detached through various switches. This likewise improves the system's reliability during fault conditions. In [105], a five-level diode clamped inverter is proposed to simplify the circuit, be robust-free, and have a great unique response. This is applied for direct torque control (DTC) and field-oriented control (FOC) in motor applications. In [110], different switching operations of the nine-level inverter are required to develop the dynamic load changing and the settling time of the applied induction motor further. The author in [16] presents that, although zero voltage vectors might also be employed, they appear to be useful for induction motor direct torque control in the OVT-ST inverter.

#### 2.2.4. Industrial Applications

In [111], two identical DC–AC inverters are connected in parallel with the assistance of the standard capacitor. The designed circuit benefits high-power applications and accomplishes the greatest efficiency of 93.7%. In [112], the multi-port converters are (a) MISO-able to work as boost and Cuk converters (b) SIMO-switch losses are diminished, and (c) MIMO-different duty cycles can be worked for various modes and are proposed and utilized for high/low-level applications.

#### 2.2.5. Multi-Purpose and Other Applications

The novel converter planned in [112] has simple and reliable inactivity, and can be applied for various AC–DC, DC–DC, DC–AC, and AC–AC applications. While utilizing traditional inverters because of many disadvantages, many adjusted forms of MLI are created. In [113], switched capacitor (SC) is developed, the voltage levels are greater in number, and the voltage level is boosted. Capacitors and inductors are eliminated within this topology to decrease the system's weight and cost. Along these lines, the effectiveness of the circuit can be improved to high and further develop the energy density. It is applied for AC–DC/DC–AC power conversions [113]. For different applications, such as EV and aerospace, the MLI is designed using silicon (Si) and gallium nitride (GaN). GaN e-FETs are preferred more than Si MOSFETs because the component is a three [114] plan  $3\varphi$  five-level CHB, even though MLI employs 24 switches, produces more voltage, and utilizes only two separate DC sources. Results in [115] show that the THD is diminished, and power quality is further developed when the VFISPWM technique is applied to multi-purpose applications. The authors of [116] proposed an inverter which is designed so that it has just a couple of parts counts, and it is used for naval ship propulsion rectifier applications.

#### 3. Modulation Techniques for Derived Converters

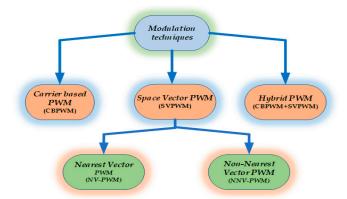

Different modulation schemes are accessible to control the operations in the inverter. A portion of these is informed here. Changing the voltage or frequency waveform modulation technique finds use where it involves two signs: the carrier signal and the reference signal. By changing the pulse width in the sinewave, the resulting levels of the voltage/frequency are modified. For the most part, the pulse width modulation (PWM) methods are created to diminish the operations and switching losses, and to further develop the system's efficiency [117]. Overall, modulation methods are grouped into two classifications. Low frequency/high switching frequency, which is sub characterized by (a) selective harmonic elimination (SHE), (b) nearest vector, (c) nearest level, and (d) hybrid modulation. The second one is high switching frequency, and it is sub-delegated by (a) multi carrier PWM is further classified as phase shifted and level shifted, phase disposition (PD-PWM) which is in phase with each carrier, phase opposition disposition (POD-PWM) where carriers are in phase above the zero references and below 180° out of phase, alternate phase opposition disposition (APOD-PWM) which is  $180^{\circ}$  out of the phase, (b) space vector modulation (2D-Algorithm and 3D-Algorithm) and (c) hybrid modulation. According to the accessibility and the suitability, these techniques are utilized.

Figure 16 classifies the commonly used modulation techniques. In [2], the carrier-based PWM technique is easy to implement and control. Output can be modulated using CBPWM. SVPWM is used for controlling the neutral point; also, [115] was used to calculate the timings of the modulation with level information. Nearest vector PWM is a part of SVPWM, similar to CBPWM [11]. SVPWM gives the exact switching sequences; it can be derived from the dwell times with easy computational effects and can be implemented in FPGA. Ref. [116] proposes the two frequency operations. Firstly, the low-frequency modulation, where the works are with a f = 50 Hz grid, supply frequency. It generates a qualified output waveform. Cost and efficiency are added parameters. Secondly, high-frequency modulation works with a switching frequency of 200 KHz. Duty cycles are controlled to obtain the desired output voltage at a particular frequency (f) [5]. Spatial vector represents the recommended SVPWM. It is made of three hexagons, whose size fluctuates depending on the DC input voltages [6]. Conventional CII uses common carrier interleaving or a discontinuous form of PWM (DPWM). Line PWM frequency is always equal to  $(2 \times n \times fc)$ . Standard interleaving and carrier manipulation schemes are employed. In [117], for a seven-level symmetrical inverter, the modulation index is given as  $m = \frac{\pi v_1}{\pi v_1}$  [30]. NPC topologies use (PD-SPWM) [53]. Modified PWM control strategy uses triangular signals as carrier signals and sinewaves as reference signals. PD strategy is used for carrier signals with a switching frequency of 1.1 KHz. Only two switching angles are required to calculate five-level output.

Figure 16. Classification of different modulation techniques.

Refs. [29,31] involves a P&O calculation-based MPPT procedure for the applications to extricate the maximum power from the PV array; the stable output is accomplished under all conditions (even partially shaded conditions).

## 3.1. Fundamental Frequency Switching (FFS) and High-Frequency Switching (HFS)

In [28], NLC control exchanges tasks and decreases THD. Reference [30] employs fundamental frequency switching (FFS), which is sub-classified as low switching frequency (LFS) and high switching frequency (HFS) [33]. It has an open loop and closed loop switching for specific applications [37]. It works so that only one switching operation is permitted in turn. Subsequently, it diminishes the losses in the system and accomplishes higher energy levels with minimal expense [38]. NLC is mostly used for higher levels because of its simple control [39]. It enjoys a significant benefit in that the computation angle switching can effectively store these qualities in the lookup table by the processor, and is perfectly carried out. Ref. [118] is used for a more severe level of adaptability in the exchanging activity with variable magnitude count.

## 3.2. Selective Harmonic Elimination (SHE)

In [32], to dispense with the odd-order harmonics (third, fifth, seventh, ninth, eleventh, thirteenth, fifteenth), PSO calculation is carried out in the selective harmonic elimination strategy [34,35]. PS1 structure utilizes carrier-based SPWM techniques [107], and the respective highlights of SHE are mentioned in Table 3. It likewise collaborates with the NR strategy for solving the angles of non-linear equations.

$$V(\omega t) = a_0/2 + \sum_{n=1}^{\infty} (a_n \cos(n\omega t) + b_n \sin(n\omega t)$$

(25)

Table 3. SHE-PWM technique advantages.

| Type of Technique | Pros                                                                                                         |  |

|-------------------|--------------------------------------------------------------------------------------------------------------|--|

| SHE-PWM           | $\checkmark$ It has low switching frequency/low operation and conduction loss                                |  |

|                   | $\checkmark$ In a single phase, triple harmonics are controlled.                                             |  |

|                   | $\checkmark$ Heavy computational calculations are reduced.                                                   |  |

|                   | <ul> <li>Balancing and unequal distribution of voltages can be controlled in<br/>case of DC-link.</li> </ul> |  |

|                   | $\checkmark$ It can be dealt with in any switching pattern.                                                  |  |

|                   | ✓ Dominant harmonics are monitored with intelligent algorithms in real-data implementation.                  |  |

## 3.3. Pulse Width Modulation (PWM)

Refs. [37,115] utilize pulse width modulation, where level shifted and phase shifted schemes play a vital role in this strategy [40]. FPGA-based harmonic reduction (HR) calculations can likewise be carried out in the strategy [103]. Harmonics in this scheme are limited, and voltage adjusting can be accomplished [15]. Additionally, FFT investigation and current strategies can likewise be carried out in numerous applications, and advantages related to PS-PWM are mentioned in Table 4.

Table 4. PS-PWM technique advantages.

| Type of Technique | Pros                                                                                            |

|-------------------|-------------------------------------------------------------------------------------------------|

| PS-PWM            | ✓ MLI performance is balanced throughout the operation during the charging/discharging process. |

|                   | ✓ It results in low leakage power and loss, therefore resulting in high efficiency.             |

|                   | $\checkmark$ It avoids leakage currents when applied to grid-connected systems.                 |

|                   | ✓ It operates in a safer region with a high switching frequency.                                |

## 3.4. Predictive Torque Control

In [107], the authors present the predictive torque control (PTC) and model predictive control (MPC) methods for calculating the errors present in the motor drives [105]. This additionally works on the decrease in system ripples and reduces the switching frequency.

#### 3.5. Perturb and Observe (P&O) and MPPT-Based Approach

An MPPT controller is used to operate solar PV to extract the maximum power possible from the PV module. Solar PV's efficiency and life span have improved throughout all of the disruptions above. The solar source can be set to the load to obtain maximum power production under different climatic conditions. By adjusting the voltage from the array by a small amount, the controller measures the power and, if it rises, performs more adjustments in that direction until the power stops rising [29]. The most popular strategy is perturb and observe (P&O), which might lead to power output oscillations. It is often referred to as the "hill climbing" technique, since it depends on the power versus voltage curve rising below the maximum power point and falling above it [32]. The perturb and observe method is the most used since it is so simple.

## 4. Conclusions

The study covers recent developments in the recently established MLI, where different topologies are compared with the conventional inverters to continue research and advancement in multi-level generations. As a result, it is understood that each topology has a distinct feature that leads to significant inherent benefits, such as a decrease in switching losses, voltage ripples, voltage stress, active switches, diodes, capacitors, and driver circuits. In addition, there are reductions in DC sources, TSV, TBV, THD, EMI issues, standard mode voltages, fault operations, quality output voltage, cost, volume, and weight, which improve the efficiency that aids in reducing the complexity of inverters. These are mostly preferred for RECS, PV, EV, and industrial drive applications. Comparative analysis with different topologies also made for a clear understanding. Asymmetrical configurations with different topologies, their operations, benefits, and applications are explained in a broad way. In some topologies of the circulating inrush currents, voltage balancing is minimal. Various modulation techniques and control schemes are also highlighted to know which will suit a particular application. It can be observed that the maximum efficiency achieved is 99.06%, and the THD factor is 1.41%. The extensive review shows that MLI faced many problems, such as high switching rating, larger filtering devices for distortion-free output, heating problems, more sensing components, and a lack of DC sources. For switching/frequency operations for higher levels, GaN/SiC switches are preferred solutions due to their inherent benefits such as high thermal conductivity, which also lowers the device count.

Author Contributions: Conceptualization, K.N.D.V.S.E. and M.A.N.D.; methodology, M.B.; software, P.V.; validation, M.B. and H.K.; formal analysis, K.N.D.V.S.E. and M.A.N.D.; investigation K.N.D.V.S.E., M.A.N.D. and A.S.; resources, P.V. and S.K.; data curation, K.N.D.V.S.E.; writing— K.N.D.V.S.E.; writing—review and editing, M.B. and H.K.; visualization, A.S. and H.K.; supervision, M.A.N.D. and P.V.; project administration, M.A.N.D., P.V., A.S. and S.K.; funding acquisition, S.K. All authors have read and agreed to the published version of the manuscript.

**Funding:** This work was supported by Science, Technology & Innovation Funding Authority (STDF) under grant (43180).

Data Availability Statement: Not applicable.

Conflicts of Interest: The authors declare no conflict of interest.

# Nomenclature

| MLI     | Multilevel Inverter                                        |

|---------|------------------------------------------------------------|

| THD     | Total Harmonic Distortion                                  |

| PWM     | Pulse Width Modulation                                     |

| EV      | Electric Vehicle                                           |

| PV      | Photovoltaic                                               |

| RECS    | Renewable Energy Conventional Sources                      |

| UPS     | Uninterrupted Power Supply                                 |

| RE      | Renewable Energy                                           |

| V2G     | Vehicle-to-Grid                                            |

| EMC/EMI | Electromagnetic Compatibility/Electromagnetic Interference |

| TBV     | Total Blocking Voltage                                     |

| TSV     | Total Standing Voltage                                     |

| SC      | Super Capacitor                                            |

| VSI     | Voltage Source Inverters                                   |

| CSI     | Current Source Inverters                                   |

| Q-ZSI   | Quasi-impedance Source Inverters                           |

| SC      | Super Capacitor                                            |

| SOC     | State of Charge                                            |

| SOD     | State of Discharge                                         |

| SCSS    | Switched Connected Switched Sources                        |

| SSPS    | Switched Series Parallel Sources                           |

| IGBT    | Insulated Gate Bi-polar Transistor                         |

| MOSFET  | Metal Oxide Converter Field Effect Transistor              |

| SC-MLI  | Switched Capacitor—Multilevel Inverter                     |

| PIV     | Peak Inverse Voltage                                       |

| WBG     | Wide Band Gap                                              |

| LV      | Low Voltage                                                |

| HV      | High Voltage                                               |

| LDC     | Level Doubling Circuits                                    |

|         |                                                            |

# References

- 1. Kumar, G.G.; Krishna, M.V.S.; Kumaravel, S.; Babaei, E. Multi-Stage DC-DC Converter Using Active LC2D Network with Minimum Component. *IEEE Trans. Circuits Syst. II Express Briefs* **2020**, *68*, 943–947. [CrossRef]

- Raju, K.N.; Rao, M.V.G.; Ramamoorthy, M. Hybrid modulation technique for neutral point clamped inverter to eliminate neutral point shift with minimum switching loss. In Proceedings of the TENCON 2015—2015 IEEE Region 10 Conference, Macao, China, 1–4 November 2015; Volume 2016, pp. 1–5. [CrossRef]

- 3. Rawa, M.; Ali, J.M.; Siddique, M.; Mekhilef, S.; Wahyudie, A.; Seyedmahmoudian, M.; Stojcevski, A. A new multilevel inverter topology with reduced dc sources. *Energies* **2021**, *14*, 4709. [CrossRef]

- Mamede, H.R.; Santos, W.M.D.; Coelho, R.F.; Martins, D.C. A multicell Dual-Active Bridge converter for increasing the reliability of power supply in a DC microgrid. In Proceedings of the 2015 IEEE First International Conference on DC Microgrids (ICDCM), Atlanta, GA, USA, 7–10 June 2015; pp. 274–279. [CrossRef]

- 5. Dorn-Gomba, L.; Guo, J.; Emadi, A. Multi-source inverter for power-split hybrid electric powertrains. *IEEE Trans. Veh. Technol.* **2019**, *68*, 6481–6494. [CrossRef]

- Tripathi, R.S.; Thukral, M.K. Switching Angles Computation of Multi-Level Inverter for Electrical Vehicle Application. In Proceedings of the 2019 Global Conference for Advancement in Technology (GCAT), Bangalore, India, 18–20 October 2019; pp. 5–9. [CrossRef]

- Sathik, J.; Aleem, S.H.E.A.; Alishah, R.S.; Almakhles, D.; Bertilsson, K.; Bhaskar, M.S.; Savier, G.F.; Dhandapani, K. A multilevel inverter topology using diode half-bridge circuit with reduced power component. *Energies* 2021, 14, 7249. [CrossRef]

- 8. Bassi, H.M.; Salam, Z. A new hybrid multilevel inverter topology with reduced switch count and dc voltage sources. *Energies* **2019**, *12*, 977. [CrossRef]

- 9. Gopal, Y.; Birla, D.; Lalwani, M. Selected Harmonic Elimination for Cascaded Multilevel Inverter Based on Photovoltaic with Fuzzy Logic Control Maximum Power Point Tracking Technique. *Technologies* **2018**, *6*, 62. [CrossRef]

- 10. Iwaszkiewicz, J.; Bogusławski, P.; Krahel, A.; Łowiec, E. Three-phase voltage outages compensator with cascaded multilevel converter. *Arch. Electr. Eng.* 2012, *61*, 325–336. [CrossRef]

- Pallo, N.; Coday, S.; Schaadt, J.; Assem, P.; Pilawa-Podgurski, R.C.N. A 10-Level Flying Capacitor Multi-Level Dual-Interleaved Power Module for Scalable and Power-Dense Electric Drives. In Proceedings of the 2020 IEEE Applied Power Electronics Conference and Exposition (APEC), New Orleans, LA, USA, 15–19 March 2020; pp. 893–898. [CrossRef]

- 12. Nabae, A.; Takahashi, I.; Akagi, H. A New Neutral-Point-Clamped PWM Inverter. *IEEE Trans. Ind. Appl.* **1981**, *IA*-17, 518–523. [CrossRef]

- 13. Tsai, C.T.; Chen, W.M. Buck converter with soft-switching cells for PV panel applications. Energies 2016, 9, 148. [CrossRef]

- 14. Tobón, A.; Peláez-Restrepo, J.; Villegas-Ceballos, J.P.; Serna-Garcés, S.I.; Herrera, J.; Ibeas, A. Maximum power point tracking of photovoltaic panels by using improved pattern search methods. *Energies* **2017**, *10*, 1316. [CrossRef]

- 15. Siddique, M.D.; Mekhilef, S.; Shah, N.M.; Sarwar, A.; Iqbal, A.; Memon, M.A. A New Multilevel Inverter Topology with Reduce Switch Count. *IEEE Access* 2019, *7*, 58584–58594. [CrossRef]

- Hashad, M.; Iwaszkiewicz, J. A novel orthogonal-vectors-based topology of multilevel inverters. *IEEE Trans. Ind. Electron.* 2002, 49, 868–874. [CrossRef]

- Lin, B.R.; Zhuang, Y.S.; Syu, H.S. Parallel soft switching converters: Analysis, design and implementation. In Proceedings of the 2018 13th IEEE Conference on Industrial Electronics and Applications (ICIEA), Wuhan, China, 31 May–2 June 2018; pp. 1016–1021. [CrossRef]

- Pharne, I.D.; Bhosale, Y.N. A review on multilevel inverter topology. In Proceedings of the 2013 International Conference on Power, Energy and Control (ICPEC), Dindigul, India, 6–8 February 2013; pp. 700–703. [CrossRef]

- Hasan, N.S.; Rosmin, N.; Osman, D.A.A.; Musta'Amal@jamal, A.H. Reviews on multilevel converter and modulation techniques. *Renew. Sustain. Energy Rev.* 2017, 80, 163–174. [CrossRef]

- Rodriguez, J.; Bernet, S.; Steimer, P.K.; Lizama, I.E. A Survey on Neutral-Point-Clamped Inverters. *IEEE Trans. Ind. Electron.* 2010, 57, 2219–2230. [CrossRef]

- Roy, A.D.; Umayal, C. A review of various multilevel inverter topologies with reduced component count. In Proceedings of the 2018 International Conference on Recent Trends in Electrical, Control and Communication (RTECC), Malaysia, 20–22 March 2018; pp. 234–239. [CrossRef]

- Choudhury, S.; Bajaj, M.; Dash, T.; Kamel, S.; Jurado, F. Multilevel Inverter: A Survey on Classical and Advanced Topologies, Control Schemes, Applications to Power System and Future Prospects. *Energies* 2021, 14, 5773. [CrossRef]

- 23. Venkataramanaiah, J.; Suresh, Y.; Panda, A.K. A review on symmetric, asymmetric, hybrid and single DC sources based multilevel inverter topologies. *Renew. Sustain. Energy Rev.* 2017, 76, 788–812. [CrossRef]

- McGrath, B.P.; Holmes, D.G. Analytical modelling of voltage balance dynamics for a flying capacitor multilevel converter. In Proceedings of the 2007 IEEE Power Electronics Specialists Conference, Orlando, FL, USA, 17–21 June 2007; Volume 23, pp. 1810–1816. [CrossRef]

- 25. Prabaharan, N.; Palanisamy, K. A comprehensive review on reduced switch multilevel inverter topologies, modulation techniques and applications. *Renew. Sustain. Energy Rev.* 2017, *76*, 1248–1282. [CrossRef]

- 26. Malinowski, M.; Gopakumar, K.; Rodriguez, J.; Perez, M.A. A survey on cascaded multilevel inverters. *IEEE Trans. Ind. Electron.* **2009**, *57*, 2197–2206. [CrossRef]

- 27. Masoudina, F.; Babaei, E.; Sabahi, M.; Alipour, H. New cascaded multilevel inverter with reduced power electronic components. *Iran. J. Electr. Electron. Eng.* 2020, *16*, 107–113. [CrossRef]

- Dhanamjayulu, C.; Padmanaban, S.; Ramachandaramurthy, V.K.; Holm-Nielsen, J.B.; Blaabjerg, F. Design and Implementation of Multilevel Inverters for Electric Vehicles. *IEEE Access* 2020, *9*, 317–338. [CrossRef]

- Varesi, K.; Karimi, M.; Kargar, P. A New Cascaded 35-Level Inverter with Reduced Switch Count. In Proceedings of the 2019 Iranian Conference on Renewable Energy & Distributed Generation (ICREDG), Tehran, Iran, 11–12 June 2019; pp. 11–12. [CrossRef]

- Hosseinzadeh, M.A.; Sarbanzadeh, M.; Sarbanzadeh, E.; Rivera, M.; Wheeler, P. New Asymmetric Cascaded Multi-level Converter with Reduced Components. In Proceedings of the 2018 IEEE International Conference on Electrical Systems for Aircraft, Railway, Ship Propulsion and Road Vehicles & International Transportation Electrification Conference (ESARS-ITEC), Nottingham, UK, 7–9 November 2018; pp. 7–12. [CrossRef]

- Khasim, S.R.; Dhanamjayulu, C.; Padmanaban, S.; Holm-Nielsen, J.B.; Mitolo, M. A Novel Asymmetrical 21-Level Inverter for Solar PV Energy System with Reduced Switch Count. *IEEE Access* 2021, *9*, 11761–11775. [CrossRef]

- 32. Bana, P.R.; Panda, K.P.; Panda, G. Power Quality Performance Evaluation of Multilevel Inverter with Reduced Switching Devices and Minimum Standing Voltage. *IEEE Trans. Ind. Inform.* 2020, *16*, 5009–5022. [CrossRef]

- Varesi, K.; Hosseini, S.H.; Sabahi, M.; Babaei, E.; Saeidabadi, S.; Vosoughi, N. Design and Analysis of a Developed Multiport High Step-Up DC-DC Converter with Reduced Device Count and Normalized Peak Inverse Voltage on the Switches/Diodes. *IEEE Trans. Power Electron.* 2019, 34, 5464–5475. [CrossRef]

- Panda, K.P.; Bana, P.R.; Panda, G. Design and Control of An Asymmetrical Cascaded Compact Module Multilevel Inverter for PV System. In Proceedings of the TENCON 2019-2019 IEEE Region 10 Conference (TENCON), Kochi, India, 17–20 October 2019; pp. 2616–2621. [CrossRef]

- 35. Ebadpour, M.; Bagher, M.; Sharifian, B.; Hosseini, S.H. A New Structure of Multilevel Inverter with Reduced Number of Switches for Electric Vehicle Applications. *Energy Power Eng.* **2011**, *3*, 198. [CrossRef]

- 36. Siddique, M.D.; Rawa, M.; Mekhilef, S.; Shah, N.M. A new cascaded asymmetrical multilevel inverter based on switched dc voltage sources. *Int. J. Electr. Power Energy Syst.* **2021**, 128, 106730. [CrossRef]

- Panda, K.P.; Bana, P.R.; Panda, G. A Reduced Device Count Single DC Hybrid Switched-Capacitor Self-Balanced Inverter. *IEEE Trans. Circuits Syst. II Express Briefs* 2021, 68, 978–982. [CrossRef]

- Panda, K.P.; Bana, P.R.; Panda, G. A Switched-Capacitor Self-Balanced High-Gain Multilevel Inverter Employing a Single DC Source. *IEEE Trans. Circuits Syst. II Express Briefs* 2020, 67, 3192–3196. [CrossRef]

- Kanimozhi, M.; Ramaprabha, R. Design of 500W standalone photovoltaic system with reduced switch count multilevel inverter. In Proceedings of the 2017 Trends in Industrial Measurement and Automation (TIMA), Chennai, India, 6–8 January 2017; pp. 4–10. [CrossRef]

- 40. Salem, A.; van Khang, H.; Robbersmyr, K.G.; Norambuena, M.; Rodriguez, J. Novel Three-Phase Multilevel Inverter with Reduced Components for Low- and High-Voltage Applications. *IEEE Trans. Ind. Electron.* **2021**, *68*, 5978–5989. [CrossRef]

- Amadeh-Roodmajan, M.; Monfared, M.; Hashemizadeh-Ashan, S. A single-phase cascaded multilevel inverter composed of four-level sub-multilevel cells. In Proceedings of the 2017 8th Power Electronics, Drive Systems & Technologies Conference (PEDSTC), Mashhad, Iran, 14–16 February 2017; pp. 389–394. [CrossRef]

- Gohari, A.; Mosallanejad, A.; Afjei, E. New symmetric cascaded multilevel inverter with reduced number of controlled devices and low blocked voltage by switches. In Proceedings of the 2017 8th Power Electronics, Drive Systems & Technologies Conference (PEDSTC), Mashhad, Iran, 14–16 February 2017; pp. 502–506.

- Manjrekar, M.; Lipo, T. Hybrid multilevel inverter topology for drive applications. In Proceedings of the APEC'98 Thirteenth Annual Applied Power Electronics Conference and Exposition, Anaheim, CA, USA, 15–19 February 1998; Volume 2, pp. 523–529. [CrossRef]