Article

# Circuit Structure and Control Method to Reduce Size and Harmonic Distortion of Interleaved Dual Buck Inverter

Min-Gi Cho<sup>®</sup>, Sang-Hoon Lee, Hyeon-Seok Lee<sup>®</sup>, Yoon-Geol Choi<sup>®</sup> and Bongkoo Kang \*

Department of Electrical engineering, Pohang University of science and technology, Pohang 790-783, Korea; lunarmagic@postech.ac.kr (M.-G.C.); power2sh@postech.ac.kr (S.-H.L.); hsasdf@postech.ac.kr (H.-S.L.); ygchoi@postech.ac.kr (Y.-G.C.)

\* Correspondence: bkkang@postech.ac.kr; Tel.: +82-54-279-5939

Received: 13 January 2020; Accepted: 19 March 2020; Published: 24 March 2020

**Abstract:** A new circuit structure and control method for a high power interleaved dual-buck inverter are proposed. The proposed inverter consists of six switches, four diodes and two inductors, uses a dual-buck structure to eliminate zero-cross distortion, and operates in an interleaved mode to reduce the current stress of switch. To reduce the total harmonic distortion at low output power, the inverter is controlled using discontinuous-current-mode control combined with continuous-current-mode control. The experimental inverter had a power-conversion efficiency of 98.5% at output power = 1300 W and 98.3% at output power = 2 kW, when the inverter was operated at an input voltage of 400  $V_{DC}$ , output voltage of 220  $V_{AC}/60$  Hz, and switching frequency of 20 kHz. The total harmonic distortion was < 0.66%, which demonstrates that the inverter is suitable for high-power dc-ac power conversion.

Keywords: DC-AC power conversion; inverters; harmonic distortion; low cost

### 1. Introduction

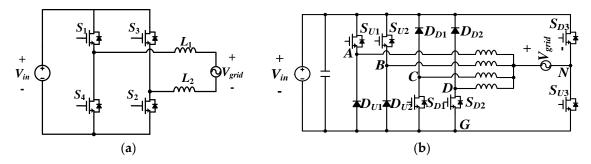

The full-bridge inverter (FBI, Figure 1a) is widely used for dc-ac power conversion because of its simple structure and easy control [1]. An FBI uses sinusoidal modulation of the switching duty to produce an alternating output voltage. The FBI has a shoot-through problem [2], which occurs when the high side and low side switches ( $S_1$  and  $S_4$ , or  $S_3$  and  $S_2$ ) are turned on at the same time; this problem can cause serious circuit damage. The shoot-through problem can be solved by inserting a dead-time between the gate pulses of the high and low side switches, but inserting a dead-time changes the effective switching duty ratio and increases zero-cross distortion (ZCD) [3]. The FBI has the other disadvantage of requiring high-rated switches and large output filters [4,5].

Various dual-buck inverters [6–15] have been proposed to remedy the disadvantages of the FBI. The dual-buck inverters use freewheeling diodes to solve the shoot-through problem but have high output current ripple. The interleaved dual-buck inverter (IDBI) in [9], as shown in Figure 1b, is basically a parallel connection of four buck converters. In this inverter,  $S_{U1}$  and  $S_{U2}$  operate to generate positive sinusoidal voltage,  $S_{D1}$  and  $S_{D2}$  operate to generate negative sinusoidal voltage, and the switching-phase differences between  $S_{U1}$  and  $S_{U2}$  and between  $S_{D1}$  and  $S_{D2}$  are set to 180°. Thus, the current of  $S_{U1}$  is interleaved with that of  $S_{U2}$ , and the current of  $S_{D1}$  is interleaved with that of  $S_{D2}$ . Using an interleaved mode reduces conduction losses, output current ripple, and current stress in switches and diodes. IDBI requires four inductors, so it is expensive and bulky. When IDBI uses typical sinusoidal pulse width control and operates at a low output power  $P_o$ , IDBI has much higher total harmonic distortion (THD) of the output current than that of the FBI.

Energies **2020**, *13*, 1531 2 of 19

**Figure 1.** Circuit structure of dc-ac inverters: (a) full-bridge inverter (FBI) and (b) interleaved dual-buck inverter of [9] (IDBI [9]).

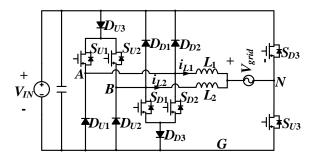

The inverter proposed in this paper (Figure 2) is a modified IDBI. This inverter inherits the IDBI's advantages but uses two reverse-current-protection diodes  $D_{D3}$  and  $D_{U3}$  to reduce the number of inductors and a new control method to reduce the THD of the output current. The proposed inverter operates in discontinuous conduction mode (DCM) [16] when the output current is below the threshold; otherwise, it operates in continuous conduction mode (CCM). The circuit structure and principle of operation are described in Section 2, experimental results and discussions are given in Section 3, and a conclusion is given in Section 4.

Figure 2. Circuit structure of the proposed inverter.

#### 2. Proposed Interleaved Dual-buck Inverter

# 2.1. Circuit Structure and Principle of Operation

The proposed inverter (Figure 2) uses two dual-buck legs (leg 1:  $S_{U1}$ ,  $D_{U1}$ ; leg 2:  $S_{U2}$ ,  $D_{U2}$ ) to generate  $V_{grid} \ge 0$  V, two dual-buck legs (leg 3:  $S_{D1}$ ,  $D_{D1}$ ; leg 4:  $S_{D2}$ ,  $D_{D2}$ ) to generate  $V_{grid} < 0$  V, two blocking diodes ( $D_{U3}$ ,  $D_{D3}$ ) to prevent the current flowing through the body diode of switch during freewheeling mode, and two unfolding switches ( $S_{U3}$ ,  $S_{D3}$ ) to determine the polarity of the output current. Legs 1 and 4 are connected to  $L_1$ , and legs 2 and 3 are connected to  $L_2$ . Therefore, the proposed inverter requires two inductors, unlike interleaved dual-buck inverters, which have four legs and one inductor per leg. The proposed inverter works with the switching states and leg voltages  $V_{AN\_on}$  and  $V_{AN\_off}$  in Table 1. Leg switches  $S_{U1}$ ,  $S_{U2}$ ,  $S_{D1}$ , and  $S_{D2}$  operate at a fixed switching frequency  $f_s = 1/T_s$ , where  $T_s$  is the switching period. The switching duty D is varied to produce a sinusoidal output voltage  $V_{grid}(t) = V_g \sin(\omega t)$ .

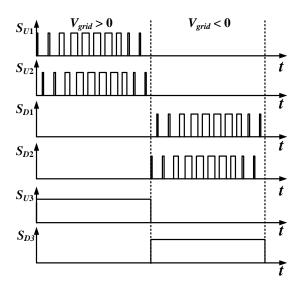

The simplified gate signals (Figure 3) for the proposed inverter show that legs 1 and 2 operate for  $V_{grid} > 0$  V and legs 3 and 4 operate for  $V_{grid} < 0$  V.  $S_{U3}$  turns for  $V_{grid} \ge 0$  V and  $S_{D3}$  turns on for  $V_{grid} < 0$  V. To obtain interleaved dual-buck operation, the switching phase differences between  $S_{U1}$  and  $S_{U2}$  and between  $S_{D1}$  and  $S_{D2}$  are set to  $T_s/2$ . The difference in switching phases reduces ZCD and prevents shoot-through without inserting dead time between switching pulses (Table 1).

Energies **2020**, *13*, 1531 3 of 19

| $ ule{V_{ m grid}}$     | ≥0 V     | <0 V      |

|-------------------------|----------|-----------|

| $S_{U1}$                | ON/OFF   | OFF       |

| $\frac{S_{U1}}{S_{U2}}$ | ON/OFF   | OFF       |

|                         | ON       | OFF       |

| $\frac{S_{U3}}{S_{U3}}$ |          |           |

| $S_{D1}$                | OFF      | ON/OFF    |

| $S_{D2}$                | OFF      | ON/OFF    |

| $S_{D3}$                | OFF      | ON        |

| V <sub>AN_on</sub>      | $V_{in}$ | $-V_{in}$ |

| $V_{AN\_off}$           | 0        | 0         |

Table 1. Switching states and input voltages for inductors in the proposed inverter.

**Figure 3.** Simplified gate signals of the proposed inverter.

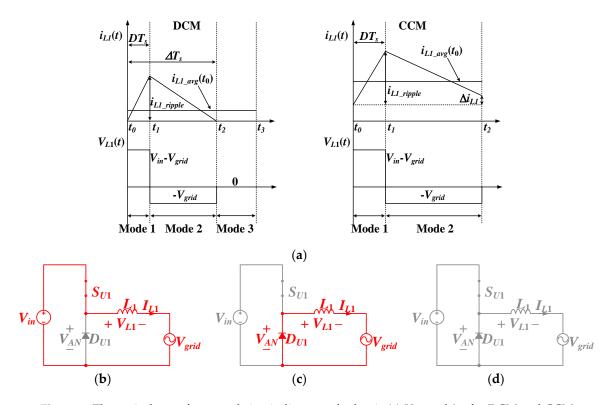

When  $V_{grid} > 0$  V, the current  $i_{L1}$  and voltage  $V_{L1}$  waveforms of the inductor  $L_1$  (Figure 4a) consist of three operating modes: Mode 1 during which the input energy is delivered to  $L_1$  and the load; Mode 2 during which the stored energy in  $L_1$  is delivered to the load; and Mode 3 during which the stored energy in  $L_1 = 0$ ; Mode 3 occurs only when the inverter operates in DCM.

Mode 1 starts at  $t_0 = (n-1)T_s$  by turning on  $S_{U1}$  (Figure 4b), where the integer n is a switching sequence number. During this mode, the output voltage  $V_{AN}$  of leg 1 is  $V_{in}$ . The inductor current  $i_{L1}(t)$  increases as t increases, because  $V_{L1} = V_{AN} - V_{grid} > 0$  V and

$$i_{L1}(t) = i_{L1}(t_0) + \frac{1}{L_1} \int_{t_0}^t V_{L1}(t) dt.$$

(1)

Mode 2 starts at  $t_1 = (n-1+D)T_s$  by turning off  $S_{U1}$  (Figure 4c). During this mode,  $V_{AN}$  is 0 V.  $i_{L1}(t)$  decreases as t increases because  $V_{L1} = V_{AN} - V_{grid} < 0$  V and

$$i_{L1}(t) = i_{L1}(t_1) + \frac{1}{L_1} \int_{t_1}^{t} V_{L1}(t) dt.$$

(2)

Mode 3 starts at  $t_2=(n-1+\Delta)T_s$  where  $\Delta T_s$  is duration of  $i_{L1}(t)>0$ , when  $D_{U1}$  is turned off (Figure 4d). This mode is skipped when  $\Delta=1$ , i.e., when the inverter is operating in CCM. During this mode,  $V_{AN}=V_{grid}$  because  $i_{L1}(t)=0$  and the energy stored in  $L_1$  is 0.

Energies **2020**, *13*, 1531 4 of 19

The voltage  $V_{AN}$  of node A with respect to node N equals to  $V_{grid} + V_{L1}(t)$ . The switching states (Table 1) produce  $V_{AN} = V_{in}$  in Mode 1,  $V_{AN} = 0$  V in Mode 2, and  $V_{AN} = V_{grid}$  in Mode 3. The average of  $V_{AN}$  for one switching period is expressed as

$$V_{AN\_avg} = V_{grid} + V_{L1\_avg} = V_{grid} + L_1 \frac{di_{L1\_avg}}{dt}.$$

(3)

$S_{U1}$  operates with a switching duty of  $D = D_{SU1}$ .  $V_{AN\_avg}$  can also be expressed as

$$V_{AN\_avg} = V_{in}D_{SU1} + V_{grid}(1 - \Delta), \tag{4}$$

because  $V_{AN} = V_{in}$  in Mode 1,  $V_{AN} = 0$  V in Mode 2, and  $V_{AN} = V_{grid}$  in Mode 3. Solving for  $\Delta$  using (3) and (4) yields

$$\Delta = \frac{V_{in}D_{SU1}}{V_{grid}} - \frac{L_1}{V_{grid}} \frac{di_{L1\_avg}}{dt}.$$

(5)

$i_{L1\_avg}$  is calculated using Equations (1) and (2) as

$$i_{L1\_avg} \approx i_{L1}(t_0) + \left(\frac{V_{in} - V_{grid}(t_0)}{2L_1}\right) D_{SU1} T_s \Delta.$$

(6)

**Figure 4.** Theoretical waveforms and circuit diagrams for leg 1: (a)  $V_{L1}$  and  $i_{L1}$  for DCM and CCM operation, (b) circuit diagrams for Mode 1, (c) circuit diagrams for Mode 2, and (d) circuit diagrams for Mode 3.

To achieve a power factor of 1, the time average of output current  $i_{o\_avg}$  should be  $I_o \sin(\omega t)$  for  $V_{grid}(t) = V_g \sin(\omega t)$ . The inverter has  $L_1 = L_2 = L$  and operates in interleaved dual-buck mode,

Energies **2020**, *13*, 1531 5 of 19

so  $i_{o\_avg} = 2i_{L1\_avg}$ . When the inverter operates in DCM,  $D_{SU1}$  at  $t = t_0$  to produce sinusoidal  $i_{o\_avg}$  is obtained using Equations (5) and (6),  $2\pi f_s >> \omega$  and  $i_{L1}(t_0) = 0$  as

$$D_{SU1} = \sqrt{\frac{LI_oV_g\sin^2(\omega t)}{V_{in}(V_{in} - 2V_g\sin(\omega t))T_s} + \left(\frac{\omega LI_o\cos(\omega t)}{4V_{in}}\right)^2} + \frac{\omega LI_o\cos(\omega t)}{4V_{in}}.$$

(7)

When the inverter is operating in CCM,  $\Delta = 1$  and  $D_{SU1}$  at  $t = t_0$  is obtained using Equation (5) as

$$D_{SU1} = \frac{V_g \sin(\omega t)}{V_{in}} + \frac{\omega L I_o \cos(\omega t)}{2V_{in}}.$$

(8)

The DCM interval during which the inverter operates in DCM is calculated using Equations (5), (7), and  $\Delta \leq 1$  as

$$0 < \omega t \le \sin^{-1} \left( \frac{V_{in}}{V_g} \left( 1 - \frac{LI_o}{V_g T_s} \right) \right) \tag{9}$$

when  $V_{grid}$  increases, and

$$\pi - \sin^{-1}\left(\frac{V_{in}}{V_g}\left(1 - \frac{LI_o}{V_gT_s}\right)\right) \le \omega t < \pi,\tag{10}$$

when  $V_{grid}$  decreases.

The condition for operating the inverter only in CCM is obtained by setting the argument of arcsine in Equations (9) and (10) less than 0, and is given as

$$I_o > \frac{V_g T_s}{I_s},\tag{11}$$

and the condition for operating the inverter only in DCM is obtained by setting the argument of arcsine in Equations (9) and (10) greater than 1, and is given as

$$I_o < \frac{V_g T_s}{L} \left( 1 - \frac{V_g}{V_{in}} \right). \tag{12}$$

The waveforms  $i_{L2}$  and  $V_{L2}$  of the inductor  $L_2$  for  $V_{grid} > 0$  V are the same as  $i_{L1}$  and  $V_{L1}$  except that they are delayed by  $T_s/2$ .

The waveforms  $i_{L1}$ ,  $V_{L1}$ ,  $i_{L2}$ , and  $V_{L2}$  for  $V_{grid} < 0$  V are identical to the waveforms  $i_{L2}$ ,  $V_{L2}$ ,  $i_{L1}$ , and  $V_{L1}$  for  $V_{grid} > 0$  V, respectively, except that the polarity is reversed.

# 2.2. Design Constraint for $L_1$ and $L_2$

The inverter must operate at  $I_0 \le I_{0,\text{max}}$ . The highest switching duty  $D_{SU1\_\text{max}}$  of  $S_{U1}$  is calculated using Equation (8) as

$$D_{SU1\_max} = \frac{\sqrt{4V_g^2 + (\omega L I_{0\_max})^2}}{2V_{in}} < 1$$

(13)

which results in the upper bound of  $L_1 = L_2 = L$  as

$$L < \frac{2\sqrt{V_{in}^2 - V_g^2}}{\omega I_{0 \text{ max}}}. (14)$$

This condition gives L < 103.44 mH when  $P_0 = 2$  kW and  $I_{0_{\text{max}}} = 12.9$  A.

Energies **2020**, *13*, 1531 6 of 19

The current and voltage waveforms for  $L_2$  are same as those for  $L_1$ , except the time delay by  $T_s/2$ ; hence, the output current ripple  $i_{o\_ripple}$  of the proposed inverter can be calculated using Equations (1), (2) and (8) as

$$i_{o\_ripple} = \frac{V_{in}T_s}{I}D(1-2D). \tag{15}$$

for 0 < D < 1/2 and

$$i_{o\_ripple} = \frac{V_{in}T_s}{I_s}(1-D)(2D-1).$$

(16)

for 1/2 < D < 1; the highest  $i_{o\_ripple}$  occurs at D = 1/4 or 3/4. After allowing the highest  $i_{o\_ripple}$  of 1 A at  $P_o = 2$  kW and  $f_s = 20$  kHz (this condition corresponds to THD < 3%), the lower bound of L is obtained using Equations (15) and (16) as

$$L \ge \frac{V_{in}T_s}{8i_{o\_ripple\_max}} \approx 2.5 \text{ mH}. \tag{17}$$

$L_{\min} = 2.5 \text{ mH}$  was used in the experimental inverters to minimize the inductor size.

### 2.3. Controller Design

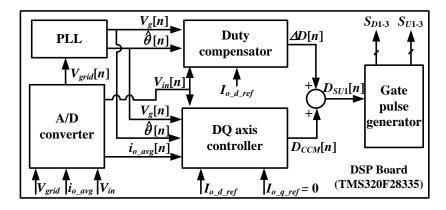

The controller (Figure 5) was designed using Texas Instrument's TMS320F28335 digital signal processor (DSP). This controller inputs  $V_{grid}$ ,  $i_{0\_avg}$ , and  $V_{in}$  and uses the D-Q axis control method [17] to produce gating signals  $S_{U1}-S_{U3}$  and  $S_{D1}-S_{D3}$  that can generate a sinusoidal  $i_{0\_avg}$ . The controller consists of a phase-locked loop (PLL), a D-Q axis controller, and a gate pulse generator. The DSP operates at a clock frequency  $f_{clk}=1/T_{clk}=150$  MHz and the sampling frequency is the same as the switching frequency  $f_s=1/T_s=20$  kHz. Thus, the sampling sequence number n is in the range of  $0 \le n \le 332$  when the grid frequency  $f=\omega/2\pi=60$  Hz, and clock sequence number f is in the range of  $0 \le f \le 7499$ .

Figure 5. Block diagram of the control circuit for the proposed inverter.

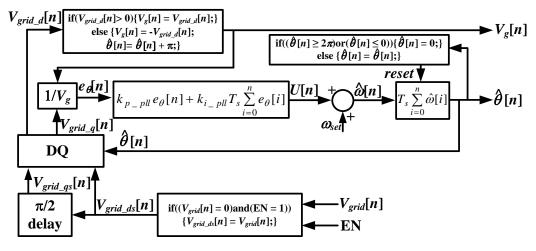

The PLL (Figure 6) sets n=0 and starts to operate when  $V_{grid}=0$  and the enable signal EN = 1. This circuit inputs  $V_{grid}$  and estimates the amplitude  $V_g$  and phase  $\hat{\theta}=\hat{\omega}t$  of  $V_{grid}$ . Using  $V_{grid}[n]=V_g\sin(\theta[n])$ , the PLL generates a virtual grid-voltage  $V_{grid}_{grid}$  as

$$V_{grid\_gs}[n] = V_g \cos(\theta[n]) \tag{18}$$

$\hat{\theta}[0]$  has been set to 0 if  $V_{grid}$ \_qs  $[0] \geq 0$  and to  $\pi$  otherwise. Thus, the initial estimation error  $e_{\theta}[0] = \theta[0] - \hat{\theta}[0]$  is very small.  $V_{grid}$  and  $V_{grid\_qs}$  are transformed into the voltages  $V_{grid\_d}$  and  $V_{grid\_q}$  in the synchronous reference frame as

$$\begin{pmatrix} V_{grid\_d} \\ V_{grid\_q} \end{pmatrix} = \begin{pmatrix} \sin(\hat{\theta}[n]) & \cos(\hat{\theta}[n]) \\ \cos(\hat{\theta}[n]) & -\sin(\hat{\theta}[n]) \end{pmatrix} \begin{pmatrix} V_{grid\_ds} \\ V_{grid\_qs} \end{pmatrix}$$

(19)

Energies **2020**, *13*, 1531 7 of 19

Because

$$V_{grid\_d} = V_g \cos(\theta[n] - \hat{\theta}[n]) \approx V_g$$

(20)

$$V_{grid\_q} = V_g \sin(\theta[n] - \hat{\theta}[n]) \approx V_g(\theta[n] - \hat{\theta}[n])$$

(21)

when  $\hat{\theta}[n] \approx \theta[n]$ ,  $V_g$  and  $e_{\theta}[n] = \theta[n] - \hat{\theta}[n]$  can be calculated using Equations (20) and (21). The PLL loop filter for a proportional-integral (PI) control produces

$$\hat{\theta}[n] = T_s \sum_{m=0}^{n} \left( \omega_{set} + k_{p\_pll} e_{\theta}[m] + k_{i\_pll} T_s \sum_{i=0}^{m} e_{\theta}[i] \right)$$

(22)

This equation is equivalent to

$$\hat{\theta}(s) = \frac{k_p s + k_i}{s^2 + k_p s + k_i} \theta(s) + \frac{\omega_{set}}{s^2 + k_p s + k_i}$$

(23)

in the s-domain, where s is the complex frequency. The final value theory  $\limsup_{s\to 0} \hat{\theta}(s) = \lim_{t\to\infty} \hat{\theta}(t)$  of the Laplace transform yields  $\lim_{t\to\infty} \hat{\theta}(t) = \lim_{t\to\infty} \theta(t)$ , i.e.,  $\hat{\theta}\approx\theta=\omega t$  under steady state. ( $k_p=2000$  and  $k_i=0.1$  have been chosen for the experimental inverter; these values result in at a zero at s=-0.00005 and two poles at  $s\approx-0.00005$  and -2000, so the loop filter operates as a first-order system with a cutoff frequency  $f_c\approx2000/2\pi$  Hz =  $f_s/20\pi\approx5\times60$  Hz.)

Figure 6. Block diagram of the phase locked loop.

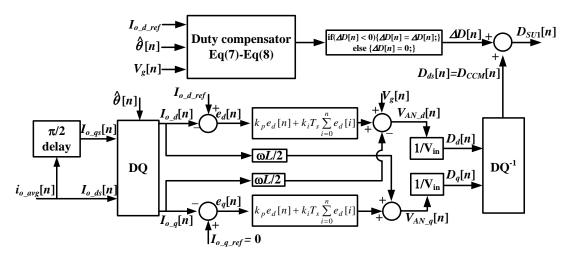

The D-Q axis controller (Figure 7) consists of a CCM duty-calculator and a duty compensator. The CCM duty-calculator inputs  $i_{o\_avg}$  and  $V_{in}$  from the inverter, and  $\hat{\theta}$  and  $V_g$  from the PLL. In the CCM duty-calculator,  $i_{o\_avg} = i_{o\_ds}$  is delayed by  $\pi/2$  to obtain the virtual current  $i_{o\_qs}$  of  $i_{o\_avg}$ . The D-Q transformation separates  $i_{o\_avg}$  into a D component  $I_{o\_d}$  parallel to the grid voltage and a Q component  $I_{o\_q}$  orthogonal to the grid voltage:

$$\begin{pmatrix} I_{o\_d} \\ I_{o\_q} \end{pmatrix} = \begin{pmatrix} \sin(\hat{\theta}[n]) & \cos(\hat{\theta}[n]) \\ \cos(\hat{\theta}[n]) & -\sin(\hat{\theta}[n]) \end{pmatrix} \begin{pmatrix} i_{o\_ds} \\ i_{o\_qs} \end{pmatrix}$$

(24)

For given  $I_{0\_d}$  and  $I_{0\_q}$ , the circuit topology results in the D-Q components of  $V_{AN}$  in the synchronous reference frame as

$$\begin{pmatrix} V_{AN\_d} \\ V_{AN\_q} \end{pmatrix} = \begin{pmatrix} V_g \\ 0 \end{pmatrix} + \frac{\omega L}{2} \begin{pmatrix} -I_{o\_q} \\ I_{o\_d} \end{pmatrix} + \frac{L}{2} \frac{d}{dt} \begin{pmatrix} I_{o\_d} \\ I_{o\_q} \end{pmatrix}, \tag{25}$$

Energies **2020**, *13*, 1531 8 of 19

and the D-Q components of the switching duty as

$$\begin{pmatrix} D_d \\ D_q \end{pmatrix} = \frac{1}{V_{in}} \begin{pmatrix} V_g \\ 0 \end{pmatrix} + \frac{\omega L}{2V_{in}} \begin{pmatrix} -I_{o\_q} \\ I_{o\_d} \end{pmatrix} + \frac{L}{2V_{in}} \frac{d}{dt} \begin{pmatrix} I_{o\_d} \\ I_{o\_q} \end{pmatrix}, \tag{26}$$

because  $V_{AN\_d} = V_{in}D_d$  and  $V_{AN\_q} = V_{in}D_q$ . The D-Q axis controller inputs  $I_{o\_d\_ref}$  and  $I_{o\_q\_ref}$  as the reference values of  $I_{o\_d}$  and  $I_{o\_q}$ , respectively, and calculates the errors  $e_d[n] = I_{o\_d\_ref} - I_{o\_d}$  and  $e_q[n] = I_{o\_q\_ref} - I_{o\_q}$ . Then, the controller generates the D-Q components of the switching duty for CCM operation:

$$\begin{pmatrix} D_{d}[n] \\ D_{q}[n] \end{pmatrix} = \frac{1}{V_{in}} \begin{pmatrix} V_{g} \\ 0 \end{pmatrix} + \frac{\omega L}{2V_{in}} \begin{pmatrix} -I_{o\_q}[n] \\ I_{o\_d}[n] \end{pmatrix} + \frac{k_{p}}{V_{in}} \begin{pmatrix} e_{d}[i] \\ e_{q}[n] \end{pmatrix} + \frac{k_{i}T_{s}}{V_{in}} \sum_{i=0}^{n} \begin{pmatrix} e_{d}[i] \\ e_{q}[i] \end{pmatrix}$$

(27)

Figure 7. Block diagram of the D-Q axis controller.

Both D and Q components have equivalent closed-loop transfer function in the s-domain as

$$\frac{I_{o\_d}(s)}{I_{o\_d\_ref}(s)} = \frac{I_{o\_q}(s)}{I_{o\_q\_ref}(s)} = \frac{k_p s + k_i}{L s^2 + k_p s + k_i} \equiv H(s).$$

(28)

$k_p = 5$  and  $k_i = 25$  have been chosen for the H(s) of the experimental inverter. These values result in a zero at s = -5 and two poles at  $s \approx -5.012$ ,  $s \approx -1944.99$ . The zero at s = -5 is close enough to cancel the pole at  $s \approx -5.012$ ; hence, H(s) operates like a first-order system with a cutoff frequency  $f_c \approx 2000/2\pi$  Hz =  $f_s/20\pi \approx 5 \times 60$  Hz [18].

To operate the inverter with a power factor of 1, the reference inputs must be  $I_{o\_d\_ref} = I_o = 2P_o/V_g$  and  $I_{o\_q\_ref} = 0$ ; therefore,  $I_{o\_d} \to I_{o\_d\_ref} = I_o$  and  $I_{o\_q\_ref} = 0$  under steady state. Thus, the inverse D-Q transform produces the switching duty  $D_{CCM}$  for CCM operation as

$$D_{CCM} = D_{ds} = D_{d}\sin(\omega t) + D_{q}\cos(\omega t) = \frac{V_{g}\sin(\omega t)}{V_{in}} + \frac{\omega LI_{o}\cos(\omega t)}{2V_{in}}$$

(29)

that is given in Equation (8).

Energies **2020**, *13*, 1531 9 of 19

The duty compensator inputs  $V_{in}$  from the inverter,  $\hat{\theta}$  and  $V_g$  from the PLL, and  $I_{o\_d\_ref}$  from CCM duty-calculator. Then, the compensator uses in Equations (7) and (8) to calculate the steady-state duty difference  $\Delta D$  between the switching duties for CCM and DCM operations.  $\Delta D$  is given by

$$\Delta D[n] = \left(\frac{LI_{o\_d\_ref}V_g \sin^2(\hat{\theta}[n])}{V_{in}(V_{in} - 2V_g \sin(\hat{\theta}[n]))T_s} + \left(\frac{\omega LI_{o\_d\_ref} \cos(\hat{\theta}[n])}{4V_{in}}\right)^2\right)^{1/2} - \frac{V_g \sin(\hat{\theta}[n])}{V_{in}} - \frac{\omega LI_{o\_d\_ref} \cos(\hat{\theta}[n])}{4V_{in}}.$$

(30)

The time fraction  $\Delta$  in Equation (5) for which  $i_L \neq 0$  is calculated using Equation (7) as

$$\Delta = \frac{V_{in}}{V_g \sin(\hat{\theta}[n])} \left( \left( \frac{LI_{o\_d\_ref} V_g \sin^2(\hat{\theta}[n])}{V_{in} \left( V_{in} - 2V_g \sin(\hat{\theta}[n]) \right) T_s} + \left( \frac{\omega LI_{o\_d\_ref} \cos(\hat{\theta}[n])}{4V_{in}} \right)^2 \right)^{1/2} + \frac{\omega LI_{o\_d\_ref} \cos(\hat{\theta}[n])}{4V_{in}} \right) - \frac{\omega LI_{o\_d\_ref} \cos(\hat{\theta}[n])}{2V_g \sin(\hat{\theta}[n])} < 1$$

(31)

which yields

$$\sqrt{\frac{LI_{o\_d\_ref}V_g\sin^2(\hat{\theta}[n])}{V_{in}\left(V_{in}-2V_g\sin(\hat{\theta}[n])\right)T_s}} + \left(\frac{\omega LI_{o\_d\_ref}\cos(\hat{\theta}[n])}{4V_{in}}\right)^2 + \frac{\omega LI_{o\_d\_ref}\cos(\hat{\theta}[n])}{4V_{in}} \\

< \frac{V_g\sin(\hat{\theta}[n])}{V_{in}} + \frac{\omega LI_{o\_d\_ref}\cos(\hat{\theta}[n])}{2V_{in}} \tag{32}$$

This equation shows that the switching duty in Equation (7) for DCM operation is always smaller than the one in Equation (8) for CCM operation. Thus, the controller uses  $D_{SU1}[n] = D[n] = D_{CCM}[n] + \Delta D[n]$  when  $\Delta D[n] < 0$ , and the inverter operates in DCM. Otherwise, the controller sets  $\Delta D[n] = 0$ , and the inverter operates in CCM.

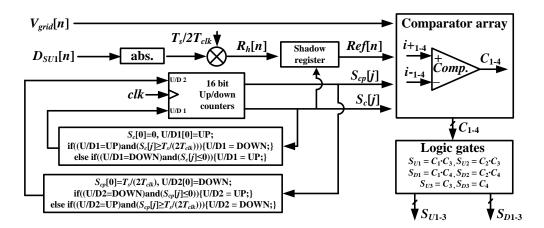

The gate pulse generator (Figure 8) inputs  $D_{SU1}$  form the D-Q axis controller and generates gate pulses for  $S_{U1} - S_{U3}$  and  $S_{D1} - S_{D3}$ . In the gate pulse generator, two saw-tooth-signals  $S_c[j]$  and  $S_{cp}[j]$  are generated using two 16-bit up/down (U/D) counters; at each clock (clk) edge, the outputs  $S_c[j]$  and  $S_{cp}[i]$  of U/D counters increase by 1 when U/D = UP and decrease by 1 when U/D = DOWN. Initial values of saw-tooth signals are Sc[0] = 0, Scp[0] = Ts/(2Tclk), U/D1[0] = UP, and U/D2[0] = DOWN to yield an interleave operation.

Figure 8. Block diagram of the gate pulse generator.

At each clock edge,  $S_c[j]$  increases by 1 for  $nT_s \le t < (n+(1/2))T_s$  during which U/D<sub>1</sub> is UP, and  $S_c[j]$  decreases by 1 for  $(n+(1/2))T_s \le t < (n+1)T_s$  during which U/D<sub>1</sub> is DOWN. When  $S_c[j] < 0$ , U/D<sub>1</sub> changes to UP and the next sequence begins.  $S_{cp}[j]$  decreases by 1 for  $nT_s \le t < (n+(1/2))T_s$  during which U/D<sub>2</sub> is DOWN, and  $S_{cp}[j]$  increases by 1 for  $(n+(1/2))T_s \le t < (n+1)T_s$  during which U/D<sub>2</sub> is UP. U/D<sub>2</sub> changes to DOWN when  $S_{cp}[j] < 0$ , and the next sequence begins. Thus,  $S_{cp}[j]$  is a time-delayed

signal of  $S_c[j]$  by  $T_s/2$ , the maximum values of  $S_c[j]$  and  $S_{cp}[j]$  are  $T_s/(2T_{clk})$ , and the minimum values of  $S_c[j]$  and  $S_{cp}[j]$  are 0. To generate PWM signals using the saw-tooth signals, a reference signal  $R_h[n]$  is generated using  $D_{SU1}$  and  $T_s/(2T_{clk})$  as

$$R_h[n] = \frac{T_s}{2T_{clk}} |D_{SU1}[n]|. (33)$$

$R_h[n]$  is stored in the shadow register of the PWM generation module in TMS320F28335 and transferred to the comparator reference-input Ref[n] when  $S_C[j] = 0$ . Two comparators check the sign of  $V_{grid}[n]$ :  $C_3 = 1$  and  $C_4 = 0$  for  $V_{grid}[n] \ge 0$ , otherwise  $C_3 = 0$  and  $C_4 = 1$  (Table 2). The other comparators output two PWM signals:  $C_1 = 1$  for  $Ref[n] > S_c[j]$  and  $C_2 = 1$  for  $Ref[n] > S_{cp}[j]$ . Finally, the logic gates produce gate control pulses  $S_{U1} = C_1 \cdot C_3$ ,  $S_{U2} = C_2 \cdot C_3$ ,  $S_{U3} = C_3$ ,  $S_{D1} = C_1 \cdot C_4$ ,  $S_{D2} = C_2 \cdot C_4$ , and  $S_{D3} = C_4$ .

| Output         | i + n         | i - n         |

|----------------|---------------|---------------|

| $C_1$          | Ref[n]        | $S_c[j]$      |

| $C_2$          | Ref[n]        | $S_{cp}[j]$   |

| C <sub>3</sub> | $V_{grid}[n]$ | 0             |

| C <sub>4</sub> | 0             | $V_{grid}[n]$ |

**Table 2.** Input and output relationship of comparator array.

# 3. Experimental Results and Discussions

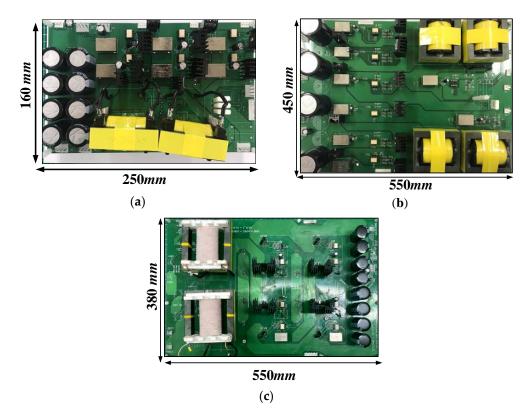

The proposed inverter (Figure 9a, Table 3) was designed to operate at  $V_{in} = 400 \text{ V}_{DC}$ ,  $V_{grid} = 220 \text{ V}_{AC}/60 \text{ Hz}$  and  $150 \text{ W} \leq P_o \leq 2 \text{ kW}$ , and it was fabricated and tested using the calculated circuit parameters. An IDBI [9] (Figure 9b, Table 3) and an FBI [1] (Figure 9c, Table 3) were also fabricated and tested for comparison; the circuit elements for these inverters were the same as those for the proposed inverter. The control circuits for all experimental inverters were implemented using the TMS320F28335 digital signal processor (DSP) from Texas Instruments.

| Compo                     | onents     | IDBI [9]                                    | FBI                 | Proposed Inverter                           |

|---------------------------|------------|---------------------------------------------|---------------------|---------------------------------------------|

| HF Switches               | Name       | FCH110N65F                                  | FCH110N65F          | FCH110N65F                                  |

|                           | Price (\$) | 5.03                                        | 5.03                | 5.03                                        |

|                           | Number     | $4\left(S_{U1},S_{U3},S_{D1},S_{D2}\right)$ | $4(S_1 - S_4)$      | $4\left(S_{U1},S_{U3},S_{D1},S_{D2}\right)$ |

| LF Switches               | Name       | IXFK80N60P3                                 | -                   | IXFK80N60P3                                 |

|                           | Price (\$) | 5.03                                        | -                   | 5.03                                        |

|                           | Number     | $2(S_{U3}, S_{D3})$                         | -                   | $2(S_{U3}, S_{D3})$                         |

| Diodes                    | Name       | 30ETH06                                     | -                   | 30ETH06                                     |

|                           | Price (\$) | 1.59                                        | -                   | 1.59                                        |

|                           | Number     | $4\left(D_{U1},D_{U2},D_{D1},D_{D2}\right)$ | -                   | $6\left(D_{U1}-D_{U3},D_{D1}-D_{D3}\right)$ |

| Inductor core             | Part Name  | EER6062                                     | EC90                | EER6062                                     |

|                           | Price (\$) | 4.94                                        | 16.17               | 4.94                                        |

|                           | Number     | 4                                           | 2                   | 2                                           |

| Electrolytic<br>capacitor | Part Name  | EKMR451VS N681MA50S                         | EKMR451VS N681MA50S | EKMR451VS N681MA50S                         |

|                           | Price (\$) | 2.68                                        | 2.68                | 2.68                                        |

|                           | Number     | 8                                           | 8                   | 8                                           |

| Total costs (\$)          |            | 77.74                                       | 73.9                | 71.04                                       |

Table 3. Components for the experimental inverters.

**Figure 9.** Photographs of the experimental inverters: (**a**) proposed inverter, (**b**) interleaved dual buck inverter (IDBI), and (**c**) full bridge inverter (FBI).

The proposed inverter uses two inductors, whereas the IDBI uses four inductors, and the proposed inverter uses a small inductor core (EER6062), whereas the FBI uses a large inductor core. The fabricated inverters had a circuit volume of  $160 \text{mm} \times 250 \text{ mm} \times 43.9 \text{ mm}$  for the proposed inverter,  $450 \text{ mm} \times 550 \text{ mm} \times 43.9 \text{ mm}$  for the IDBI, and  $380 \text{mm} \times 550 \text{ mm} \times 78.0 \text{ mm}$  for the FBI; the proposed inverter reduced 83.8% of the circuit volume compared with the IDBI, and 89.3% compared with the FBI. The circuit cost was \$71.04 for the proposed inverter, \$77.74 for the IDBI, and \$73.9 for the FBI; the proposed inverter saved 8.62% of the circuit cost compared with the IDBI, and 3.87% compared with FBI.

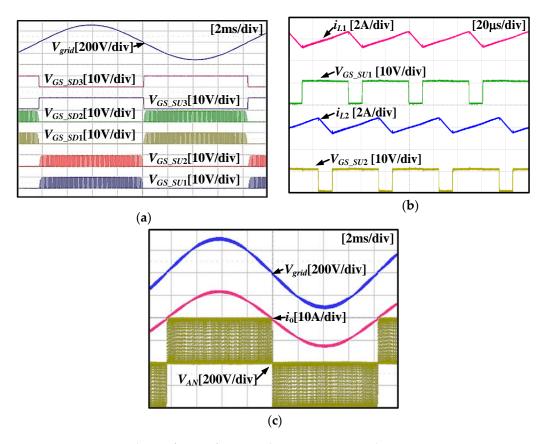

To verify operation of the proposed inverter, the waveforms of switch-control pulses (Figure 10a) were measured at Vin = 400 VDC,  $V_{grid}$  = 220  $V_{AC}/60$  Hz,  $P_o$  = 2 kW, and  $f_s$  = 20 kHz. These waveforms show that the switches operated according to the switching states in Table 1; when  $V_{grid}$  > 0 V,  $S_{U1}$  and  $S_{U2}$  operated in PWM mode,  $S_{U3}$  stayed ON and other switches stayed OFF; when  $V_{grid}$  < 0 V,  $S_{D1}$  and  $S_{D2}$  operated in PWM mode,  $S_{D3}$  stayed ON and other switches stayed OFF. The inductor currents  $i_{L1}$  and  $i_{L2}$ , and the leg voltages  $V_{GS\_SU1}$  and  $V_{GS\_SU2}$  (Figure 10b) show that the inverter operated in an interleaved mode; the phase differences between  $i_{L1}$  and  $i_{L2}$ , and between  $V_{GS\_SU1}$  and  $V_{GS\_SU2}$  were  $T_s/2$ . These switching states produced the sinusoidal leg voltage  $V_{AN}$  (Figure 10c).

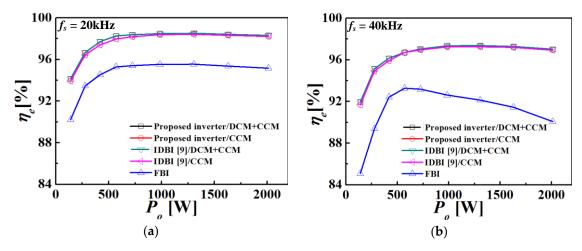

$\eta_e$  vs.  $P_o$  (Figure 11) was measured at  $V_{in}=400~{\rm V_{DC}}$ ,  $V_{grid}=220~{\rm V_{AC}}/60~{\rm Hz}$ ,  $150~{\rm W} \le P_o \le 2~{\rm kW}$ , and  $f_s=20~{\rm kHz}$  and 40 kHz, using a PW3336 (HIOKI E.E. Co.) power meter. At  $f_s=20~{\rm kHz}$ , the proposed inverter had  $\eta_e > 98\%$  for  $P_o \ge 500~{\rm W}$ , but  $\eta_e$  for  $P_o < 500~{\rm W}$  decreased as  $P_o$  decreased because the inverter operated in DCM. The highest power conversion efficiency  $\eta_{emax}$  of the proposed inverter was 98.5% at  $P_o=1300~{\rm W}$  when the power loss  $P_{DSP}$  of the gate control/drive circuit was included. ( $\eta_{emax}=99.2\%$  at  $P_o=500~{\rm W}$  when  $P_{DSP}$  was excluded.) The FBI does not use the interleaved buck inversion; hence, the switching and conduction losses in the current path were higher in the FBI than in the proposed inverter; as a result, the FBI had the lowest  $\eta_e$  among the inverters tested. The IDBI has a circuit structure similar to the proposed inverter and operates in interleaved mode, so  $\eta_e$  of the IDBI was very close to that of the proposed inverter. However, the proposed inverter requires two

inductors to operate the inverter in interleaved mode, while the IDBI requires four inductors; hence, the proposed inverter can be implemented in a smaller size.

**Figure 10.** Experimental waveforms of proposed inverter, measured at  $V_{in} = 400 \text{ V}_{DC}$ ,  $V_{grid} = 220 \text{ V}_{AC}/60 \text{ Hz}$ ,  $f_s = 20 \text{ kHz}$ , and  $P_o = 2 \text{ kW}$ : (a) gate input pulses, (b)  $V_{GS\_SU1}$ ,  $V_{GS\_SU2}$ ,  $i_{L1}$ , and  $i_{L2}$ , and (c)  $i_o$ ,  $V_{AN}$ , and  $V_{grid}$ .

**Figure 11.**  $\eta_e$  vs.  $P_o$  for the experimental inverters operating at (a)  $f_s = 20$  kHz and (b)  $f_s = 40$  kHz: measured at  $V_{in} = 400$  V<sub>DC</sub>,  $V_{grid} = 220$  V<sub>AC</sub>/60 Hz, and  $Q_o = 0$  VAR. The power loss  $P_{DSP}$  in the control circuit was included in  $\eta_e$  measurement.

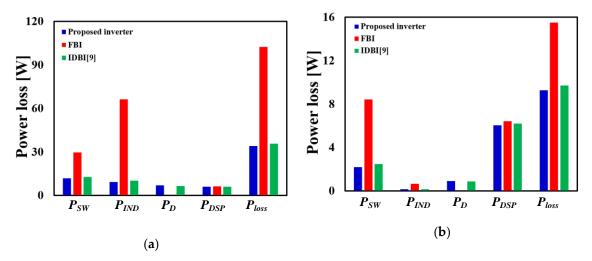

Losses (Figure 12) of the experimental inverters were analyzed at  $V_{in}$  = 400 V<sub>DC</sub>,  $V_{grid}$  = 220 V<sub>AC</sub>/60 Hz,  $f_s$  = 20 kHz,  $P_o$  = 2 kW and 150 W, and reactive output power  $Q_o$  = 0 volt-ampere-reactive (VAR). The switching losses  $P_{SW}$  were 13.2 W for proposed, 13.89 W for IDBI,

and 29.71 W for FBI at  $P_o = 2$ kW, and  $P_{SW}$  were 2.18 W for proposed, 2.48 W for IDBI, and 8.42 W for FBI at  $P_o = 150$  W. The inverters operated at  $V_{SW} = V_{in}$  and  $N_{SW} = 666$  for proposed and IDBI, and  $V_{SW} = V_{in}$  and  $N_{SW} = 1333$  for FBI, where  $N_{SW}$  is the total switching number for one cycle of  $V_{grid}$ . Thus, the proposed inverter and IDBI had the lowest  $P_{SW}$ . The inductor loss  $P_{IND}$  was 9.25 W for proposed, 10.33 W for IDBI, and 66.32 W for FBI at  $P_o = 2$ kW and 0.155 W for proposed, 0.162 W for IDBI, and 0.66 W for FBI at  $P_o = 150$  W. The proposed inverter uses interleaved inputs; hence, the inductor current  $i_L$  is half of the  $i_L$  of FBI. Moreover, the proposed inverter uses small inductors with fewer turns than that of the FBI. Thus, FBI had the highest  $P_{IND}$ . The diode loss  $P_D$  was 7.04 W for proposed, 6.45 W for IDBI, and 0 for FBI at  $P_o = 2$  kW, and  $P_D$  was 0.907 W for proposed, 0.885 W for IDBI, and 0 for FBI at  $P_o = 150$  W. The power loss  $P_{DSP}$  of the gate control/drive circuit was 6.02 W for proposed, 6.19 W for IDBI, and 6.48 W for FBI at both  $P_o = 150$  W and  $P_o = 2$  kW. The total power loss  $P_{loss}$  at  $P_o = 2$  kW was 35.53 W for proposed, 36.87 W for IDBI, and 102.51 W for FBI, and the power conversion efficiency  $\eta_e$  at  $P_o = 2$  kW was 98.2% for proposed, 98.1% for IDBI, and 94.9 % for FBI.  $P_{loss}$  at  $P_o = 150$ W was 9.279 W for proposed, 9.717 W for IDBI, and 15.5 W for FBI, and  $\eta_e$  at  $P_o = 150$  W was 93.8% for proposed, 93.5% for IDBI, and 89.6 % for FBI.

**Figure 12.** Power losses in the experimental inverters at (a)  $P_o = 2$  kW and (b)  $P_o = 150$ W: calculated using PSPICE at  $V_{in} = 400$  V<sub>DC</sub>,  $V_{grid} = 220$  V<sub>AC</sub> / 60 Hz,  $f_s = 20$  kHz, and  $Q_o = 0$  VAR.

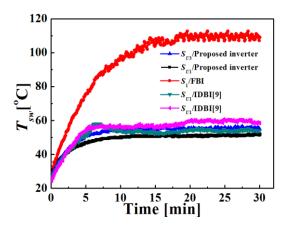

The temperature  $T_{SW}$  of switch vs. time of operation (Figure 13) was measured while operating the experimental inverters at  $V_{in} = 400 \text{ V}_{DC}$ ,  $V_{grid} = 220 \text{ V}_{AC}/60 \text{ Hz}$ ,  $P_o = 2 \text{ kW}$ , and  $f_s = 20 \text{ kHz}$ .  $T_{SW}$  was stabilized at ~52 °C ( $S_{U1}$ ,  $S_{U2}$ ,  $S_{D1}$ ,  $S_{D2}$ ) and ~55 °C ( $S_{U3}$ ,  $S_{D3}$ ) in the proposed inverter, ~54 °C ( $S_{U1}$ ,  $S_{U2}$ ,  $S_{D1}$ ,  $S_{D2}$ ) and ~58 °C ( $S_{U3}$ ,  $S_{D3}$ ) in the IDBI, and at ~110 °C in FBI.  $P_{SW}$  at  $P_o = 2 \text{ kW}$  were 13.2 W for proposed, 13.89W for IDBI, and 29.71 W for FBI; therefore,  $T_{SW}$  of the proposed inverter and IDBI was half that of FBI.

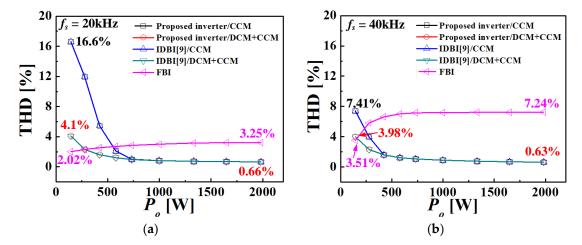

THD of  $i_0$  vs.  $P_0$  (Figure 14) was also measured at  $V_{in} = 400 \, \text{V}_{DC}$ ,  $V_{grid} = 220 \, \text{V}_{AC}/60 \, \text{Hz}$ ,  $P_0 = 150 \, \text{W}$  ~ 2 kW, and  $f_s = 20 \, \text{kHz}$ . THD at  $P_0 = 2 \, \text{kW}$  was 0.66% for proposed and IDBI and 3.25% for FBI; FBI had the highest THD because this inverter produced a ZCD during the dead-time period. THD at  $P_0 = 150 \, \text{W}$  was 16.6% for IDBI and the proposed inverter when the switching duties for the inverters were controlled using the CCM control (given in (8)). At a low  $P_0$ , the proposed inverter operated in DCM for some time-interval of sinusoidal  $V_{grid}$ , as discussed in Section 2.2. This operation produced a distortion in  $I_0$  when the inverters were operated under CCM control only.

When the switching duties for IDBI and the inverters were controlled using the proposed DCM+CCM control (a combination of the CCM control and the DCM control given in Equation (7)), the THD at  $P_0 = 150$  W was reduced to 4.1% because the combined DCM+CCM control reduced the distortion in  $I_0$  significantly.

Energies **2020**, 13, 1531 14 of 19

**Figure 13.** Switch temperature  $T_{SW}$  vs. time of operation, measured at  $V_{in} = 400 \text{ V}_{DC}$ ,  $V_{grid} = 220 \text{ V}_{AC}/60 \text{ Hz}$ ,  $f_s = 20 \text{ kHz}$ ,  $P_o = 2 \text{ kW}$ , and  $Q_o = 0 \text{ VAR}$ .

**Figure 14.** Total harmonic distortion (THD) of  $i_0$  vs.  $P_0$  for the experimental inverters operating at (a)  $f_s = 20$  kHz and (b)  $f_s = 40$  kHz: measured at  $V_{in} = 400$  V<sub>DC</sub> and  $V_{grid} = 220$  V<sub>AC</sub>/60 Hz.

When  $f_s$  was increased to 40 kHz, THD of  $i_0$  at  $P_o = 2$  kW was 0.63% for proposed and IDBI and 7.24% for FBI. The FBI nearly doubled the THD at  $f_s = 40$  kHz compared to the value at  $f_s = 20$  kHz, because the change increased the effect of dead-time on the switching duty. The THD at  $P_o = 150$  W was 7.41% for the proposed inverter using CCM control, 3.98% for the proposed inverter using DCM+CCM control, and 3.51% for FBI. The DCM operating time was reduced at higher  $f_s$  (Equations (9) and (10)); hence, THD of the proposed inverter decreased as  $f_s$  increased; a DCM control near the zero crossing point increased  $i_L$ . In contrast, the THD for FBI increased as  $f_s$  increased because the impact of dead-time on the switching duty increased.

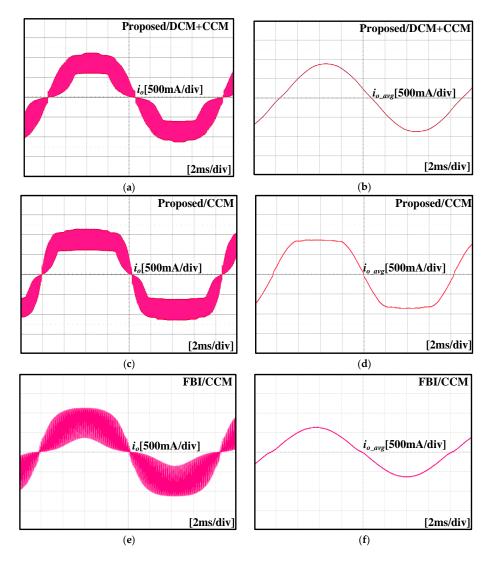

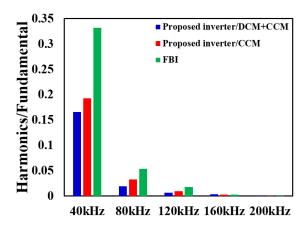

The waveforms of  $i_0$  and  $i_{0\_avg}$  for the experimental inverters (Figure 15) were measured at  $V_{in} = 400 \text{ V}_{DC}$ ,  $V_{grid} = 220 \text{ V}_{AC}/60 \text{ Hz}$ ,  $f_s = 20 \text{ kHz}$ ,  $P_0 = 150 \text{ W}$ ,  $Q_0 = 0 \text{ VAR}$ , and  $I_0 = 0.95 \text{ A}$ . The cutoff frequency of the low-pass filter for  $i_{0\_avg}$  measurement was 2 kHz (= $f_s$ /10). The inverters were controlled using CCM or DCM+CCM control. The waveforms of  $i_0$  show that the proposed inverter had the lowest switching ripple of  $i_0$ , and the waveforms of  $i_{0\_avg}$  show that the DCM+CCM control of the proposed inverter achieved the best sinusoidal waveform. The harmonic components of  $i_0$  (Figure 16) show that harmonics of  $i_0$  of FBI were slightly higher than those of the proposed inverter because the proposed inverter operated as an interleaved dual buck inverter.

**Figure 15.** Waveforms of  $i_0$  and  $i_{o\_avg}$  measured at at  $V_{in} = 400 \text{ V}_{DC}$ ,  $V_{grid} = 220 \text{ V}_{AC}$  / 60 Hz,  $f_0 = 20 \text{ kHz}$ ,  $P_0 = 150 \text{ W}$ ,  $Q_0 = 0 \text{ VAR}$ , and  $I_0 = 0.95 \text{ A}$ : (a)  $i_0$  (Proposed, DCM+CCM), (b)  $i_{o\_avg}$  (Proposed, DCM+CCM), (c)  $i_0$  (Proposed, CCM), (d)  $i_{o\_avg}$  (Proposed, CCM), (e)  $i_0$  (FBI, CCM), (f)  $i_{o\_avg}$  (FBI, CCM).

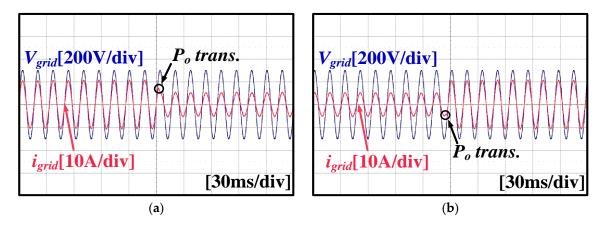

The dynamic responses of the proposed inverter (Figure 17) were measured for a step change of  $P_o$  from 2 kW to 1 kW and a step change of  $P_o$  from 1 kW to 2 kW; the operating conditions for this measurement were  $V_{in} = 400 \text{ V}_{DC}$ ,  $V_{grid} = 220 \text{ V}_{AC}/60 \text{ Hz}$ ,  $f_s = 20 \text{ kHz}$ , and  $Q_o = 0 \text{ VAR}$ . For both  $P_o$  changes, the output current  $i_o$  did not overshoot, and the transient time of  $i_o$  was < 2 ms, which is ~1/8 of the sinusoidal period at 60 Hz. PF, THD, and  $i_o$  of the proposed inverter were measured for  $P_o = 666.6 \text{ W}$ , 1.333 kW, and 2 kW at  $V_{in} = 400 \text{ V}_{DC}$ ,  $V_{grid} = 220 \text{ V}_{AC}/60 \text{ Hz}$ ,  $f_s = 20 \text{ kHz}$ , and line impedance  $Z = 0.4 + j0.25 \Omega$ . The measured PF was 0.9973 at  $P_o = 666.6 \text{ W}$  (33% of the rated power), 0.9985 at  $P_o = 1.333 \text{ kW}$  (66% of the rated power), and 0.9992 at  $P_o = 2 \text{ kW}$  (100% of the rated power). The measured THD of  $i_o$  was 4.20% at  $P_o = 666.6 \text{ W}$ , 3.68% at  $P_o = 1.333 \text{ kW}$ , and 3.43% at  $P_o = 2 \text{ kW}$ . These results fulfill most grid-connected inverter standards for renewable energy [19–22].

Comparisons (Table 4) of the circuit parameters and experimental results demonstrate the superiority of the proposed inverter. The proposed inverter has the following advantages: (1) proposed inverter requires two inductors, whereas IDBI requires four inductors; hence, the proposed inverter can be implemented with lower cost and smaller volume than IDBI; (2) it uses interleaved operation, which reduces the current stress of the switch by 1/2 of that in FBI; (3) the number of switching for one period of  $V_{grid}$  in the proposed inverter is 1/2 of that in FBI; hence, the switching loss is reduced; and

(4)  $\eta_e$  at  $P_o$  = 2 kW is as high as 98.3%, compared to 95.0% for FBI. These advantages indicate that the proposed inverter is useful for high-power dc-ac power conversion.

**Figure 16.** Harmonic components of  $i_0$ ; measured at  $V_{in} = 400 \text{ V}_{DC}$ ,  $V_{grid} = 220 \text{ VAC/60 Hz}$ ,  $f_s = 20 \text{ kHz}$ ,  $P_0 = 150 \text{ W}$ ,  $Q_0 = 0 \text{ VAR}$ , and  $I_0 = 0.95 \text{ A}$ .

**Figure 17.** Step responses of the proposed inverter at  $V_{in} = 400 \text{ V}_{DC}$ ,  $V_{grid} = 220 \text{ VAC/60 Hz}$ ,  $f_s = 20 \text{ kHz}$ , and  $Q_o = 0 \text{ VAR}$ : (a) for a decrease of  $P_o$  from 2 kW to 1 kW and (b) for an increase of  $P_o$  from 1 kW to 2 kW.

**Table 4.** Circuit parameters and experimental results for experimental inverters. Parenthesis contain peak switch voltages and currents measured at  $V_{\rm in} = 404$  V.

| Circuit I           | Parameters              | Proposed Inverter                                    | IDBI [9]                                                      | FBI                          |

|---------------------|-------------------------|------------------------------------------------------|---------------------------------------------------------------|------------------------------|

| # of s              | witches                 | 6                                                    | 6                                                             | 4                            |

| # of 0              | diodes                  | 6                                                    | 4                                                             | 0                            |

| # of in             | ductors                 | 2                                                    | 4                                                             | 2                            |

| V <sub>sw,max</sub> | Unfolding<br>Switching  | V <sub>in</sub> (404 V)<br>V <sub>in</sub> (413 V)   | V <sub>in</sub> (404 V)<br>V <sub>in</sub> (415 V)            | -<br>V <sub>in</sub> (423 V) |

| I <sub>sw,max</sub> | Unfolding<br>Switching  | I <sub>o</sub> (13.1 A)<br>I <sub>o</sub> /2 (5.8 A) | <i>I<sub>o</sub></i> (13.5 A) <i>I<sub>o</sub></i> /2 (6.0 A) | -<br>I <sub>o</sub> (13.5 A) |

| Indu                | ctance                  | 2.5 mH                                               | 2.5 mH                                                        | 2.5 mH                       |

| THD at 1            | $P_0 = 2 \text{ kW}$    | 0.66%                                                | 0.66%                                                         | 3.25%                        |

| Maximur             | n efficiency            | 98.5%                                                | 98.4%                                                         | 95.2%                        |

| Efficiency a        | at $P_0 = 2 \text{ kW}$ | 98.3%                                                | 98.2%                                                         | 95.0%                        |

Energies **2020**, 13, 1531 17 of 19

#### 4. Conclusions

This paper proposes an inverter that can achieve high power conversion efficiency  $\eta_e$  at high output power  $P_o$ . The inverter uses a dual-buck structure to eliminate zero-cross distortion, operates in an interleaved mode to reduce the current stress of switch, and uses DCM + CCM combined control to reduce the output current distortion at low output power. The size and weight of the circuit are reduced by decreasing the number of inductors and by using blocking diodes; the proposed inverter could reduce 83.8% of the circuit volume compared with IDBI and 89.3% compared with FBI, and it could save 8.62% of the circuit cost compared with IDBI and 3.87% compared with FBI. When the experimental inverter was operated at an input voltage of 400  $V_{DC}$ , an output voltage of 220  $V_{AC}/60$  Hz, and switching frequency of 20 kHz,  $\eta_e$  was > 94% at 150 W  $\leq P_o \leq$  2 kW, 98.5% at  $P_o =$  1300 W, and 98.3% at  $P_o =$  2 kW. The total harmonic distortion was 0.66% at  $P_o =$  2kW. The proposed inverter is well-suited for high power dc-ac power conversion.

**Author Contributions:** M.-G.C. developed the circuit, constructed the hardware prototype, and conducted the experiments. B.K. provided guidance and key suggestions for this study. S.-H.L., H.-S.L., and Y.-G.C. collected the data and investigated early works. All authors have read and agreed to the published version of the manuscript.

**Funding:** This research was supported by the Ministry of Science and ICT(MSIT), Korea, under the "ICT Consilience Creative program" (IITP-2019-2011-1-00783) supervised by the Institute for Information & Communications Technology Planning & Evaluation (IITP).

Conflicts of Interest: The authors declare no conflict of interest.

#### Nomenclature

$C_1 - C_4$  Output of comparators in the PWM generator. D Switching duty of the proposed inverter.  $D_d$  Amplitude of  $D_{SU1}$  parallel to  $V_{grid}$ .

$D_{D1}$ ,  $D_{D2}$  Low-side freewheeling diodes of the proposed inverter and IDBI [9].

$D_q$  Amplitude of  $D_{SU1}$  orthogonal to  $V_{grid}$ .  $D_{SU1}$  Switching duty of  $S_{U1}$  in the proposed inverter.

$D_{U1}$ ,  $D_{U2}$  High-side freewheeling diodes of the proposed inverter and IDBI [9].

$D_{U3}$ ,  $D_{D3}$  Blocking diodes of the proposed inverter.

$e_d, e_q$  Control errors of  $I_{o\_d}$  and  $I_{o\_q}$  in the D-Q axis controller (A). Estimation error of  $\hat{\theta}$  in the phased locked loop (rad).

$f_{clk}$ ,  $T_{clk}$  Clock frequency (Hz), and period (s) of TMS320F28335 digital signal processor.

$f_s$ ,  $T_s$  Switching frequency (Hz) and period (s).  $i_{L1}$ ,  $i_{L2}$  Inductor currents of the proposed inverter (A).

$i_{L1\_avg}$ ,  $i_{L2\_avg}$  Time average of  $i_{L1}$  and  $i_{L2}$  of the proposed inverter (A).

$I_o$  Amplitude of  $i_{o\_avg}$  (A).

$i_{o\_avg}$  Time averaged value of the output current  $i_o$  for one switching period (A).

$I_{o\_d}$  Amplitude of  $i_{o\_avg}$  parallel to  $V_{grid}$  (A).

$I_{o\_d\_ref}, I_{o\_q\_ref}$  Reference values of  $I_{o\_d}$  and  $I_{o\_d}$  for the D-Q axis controller (A).

$I_{o\_q}$  Amplitude of  $i_{o\_avg}$  orthogonal to  $V_{grid}$  (A).

$i_{o\_ripple}$  Ripple in output current of the proposed inverter (A).  $k_p, k_i$  Control coefficients 94768 for the D-Q axis controller.  $k_{p\_pll}, k_{i\_pll}$  Control coefficients for the phased locked loop.

$L_1, L_2$  Output filter inductors (H).

*n*, *j* Sampling and clock sequence numbers.

Ref Reference input for the comparator array in the PWM generator.

$S_1 - S_4$  High frequency switches of FBI [1].

$S_c$ ,  $S_{cp}$  Counter outputs for PWM.

$S_{D1}$ ,  $S_{D2}$  Low-side high frequency switches of the proposed inverter and IDBI [9].  $S_{D3}$  Low-side unfolding switch of the proposed inverter and IDBI [9].  $S_{U1}$ ,  $S_{U2}$  High-side high frequency switches of the proposed inverter and IDBI [9].  $S_{U3}$  High-side unfolding switch of the proposed inverter and IDBI [9].

Energies **2020**, 13, 1531 18 of 19

$T_{sw}$  Temperature of switches (°C).

$V_{AN}$  Leg voltage with respect to the ground (V).

$V_{AN\_avg}$  Time averaged value of  $V_{AN}$  for one switching period (V).

$V_{AN\_d}$  Amplitude of  $V_{AN\_avg}$  parallel to  $V_{grid}$  (V).  $V_{AN\_q}$  Amplitude of  $V_{AN\_avg}$  orthogonal to  $V_{grid}$  (V).

$V_g$  Amplitude of  $V_{grid}$  (V).

$V_{grid}$  AC output voltage (AC grid voltage) (V).

$V_{in}$  DC input voltage (V).

$V_{L1}$ ,  $V_{L2}$  Voltages across the output filter inductors  $L_1$  and  $L_2$  (V).

$V_{L1\_avg}$ ,  $V_{L2\_avg}$  Time averaged values of  $V_{L1}$  and  $V_{L2}$  for one switching period (V).  $\Delta D$  Difference of switching duties for CCM and DCM operations.

$\Delta T_s$  Duration of  $i_{L1}(t) \neq 0$  for one switching period (s).

$\theta$  Phase angle of  $V_{qrid}$  (rad).

$\begin{array}{ll} \hat{\theta} & \text{Estimated } \theta \text{ by the phased locked loop (rad).} \\ \eta_e & \text{Power conversion efficiency of inverters.} \\ \omega & \text{Angular frequency of } V_{grid} \text{ (rad/s).} \\ \omega_{set} & \text{Nominal value of } \omega \text{ (rad/s).} \\ \end{array}$

#### References

1. Mazumder, S.K.; Nayfeh, A.H.; Boroyevich, D. Theoretical and experimental investigation of the fast—and slow-scale instabilities of a DC–DC converter. *IEEE Trans. Power Electron.* **2001**, *16*, 201–216. [CrossRef]

- 2. Hwang, S.; Kim, J. Dead time compensation method for voltage-fed PWM inverter. *IEEE Trans. Energy Convers.* **2010**, 25, 1–10. [CrossRef]

- Herran, M.A.; Fischer, J.R.; Gonzalez, A.; Judewicz, M.G.; Carrica, D.O. Adaptive dead-time compensation for grid-connected PWM inverters of single-stage PV systems. *IEEE Trans. Power Electron.* 2013, 28, 2816–2825.

[CrossRef]

- 4. Kang, F.S.; Park, S.-J.; Cho, S.E.; Kim, C.U.; Ise, T. Multilevel PWM inverters suitable for the use of stand-alone photovoltaic power systems. *IEEE Trans. Energy Convers.* **2005**, *20*, 906–915. [CrossRef]

- 5. Zhou, J.; Huang, C.; Cheng, C.; Zhao, F. A Comprehensive Analytical Study of Dielectric Modulated Drift Regions—Part I: Static Characteristics. *IEEE Trans. Electron. Devices* **2016**, *63*, 2255–2260. [CrossRef]

- 6. Araújo, S.V.; Zacharias, P.; Mallwitz, R. Highly Efficient Single-Phase Transformerless Inverters for Grid-Connected Photovoltaic Systems. *IEEE Trans. Ind. Electron.* **2010**, *57*, 3118–3128. [CrossRef]

- 7. Yao, Z.; Xiao, L.; Yan, Y. Control strategy for series and parallel output dual-buck half bridge inverters based on DSP control. *IEEE Trans. Power Electron.* **2009**, *24*, 434–444.

- 8. Liu, J.; Yan, Y. A Novel Hysteresis Current Controlled Dual Buck Half Bridge Inverter. In Proceedings of the IEEE 34th Annual Conference on Power Electronics Specialists (PESC), Acapulco, Mexico, 15–19 June 2003; IEEE: Piscataway, NJ, USA, 2003; pp. 1615–1620.

- 9. Hong, F.; Liu, J.; Ji, B.; Zhou, Y.; Wang, J. Interleaved Dual Buck Full-Bridge Three-Level Inverter. *IEEE Trans. Power Electron.* **2016**, 31, 964–974. [CrossRef]

- Zhou, L.W.; Gao, F. Dual Buck Inverter with Series Connected Diodes and Single Inductor. In Proceedings of the 2016 IEEE Applied Power Electronics Conference and Exposition (APEC), Long Beach, CA, USA, 21 March 2016; IEEE: Piscataway, NJ, USA, 2016; pp. 2259–2263.

- 11. Hong, F.; Liu, J.; Ji, B.; Zhou, Y. Single Inductor Dual Buck Full-Bridge Inverter. *IEEE Trans. Ind. Electron.* **2015**, *62*, 4869–4877. [CrossRef]

- 12. Zhou, L.; Gao, F. Improved Transformerless Dual Buck Inverters with Buffer Inductors. In Proceedings of the 2016 IEEE Applied Power Electronics Conference and Exposition (APEC), Long Beach, CA, USA, 21 March 2016; IEEE: Piscataway, NJ, USA, 2016; pp. 2935–2941.

- 13. Yang, M.K.; Kim, Y.J.; Choi, W.Y. Power Efficiency Improvement of Dual-Buck Inverter with SiC Diodes using Coupled Inductors. In Proceedings of the 2018 IEEE 6th Workshop on Wide Bandgap Power Devices and Applications (WiPDA), Atlanta, GA, USA, 31 October–2 November 2018; pp. 56–59.

- 14. Nguyen, T.T.; Cha, H.Y.; Nguyen, B.L.; Kim, H.G. A Novel Single-Phase Three-Level Dual-Buck Inverter. *IEEE Trans. Power Electron..* (accepted). [CrossRef]

15. Kow, B.; Wei, J.; Zhang, L. Switching and Conduction Losses Reduction of Dual Buck Full Bridge Inverter through ZVT Soft-Switching under Full-Cycle Modulation. *IEEE Trans. Power Electron.*. (accepted).

- 16. Johnson, J. Improving Buck Converter Light-Load Efficiency. Power Electron. Eur. 2015, 5, 17–18.

- 17. Zhang, R.; Cardinal, M.; Szczesny, P.; Dame, M. A grid simulator with control of single-phase power converters in D-Q rotating frame. In Proceedings of the 2002 IEEE 33rd Annual IEEE Power Electronics Specialists Conference (PESC), Cairns, QLD, Australia, 23–27 June 2002; pp. 1431–1436.

- 18. Nise, N.S. Chapter 4, Time response. In *Control System Engineering*, 4th ed.; Dumas, S., Kulesa, T., Sayre, D., Eds.; John Wiley & Sons, Inc.: Hoboken, NJ, USA, 2004; Volume 1, pp. 198–201.

- 19. VDE Association for Electrical Electronic and Information Technologies. *VDE-AR-N* 4105:2011-08 Power Generation Systems Connected to the Low-Voltage Distribution Network; VDE Association for Electrical, Electronic and Information Technologies: Frankfurt, Germany, 2011.

- 20. IEEE Standards Association. *IEEE 1547 Standard for Interconnecting Distributed Resources with Electric Power Systems*; IEEE Standards Association: Piscataway, NJ, USA, 2003.

- 21. Korean Agency for Technology and Standards. SGSF-04-2012-07 General Performance Requirements of PCS (Power Conditioning System) for Energy Storage Systems; Smart Grid Standardization Forum: Seoul, Korea, 2012.

- 22. Operation Directorate of Energy Network Association. *Engineering Recommendation G83, Issue 2;* Energy Networks Association: London, UK, 2012.

© 2020 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).