Article

# Voltage Balance Switching Scheme for Series-Connected SiC MOSFET LLC Resonant Converter

Hwa-Rang Cha and Rae-Young Kim \*

The Department of Electrical and Biomedical Engineering, Hanyang University, Seoul 04763, Korea; hrcha33@hanyang.ac.kr

\* Correspondence: rykim@hanyang.ac.kr; Tel.: +82-2-2220-2897

Received: 30 September 2019; Accepted: 20 October 2019; Published: 21 October 2019

Abstract: To achieve high efficiency and power density, silicon carbide (SiC)-based Inductor-Inductor-Capacitor (LLC) resonant converters are applied to the DC/DC converter stage of a solid-state transformer (SST). However, because the input voltage of an SST is higher than the rated voltage of a commercial SiC device, it is essential to connect SiC devices in series. This structure is advantageous in terms of voltage rating, but a parasitic capacitance tolerance between series-connected SiC devices causes voltage imbalance. Such imbalance greatly reduces system stability as it causes overvoltage breakdown of SiC device. Therefore, this paper proposes a switching scheme to solve the voltage imbalance between SiC metal-oxide-semiconductor field-effect transistors (MOSFETs). The proposed scheme sequentially turns off series-connected SiC MOSFETs to compensate for the turn-off delays caused by parasitic capacitor tolerances. In addition, dead-time selection methods to achieve voltage balance and zero voltage switching simultaneously are provided in detail. To verify the effectiveness of the proposed scheme, experiments were conducted on a 2 kW series-connected SiC MOSFET LLC resonant converter prototype.

**Keywords:** series-connected SiC MOSFETs; voltage balancing; solid-state transformer; LLC resonant converter

## 1. Introduction

Due to the recent interest in smart grid, distributed power system, and renewable energy, researches have been actively conducted to replace large and heavy line-frequency transformers. A solid-state transformer (SST) proposed as a solution is a power converter that converts the magnitude or type of voltage using a power semiconductor and a high-frequency transformer [1-4]. As shown in Figure 1, an SST consists of an AC/DC rectifier stage, a DC/DC converter stage, and a DC/AC inverter stage. In particular, the DC/DC converter stage enables DC voltage conversion, high power density, and galvanic isolation by using a high-frequency transformer. The most commonly used topology for the DC/DC converter stage is a dual active bridge (DAB) [5-8], which exhibits characteristics of galvanic isolation and high power density, and can achieve zero-voltage switching (ZVS) without additional circuit. However, due to a high turn-off current, the turn-off loss is large and it is difficult to guarantee ZVS under light load conditions. In addition, it is difficult to achieve high efficiency over a wide load range because of the large conduction losses caused by circulating current. At the same time, an Inductor-Inductor-Capacitor (LLC) resonant converter has very low switching losses because it guarantees ZVS of the switches and zero-current switching (ZCS) of the rectifier diodes from no load to full load. As a result, operating at high switching frequencies, the size of passive elements and transformers can be reduced, which allows for high power density. Therefore, research has been conducted to replace DAB converters with LLC resonant converters to Energies 2019, 12, 4003 2 of 18

improve the efficiency and power density of DC/DC converter stage [3,9–12]. However, silicon (Si)-based LLC resonant converters still exhibit high conduction and turn-off losses, making it difficult to design for high frequencies and power [3,9,10].

Figure 1. The block diagram of solid-state transformer.

To overcome the physical limitations of Si materials, researches are being conducted actively on wide-bandgap (WBG) materials such as silicon-carbide (SiC) and gallium-nitride (GaN). WBG materials have a very thin drift layer because they have a higher dielectric breakdown field than Si materials. As a result, WBG devices have a low on-resistance and reverse recovery loss [13–16]. Therefore, much effort is being put in to apply WBG devices to LLC resonant converters to achieve high efficiency and power density [17–21].

Among WBG devices, GaN devices typically have low voltage ratings of less than 600 V and hence SiC devices, which have relatively higher voltage ratings, are suitable for high-voltage applications. Although technological advances in SiC devices have greatly improved their voltage rating, they are still not a perfect replacement for Si devices. Thus, in the case of an SST where very high voltage ratings are required, it is essential to connect SiC devices in series [22–25]. However, connecting SiC devices in series may cause voltage imbalance due to a parasitic capacitor tolerance between them, which causes overvoltage breakdown of the device. In particular, SiC devices have a very small parasitic capacitor as their drift layers are thinner than those of Si devices [26], which causes a large voltage imbalance even with small parameter tolerances.

To solve voltage imbalance problems caused by the series connection, a number of methods have been proposed. Snubber circuits are the simplest way to resolve voltage imbalance [22–25,27]. These circuits can reduce voltage and current stress and switching losses, as well as voltage imbalances [23,24,27]. However, snubber circuits not only decrease the switching speed and power density but also reduce power conversion efficiency due to additional losses. In [22,25], a parameter optimization design was proposed to minimize snubber losses, but the optimal design of parameters is complicated.

In the active voltage control (AVC) method, the drain-source voltage of the switch is directly controlled [28–36]. In [28–30], a temporary clamp technique is proposed to eliminate the voltage imbalance. In [31–36], voltage imbalance was eliminated by adjusting the gate signal timing of seriesconnected switches. However, the gate driver circuit is enlarged by the AVC circuit, and these methods do not solve voltage imbalance during the transient [28–30]. In addition, it takes several milliseconds to solve voltage imbalance. Therefore, it is difficult to apply the methods to WBG devices operating at high frequency [31–36].

Quasi-active gate control (QAGC) [37,38] is a combination of snubber circuits and the AVC method. This method has the advantage that the number of additional devices is small and the circuit is simple. However, as the number of series-connected switches increase, the voltage balancing performance is greatly reduced and the parameter design is complicated.

Gate current control [39–43] eliminates voltage imbalance by controlling the gate charge or discharge current. This method, however, complicates the gate driver circuit due to additional components [39,40] and reduces the switching speed by limiting the gate current. In addition, very high current control bandwidth is required for fast response speed [41–43].

To overcome these problems, a gate signal delay control has been proposed in [44]. The advantage of this method is that no voltage balancing circuit is required, which implies no additional losses or power density reduction. In addition, this method enables voltage balancing through simple

Energies 2019, 12, 4003 3 of 18

gate signal adjustment even when the operating point changes. However, analysis of several seriesconnected switches is insufficient, and the analysis of problems that occur during turn-on when applying this method is not provided.

This paper proposes a switching scheme to solve the voltage imbalance in series-connected SiC metal-oxide-semiconductor field-effect transistors (MOSFETs) LLC resonant converter without any additional circuitry. The proposed scheme sequentially turns off series-connected SiC MOSFETs to compensate for the turn-off delay caused by parasitic capacitor tolerances. A detailed analysis of the effect of input and output parasitic capacitance differences on voltage imbalance is presented. In addition, a dead-time analysis considering the junction capacitors of the rectifier diode is provided to achieve both voltage balance and ZVS. The effectiveness of the proposed scheme is verified experimentally using a 2 kW series-connected SiC MOSFETs LLC resonant converter prototype.

#### 2. Series-Connected SiC-MOSFET LLC Resonant Converter

### 2.1. System Description

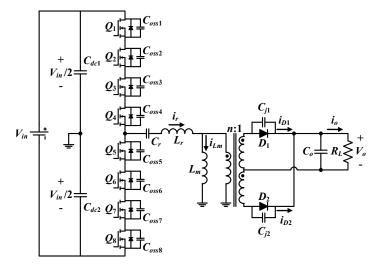

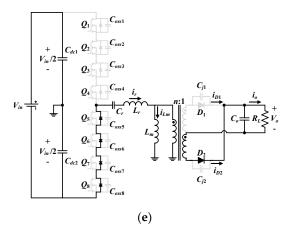

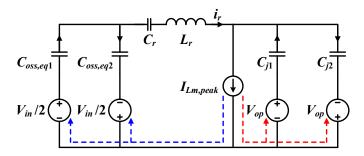

Figure 2 shows a series-connected SiC-MOSFET LLC resonant converter circuit. The circuit consists of a half-bridge converter with a split-capacitor, resonant tank, and center tap rectifier.  $V_{in}$  represents the input voltage of the bridge,  $C_{ds1}$  and  $C_{ds2}$  are split capacitors, respectively,  $Q_1$ – $Q_8$  are SiC-MOSFETs, and their output capacitances are expressed as  $C_{oss1}$ ~ $C_{oss8}$ . Switches  $Q_1$ – $Q_4$  are connected in series with each other and they are turned on and off at the same time. The same is true for switches  $Q_5$ – $Q_8$ . In addition,  $Q_1$ – $Q_4$  and  $Q_5$ – $Q_8$  operate complementary to each other. The resonant tank consists of the resonant capacitor  $C_r$ , leakage inductor of the transformer  $L_r$ , and magnetizing inductor of the transformer  $L_m$ . The center tap rectifier consists of rectifier diodes  $D_1$  and  $D_2$ , an output capacitor  $C_r$ , and a load resistor  $R_L$  where  $C_{j1}$  and  $C_{j2}$  denote junction capacitances of the rectifier diodes.

Figure 2. Circuit diagram of the series-connected silicone carbide (SiC)-MOSFETs LLC resonant converter.

## 2.2. Operating Principle

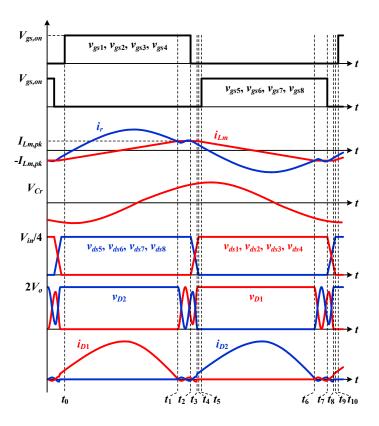

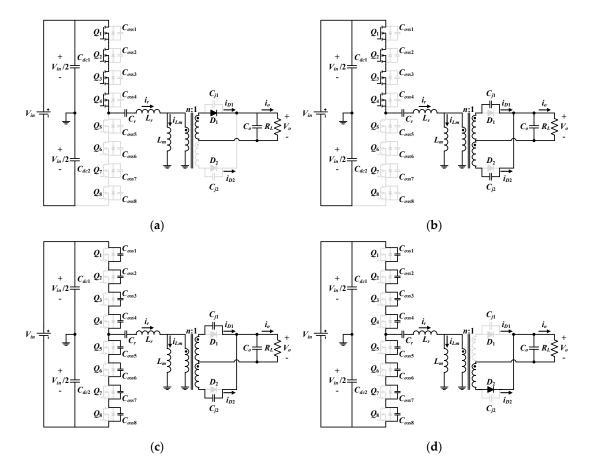

Figures 3 and 4 show the main waveforms of the series-connected SiC MOSFET LLC resonant converter and the equivalent circuit for each mode, respectively. To simplify analysis, it is assumed that the parasitic capacitances of the switches are the same and circuit operation is steady-state. The operation is divided into ten modes during the switching period.

Energies 2019, 12, 4003 4 of 18

Figure 3. Operational waveforms of the LLC resonant converter.

Energies **2019**, 12, 4003 5 of 18

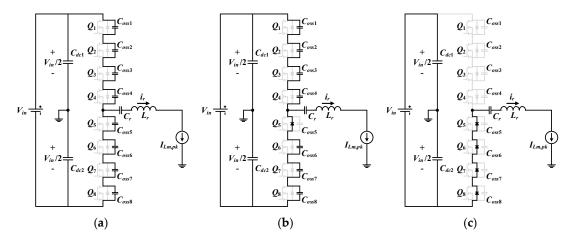

Figure 4. Equivalent circuits for each mode: (a) Mode 1; (b) Mode 2; (c) Mode 3; (d) Mode 4; (e) Mode 5.

Mode 1 [ $t_0 < t < t_1$ ]: At  $t_0$ ,  $Q_1$ – $Q_4$  are turned on at the same time and Mode 1 is initiated. In this mode,  $L_r$  and  $C_r$  participate in resonance.  $L_m$  does not participate in resonance because it is clamped by the output voltage. A resonance current  $i_r$  flows through  $Q_1$ – $Q_4$ .  $i_r$  is larger than the magnetizing inductance current  $i_{Lm}$  and energy is transferred to the load through the rectifier diode  $D_1$ . This mode ends when  $i_r$  equals  $i_{Lm}$ . During this mode,  $i_r$ ,  $i_{Lm}$ , and the voltage of the resonant capacitor  $v_{Cr}$  can be expressed as follows

$$i_r(t) = i_r(t_0) \cdot \cos \omega_{r1}(t - t_0) + \frac{V_a}{Z_1} \sin \omega_{r1}(t - t_0)$$

$$\tag{1}$$

$$i_{Lm}(t) = \frac{V_{op}}{L_{m}} t + i_{Lm}(t_{0})$$

(2)

$$v_{Cr}(t) = Z_1 i_r(t_0) \cdot \sin \omega_{r1}(t - t_0) - V_a \cos \omega_{r1}(t - t_0) + \frac{V_{in}}{2} - V_{op}$$

(3)

where  $\omega_{r1} = 1/\sqrt{(L_r C_r)}$  is the resonant angular frequency,  $Z_1 = \sqrt{(L_r/C_r)}$  is the characteristic impedance, n is the turn ratio of transformer,  $V_{op} = nV_o$  is the output voltage converted to the transformer primary side, and  $V_a = V_{in}/2 - V_{op} - V_{cr}(t_0)$ .

Mode 2 [ $t_1 < t < t_2$ ]: This mode starts when the linearly increasing  $i_{Lm}$  becomes equal to  $i_r$ . At this time, the rectifier diodes  $D_1$  and  $D_2$  do not conduct, and junction capacitances  $C_{j1}$  and  $C_{j2}$  participate in resonance.  $L_m$  also participates in resonance as it is no longer clamped by the output voltage. Therefore, the resonant capacitor  $C_r$ , resonant inductor  $L_r$ , magnetizing inductor  $L_m$ , and junction capacitances of the rectifier diodes  $C_{j1}$  and  $C_{j2}$  form a resonant tank. Assuming that  $L_m$  is larger than  $L_r$  and that the interval of this mode is sufficiently short relative to the switching period, the magnitude of  $i_{Lm}$  is constant [45]. This mode ends when  $Q_1$ – $Q_4$  are turned off. During this mode,  $i_r$ ,  $i_{Lm}$ , and  $v_{Cr}$  can be expressed as follows

$$i_{r}(t) = \left[i_{r}(t_{1}) - \frac{I_{Lm,pk}C_{eq1}}{C_{jp}}\right] \cos \omega_{r2}(t - t_{1}) + \frac{V_{b}}{Z_{2}} \sin \omega_{r2}(t - t_{1}) + \frac{I_{Lm,pk}C_{eq1}}{C_{jp}}$$

(4)

$$i_{Lm}(t) = I_{Lm,pk} = \frac{nV_o}{L_m} \frac{T_s}{4}$$

(5)

Energies **2019**, 12, 4003 6 of 18

$$v_{Cr}(t) = \frac{1}{C_r \omega_{r2}} \left[ i_r(t_1) - \frac{I_{Lm,pk} C_{eq1}}{C_{jp}} \right] \sin \omega_{r2}(t - t_1) - \frac{V_b}{Z_2 C_r \omega_{r2}} \cos \omega_{r2}(t - t_1) + \frac{I_{Lm,pk} C_{eq1}}{C_{jp} C_r} t + \frac{V_a}{Z_1 C_r \omega_{r2}} + v_{Cr}(t_2)$$

(6)

where  $T_s$  is the switching period, n is transformer turn ratio,  $\omega_{r2} = 1/\sqrt{(L_r C_{eq1})}$  is the resonant angular frequency,  $Z_2 = \sqrt{(L_r/C_{eq1})}$  is the characteristic impedance,  $C_{jp} = 2C_{j1}/n^2$  is the total junction capacitance of the rectifier diode converted to the transformer primary side,  $C_{eq1} = C_r \parallel C_{jp}$ , and  $V_b = V_{in}/2 - V_{op} - V_{cr}(t_1)$ .

Mode 3 [ $t_2 < t < t_3$ ]: This mode starts when  $Q_1$ – $Q_4$  are turned off. In this mode, output capacitances  $C_{oss1}$ – $C_{oss8}$  and junction capacitances,  $C_{j1}$  and  $C_{j2}$ , are charged or discharged by  $i_{Lm}$ . This mode ends when  $C_{j1}$  and  $C_{j2}$  are fully charged and discharged, respectively. During this mode,  $i_r$ ,  $i_{Lm}$ , and  $v_{Cr}$  can be expressed as follows

$$i_{r}(t) = \left[i_{r}(t_{2}) - \frac{I_{Lm,pk}C_{eq2}}{C_{jp}}\right] \cos \omega_{r3}(t - t_{2}) + \frac{V_{c}}{Z_{3}} \sin \omega_{r3}(t - t_{2}) + \frac{I_{Lm,pk}C_{eq2}}{C_{jp}}$$

(7)

$$i_{Lm}\left(t\right) = I_{Lm,pk} = \frac{nV_o}{L_m} \frac{T_s}{4} \tag{8}$$

$$v_{Cr}(t) = \frac{1}{C_r \omega_{r3}} \left[ i_r(t_2) - \frac{I_{Lm,pk} C_{eq2}}{C_{jp}} \right] \sin \omega_{r3}(t - t_2) - \frac{V_c}{Z_3 C_r \omega_{r3}} \cos \omega_{r3}(t - t_2) + \frac{I_{Lm,pk} C_{eq2}}{C_{jp} C_r} t + \frac{V_c}{Z_3 C_r \omega_{r3}} + v_{Cr}(t_2)$$

(9)

where  $\omega_{r3} = 1/\sqrt{(L_r C_{eq2})}$  is the resonant angular frequency,  $Z_3 = \sqrt{(L_r/C_{eq2})}$  is the characteristic impedance,  $C_{oss,eq} = C_{oss,eq} \parallel C_r \parallel C_{jp}$ , and  $V_c = V_{in}/2 - V_{op} - V_{cr}(t_2)$ .

Mode 4 [ $t_3 < t < t_4$ ]: At  $t_3$ , the rectifier diode  $D_1$  is turned off and  $D_2$  is turned on. Thus, the energy stored in the magnetizing inductor is not fully used to charge and discharge output capacitances; instead, a part of it is transferred to the load through  $D_2$ . This mode ends when  $C_{oss1}$ – $C_{oss4}$  are fully charged and  $C_{oss5}$ – $C_{oss8}$  are fully discharged. During this mode,  $i_r$ ,  $i_{Lm}$ , and  $v_{Cr}$  can be expressed as follows

$$i_r(t) = i_r(t_3)\cos\omega_{r4}(t - t_3) + \frac{V_d}{Z_4}\sin\omega_{r4}(t - t_3)$$

(10)

$$i_{Lm}(t) = -\frac{V_{op}}{L_m}t + i_{Lm}(t_3)$$

$$\tag{11}$$

$$v_{Cr}(t) = \frac{i(t_3)}{C_r \omega_{rA}} \sin \omega_{rA}(t - t_3) - \frac{V_d}{Z_A C_r \omega_{rA}} \cos \omega_{rB}(t - t_3) + \frac{V_d}{Z_A C_r \omega_{rA}} + v_{Cr}(t_3)$$

(12)

where  $\omega_{r4} = 1/\sqrt{(L_r C_{eq3})}$  is the resonant angular frequency,  $Z_4 = \sqrt{(L_r/C_{eq3})}$  is the characteristic impedance,  $C_{eq3} = C_{oss,eq} \parallel C_r$ , and  $V_d = V_{in}/4 + V_{op} - V_{cr}(t_3)$ .

Mode 5 [ $t_4 < t < t_5$ ]: At  $t_4$ , the output capacitance is fully charged or discharged and this mode starts. In this mode, all the switches are off but the body diodes of  $Q_5$ – $Q_8$  start to conduct due to the continuity of the resonant current  $i_r$ . Therefore, the drain-source voltage of  $Q_5$ – $Q_8$  is equal to the forward voltage of its body diode; this ensures that ZVS conditions are achieved. This mode ends when  $Q_5$ – $Q_8$  are turned on. At this time, if resonant current  $i_r$  flows in the positive direction,  $Q_5$ – $Q_8$  are ZVS turned on. During this mode,  $i_r$ ,  $i_L m_r$ , and  $v_{Cr}$  can be expressed as follows

Energies **2019**, 12, 4003 7 of 18

$$i_r(t) = i_r(t_4)\cos\omega_{r_1}(t - t_4) + \frac{V_e}{Z_1}\sin\omega_{r_1}(t - t_4)$$

(13)

$$i_{Lm}(t) = -\frac{V_{op}}{L_m}t + i_{Lm}(t_4)$$

(14)

$$v_{Cr}(t) = Z_1 i(t_3) \sin \omega_{r1}(t - t_4) - V_e \cos \omega_{r1}(t - t_4) + V_{op} - V_{in}/2$$

(15)

where  $V_e = V_{op} - V_{cr}(t_4) - V_{in}/2$ .

Because the operation principle of Mode 6 to Mode 10 is similar to that of Mode 1 to Mode 5, a detailed description of these modes is omitted here.

## 3. Analysis of Voltage Imbalance in the Series-Connected SiC MOSFET LLC Resonant Converter

In this section, the effect of parasitic capacitance differences of series-connected switches on their turn-on and turn-off switching characteristics is discussed.

## 3.1. Turn-On Switching Characteristics

As shown in Figure 3, during Mode 3 and Mode 4,  $Q_5$ – $Q_8$  are off, and  $C_{oss5}$ – $C_{oss8}$  are discharged by  $i_r$ . Because it is assumed that all parasitic capacitances of the switches are equal, the drain-source voltages  $V_{ds}$  of  $Q_5$ – $Q_8$  simultaneously decreases to zero. If  $C_{oss5}$ – $C_{oss8}$  are different, their  $V_{ds}$  values decrease at different rates. These rates are inversely proportional to the output capacitance and can be calculated as follows

$$\Delta Q = C_{oss} \cdot \Delta V_{ds} \tag{16}$$

where  $\Delta Q$  is the incremental change in the charge supplied by the resonant current,  $C_{oss}$  is the output capacitance of the switch, and  $\Delta V_{ds}$  is the incremental change in the drain-source voltage of the switch.

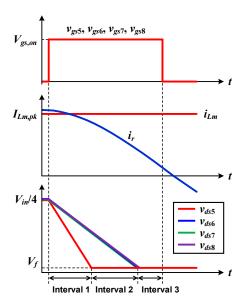

Figure 5 shows the turn-on switching transient waveforms when *Coss5–Coss8* satisfy the following inequality:

$$C_{ass5} < C_{ass6} = C_{ass7} = C_{ass8}$$

(17)

According to Equations (16) and (17), the drain-source voltage of switch  $Q_5$ , which has the smallest output capacitance, decreases most rapidly. Figure 6a shows the switch discharge situations during Interval 1. Because  $v_{ds5}$  is not fully discharged, the body diode of  $Q_5$  does not conduct. Figure 6b shows the switch discharge situations during Interval 2. Once  $v_{ds5}$  is completely discharged, the body diode of  $Q_5$  conducts due to continuity of the current. Those switches that are not yet fully discharged are discharged by the resonant current.  $v_{ds5}$  is clamped to the body diode forward voltage  $V_f$  until all the switches are fully discharged. Therefore, during turn-on transient, differences in the output capacitance do not cause voltage spikes.

As shown in Figure 6c, the body diodes of all switches are conducting when  $Q_5$ — $Q_8$  are fully discharged. Because  $v_{ds}$  of the switches is clamped to  $V_f$ , all the switches achieve ZVS conditions and differences in the input capacitance of the switches do not substantially affect  $v_{ds}$ . Thus, when ZVS turn-on is achieved, input and output capacitance differences between the series-connected switches do not cause problems during turn-on switching transients.

Energies 2019, 12, 4003 8 of 18

Figure 5. Turn-on switching transient waveforms.

**Figure 6.** Equivalent circuits during turn-on switching transient: (a) Interval 1; (b) Interval 2; (c) Interval 3.

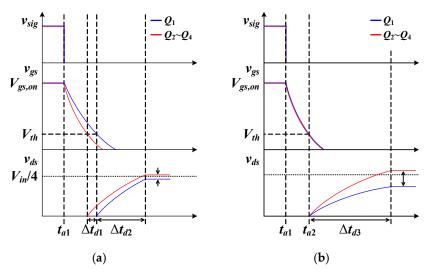

# 3.2. Turn-Off Switching Characteristics

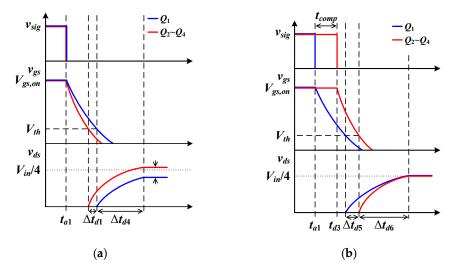

The drain-source voltage imbalance caused by the parasitic capacitance difference in the series-connected switches during the turn-off switching transients is discussed in this section. Figure 7 shows the turn-off switching waveforms of the gate signal  $v_{sig}$ , gate-source voltage  $v_{gs}$ , and drain-source voltage  $v_{ds}$  of the switches with different input capacitance  $C_{iss}$  or output capacitance  $C_{oss}$  value. Figure 7a shows the turn-off switching waveforms when the input capacitance  $C_{iss1}$  of switch  $Q_1$  is larger than the input capacitances  $C_{iss2}$ – $C_{iss4}$  of switches  $Q_2$ – $Q_4$ . Although turn-off signals are simultaneously applied at  $t_{a1}$ ,  $v_{gs}$  decreases at different rates because the input capacitances are different. In other words,  $v_{gs1}$  of switch  $Q_1$  decreases slowly and it takes longer to decrease from the gate-source turn-on voltage  $V_{gs,on}$  to the threshold voltage  $V_{th}$ . In this case, the turn-off delay caused by the difference in input capacitance can be expressed as [44,46]

$$\Delta t_{d1} = R_g \left( C_{iss1} - C_{iss2} \right) \ln \left( \frac{V_{gs,on}}{V_{th}} \right)$$

(18)

where  $R_g$  denotes a gate resistor.

Energies **2019**, 12, 4003 9 of 18

As can be seen in Figure 7a, even though the output capacitance  $C_{oss}$  of series-connected switches is equal, their  $v_{ds}$  rises at different time due to the time delay shown in Equation (18). Thus, a difference in input capacitance causes voltage imbalance. In this case, the steady-state voltage ratios of  $Q_1$ – $Q_4$  follow the relationship

$$v_{ds1}: v_{ds2}: v_{ds3}: v_{ds4} = \frac{\Delta t_{d2}}{C_{oss1}}: \frac{\Delta t_{d1} + \Delta t_{d2}}{C_{oss2}}: \frac{\Delta t_{d1} + \Delta t_{d2}}{C_{oss3}}: \frac{\Delta t_{d1} + \Delta t_{d2}}{C_{oss4}}$$

(19)

where  $\Delta t_{d2}$  is the time taken for  $v_{ds1}$  to reach steady-state from zero voltage under different input capacitance condition.

By assumption, the output capacitances are equal. Using Equation (19), the magnitude of voltage imbalance due to input capacitance tolerance is calculated as

$$\left| v_{ds2} - v_{ds1} \right| = \left| \frac{V_{in} \Delta t_{d1}}{3 \Delta t_{d1} + 4 \Delta t_{d2}} \right|. \tag{20}$$

Figure 7b shows the turn-off switching waveforms when the output capacitance  $C_{oss1}$  of switch  $Q_1$  is larger than the output capacitances  $C_{oss2}$ – $C_{oss4}$  of switches  $Q_2$ – $Q_4$ . At  $t_{\sigma 1}$ , the turn-off signal is applied, and  $v_{gs}$  decreases at the same rate.

At  $t_{a2}$ ,  $v_{gs}$  reaches  $V_{th}$  and  $v_{ds}$  increases. Because  $C_{oss1}$  is larger than  $C_{oss2}$ – $C_{oss4}$ ,  $v_{ds1}$  increases slowly, which causes a voltage imbalance. In this case, the steady-state voltage ratios of  $Q_1$ – $Q_4$  and the magnitude of voltage imbalance due to output capacitance tolerance are calculated as

$$v_{ds1}: v_{ds2}: v_{ds3}: v_{ds4} = \frac{\Delta t_{d3}}{C_{oss1}}: \frac{\Delta t_{d3}}{C_{oss3}}: \frac{\Delta t_{d3}}{C_{oss3}}: \frac{\Delta t_{d3}}{C_{oss4}}$$

(21)

$$\left| v_{ds2} - v_{ds1} \right| = \left| \frac{C_{oss1} - C_{oss2}}{3C_{oss1} + C_{oss2}} V_{in} \right|$$

(22)

where  $\Delta t_{d3}$  is the time taken for  $v_{ds1}$  to reach steady-state from zero voltage under different output capacitance condition.

**Figure 7.** Turn-off switching waveforms: (a) with different input capacitances  $C_{iss}$ ; (b) with different output capacitances  $C_{oss}$ .

## 4. Proposed Switching Scheme

In this section, a gate signal compensation method is proposed to overcome the voltage imbalance caused by discrepancies between the parasitic capacitances of series-connected switches.

Energies 2019, 12, 4003 10 of 18

To simplify analysis, it is assumed that the parasitic capacitances of all switches, except  $Q_1$ , are equal and the parasitic capacitances of  $Q_1$  are larger than those of  $Q_2$ – $Q_8$ .

Figure 8 shows the operation principle of the proposed switching scheme. As discussed in Section 3, when the proposed switching scheme is not applied, switch  $Q_1$ , which has a large parasitic capacitance, causes voltage imbalance. In this case, the steady-state voltage ratios of  $Q_1$ – $Q_4$  and the magnitude of voltage imbalance due to input and output capacitance tolerance are calculated as

$$v_{ds1}: v_{ds2}: v_{ds3}: v_{ds4} = \frac{\Delta t_{d4}}{C_{oss1}}: \frac{\Delta t_{d1} + \Delta t_{d4}}{C_{oss2}}: \frac{\Delta t_{d1} + \Delta t_{d4}}{C_{oss3}}: \frac{\Delta t_{d1} + \Delta t_{d4}}{C_{oss4}}$$

(23)

$$|v_{ds2} - v_{ds1}| = \left| \frac{\left( C_{oss1} - C_{oss2} \right) \Delta t_{d4} + C_{oss1} \Delta t_{d1}}{\left( 3C_{oss1} + C_{oss2} \right) \Delta t_{d1} + 3C_{oss1} \Delta t_{d1}} V_{in} \right|$$

(24)

where  $\Delta t_{d4}$  is the time taken for  $v_{ds1}$  to reach from zero voltage to steady-state value under different input and output capacitance condition.

**Figure 8.** Turn-off switching waveforms: (a) without proposed switching scheme; (b) with proposed switching scheme.

Figure 8b shows the turn-off switching waveforms when the proposed scheme is applied. This scheme solves voltage imbalance by sequentially turning off switches with a large parasitic capacitance. This scheme ensures time for  $v_{ds}$  of the switch with a large parasitic capacitance to increase to  $V_{in}/4$ . As shown in Figure 8b,  $t_{comp}$  is required to compensate for the turn-off delay and it can be calculated as follows

$$t_{comp} = \Delta t_{d1} + \Delta t_{d5} \tag{25}$$

where  $\Delta t_{d1}$  and  $\Delta t_{d5}$  represent the time taken for  $v_{gs}$  to reach from  $V_{gs,on}$  to  $V_{th}$  without and with the proposed switching scheme, respectively.  $\Delta t_{d1}$  is the time delay caused by input capacitance tolerance and it is constant in Equation (18), regardless of whether the proposed scheme is applied or not. Therefore,  $\Delta t_{d5}$  must be calculated to derive the gate signal compensation time. The magnetizing current is constant during turn-off switching transient by assumption. The best case is when the voltages of the series-connected switches are  $V_{in}/4$  and this relationship is expressed as

$$\frac{V_{in}}{4} = \frac{\Delta t_{d6}}{C_{oss2}} I_{Lm,pk,H} = \frac{\Delta t_{d5} + \Delta t_{d6}}{C_{oss1}} I_{Lm,pk,H}$$

(26)

$$I_{Lm,pk,H} = \frac{C_{oss,H}}{C_{oss,H} + C_{oss,L}} I_{Lm,pk}$$

(27)

Energies 2019, 12, 4003 11 of 18

where  $I_{Lm,pk,H}$  is the magnitude of current that charges the upper switches of the half-bridge during the dead-time and  $C_{oss,H}$  and  $C_{oss,L}$  are the total output capacitance of the upper and lower switches, respectively.

Using Equation (25),  $\Delta t_{d5}$  can be calculated as follows:

$$\Delta t_{d5} = \frac{C_{oss1} - C_{oss2}}{4I_{Im.nk}} V_{in} \,. \tag{28}$$

## 5. Design Considerations for Achieving ZVS

In this section, the dead-time design process for achieving ZVS is analyzed. As discussed earlier, the LLC resonant converter achieves ZVS from no load to full load. However, some constraints must be met to achieve ZVS, one of which can be expressed as

$$I_{Lm,pk} \cdot t_{dead} \ge \sum_{i=1}^{8} \left( C_{oss1} \Delta V_{ds,i} \right)$$

(29)

where  $t_{dead}$  denotes dead-time [45,47].

Equation (29) indicates that charge supplied by the magnetizing current  $I_{Lm,pk}$  should be larger than the charge necessary for fully charging and discharging the output capacitance of all switches in the dead-time. However, Equation (29) assumes that  $I_{Lm,pk}$  is used only to charge or discharge the output capacitance to achieve ZVS during the dead-time, so it is not valid when considering the junction capacitance of the rectifier diode.

Figure 9 shows the equivalent circuit during dead-time. The magnetizing inductor is represented as a current source by assumption. During the dead-time,  $I_{Lm,pk}$  charges or discharges the output capacitances of switches and junction capacitances of rectifier diodes. Therefore, if the dead-time is selected using Equation (29), ZVS cannot be achieved because  $v_{ds}$  is fully discharged. In this paper, a resonant current  $i_r$  is used instead of a magnetizing current for accurate dead-time design.

Figure 9. Equivalent circuit during dead-time.

Referring to Figure 3, the resonant current during dead-time can be approximated as

$$i_r(t) \approx f(t) = i_r'(t_2)(t - t_2) + i_r(t_2)$$

(30)

where

$$i_r'(t_2) = \frac{V_c \omega_{r3}}{Z_3} = \frac{V_c}{L_r} < 0 \tag{31}$$

$$i_r(t_2) = I_{Lm,pk}. (32)$$

Because charge  $Q_{ir}$  supplied by the resonant current is equal to the area below  $i_r(t)$  during the dead-time, it is obtained as

Energies 2019, 12, 4003 12 of 18

$$Q_{ir} = \frac{t_{dead}}{2} \left[ I_{Lm,pk} + \left\{ \frac{V_c}{L_r} t_{dead} + I_{Lm,pk} \right\} \right] = t_{dead} \left( I_{Lm,pk} + \frac{V_c}{2L_r} t_{dead} \right)$$

(33)

Assuming that  $C_{0881}$ – $C_{0888}$  are equal, using Equations (29) and (33), the dead-time constraint for achieving ZVS is derived as follows:

$$\frac{V_c}{2L} (t_{dead})^2 + I_{Lm,pk} t_{dead} \ge \frac{C_{oss1} V_{in}}{2}.$$

(34)

Using Equation (31), the lower limit of tdead is obtained as

$$t_{dead} \ge -\frac{L_r I_{Lm,pkc}}{V_c} \left\{ 1 + \sqrt{1 + \frac{V_c V_{in} C_{oss1}}{L_r \left(I_{Lm,pk}\right)^2}} \right\}.$$

(35)

Using Equation (35), it is possible to calculate the ZVS condition taking into account *C<sub>i</sub>*. However, Equation (32) does not consider the parasitic capacitance tolerance at all. When the parasitic capacitances of individual switches are different, the lowest dead-time limit to achieve both ZVS and voltage balance is obtained as follows

$$t_{dead,i} \ge -\frac{L_r I_{Lm,pkc}}{V_c} \left\{ 1 + \sqrt{1 + \frac{2V_c V_{in} C_{oss,tot}}{L_r \left( I_{Lm,pk} \right)^2}} \right\} + t_{comp,i}$$

(36)

where  $t_{dead,i}$  is the dead-time of switch  $Q_i$ ,  $C_{oss,tot}$  is the sum of  $C_{oss1}$ – $C_{oss8}$ , and  $t_{comp,i}$  is the gate signal compensation time of switch  $Q_i$  calculated using Equation (25).

The other constraint for achieving ZVS is related to turn-on switching. If the dead-time selected is too long and the direction of  $i_r$  is changed before the gate signal is applied, ZVS cannot be achieved. When  $i_r$  changes direction, the output capacitor being charged begins to discharge and vice versa. The ZVS constraint reflecting the above phenomenon is expressed as follows:

$$i_r(t_5) = i_r(t_4)\cos\omega_{r_1}(t_{dead} + t_2 - t_4) + \frac{V_e}{Z_1}\sin\omega_{r_1}(t_{dead} + t_2 - t_4) \ge 0.$$

(37)

Using Equation (37), the dead-time constraint is derived as follows

$$t_{dead} \le \frac{\arctan \phi}{\omega_{c1}} + t_{low,lim} \tag{38}$$

where

$$\phi = -\frac{Z_1 i_r(t_4)}{V_c} \tag{39}$$

$$t_{low,lim} = -\frac{L_r I_{Lm,pk}}{V_c} \left\{ 1 + \sqrt{1 + \frac{2V_c V_{in} C_{oss,tot}}{L_r \left(I_{Lm,pk}\right)^2}} \right\}.$$

(40)

Using Equations (36) and (38), the dead-time range to achieve both ZVS and voltage balance is derived as follows:

$$t_{low,lim} + t_{comp,i} \le t_{dead} \le \frac{\arctan \phi}{\omega_{r1}} + t_{low,lim} . \tag{41}$$

## 6. Experimental Results

To verify the effectiveness of the proposed switching scheme, a series-connected SiC-MOSFET LLC resonant converter was implemented as shown in Figure 10. The equivalent circuit is shown in

Energies **2019**, 12, 4003

Figure 2 and the design parameters are listed in Table 1. A Rohm 1.2 kV SiC MOSFET (SCH2080KE) was used for the series-connected switches and gate signals were generated by a Texas Instruments TMS320F28377D DSP board.

Figure 10. Test setup for series-connected SiC-MOSFETs LLC resonant converter.

| _ |                   |                         |                |

|---|-------------------|-------------------------|----------------|

|   | Symbol            | Quantity                | Value (Unit)   |

|   | $V_{in}$          | Input voltage           | 600-800 (V)    |

|   | $f_{r1}$          | Resonant frequency      | 100 (kHz)      |

|   | $f_s$             | Switching frequency     | 86.6 (kHz)     |

|   | $L_m$             | Magnetizing inductor    | 873 (μH)       |

|   | $L_r$             | Resonant inductor       | 135 ( $\mu$ H) |

|   | $C_r$             | Resonant capacitor      | 11 (nF)        |

|   | <i>np:ns1:ns2</i> | Transformer turns ratio | 44:8:8         |

**Table 1.** Component parameters of the test setup.

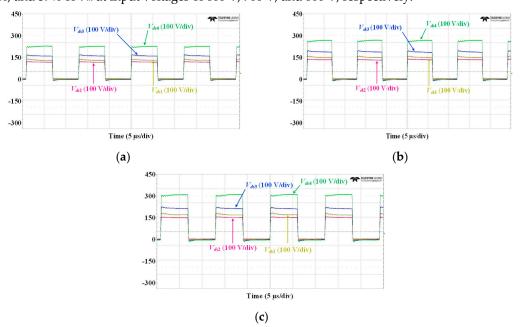

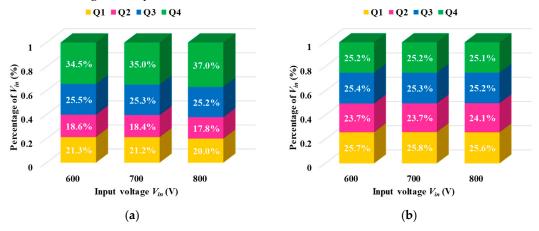

Figure 11 shows the drain-source voltage waveforms of the upper switches  $Q_1$ – $Q_4$  under different input voltage conditions. As discussed in Section 3, input and output capacitance tolerance causes a voltage imbalance between series-connected switches. Switch  $Q_4$ , which has the smallest parasitic capacitance, blocks higher voltage when compared to the other switches.  $V_{ds4}$  blocks 34.5%, 35%, and 37% of  $V_{in}$  at input voltages of 600 V, 700 V, and 800 V, respectively.

**Figure 11.** Experimental results with series-connected SiC MOSFETs without the proposed method: (a)  $V_{in} = 600 \text{ V}$ ; (b)  $V_{in} = 700 \text{ V}$ ; (c)  $V_{in} = 800 \text{ V}$ .

Energies 2019, 12, 4003 14 of 18

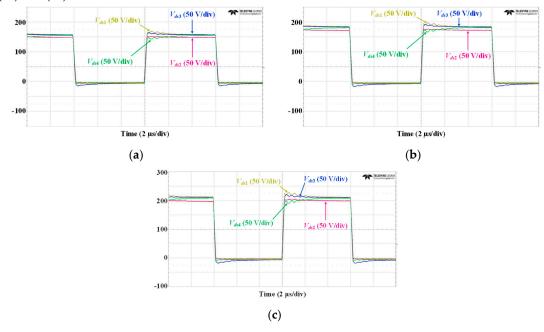

Figure 12 shows the drain-source voltage waveforms of the upper switches when the proposed switching scheme is applied. Voltage imbalance is solved by turning off switches with a large parasitic capacitance in sequence. The gate signal compensation time is calculated using Equations (25) and (41).

**Figure 12.** Experimental results with series-connected SiC MOSFETs with the proposed method: (a)  $V_{in} = 600 \text{ V}$ ; (b)  $V_{in} = 700 \text{ V}$ ; (c)  $V_{in} = 800 \text{ V}$ .

Figure 13 compares the drain-source voltage of series-connected switches at different input voltages. Approximately 35% of the input voltage is applied to switch  $Q_4$ . Therefore, this switch has a risk of overvoltage breakdown. However, after using the proposed scheme, approximately 25% of the input voltage is applied to switch  $Q_4$ . In addition, voltage imbalance between the series-connected switches is also significantly reduced.

**Figure 13.** Comparison of the drain-source voltage of series-connected switches at different input voltages: (a) without the proposed scheme; (b) with the proposed scheme.

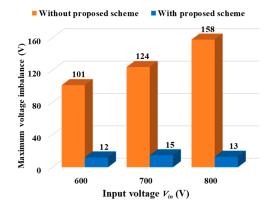

Figure 14 shows the maximum voltage imbalance between the series-connected switches. Parasitic capacitance tolerances cause a voltage imbalance of 101–158 V. However, after applying the proposed method, the maximum voltage imbalance reduced by 90% to 12–15 V.

Energies 2019, 12, 4003 15 of 18

**Figure 14.** Comparison of the maximum voltage imbalance between the series-connected switches at different input voltages.

#### 7. Conclusion

This paper proposes a switching scheme to overcome voltage imbalance in series-connected SiC MOSFET LLC resonant converter. The proposed method eliminates voltage imbalance by sequentially turning off switches with a large parasitic capacitance. Furthermore, we analyzed the effect of parasitic capacitance on voltage imbalance in detail. The procedure for calculating the gate signal compensation time was provided. In addition, to achieve both voltage balance and ZVS turnon, dead-time design constraints were derived. In order to verify the effectiveness of the proposed method, experimental results were presented at various input voltages. Compared to series-connected switches in which the proposed method was not applied, voltage imbalance reduced by 91% at 800 V after applying the proposed method.

**Author Contributions:** Conceptualization, H.-R.C. and R.-Y.K.; Formal analysis, H.-R.C.; Project administration, R.-Y.K.; Supervision, R.-Y.K.; Validation, H.-R.C.; Visualization, H.-R.C. and R.-Y.K.; Writing—original draft, H.-R.C.; Writing—review and editing, H.-R.C. and R.-Y.K.

**Funding:** This work was supported by "Human Resources Program in Energy Technology" of the Korea Institute of Energy Technology Evaluation and Planning (KETEP), granted financial resource from the Ministry of Trade, Industry & Energy, Republic of Korea (No. 20171210201100, No. 20184010201710).

Conflicts of Interest: The authors declare no conflict of interest.

## References

- 1. She, X.; Yu, X.; Wang, F.; Huang, A.Q. Design and demonstration of a 3.6-kV–120-V/10-kVA solid-state transformer for smart grid application. *IEEE Trans. Power Electron.* **2014**, *29*, 3982–3996.

- 2. Zhao, T.; Wang, G.; Bhattacharya, S.; Huang, A.Q. Voltage and power balance control for a cascaded H-bridge converter-based solid-state transformer. *IEEE Trans. Power Electron.* **2013**, *28*, 1523–1532.

- Tan, K.; Yu, R.; Guo, S.; Huang, A.Q. Optimal design methodology of bidirectional LLC resonant DC/DC converter for solid state transformer application. In Proceedings of the IECON 2014-40th Annual Conference of the IEEE Industrial Electronics Society, Dallas, TX, USA, 29 October–1 November 2014; pp. 1657–1664.

- 4. Falcones, S.; Ayyanar, R.; Mao, X. A DC–DC multiport-converter-based solid-state transformer integrating distributed generation and storage. *IEEE Trans. Power Electron.* **2013**, *28*, 2192–2203.

- Basu, K.; Shahani, A.; Sahoo, A.K.; Mohan, N. A single-stage solid-state transformer for PWM AC drive with source-based commutation of leakage energy. *IEEE Trans. Power Electron.* 2015, 30, 1734–1746.

- Fan, H.; Li, H. High-frequency transformer isolated bidirectional DC-DC converter modules with high efficiency over wide load range for 20 kVA solid-state transformer. *IEEE Trans. Power Electron.* 2011, 26, 3599–3608.

- 7. Falcones, S.; Mao, X.; Ayyanar, R. Topology comparison for solid state transformer implementation. In Proceedings of the IEEE PES General Meeting, Providence, RI, USA, 25–29 July 2010; pp. 1–8.

Energies 2019, 12, 4003 16 of 18

Qin, H.; Kimball, J.W. Closed-loop control of DC-DC dual-active-bridge converters driving single-phase inverters. *IEEE Trans. Power Electron.* 2014, 29, 1006–1017.

- Itoh, J.-I.; Aoyagi, K.; Nakanishi, T. Bidirectional single-phase Solid-State Transformer using multi cell for volume reduction of high voltage capacitor. In Proceedings of the 2017 IEEE 3rd International Future Energy Electronics Conference and ECCE Asia (IFEEC 2017-ECCE Asia), Kaohsiung, Taiwan, 3–7 June 2017; pp. 332–337.

- Dujic, D.; Steinke, G.K.; Bellini, M.; Rahimo, M.; Storasta, L.; Steinke, J.K. Characterization of 6.5 kV IGBTs for high-power medium-frequency soft-switched applications. *IEEE Trans. Power Electron.* 2014, 29, 906–919.

- 11. Lai, J.-S.; Choe, J.M.; Yeh, C.-S.; Moon, S.-R.; Lai, W.-H.; Zhang, L. A modular front-end medium-voltage solid-state transformer. In Proceedings of the 2017 Asian Conference on Energy, Power and Transportation Electrification (ACEPT), Singapore, Singapore, 24–26 October 2017; pp. 1–6.

- Lee, M.; Kim, J.-W.; Lai, J.-S. Small-signal modeling of three-level boost rectifier and system design for medium-voltage solid-state transformer. In Proceedings of the 2019 10th International Conference on Power Electronics and ECCE Asia (ICPE 2019-ECCE Asia), Busan, South Korea, 27–30 May 2019; pp. 1–7.

- Hazra, S.; De, A.; Cheng, L.; Palmour, J.; Schupbach, M.; Hull, B.A.; Allen, S.; Bhattacharya, S. High switching performance of 1700-V, 50-A SiC power MOSFET over Si IGBT/BiMOSFET for advanced power conversion applications. *IEEE Trans. Power Electron.* 2016, 31, 4742–4754.

- 14. Millán, J.; Godignon, P.; Perpiñà, X.; Pérez-Tomás, A.; Rebollo, J. A survey of wide bandgap power semiconductor devices. *IEEE Trans. Power Electron.* **2014**, *29*, 2155–2163.

- 15. Mitova, R.; Ghosh, R.; Mhaskar, U.; Klikic, D.; Wang, M.-X.; Dentella, A. Investigations of 600-V GaN HEMT and GaN diode for power converter applications. *IEEE Trans. Power Electron.* **2014**, 29, 2441–2452.

- Nawaz, M.; Ilves, K. On the comparative assessment of 1.7 kV, 300 A full SiC-MOSFET and Si-IGBT power modules. In Proceedings of the 2016 IEEE Applied Power Electronics Conference and Exposition (APEC), Long Beach, CA, USA, 20–24 March 2016; pp. 276–282.

- Wang, X.; Jiang, C.; Lei, B.; Teng, H.; Bai, H.K.; Kirtley, J.L. Power-loss analysis and efficiency maximization

of a silicon-carbide MOSFET-based three-phase 10-kW bidirectional EV charger using variable-DC-bus

control. *IEEE J. Emerg. Sel. Top. Power Electron.* 2016, 4, 880–892.

- 18. Nakakohara, Y.; Otake, H.; Evans, T.M.; Yoshida, T.; Tsuruya, M.; Nakahara, K. Three-phase LLC series resonant DC/DC converter using SiC MOSFETs to realize high-voltage and high-frequency operation. *IEEE Trans. Ind. Electron.* **2016**, *63*, 2103–2110.

- Zhang, W.; Long, Y.; Zhang, Z.; Wang, F.; Tolbert, L.M.; Blalock, B.J.; Henning, S.; Wilson, C.; Dean, R. Evaluation and comparison of silicon and gallium nitride power transistors in LLC resonant converter. In Proceedings of the 2012 IEEE Energy Conversion Congress and Exposition (ECCE), Raleigh, NC, USA, 15–20 September 2012; pp. 1362–1366.

- Zhang, W.; Xu, Z.; Zhang, Z.; Wang, F.; Tolbert, L.M.; Blalock, B.J. Evaluation of 600 V cascode GaN HEMT in device characterization and all-GaN-based LLC resonant converter. In Proceedings of the 2013 IEEE Energy Conversion Congress and Exposition (ECCE), Denver, CO, USA, 15–19 September 2013; pp. 3571– 3578.

- 21. Zhang, W.; Wang, F.; Costinett, D.J.; Tolbert, L.M.; Blalock, B.J. Investigation of gallium nitride devices in high-frequency LLC resonant converters. *IEEE Trans. Power Electron.* **2017**, *32*, 571–583.

- Vechalapu, K.; Bhattacharya, S.; Aleoiza, E. Performance evaluation of series connected 1700V SiC MOSFET devices. In Proceedings of the 3rd IEEE Workshop on Wide Bandgap Power Devices and Applications (WiPDA), Blacksburg, VA, USA, 2–4 November 2015; pp. 184–191.

- Vechalapu, K.; Kadavelugu, A.K.; Bhattacharya, S. High voltage dual active bridge with series connected high voltage silicon carbide (SiC) devices. In Proceedings of the 2014 IEEE Energy Conversion Congress and Exposition (ECCE), Pittsburgh, PA, USA, 14–18 September 2014; pp. 2057–2064.

- 24. Han, Y.; Chen, W.; Chen, X.; Ma, X.; Sha, Y.; Yang, X.; Li, X. A 4000V input auxiliary power supply with series connected SiC MOSFETs for MMC-based HVDC system. In Proceedings of the 2016 IEEE 8th International Power Electronics and Motion Control Conference (IPEMC-ECCE Asia), Hefei, China, 22–26 May 2016; pp. 279–284.

- Vechalapu, K.; Bhattacharya, S. Performance comparison of 10 kV-15 kV high voltage SiC modules and high voltage switch using series connected 1.7 kV LV SiC MOSFET devices. In Proceedings of the 2016 IEEE

Energies 2019, 12, 4003 17 of 18

- Energy Conversion Congress and Exposition (ECCE), Milwaukee, WI, USA, 18–22 September 2016; pp. 1–8.

- 26. Gonzalez, J.O.; Alatise, O.; Hu, J.; Ran, L.; Mawby, P.A. An investigation of temperature-sensitive electrical parameters for SiC power MOSFETs. *IEEE Trans. Power Electron.* **2017**, 32, 7954–7966.

- 27. Chen, X.; Yu, L.; Jiang, T.; Tian, H.; Huang, K.; Wang, J. A high-voltage solid-state switch based on series connection of IGBTs for PEF applications. *IEEE Trans. Plamsa Sci.* **2017**, *45*, 2328–2334.

- 28. Palmer, P.R.; Zhang, J.; Zhang, X. SiC MOSFETs connected in series with active voltage control. In Proceedings of the 3rd IEEE Workshop on Wide Bandgap Power Devices and Applications (WiPDA), Blacksburg, VA, USA, 2–4 November 2015; pp. 60–65.

- 29. Palmer, P.; He, W.; Zhang, X.; Zhang, J.; Snook, M. IGBT series connection under Active Voltage Control with temporary clamp. In Proceedings of the IECON 2012-38th Annual Conference on IEEE Industrial Electronics Society, Montreal, QC, Canada, 25–28 October 2012; pp. 465–470.

- Yang, X.; Zhang, J.; He, W.; Long, Z.; Palmer, P.R. Physical investigation into effective voltage balancing by temporary clamp technique for the series connection of IGBTs. *IEEE Trans. Power Electron.* 2018, 33, 248– 258

- Zhang, Z.; Gui, H.; Niu, J.; Chen, R.; Wang, F.; Tolbert, L.M.; Costinett, D.J.; Blalock, B.J. High precision gate signal timing control based active voltage balancing scheme for series-connected fast switching fieldeffect transistors. In Proceedings of the 2018 IEEE Applied Power Electronics Conference and Exposition (APEC), San Antonio, TX, USA, 4–8 March 2018; pp. 925–930.

- 32. Ji, S.; Wang, F.; Tolbert, L.M.; Lu, T.; Zhao, Z.; Yu, H. An FPGA-Based Voltage Balancing Control for Multi-HV-IGBTs in Series Connection. *IEEE Trans. Ind. Appl.* **2018**, *54*, 4640–4649.

- 33. Ji, S.; Wang, F.; Tolbert, L.; Lu, T.; Zhao, Z.; Yu, H. Active voltage balancing control for multi HV-IGBTs in series connection. In Proceedings of the 2016 IEEE Energy Conversion Congress and Exposition (ECCE), Milwaukee, WI, USA, 18–22 September 2016; pp. 1–6.

- Ji, S.; Lu, T.; Zhao, Z.; Yu, H.; Yuan, L. Series-connected HV-IGBTs using active voltage balancing control with status feedback circuit. *IEEE Trans. Power Electron.* 2015, 30, 4165–4174.

- 35. Lu, T.; Zhao, Z.; Ji, S.; Yu, H.; Yuan, L. Active clamping circuit with status feedback for series-connected HV-IGBTs. *IEEE Trans. Ind. Appl.* **2014**, *50*, 3579–3590.

- 36. Ji, S.; Lu, T.; Zhao, Z.; Yu, H.; Wang, F. Active voltage balancing control for 10kV three-level converter using series-connected HV-IGBTs. In Proceedings of the 2016 IEEE Applied Power Electronics Conference and Exposition (APEC), Long Beach, CA, USA, 20–24 March 2016; pp. 1456–1461.

- 37. Teerakawanich, N.; Johnson, C.M. Design optimization of quasi-active gate control for series-connected power devices. *IEEE Trans. Power Electron.* **2014**, *29*, 2705–2714.

- Bagheri, A.; Iman-Eini, H.; Farhangi, S. A Gate Driver Circuit for Series-Connected IGBTs Based on Quasi-Active Gate Control. IEEE J. Emerg. Sel. Top. Power Electron. 2018, 6, 791–799.

- 39. Ren, Y.; Yang, X.; Zhang, F.; Chen, W. Analysis of series SiC MOSFETs stack using a single standard gate driver. In Proceedings of the 2016 IEEE 8th International Power Electronics and Motion Control Conference (IPEMC-ECCE Asia), Hefei, China, 22–26 May 2016; pp. 1664–1668.

- Ren, Y.; Yang, X.; Zhang, F.; Wang, K.; Chen, W.; Wang, L.; Pei, Y. A compact gate control and voltagebalancing circuit for series-connected SiC MOSFETs and its application in a DC breaker. *IEEE Trans. Ind. Electron.* 2017, 64, 8299–8309.

- 41. Baraia, I.; Barrena, J.A.; Abad, G.; Segade, J.M.C.; Iraola, U. An experimentally verified active gate control method for the series connection of IGBT/diodes. *IEEE Trans. Power Electron.* **2012**, *27*, 1025–1038.

- 42. Belverde, G.; Galluzzo, A.; Melito, M.; Musumeci, S.; Raciti, A. Active voltage sharing of series connected strings of IGBT devices in bridge applications. In Proceedings of the Conference Record of 1998 IEEE Industry Applications Conference. Thirty-Third IAS Annual Meeting (Cat. No. 98CH36242), St. Louis, MO, USA, 12–15 October 1998; pp. 817–824.

- 43. Hong, S.; Chitta, V.; Torrey, D.A. Series connection of IGBT's with active voltage balancing. *IEEE Trans. Ind. Appl.* **1999**, *35*, 917–923.

- 44. Shingu, K.; Wada, K. Digital control based voltage balancing for series connected SiC MOSFETs under switching operations. In Proceedings of the 2017 IEEE Energy Conversion Congress and Exposition (ECCE), Cincinnati, OH, USA, 1–5 October 2017; pp. 5495–5500.

Energies 2019, 12, 4003 18 of 18

Lu, B.; Liu, W.; Liang, Y.; Lee, F.C.; Van Wyk, J.D. Optimal design methodology for LLC resonant converter. In Proceedings of the Twenty-First Annual IEEE Applied Power Electronics Conference and Exposition, 2006. APEC'06., Dallas, TX, USA, 19–23 March 2006; pp. 533–538.

- 46. Agrawal, B.; Preindl, M.; Bilgin, B.; Emadi, A. Estimating switching losses for SiC MOSFETs with non-flat miller plateau region. In Proceedings of the 2017 IEEE Applied Power Electronics Conference and Exposition (APEC), Tampa, FL, USA, 26–30 March 2017; pp. 2664–2670.

- 47. Wang, H.; Dusmez, S.; Khaligh, A. Maximum efficiency point tracking technique for LLC-based PEV chargers through variable DC link control. *IEEE Trans. Ind. Electron.* **2014**, *61*, 6041–6049.

© 2019 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).