# Article **Circuit Techniques to Improve Low-Light Characteristics and** High-Accuracy Evaluation System for CMOS Image Sensor

Norihito Kato \*, Fukashi Morishita, Satoshi Okubo and Masao Ito

Abstract: The surveillance cameras we focus on target the volume zone, and area reduction is a top priority. However, by simplifying the ADC comparator, we face a new RUSH current issue, for which we propose a circuit solution. This paper proposes two novel techniques of column-ADC for surveillance cameras to improve low-light characteristics. RUSH current compensation reduces transient current consumption fluctuations during AD conversion and utilizing timing shift ADCs decreases the number of simultaneously operating ADCs. These proposed techniques improve lowlight characteristics because they reduce the operating noise of the circuit. In order to support small signal measurement, this paper also proposes a high-accuracy evaluation system that can measure both small optical/electrical signals in low-light circumstances. To demonstrate these proposals, test chips were fabricated using a 55 nm CIS process and their optical/electrical characteristics were measured. As a result, low-light linearity as optical characteristics were reduced by 63% and column interference (RUSH current) as an electrical characteristic was also reduced by 50%. As for the highaccuracy evaluation system, we confirmed that the inter-sample variation of column interference was 0.05 LSB. This ADC achieved a figure-of-merit (FoM) of 0.32 e-·pJ/step, demonstrating its usefulness for other ADC architectures while using a single-slope-based simple configuration.

check for updates

Citation: Kato, N.; Morishita, F.; Okubo, S.; Ito, M. Circuit Techniques to Improve Low-Light Characteristics and High-Accuracy Evaluation System for CMOS Image Sensor. Sensors 2022, 22, 6040. https:// doi.org/10.3390/s22166040

Academic Editor: Yael Nemirovsky

Received: 30 June 2022 Accepted: 9 August 2022 Published: 12 August 2022

Publisher's Note: MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations

Copyright: © 2022 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https:// creativecommons.org/licenses/by/ 4.0/).

Keywords: CMOS image sensor; column-parallel ADC; multi-functional fine pattern generator; on-chip test

# 1. Introduction

CMOS image sensors are widely used in so-called digital still cameras such as smartphones, compact cameras, and single-lens reflex cameras, as well as in surveillance cameras, industrial applications [1–3], object recognition [4–8], ToF sensors for distance measurement [9–11], and medical applications [12–14]. The performance requirements in these fields are low noise, high speed, wide dynamic range, and high resolution, and various technologies have been reported to improve these performances. In particular, from the perspective of surveillance and security, improved low-light characteristics that enable clear images even in dark environments have become an important technology for image sensors in recent years. In order to process signals from pixels at high speed, such image sensor devices incorporate thousands of ADCs in the chip to enable high-speed digital output; of the available ADCs, pixel ADCs [15–18] and column ADCs [19–29] have been used as a way to achieve widely parallel operation. To achieve high resolution and low power consumption, a column ADC is the best choice, because a pixel ADC is disadvantageous in terms of power, heat, and mounting.

There are several types of ADCs suitable for column-parallel operation, including single-slope [19–26], successive approximation register (SAR) [27], cyclic [28], deltasigma [29], and folding integration [30], which provide optimal performance for each configuration. These ADCs are used in different ways depending on the application: singleslope ADCs are suitable for commercialized CMOS image sensors with compact size, while

SAR and cyclic ADCs with binary search capability are suitable for high-speed applications. Delta-sigma ADCs are also suitable for high-speed, high-resolution applications. In addition, folding integration ADCs are used for low-noise applications.

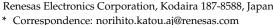

Figure 1 shows a schematic diagram of the image sensor we adopted. In this study, we focus on applications for surveillance cameras that can capture images even in low-light conditions. Since the surveillance cameras are targeted at the volume zone, the configuration is designed with the highest priority being area reduction for the purposes of cost reduction. Originally, our prior ADC comparator used a two-stage full differential amplifier [23]. However, since the full differential amplifier had a large number of transistors and capacitance elements, we adopted a simple scheme in which the second stage was a single-ended amplifier in order to achieve a smaller ADC. Such a single-ended scheme itself has already been reported [22]. However, the RUSH current issue, as mentioned in Section 2, causes linearity characteristic degradation especially in low-light applications, so we devised a way to solve this problem while still achieving a compact ADC size.

Figure 1. Block chart of an image sensor and one column structure.

In single-slope ADC, since many ADCs perform AD conversion simultaneously, there is concern about the increase in circuit noise due to their simultaneous operation. Especially in the case of surveillance cameras, since the characteristics under low illumination with few optical signals are important, the column ADCs need to amplify weak electrical signals and are relatively susceptible to noise due to circuit operation. To solve this problem, we propose a current compensation circuit and a timing shift ADC to reduce the number of simultaneous ADC operations [7]. In column ADCs, the power supply GND noise is highest during the reset operation, when all the thousands of ADCs operate simultaneously, because all the comparators that make up the ADC circuit operate simultaneously, causing a large voltage drop. Timing-shift ADCs can reduce the number of ADCs operating simultaneously by shifting the ADC operation time for each column, thereby improving voltage drop and preventing the degradation of pixel characteristics in dark mode.

We actually created a chip equipped with this ADC and compared its performance against the conventional method to demonstrate that low-light characteristics can be greatly improved. In the demonstration, since the number of signals handled by the ADC itself was very small, the effects caused by such simultaneous operation were observed through actual electrical measurement, and an evaluation device for measuring electrical characteristics was also introduced. Beginning with the fact that an electrical testing method is necessary to observe the operation of an ADC with an optical input image sensor, we solved this problem by providing an on-chip dual-path test circuit [31] that electrically measured the ADC by keeping actual CIS operating conditions. By using this technique, highly accurate measurement of the ADC performance was realized without the influence of optical input or pixel characteristics. This dual-path test circuit was capable of measuring not only INL and DNL, but also various electrical characteristics such as rush (peak) current characteristics due to simultaneous ADC operation, adjacent crosstalk interference, and horizontal smear characteristics.

Furthermore, in order to measure weak electrical signals, a high-precision evaluation device was necessary to minimize the influence of noise and disturbance noise from the evaluation environment. We analyze the measurement results by comparing the optical input measurement and the electrical signal measurement and demonstrate that the proposed timing shift ADC improves the low-light characteristics of the image sensor itself as well as granting a performance improvement as an ADC.

In Section 2, we explain the design issues of conventional column ADCs and propose a current compensation circuit and a timing shift ADC as those countermeasures. In Section 3, we present an evaluation environment for measuring low-light characteristics. In Section 4, high accuracy and low noise evaluation results are demonstrated through the measurement of various electrical characteristics and the results of test chip measurements. Finally, we conclude in Section 5.

#### 2. Design Issues of Conventional Column ADCs and Corresponding Countermeasures

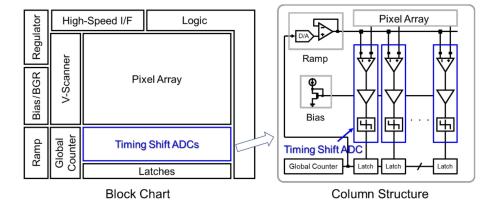

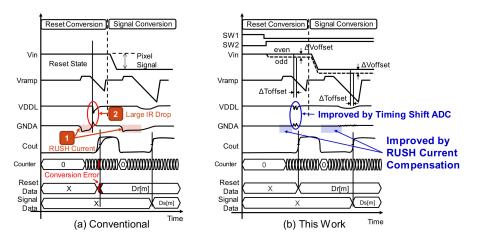

Figure 1 shows the block chart of our image sensor and one column structure. In this scheme, timing shift ADCs are used to improve low-light characteristics. To clarify the design issues of simultaneous ADC operation, Figure 2 describes ADC operation with a conventional comparator and its timing chart. In the ADC operation, we used a digital CDS (correlated double sampling) scheme in which the circuit offset is canceled by executing reset conversion and signal conversion. In the column-wise ADC structure, all ADCs operate at the same time during the reset conversion. Therefore, the supply voltage fluctuation deteriorates the conversion characteristics. The first issue is large GND noise caused by current instabilities. ADC current instabilities due to the state change of comparators induce an analog GND fluctuation; this is called the RUSH current during the ADC operation. The second issue is a large IR-drop caused by the repeater logic current switching. Through current between the ADC comparator and the repeater causes a large IR-drop of the logic voltage VDDL and its ground GNDL. These instabilities cause conversion error within the ADC, and deteriorate low-light linearity characteristics in particular because the output code itself becomes small in low-light.

Figure 2. ADC comparator of conventional scheme.

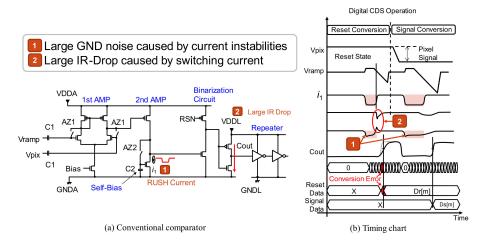

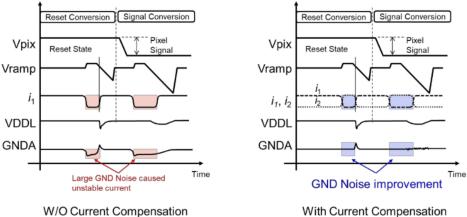

We will now discuss the first issue of RUSH current due to unstable current of the amplifier. Figure 3 shows the current mechanism of RUSH and its compensation circuit. In the configuration without current compensation, the current  $i_1$  in the second-stage amplifier changes depending on the output state of  $Vo_1$ , which is the output voltage of the first-stage amplifier. This unstable current fluctuates the analog ground *GNDA*, leading to an error during AD conversion. To suppress the fluctuation of this  $i_1$  current, in the configuration with current compensation, the  $i_2$  current path is added to compensate for current in the complementary. In this scheme, the supply current of the second-stage amplifier  $(i_1 + i_2)$  becomes constant.

Figure 3. RUSH current compensation.

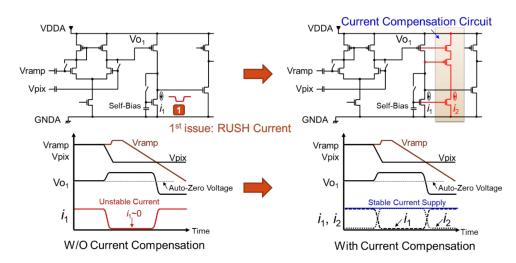

The impact of RUSH current compensation is shown in Figure 4. Without current compensation, by changing  $i_1$ , the GND fluctuations listed in the reset conversion and the signal conversion induce large GND noise during each operation period. On the other hand, in the configuration with current compensation, the amplifier current  $(i_1 + i_2)$  can be kept stable, and GND noise due to signal transition can be greatly reduced.

Figure 4. The impact of RUSH current compensation.

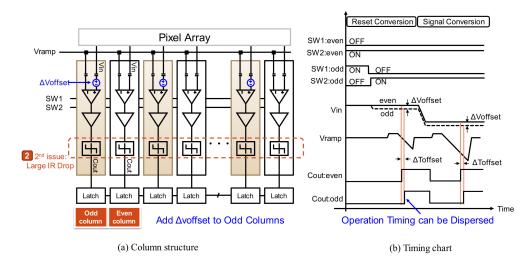

Figure 5 shows the concept of timing shift ADC, which can reduce large IR drop by means of simultaneous ADC operation-our second issue. In our column ADC structure, the behavior of even and odd columns is differentiated and the offset voltage  $\Delta V offset$  is generated only by the odd columns. For single-slope ADCs, this voltage offset is the difference in conversion time  $\Delta$ *Toffset*. Therefore, the comparator's output timing Cout\_even of even columns and Cout\_odd of odd columns can be shifted, and as a result, the simultaneous operation of ADCs can be reduced by half.

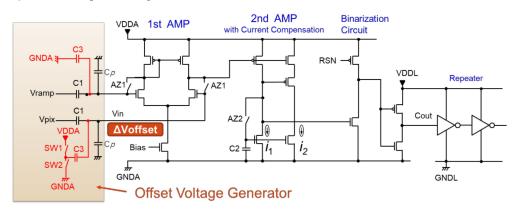

A circuit diagram of the timing shift ADC is shown in Figure 6. To add the voltage offset to the input signal  $V_{in}$ , we provide capacitance C3 and switches SW1 and SW2. By switching SW1 and SW2 on and off, the left-side voltage of C3 can be changed from VDDA to *GNDA*. Here, *Cp* is the parasitic capacitance of the first-stage amplifier input.

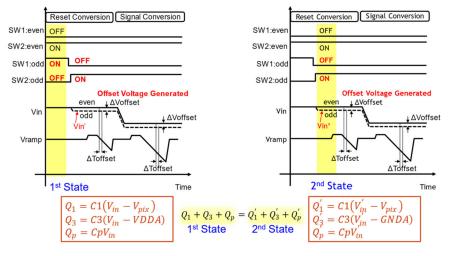

Figure 7 shows how to attach the offset voltage. This figure describes the behavior of odd columns on the offset side. When the reset conversion of digital CDS starts, the state of each switch SW1 and SW2 is as described in the first state period of Figure 7. In this state, SW1 is ON and SW2 is OFF, and the electric charge stored in each capacitance at this time is shown in Equation (1).

$$Q_1 = C1(V_{in} - V_{pix}), \ Q_3 = C3(V_{in} - VDDA), \ Q_p = CpV_{in}$$

(1)

Figure 5. Concept of timing shift ADC.

Figure 6. Circuit diagram of timing shift ADC.

Figure 7. Generation of offset voltage.

From this state, we change the SW to add the offset to the Vin node of the ADC input. This is the second state. In the second state, SW1 is turned off and SW2 is turned on. Then, the voltage of the input Hi-Z node Vin changes from  $V_{in}$  to  $V'_{in}$ , and the charge stored in those capacitors also changes, as shown in Equation (2).

$$Q'_{1} = C1(V'_{in} - V_{pix}), \ Q'_{3} = C3(V'_{in} - GNDA), \ Q'_{p} = CpV'_{in}$$

(2)

As the charge conservation law between the first state and the second state is established, the offset voltage can be expressed in Equation (3).

$$\Delta Voffset = V_{in} - V'_{in} = \frac{C3}{C1 + C3 + Cp} (VDDA - GNDA)$$

(3)

Therefore, when compared to even columns, it is possible to create a time difference of  $\Delta$ *Toffset* caused by this  $\Delta$ *Voffset*, and as a result, we can avoid the same-time operation of all ADCs.

Although this  $\Delta Voffset$  has the effect of shifting the AD conversion time by  $\Delta Toffset$ , it does not adversely affect the AD conversion characteristics after digital CDS, even if there are differences between even–odd columns or mismatched capacitance values for each column, because the term in Equation (3) itself is cancelled by the same value as the difference between the signal and reset AD conversion results through digital CDS, as described in Figure 2.

Figure 8 shows the timing diagram of the conventional scheme and the proposed one. This exhibits the two issues mentioned so far and their corresponding improvements under the proposed scheme. The RUSH current is improved by the current compensation circuit, and the large IR drop of the logic voltage is improved by the timing shift ADC, enabling stable AD conversion without worrying about power supply noise.

Figure 8. Improvement image by RUSH current compensation and timing shift ADC.

#### 3. Evaluation Method

The circuits proposed in the previous section have lower simultaneous operating noise than conventional circuits. Therefore, an evaluation system capable of detecting operating noise with high accuracy was required. This being said, even if the evaluation system can achieve low noise, if the evaluation results are not reproducible, the evaluation must be repeated many times to check the validity of the measurement results, which causes evaluation to take an enormous amount of time. In this section, we first describe the common evaluation method of image sensors and its issues, and then propose a highprecision evaluation system that solves the issues.

#### 3.1. Common Evaluation Method of Image Sensors and Evaluation Issues

The most common method of evaluation for image sensors is using optical input. Since general image sensors have linear input–output characteristics with respect to light intensity, sensor linearity is evaluated based on the difference between the ideal input/output characteristics and the characteristics of the actual measurement results. However, this evaluation method using optical input has been reported to have the following issues [31]: The first issue is that the pixel and ADC characteristics cannot be evaluated separately. If separate evaluation is not possible, it is impossible to directly confirm whether the problem is on the pixel or the ADC side. The second issue is that it is extremely difficult to

accurately expose the inter-column interference noise measurement pattern to the image sensor surface due to light diffraction. To solve these problems, a method of measuring only the electrical characteristics of the ADC by providing a direct electrical signal input path to the ADCs has been proposed [31]. However, although previous work has reported that it is possible to measure with high precision, the issue remains that it has not been confirmed whether the measurement results are reproducible.

#### 3.2. Proposed Evaluation System

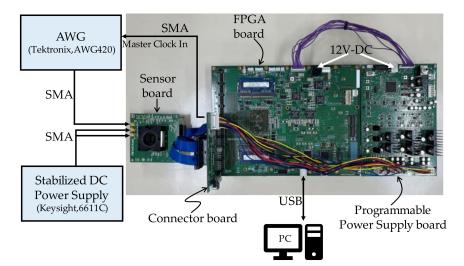

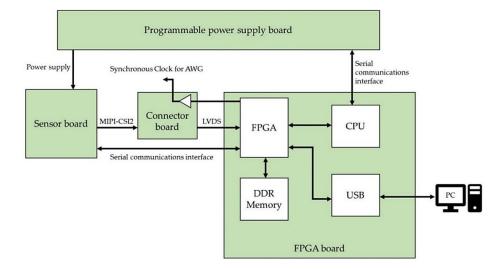

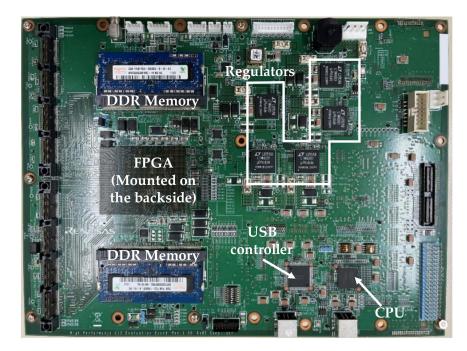

Applying previous work to confirm reproducible and accurate measurements [31], we constructed the evaluation system shown in Figure 9. The evaluation system consisted of two measurement instruments, four evaluation boards, and a PC. The instruments were used as input signals for evaluating the electrical characteristics of the ADC. The evaluation boards consisted of an image sensor board, a connector board, an FPGA board, and a programmable power supply board.

Figure 9. Evaluation system.

The operation of this system from start to finish of the evaluation is described in Figure 10. First, the power supply voltage settings and image sensor register data are read from the PC via USB. Next, the setting data read from the PC is stored in the field-programmable gate array (FPGA), and only the power supply setting data for the image sensor is passed to the central processing unit (CPU), which in turn sends the power supply voltage information to the programmable power supply board via the serial communications interface. The programmable power board executes the power-up sequence for the image sensor based on the received information. Then, register data for the image sensor is sent from the FPGA to the image sensor via the serial communications interface to write the initial settings to the image sensor. After the initial settings are completed, the image sensor is shifted into the operation mode to get data for optical evaluation or ADC electrical characterization. Digital data, which are the evaluation data output from the image sensor, are sent to the FPGA via the connector board. The FPGA accumulates the digital data on double data rate (DDR) memory, generates a RAW image when data accumulation for one frame is completed, and transfers the RAW image to the PC via USB.

During the operation mode period, the FPGA outputs synchronization clocks for the arbitrary waveform generator (AWG) and the image sensor, and the AWG output timing and the analog-to-digital (AD) conversion timing of the image sensor are synchronized. When the measurement data acquisition is completed, the programmable power supply board executes a power-down sequence to terminate the evaluation. The acquisition data of this evaluation system are RAW images for both optical evaluation and electrical characteristic evaluation. This brings the operating state of the image sensor during image acquisition, which is the normal operation of the image sensor, and the operating state

during ADC electrical characteristic evaluation closer, and makes it easier to reproduce the interference noise caused by ADC operation during the evaluation of electrical characteristics. Furthermore, since measurement data from all the several thousand image sensor ADCs can be obtained at once, if any ADCs are affected by operating noise, this can be easily confirmed because the result will be different from that of unaffected ADC outputs.

Figure 10. System overview.

The roles of each board are described below: The sensor board attaches the image sensor to be evaluated and provides access to input and output signals to the image sensor. This board is designed for both optical and electrical characterization. As shown in Figure 11, the socket of the sensor board has a hole for lens mounting, and a lens for optical evaluation can be attached there. On the other hand, in the case of evaluating the electrical characteristics of the ADC, the socket hole is plugged with a cap to prevent light from entering the image sensor, and the evaluation is performed using electrical signals from the measurement instruments connected with sub-miniature type A (SMA) cables.

Figure 11. Sensor board.

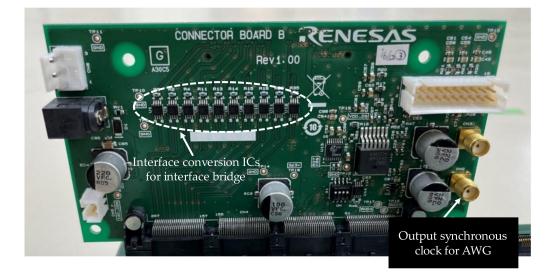

The connector board functions as an interface bridge as shown in Figure 12. Even if the sensor board and FPGA board use different high-speed interface standards, this connector board outputs signals that match the interface standard of the FPGA board. It also has the function of outputting a synchronization clock generated by the FPGA to the AWG.

Figure 12. Connector board.

The FPGA board shown in Figure 13 has three roles: The first is to create a RAW image from the digital data of the sensor output and then transfer the RAW image from the FPGA board to the PC via the USB interface. The second is to control the register settings of the image sensor via serial communication. The third role is to generate synchronization clocks for the image sensor and the AWG.

# Figure 13. FPGA board.

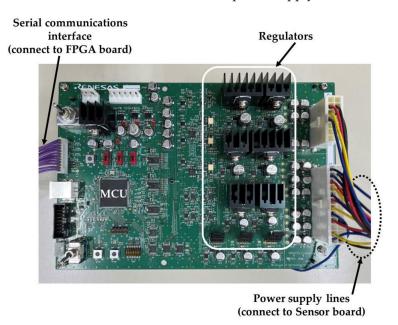

The programmable power supply board shown in Figure 14 generates the power supply voltage supplied to the image sensor. The generated voltage can be controlled on the order of millivolts. It is also possible to control the power-on and power-off of the supply power node on the order of milliseconds, allowing the power-up and power-

down sequences of the image sensor to be executed. Devices such as DC power supplies themselves can be noise sources and can be a factor in increasing environmental noise. Therefore, it is better to minimize their use. We used the programmable power supply board to reduce environmental noise. To relax physical placement restrictions between the sensor board and the programmable power supply board, the regular cables were used for the power supply lines, but ferrite beads and decoupling capacitors were placed on the back side of the sensor board to reduce power supply noise.

Figure 14. Programmable power supply board.

## 4. Measurement Results

The test chip features are shown in Figure 15. We fabricated the test chips using a 55 nm CIS process. The image sensor performance is capable of capturing video at 4 K/60 fps. The ADC resolution is 12-bit and the ADC power consumption per unit is  $9.8\mu$ W, achieving low power consumption.

|                            | Tec   |

|----------------------------|-------|

| Ріхеl Аггау<br>3840 x 2160 | Supp  |

|                            | Pix   |

|                            | Arr   |

|                            | Fra   |

| Column ADCs                | ADC   |

| Coldinii ADC3              | AD    |

|                            | ADC F |

|                            |       |

| Test Chip Features |                                               |  |  |

|--------------------|-----------------------------------------------|--|--|

| Technology         | 55 nm CMOS<br>1P5M BSI                        |  |  |

| Supply Voltage     | Pixel: 2.8 V<br>Analog: 2.8 V<br>Logic: 1.2 V |  |  |

| Pixel Size         | 1.85 µm × 1.85 µm                             |  |  |

| Array Size         | 3840 × 2160 (4K)                              |  |  |

| Frame Rate         | 60 fps                                        |  |  |

| ADC Resolution     | 12 bit                                        |  |  |

| ADC Clock          | 1.3 GHz                                       |  |  |

| ADC Power / Unit   | 9.8 uW                                        |  |  |

Figure 15. Test chip features.

Table 1 shows the electrical characteristics evaluation results of three test samples in the range of power supply voltage of  $\pm 5\%$  and temperatures of -25 °C, 27 °C, and 90 °C. Each test sample had 3840 column-parallel ADCs implemented, and the results in Table 1 show the best and worst values of the experimental results for all ADCs under all measurement conditions. The worst results of differential non-linearity (DNL) and integral non-linearity (INL) were 0.55 LSB (Sample 2) and 4.81 LSB (Sample 1), respectively, and the variability among three samples were 0.08 LSB and 2.65 LSB, respectively. Furthermore, the result of this accelerated column interference was 2.5 LSB, whereas the result for the conventional method was 5.0 LSB [7]. Therefore, the proposed technique reduced column interference by 50%. As for the accelerated column interference, the variability among three samples was 0.05 LSB.

Table 1. ADC electrical characteristics evaluation results.

| Measurement Items                           | Sample 1<br>(Best/Worst) | Sample 2<br>(Best/Worst) | Sample 3<br>(Best/Worst) |  |

|---------------------------------------------|--------------------------|--------------------------|--------------------------|--|

| Random noise [LSBrms]                       | 0.85/0.98                | 0.83/0.96                | 0.85/0.96                |  |

| Fixed pattern noise [LSB]                   | 0.28/0.36                | 0.28/0.36                | 0.28/0.37                |  |

| Min INL [LSB]                               | -1.27/-1.86              | -1.72/-2.07              | -1.55/-1.91              |  |

| Max INL [LSB]                               | 2.09/4.81                | 1.09/2.16                | 1.38/2.41                |  |

| Min DNL [LSB]                               | -0.35/-0.43              | -0.34/-0.44              | -0.36/-0.41              |  |

| Max DNL [LSB]                               | 0.38/0.51                | 0.39/0.55                | 0.46/0.53                |  |

| Min adjacent column INL<br>difference [LSB] | -0.92/-1.25              | -0.91/-1.23              | -0.91/-1.17              |  |

| Max adjacent column<br>INL difference [LSB] | 0.96/1.20                | 0.93/1.18                | 0.96/1.14                |  |

| Absolute gain error [dB]                    | 0.27/-0.70               | 0.22/-0.75               | 0.41/-0.61               |  |

| Cross talk [LSB]                            | 0.38/0.61                | 0.45/0.53                | 0.38/0.50                |  |

| Accelerated column<br>interference [LSB]    | 2.31/2.48                | 2.30/2.45                | 2.34/2.50                |  |

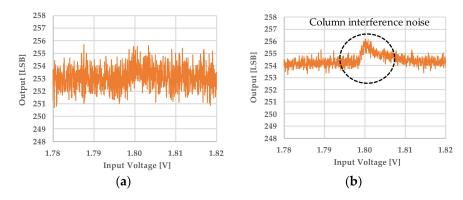

Figure 16 shows a comparison of acceleration column interference evaluation results between the conventional and proposed evaluation systems. The measurement results of the conventional system are noisy and the points where interference noise occurs are unclear. In contrast, the proposed system measures with lower noise, and the point where the interference noise occurs is clear.

**Figure 16.** Comparison of accelerated column interference evaluation results between the conventional and the proposed evaluation system. (**a**) shows the measurement result using the conventional evaluation system and (**b**) shows the result using the proposed evaluation system.

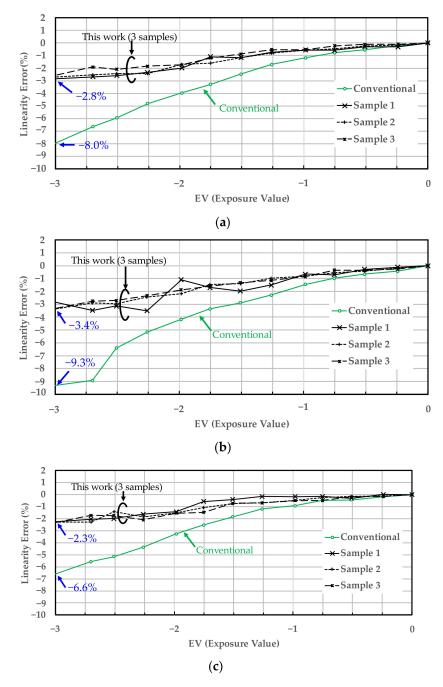

Next, we confirmed the improvement effect of the proposed circuit to reduce simultaneous operation noise. In low-light environments, linearity is degraded due to weak signals, which are recognized as vertical stripes in the image. Moreover, in low-light conditions, optical shot noise is low and column ADC operation noise is easily seen as vertical stripe noise (VSN) for each column. Therefore, we evaluated two items, sensor linearity under low-light conditions and VSN under low-light conditions, using three sample test chips fabricated on a 55 nm CIS process. We measured the sensor linearity within a supply voltage range of  $\pm 5\%$  and at room temperature only. Figure 17a–c show the results of sensor linearity evaluation under low-light conditions. The proposed circuit improved the sensor linearity error to -3.4% compared to -9.3%, the worst result of the conventional circuit. We confirmed that the sensor linearity error was reduced by 63% even if the improvement effect of this work was the smallest.

**Figure 17.** Comparison of sensor linearity error under low-light conditions between the conventional and proposed circuit. (**a**–**c**) show the evaluation result at typical, minimum, and maximum operating voltage, respectively.

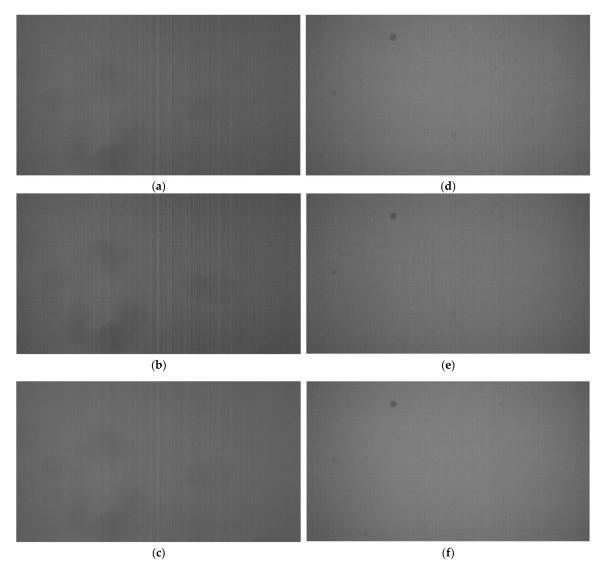

The results of VSN evaluation under low-light conditions are shown in Figure 18. In this figure, an image is an average of 10 RAW images. This averaging process reduces random noise, resulting in an image in which VSN is more emphasized. This VSN is not observed in complete darkness, but only in low-light conditions. On the other hand, it becomes invisible under bright conditions because the shot noise of the photodiode

increases. In the image of the conventional circuit, the vertical stripes are clearly visible near the center of the image, but in the image of the proposed circuit, the vertical stripes are almost invisible. The cause of this VSN is also the AD conversion error caused by the simultaneous operation noise as well as the sensor linearity, and since the proposed circuit can reduce the simultaneous operation noise, the AD conversion error is also reduced; as a result, the vertical stripe is no longer visible.

Figure 18. ( $\mathbf{a}$ - $\mathbf{c}$ ) are images taken under a low-light condition using conventional circuit. The operating voltages are as follows: ( $\mathbf{a}$ ) Typical operating voltage, ( $\mathbf{b}$ ) minimum operating voltage, and ( $\mathbf{c}$ ) maximum operating voltage. ( $\mathbf{d}$ - $\mathbf{f}$ ) are images taken with the proposed circuit under the same illumination as ( $\mathbf{a}$ - $\mathbf{c}$ ). The operating voltages are as follows: ( $\mathbf{d}$ ) typical operating voltage, ( $\mathbf{e}$ ) minimum operating voltage, and ( $\mathbf{f}$ ) maximum operating voltage. All images were enhanced with 384x digital gain.

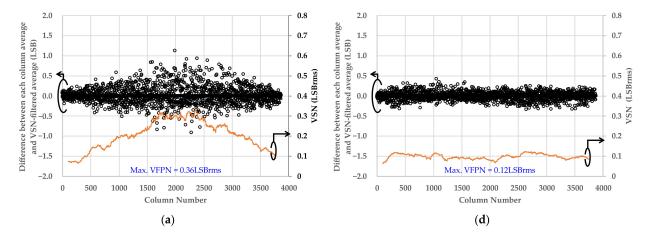

Figure 19 shows the difference between the average value of each column in Figure 18 and the average value filtered for the VSN component and its variations. The VSN filtered average was calculated by applying a median filter to each column average. The VSN was calculated from the variance of the difference for every 100 columns. The condition of maximum improvement was at the typical operating voltage in Figure 19, and the Max. VSNs of the conventional and proposed scheme were 0.36 LSB and 0.12 LSB, respectively. In this case, VSN was improved by 67%. On the other hand, the condition of minimum

improvement effect was at the maximum operating voltage in Figure 19, where the Max. VSNs of the conventional and proposed scheme were 0.26 LSB and 0.13 LSB, respectively. In this case, VSN was improved by 50%. This was worst case, and we confirmed that the proposed scheme improved VSN by at least 50%. Finally, Table 2 summarizes the performance of the implemented ADC compared with prior works with FoM [e-·pJ/step].

|                            | Unit         | This Work                               | [24]<br>Sensors 2020           | [32]<br>ISSCC 2016                             | [30]<br>JSSC 2012                      | [ <mark>33</mark> ]<br>TCAS-I 2019 | [34]<br>JSSC 2022               | [35]<br>JSSC 2019 |

|----------------------------|--------------|-----------------------------------------|--------------------------------|------------------------------------------------|----------------------------------------|------------------------------------|---------------------------------|-------------------|

| Process<br>Technology      | _            | 55 nm 1P5M<br>BSI                       | 90 nm                          | 45 nm 1P4M/<br>65 nm 1P5M                      | 180 nm<br>1P4M                         | 130 nm<br>1P3M<br>FSI              | 65 nm                           | 90 nm             |

| Power<br>supply            | V            | 2.8 (pixel,<br>analog)/1.2<br>(digital) | 2.8 (analog)/<br>1.5 (digital) | 2.5, 2.8<br>(analog)/<br>1.2, 2.5<br>(digital) | 3.3 (analog)/<br>1.8, 3.3<br>(digital) | 3.3 (analog)/<br>1.5 (digital)     | 2.8 (analog)/<br>1.05 (digital) | _                 |

| Pixel size                 | um^2         | 1.85 	imes 1.85                         | _                              | 1.1 	imes 1.1                                  | 7.5 	imes 7.5                          | $5.6 \times 5.6$                   | 4.95 	imes 4.95                 | 2.8 	imes 2.8     |

| Pixel array $(H \times V)$ | pixels       | 3840 × 2160                             | 960 × 720                      | 7728 × 4368                                    | 1032 × 1024                            | $1024 \times 128$                  | 1668 × 1364                     | 1232 × 952        |

| Frame rate                 | fps          | 60                                      | 35                             | 240                                            | 2.2 @<br>128smpls.                     | _                                  | 30/1200                         | 75                |

| Power con-<br>sumption     | W            | 0.3                                     | 0.03                           | 3                                              | 0.45                                   | 0.02                               | 0.12/0.60                       | _                 |

| ADC<br>architecture        | _            | Single Slope                            | 2–step<br>Single Slope         | 3–stage<br>cyclic based                        | Folding<br>integration<br>cyclic       | Flash TDC–<br>interpolated         | Single Slope                    | SAR               |

| ADC resolution             | bit          | 12                                      | 12                             | 12                                             | 13–19                                  | 12                                 | 10                              | 10.7              |

| ADC power consumption      | uW/column    | 9.8                                     | 6.35                           | 120                                            | _                                      | 177                                | 23.9                            | 2.1               |

| ADC DNL                    | LSB @ 12 bit | +0.55/-0.44<br>@wst (*1)                | +4.25/-1.00                    | +0.82/-0.88                                    | _                                      | +1.1/-0.4                          | _                               | +0.39/-0.36       |

| ADC INL                    | LSB @ 12 bit | +4.81/-2.07<br>@wst (*1)                | +5.73/-7.30                    | +1.04/-11.75                                   | _                                      | +5.8/-8.2                          | _                               | +2.31/-0.79       |

| FPN                        | uVrms        | 87 @wst (*1)                            | _                              | _                                              | 36                                     | _                                  | _                               | 29                |

| Random<br>noise            | uVrms        | 273                                     | 472                            | 414                                            | 65 @<br>128smpls.                      | 477                                | 294                             | 407.75            |

| FoM (*2)                   | e-∙pJ/step   | 0.32                                    | 0.56                           | 0.33                                           | 0.35                                   | _                                  | 0.52                            | _                 |

Table 2. Performance comparison.

(\*1) wst: worst value of power supply  $\pm 5\%$ , temperature  $-25^{\circ}C$  to  $90^{\circ}C$ , and 3 samples; (\*2) FoM: (power × noise)/(pixels × fps × 2°bit).

Figure 19. Cont.

**Figure 19.** (**a**–**c**) show the VSN under the low-light condition calculated from images in Figure 18a–c taken with the conventional circuit. The operating voltages are as follows: (**a**) Typical operating voltage, (**b**) minimum operating voltage, and (**c**) maximum operating voltage, respectively. (**d**–**f**) show the VSN under the low-light condition calculated from the Figure 18d–f taken by the proposed circuit. The operating voltages are as follows: (**d**) typical operating voltage, (**e**) minimum operating voltage, and (**f**) maximum operating voltage, respectively. All graph data are values of digital gain  $\times 1$ .

### 5. Conclusions

We proposed circuit techniques, RUSH current compensation, and timing shift ADC to realize a high-sensitivity image sensor. The proposed circuits reduced AD conversion errors due to simultaneous operating noise and decreased sensor linearity degradation even under low-light conditions with few optical signals. A lower-noise evaluation system was needed to measure our high-sensitivity image sensor; since measurement instruments such as DC power supplies can also be noise sources, the proposed evaluation system was configured with the minimum number of measurement instruments. To confirm these proposals, test chips were fabricated using a 55 nm CIS process and the low-light characteristics were measured. The proposed technique improved the low-light linearity error and column interference noise (RUSH current) by 63% and 50%, respectively. As for the high-accuracy evaluation system, we confirmed that the inter-sample variation of column interference was 0.05 LSB.

**Author Contributions:** Conceptualization, F.M.; methodology, N.K.; validation, N.K. and S.O.; investigation, F.M. and M.I.; writing—original draft preparation, N.K. and F.M.; writing—review and editing, M.I.; visualization, N.K.; supervision, M.I.; project administration, M.I. All authors have read and agreed to the published version of the manuscript.

Funding: This research received no external funding.

Institutional Review Board Statement: Not applicable.

Informed Consent Statement: Not applicable.

Data Availability Statement: Not applicable.

**Conflicts of Interest:** The authors declare no conflict of interest.

## References

- 1. Schanz, M.; Nitta, C.; Bussmann, A.; Hosticka, B.J.; Wertheimer, R.K. A high-dynamic-range CMOS image sensor for automotive applications. *IEEE J. Solid-State Circuits* 2000, *35*, 932–938. [CrossRef]

- Okura, S.; Nishikido, O.; Sadanaga, Y.; Kosaka, Y.; Araki, N.; Ueda, K. A 3.7 M-Pixel 1300-fps CMOS Image Sensor With 5.0 G-Pixel/s High-Speed Readout Circuit. *IEEE J. Solid-State Circuits* 2015, 50, 1016–1024. [CrossRef]

- Seo, M.-W.; Takasawa, T.; Yasutomi, K.; Kagawa, K.; Kawahito, S. A low-noise high-sensitivity CMOS image sensor for scientific and industrial applications. In Proceedings of the SENSORS, 2014 IEEE, Valencia, Spain, 2–5 November 2014; pp. 2163–2166. [CrossRef]

- 4. Bong, K.; Choi, S.; Kim, C.; Han, D.; Yoo, H.-J. A Low-Power Convolutional Neural Network Face Recognition Processor and a CIS Integrated With Always-on Face Detector. *IEEE J. Solid-State Circuits* **2017**, *53*, 115–123. [CrossRef]

- Le, V.L.; Yoo, T.; Kim, J.E.; Baek, K.-H.; Kim, T.T.-H. A 213.7-μW Gesture Sensing System-On-Chip With Self-Adaptive Motion Detection and Noise-Tolerant Outer-most-Edge-Based Feature Extraction in 65 nm. *IEEE Solid-State Circuits Lett.* 2019, 2, 123–126. [CrossRef]

- Park, I.; Jo, W.; Park, C.; Park, B.; Cheon, J.; Chae, Y. A 640 × 640 Fully Dynamic CMOS Image Sensor for Always-On Object Recognition. In Proceedings of the 2019 Symposium on VLSI Circuits, Kyoto, Japan, 9–14 June 2019; pp. C214–C215.

- Morishita, F.; Kato, N.; Okubo, S.; Toi, T.; Hiraki, M.; Otani, S.; Abe, H.; Shinohara, Y.; Kondo, H. A CMOS Image Sensor and an AI Accelerator for Realizing Edge-Computing-Based Surveillance Camera Systems. In Proceedings of the 2021 Symposium on VLSI Circuits, Kyoto, Japan, 13–19 June 2021; pp. 1–2. [CrossRef]

- Song, H.; Oh, S.; Salinas, J.; Park, S.-Y.; Yoon, E. A 5.1 ms Low-Latency Face Detection Imager with In-Memory Charge-Domain Computing of Machine-Learning Classifiers. In Proceedings of the 2021 Symposium on VLSI Circuits, Kyoto, Japan, 13–19 June 2021; pp. 1–2. [CrossRef]

- Kim, D.; Lee, S.; Park, D.; Piao, C.; Park, J.; Ahn, Y.; Cho, K.; Shin, J.; Song, S.M.; Kim, S.-J.; et al. Indirect Time-of-Flight CMOS Image Sensor With On-Chip Background Light Cancelling and Pseudo-Four-Tap/Two-Tap Hybrid Imaging for Motion Artifact Suppression. *IEEE J. Solid-State Circuits* 2020, 55, 2849–2865. [CrossRef]

- Keel, M.-S.; Jin, Y.-G.; Kim, Y.; Kim, D.; Kim, Y.; Bae, M.; Chung, B.; Son, S.; Kim, H.; An, T.; et al. A VGA Indirect Time-of-Flight CMOS Image Sensor With 4-Tap 7 μm Global-Shutter Pixel and Fixed-Pattern Phase Noise Self-Compensation. *IEEE J. Solid-State Circuits* 2019, 55, 889–897. [CrossRef]

- Niclass, C.; Soga, M.; Matsubara, H.; Ogawa, M.; Kagami, M. A 0.18 μm CMOS SoC for a 100 m-range 10 fps 20096-pixel time-of-flight depth sensor. In Proceedings of the 2013 IEEE International Solid-State Circuits Conference Digest of Technical Papers, San Francisco, CA, USA, 17–21 February 2013; pp. 488–489. [CrossRef]

- Al Abbas, T.; Almer, O.; Hutchings, S.W.; Erdogan, A.T.; Gyongy, I.; Dutton, N.A.; Henderson, R.K. A 128 × 120 5-Wire 1.96 mm<sup>2</sup> 40 nm/90 nm 3D Stacked SPAD Time Resolved Image Sensor SoC for Microendoscopy. In Proceedings of the 2019 Symposium on VLSI Circuits, Kyoto, Japan, 9–14 June 2019. [CrossRef]

- Jang, J.; Lee, J.; Lee, K.-R.; Lee, J.; Kim, M.; Lee, Y.; Bae, J.; Yoo, H.-J. A Four-Camera VGA-Resolution Capsule Endoscope System With 80-Mb/s Body Channel Communication Transceiver and Sub-Centimeter Range Capsule Localization. *IEEE J. Solid-State Circuits* 2018, 54, 538–549. [CrossRef]

- Zhang, M.; Bermak, A.; Li, X.; Wang, Z. A low power CMOS image sensor design for wireless endoscopy capsule. In Proceedings of the 2008 IEEE Biomedical Circuits and Systems Conference, Baltimore, MD, USA, 20–22 November 2008; pp. 397–400. [CrossRef]

- Sakakibara, M.; Ogawa, K.; Sakai, S.; Tochigi, Y.; Honda, K.; Kikuchi, H.; Wada, T.; Kamikubo, Y.; Miura, T.; Nakamizo, M.; et al. A 6.9-μm Pixel-Pitch Back-Illuminated Global Shutter CMOS Image Sensor With Pixel-Parallel 14-Bit Subthreshold ADC. *IEEE J.* Solid-State Circuits 2018, 53, 3017–3025. [CrossRef]

- Seo, M.-W.; Chu, M.; Jung, H.-Y.; Kim, S.; Song, J.; Lee, J.; Kim, S.-Y.; Lee, J.; Byun, S.-J.; Bae, D.; et al. A 2.6 e-rms Low-Random-Noise, 116.2 mW Low-Power 2-Mp Global Shutter CMOS Image Sensor with Pixel-Level ADC and In-Pixel Memory. In Proceedings of the 2021 Symposium on VLSI Technology, Kyoto, Japan, 13–19 June 2021.

- 17. Han, J.; Cacho-Soblechero, M.; Douthwaite, M.; Georgiou, P. A Digital ISFET Sensor with In-Pixel ADC. In Proceedings of the 2021 IEEE International Symposium on Circuits and Systems (ISCAS), Daegu, Korea, 22–28 May 2021; pp. 1–5. [CrossRef]

- Goto, M.; Honda, Y.; Watabe, T.; Hagiwara, K.; Nanba, M.; Iguchi, Y.; Saraya, T.; Kobayashi, M.; Higurashi, E.; Toshiyoshi, H.; et al. Quarter Video Graphics Array Digital Pixel Image Sensing With a Linear and Wide-Dynamic-Range Response by Using Pixel-Wise 3-D Integration. *IEEE Trans. Electron. Devices* 2018, 66, 969–975. [CrossRef]

- Oike, Y.; Akiyama, K.; Hung, L.D.; Niitsuma, W.; Kato, A.; Sato, M.; Kato, Y.; Nakamura, W.; Shiroshita, H.; Sakano, Y.; et al. 8.3 M-Pixel 480-fps Global-Shutter CMOS Image Sensor with Gain-Adaptive Column ADCs and Chip-on-Chip Stacked Integration. *IEEE J. Solid-State Circuits* 2017, 52, 985–993. [CrossRef]

- Park, I.; Park, C.; Cheon, J.; Chae, Y. 5.4 A 76mW 500fps VGA CMOS Image Sensor with Time-Stretched Single-Slope ADCs Achieving 1.95 e<sup>-</sup> Random Noise. In Proceedings of the 2019 IEEE International Solid-State Circuits Conference—(ISSCC), San Francisco, CA, USA, 17–21 February 2019; pp. 100–102. [CrossRef]

- 21. Nie, K.; Zha, W.; Shi, X.; Li, J.; Xu, J.; Ma, J. A Single Slope ADC With Row-Wise Noise Reduction Technique for CMOS Image Sensor. *IEEE Trans. Circuits Syst. I Regul. Pap.* **2020**, *67*, 2873–2882. [CrossRef]

- Wei, J.; Li, X.; Sun, L.; Li, D. A 63.2 μW 11-Bit Column Parallel Single-Slope ADC with Power Supply Noise Suppression for CMOS Image Sensors. In Proceedings of the 2020 IEEE International Symposium on Circuits and Systems (ISCAS), Seville, Spain, 12–14 October 2020; pp. 1–4. [CrossRef]

- Saito, W.; Iizuka, Y.; Kato, N.; Otake, R.; Morishita, F. A Low Noise and Linearity Improvement CMOS Image Sensor for Surveillance Camera with Skew-Relaxation Local Multiply Circuit and On-Chip Testable Ramp Generator. In Proceedings of the 2021 IEEE Asian Solid-State Circuits Conference (A-SSCC), Busan, Korea, 7–10 November 2021; pp. 1–3. [CrossRef]

- Park, H.; Yu, C.; Kim, H.; Roh, Y.; Burm, J. Low Power CMOS Image Sensors Using Two Step Single Slope ADC With Bandwidth-Limited Comparators & Voltage Range Extended Ramp Generator for Battery-Limited Application. *IEEE Sens. J.* 2019, 20, 2831–2838. [CrossRef]

- Elmezayen, M.R.; Wu, B.; Ay, S.U. Single-Slope Look-Ahead Ramp ADC for CMOS Image Sensors. *IEEE Trans. Circuits Syst. I Regul. Pap.* 2020, 67, 4484–4493. [CrossRef]

- Kim, H.-J. 11-bit Column-Parallel Single-Slope ADC With First-Step Half-Reference Ramping Scheme for High-Speed CMOS Image Sensors. *IEEE J. Solid-State Circuits* 2021, 56, 2132–2141. [CrossRef]

- Xie, S.; Theuwissen, A. A 10 Bit 5 MS/s Column SAR ADC With Digital Error Correction for CMOS Image Sensors. *IEEE Trans. Circuits Syst. II Express Briefs* 2019, 67, 984–988. [CrossRef]

- Kawahito, S.; Park, J.-H.; Isobe, K.; Shafie, S.; Iida, T.; Mizota, T. A CMOS Image Sensor Integrating Column-Parallel Cyclic ADCs with On-Chip Digital Error Correction Circuits. In Proceedings of the 2008 IEEE International Solid-State Circuits Conference—Digest of Technical Papers, San Francisco, CA, USA, 3–7 February 2008; pp. 56–595. [CrossRef]

- Okada, C.; Uemura, K.; Hung, L.; Matsuura, K.; Moue, T.; Yamazaki, D.; Kodama, K.; Okano, M.; Morikawa, T.; Yamashita, K.; et al. 7.6 A High-Speed Back-Illuminated Stacked CMOS Image Sensor with Column-Parallel kT/C-Cancelling S&H and Delta-Sigma ADC. In Proceedings of the 2021 IEEE International Solid-State Circuits Conference (ISSCC), San Francisco, CA, USA, 13–22 February 2021; pp. 116–118. [CrossRef]

- Seo, M.-W.; Suh, S.-H.; Iida, T.; Takasawa, T.; Isobe, K.; Watanabe, T.; Itoh, S.; Yasutomi, K.; Kawahito, S. A Low-Noise High Intrascene Dynamic Range CMOS Image Sensor With a 13 to 19b Variable-Resolution Column-Parallel Folding-Integration/Cyclic ADC. *IEEE J. Solid-State Circuits* 2012, 47, 272–283. [CrossRef]

- Morishita, F.; Otsuka, M.; Saito, W. An ADC Test Technique With Dual-Path/Multi-Functional Fine Pattern Generator Realizing High Accuracy Measurement for CMOS Image Sensor. In Proceedings of the 2020 IEEE 29th Asian Test Symposium (ATS), Penang, Malaysia, 23–26 November 2020; pp. 1–6. [CrossRef]

- Arai, T.; Yasue, T.; Kitamura, K.; Shimamoto, H.; Kosugi, T.; Jun, S.; Aoyama, S.; Hsu, M.-C.; Yamashita, Y.; Sumi, H.; et al. 6.9 A 1.1 μm 33 M pixel 240 fps 3D-stacked CMOS image sensor with 3-stage cyclic-based analog-to-digital converters. In Proceedings of the 2016 IEEE International Solid-State Circuits Conference (ISSCC), San Francisco, CA, USA, 31 January–4 February 2016; pp. 126–128. [CrossRef]

- Levski, D.; Wany, M.; Choubey, B. A 1-μs Ramp Time 12-bit Column-Parallel Flash TDC-Interpolated Single-Slope ADC with Digital Delay-Element Calibration. *IEEE Trans. Circuits Syst. I Regul. Pap.* 2018, 66, 54–67. [CrossRef]

- Seo, M.-W.; Chu, M.; Jung, H.-Y.; Kim, S.; Song, J.; Bae, D.; Lee, S.; Lee, J.; Kim, S.-Y.; Lee, J.; et al. 2.45 e-RMS Low-Random-Noise, 598.5 mW Low-Power, and 1.2 kfps High-Speed 2-Mp Global Shutter CMOS Image Sensor With Pixel-Level ADC and Memory. IEEE J. Solid-State Circuits 2022, 57, 1125–1137. [CrossRef]

- Janbu, O.; Johansson, R.; Martinussen, T.; Solhusvik, J. A 1.17-Megapixel CMOS Image Sensor With 1.5 A/D Conversions per Digital CDS Pixel Readout and Four In-Pixel Gain Steps. *IEEE J. Solid-State Circuits* 2019, 54, 2568–2578. [CrossRef]