Letter

# Design of an Ultrasound Transceiver ASIC with a Switching-Artifact Reduction Technique for 3D Carotid Artery Imaging

Taehoon Kim <sup>1,\*</sup>, Fabian Fool <sup>2</sup>, Djalma Simoes dos Santos <sup>2</sup>, Zu-Yao Chang <sup>1</sup>, Emile Noothout <sup>2</sup>, Hendrik J. Vos <sup>2,3</sup>, Johan G. Bosch <sup>3</sup>, Martin D. Verweij <sup>2,3</sup>, Nico de Jong <sup>2,3</sup> and Michiel A. P. Pertijs <sup>1</sup>

- Electronic Instrumentation Laboratory, Delft University of Technology, 2628 CD Delft, The Netherlands; Z.Y.Chang@tudelft.nl (Z.-Y.C.); M.A.P.Pertijs@tudelft.nl (M.A.P.P.)

- Laboratory of Medical Imaging, Department of Imaging Physics, Delft University of Technology, 2628 CJ Delft, The Netherlands; F.Fool@tudelft.nl (F.F.); D.SimoesdosSantos@tudelft.nl (D.S.d.S.); E.C.Noothout@tudelft.nl (E.N.); h.vos@erasmusmc.nl (H.J.V.); M.D.Verweij@tudelft.nl (M.D.V.); Nicolaas.deJong@tudelft.nl (N.d.J.)

- Department Biomedical Engineering, Thoraxcenter, Erasmus Medical Center, 3015 GD Rotterdam, The Netherlands; j.bosch@erasmusmc.nl

- \* Correspondence: T.Kim@tudelft.nl; Tel.: +31-06-5597-5502

Abstract: This paper presents an ultrasound transceiver application-specific integrated circuit (ASIC) directly integrated with an array of  $12 \times 80$  piezoelectric transducer elements to enable next-generation ultrasound probes for 3D carotid artery imaging. The ASIC, implemented in a 0.18  $\mu$ m high-voltage Bipolar-CMOS-DMOS (HV BCD) process, adopted a programmable switch matrix that allowed selected transducer elements in each row to be connected to a transmit and receive channel of an imaging system. This made the probe operate like an electronically translatable linear array, allowing large-aperture matrix arrays to be interfaced with a manageable number of system channels. This paper presents a second-generation ASIC that employed an improved switch design to minimize clock feedthrough and charge-injection effects of high-voltage metal-oxide-semiconductor field-effect transistors (HV MOSFETs), which in the first-generation ASIC caused parasitic transmissions and associated imaging artifacts. The proposed switch controller, implemented with cascaded non-overlapping clock generators, generated control signals with improved timing to mitigate the effects of these non-idealities. Both simulation results and electrical measurements showed a 20 dB reduction of the switching artifacts. In addition, an acoustic pulse-echo measurement successfully demonstrated a 20 dB reduction of imaging artifacts.

**Keywords:** 3D ultrasound imaging; high-voltage (HV) switches; matrix transducers; ultrasound application-specific integrated circuit (ASIC); clock feedthrough; charge injection

Citation: Kim, T.; Fool, F.; dos Santos, D.S.; Chang, Z.-Y.; Noothout, E.; Vos, H.J.; Bosch, J.G.; Verweij, M.D.; de Jong, N.; Pertijs, M.A.P.; et al. Design of an Ultrasound Transceiver ASIC with a Switching-Artifact Reduction Technique for 3D Carotid Artery Imaging. Sensors 2021, 21, 150. https://doi.org/10.3390/s21010150

Received: 30 November 2020 Accepted: 25 December 2020 Published: 29 December 2020

**Publisher's Note:** MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Copyright: © 2020 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

# 1. Introduction

Real-time 3D ultrasound imaging is an essential technique for the accurate assessment of carotid artery disease by measuring blood flow, plaque deformation, and pulse wave velocity [1–4]. To realize this, the next generation of ultrasound probes require matrix transducer arrays with thousands of elements to cover a sufficiently large aperture (>400 mm²). It is possible to build a matrix array with such a high number of elements, but making electrical connections to all the elements is highly challenging since conventional imaging systems have a limited number of channels. ✓

This issue can be addressed by integrating application-specific integrated circuits (ASICs) into the probe to reduce the number of electrical connections via cables to the imaging system. Various approaches to interface such large-aperture matrix transducer arrays using a reduced number of cables have been reported, such as receive sub-array beamform-

Sensors **2021**, 21, 150 2 of 13

ing [5–8], programmable high-voltage (HV) pulsers [9–14], switch matrices [15,16], row-by-row scanning schemes [12,14], and row- or column-parallel connection schemes [13].

We previously reported a first-generation transceiver ASIC with a row-level architecture for both receive (RX) and transmit (TX) channels [17]. This ASIC consists of  $24 \times 40$  element-level HV switches and control logic that allows selected transducer elements in each row to be connected to a TX and RX channel of an imaging system. The element-level circuits are laid out in a pitch-matched fashion and connect directly via bondpads to transducer elements stacked on top of the chip. Although the functionality of this ASIC has been successfully demonstrated in a 3D imaging experiment, noticeable imaging artifacts associated with parasitic transmissions generated by HV switch actuation at the TX to RX transition and vice versa were found. In particular, thousands of switches actuate simultaneously in a full-aperture selection for plane wave transmission, making this problem more serious. The parasitic transmissions originate from non-idealities of the HV MOSFETs in the switch circuits, i.e., clock feedthrough and charge injection, generating switching transients on the transducer elements.

Charge injection and clock feedthrough in low-voltage analog complementary metal–oxide–semiconductor (CMOS) circuits have been discussed extensively in the literature [18], and several techniques to cancel their effects have been reported, such as dummy transistor compensation [19,20] and differential clock feedthrough attenuation [21]. However, these techniques are not directly applicable in this design because the HV laterally diffused metal oxide semiconductor (LDMOS) transistors used for HV switches are much larger than low-voltage transistors. As a result, these solutions, which rely on additional transistors, would make die area occupied by the element-level switch circuit too large in comparison to the size of the transducer elements. Recently, one approach, linearized control of the gate voltage of a HV MOSFET, has been reported to address this issue in an ASIC design with large aperture transducer arrays for ultrasound imaging applications [22].

In this work, as an alternative, we propose a second-generation transceiver ASIC focusing on minimizing the effects due to non-idealities of the HV MOSFETs, the root cause of the mentioned imaging artifacts. To achieve this, we propose a new HV switch controller that generates control signals for the HV switches with improved timing to alleviate the effects of their non-idealities. In this design, a current discharging path from the transducer element to the ground is created at the TX and RX switching moments. Consequently, this leads to significantly reduced peak-to-peak amplitudes of the switching transients.

This paper is structured as follows. Section 2 describes the materials and methods of this work, which comprise a system overview in Section 2.1, the architecture of the designed ASIC in Section 2.2, the implementation of the element-level switch circuit and an analysis of the associated switching transients due to non-idealities of the HV MOSFETs in Section 2.3, the design of a switch controller with a switching-artifact reduction technique in Section 2.4, and its validation in simulation in Section 2.5. Section 3 describes the measurement results and discussion, explaining the experimental prototype used to validate the design in Section 3.1, presenting its electrical verification in Section 3.2, and showing reduced imaging artifacts in Section 3.3. Finally, the paper is concluded in Section 4.

# 2. Materials and Methods

#### 2.1. System Overview

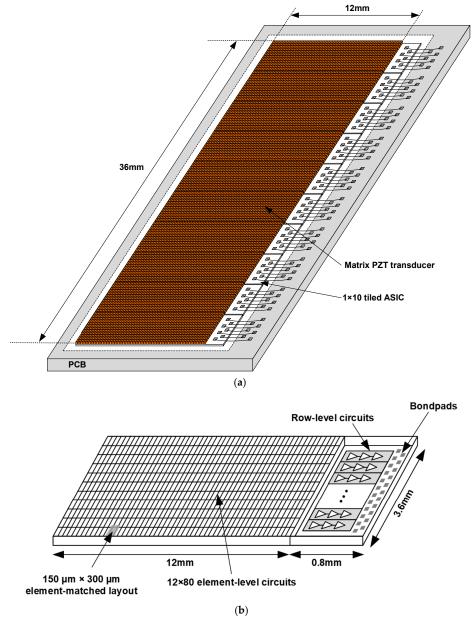

The size of the matrix transducer to cover an aperture sufficiently large enough for carotid artery imaging is  $36 \times 12 \text{ mm}^2$ . To facilitate the realization of a full-sized array, we designed the second-generation ASIC via a MLM (multi-layer mask) full-wafer fabrication process. Compared to our previous work [17], the row pitch was increased from 150 to 300  $\mu$ m while keeping the center frequency as it was. Thus, the number of rows in the ASIC was reduced from 24 to 12 so that the density of the wire bonds that electrically connect the ASIC to a printed circuit board (PCB) was also significantly reduced. This modification of physical dimensions enabled us to wire bond more reliably, which is one of the main

Sensors **2021**, 21, 150 3 of 13

challenges of the first-generation ASIC. On the other hand, the number of columns per ASIC increased from 40 to 80, which allowed us to implement the targeted aperture by tiling  $1\times 10$  ASICs, as shown in Figure 1a. This increased number of columns provided an important additional advantage compared to the previous work with  $2\times 10$  ASICs tiled, since wire-bond connections only have to be made on one side of the tiled array.

As shown in Figure 1b, each of the ASICs had a die size of  $3.6 \times 12.8 \text{ mm}^2$ , and interfaced with an array of  $12 \times 80$  (rows  $\times$  columns) transducer elements through element-level and row-level circuits. Each pitch-matched element-level circuit was connected to the corresponding transducer element via a bondpad. Bondpads on the periphery of each ASIC were arranged in two columns. The inner column connected row-level TX and RX signals to an imaging system. Bondpads of the outer column made connections for digital control signals as well as analog and digital power supplies.

**Figure 1.** (a) Overview of the proposed matrix transducer on tiled application-specific integrated circuits (ASICs). (b) Overview of a single tile consisting of  $12 \times 80$  transducer elements on top of an ASIC with  $12 \times 80$  element-level switches and row-level circuits.

Sensors **2021**, 21, 150 4 of 13

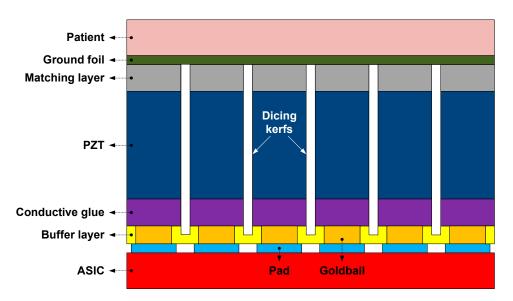

In the same way as the first-generation ASIC, the piezoelectric layer (PZT)-on-CMOS integration scheme illustrated in Figure 2 [23] was adopted to build the transducer array on top of the ASICs. To electrically connect the circuitry on the ASIC to the transducer elements, we formed gold bumps on top of the ASIC bondpads using a wire-bonding tool. This was done in a matrix pattern with the same pitch as the transducer array. A nonconductive epoxy buffer layer was then deposited, filling the gaps between the gold. After this, the buffer layer was ground down to expose the gold, thus providing reliable electrical contacts for the transducer elements. On top of the epoxy layer, the acoustic stack consisting of a PZT and a matching layer was constructed. The conductive glue layer created the electrical connection between contacts and the electrode on the back-side of the piezoelectric ceramic. After that, the stack was diced into the desired 150  $\times$  300  $\mu m$  pitch array pattern using a diamond saw. The dicing kerfs were air-filled to minimize the crosstalk between elements. Finally, the array was covered with an aluminum foil that formed the elements' common ground electrode.

Figure 2. Cross-sectional view of the transducer array mounted on top of the ASIC.

## 2.2. ASIC Architecture

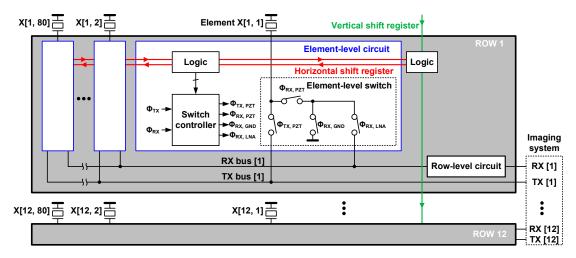

Figure 3 shows the top-level architecture of the second-generation ASIC. The 80 elements in each row of the matrix shared a row-level RX and TX bus to reduce channel count by a factor of 80. Even with  $1\times 10$  tiled ASICs, the total number of RX and TX channels was 240, which could be managed by an imaging system. Each transducer element was connected to the RX bus or the TX bus through a programmable element-level circuit. The RX bus was associated with a shared row-level circuit, which amplified the received echo signals, filtered out-of-band noise, and drove the connection to the imaging system.

Ahead of starting successive transmit/receive cycles, we needed to program the ASIC. Row-level logic was used to select one of the various element-selection modes supported by the ASIC to implement a specific imaging scheme and set the gain of the row-level circuit. This logic was programmed through a vertical shift registers (VSR) that was loaded during the programming phase. Each element was associated with logic allowing us to change rapidly between transmit/receive cycles the selection of active elements for a specific transmit and/or receive cycle. This element-level logic was pre-loaded through a horizontal shift register (HSR) during the programming phase. The switch controller received low-voltage digital signals ( $\Phi_{TX}$  and  $\Phi_{RX}$ ) from a field-programmable gain array (FPGA) and generated 5-V control signals ( $\Phi_{TX,PZT}$ ,  $\Phi_{RX,PZT}$ ,  $\Phi_{RX,GND}$ , and  $\Phi_{RX,LNA}$ ), according to the pre-loaded data, to drive the element-level switch circuit. In this design, the switch controller was implemented using a non-overlapping clock generator to minimize the non-idealities of HV devices introduced above in the switch circuit.

Sensors **2021**, 21, 150 5 of 13

Figure 3. Block diagram of the second-generation ASIC.

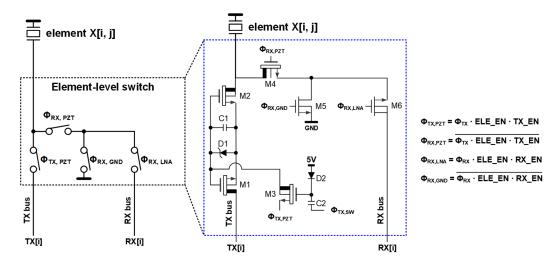

#### 2.3. Element-Level Switch Circuit and Non-Idealities

Figure 4 shows the circuit diagram of the element-level switches implemented in the first-generation ASIC. The HV switches were needed to enable HV pulse transmission while keeping a more compact implementation and less power consumption. The control signals were generated by simple combinational logic from the TX/RX phases ( $\Phi_{TX}$  and  $\Phi_{RX}$ ) and three enable bits (ELE\_EN[i, j], TX\_EN[i, j], and RX\_EN[i, j]), which were preloaded via the HSR in the programming phase. The ELE\_EN bit determined whether an element was enabled (high) or disabled (low). If a certain element was disabled, it was excluded from participating in imaging and connected to the ground via transistors M5 and M6. This helped to prevent the signal of disabled elements from coupling to the RX bus and capacitive coupling from the TX bus to the disabled elements in the TX phase  $\Phi_{TX}$ . For the enabled elements, the remaining two bits, TX\_EN and RX\_EN, determined whether they participate in transmission and/or reception.

**Figure 4.** Simplified circuit diagram of the element-level switch and the combinational logic equation, implemented as the switch controller, proposed in [17].

During the TX phase  $\Phi_{TX}$ , the row-level TX bus, TX[i] was connected to the element if ELE\_EN[i, j] and TX\_EN[i, j] were high. Two back-to-back n-type HV LDMOS transistors (M1 and M2), driven by  $\Phi_{TX,PZT}$ , allowed an external imaging system to send a unipolar pulse with a peak value up to 65 V. To turn on M1 and M2, we charged a bootstrap capacitor C1 connected between their source and gate through M3 by making  $\Phi_{TX,SW}$  high at the

Sensors **2021**, 21, 150 6 of 13

beginning of  $\Phi_{TX}$ . Soon after that,  $\Phi_{TX,SW}$  went low to turn off M3, keeping M1 and M2 on and allowing them to swing up with the transmit HV pulses on the TX bus. To provide a sufficiently high gate voltage to turn on M1 and M2, we gave the bootstrap capacitor C1 a relatively large value of 7.2 pF in this design. At the end of  $\Phi_{TX}$ , C1 was discharged by pulling down the source of M3 so that M1 and M2 were turned off. During the RX phase  $\Phi_{RX}$ , transistors M4 and M6 connected the element to the RX bus if ELE\_EN[i, j] and RX\_EN[i, j] were high.

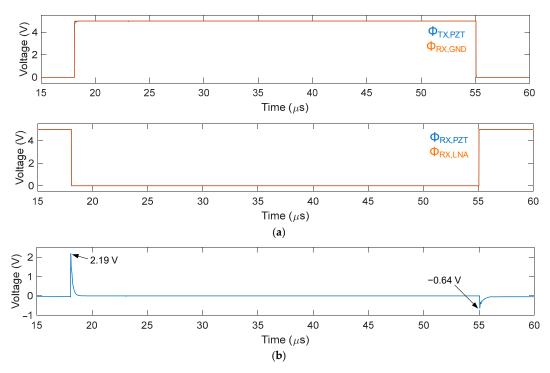

As described earlier in Section 1, an important consideration in this design is minimizing the impact of non-idealities, clock feedthrough, and charge injection of the HV switches, which generate switching glitches on the transducer element at the TX to RX transition and vice versa. This problem eventually leads to visible imaging artifacts. Figure 5a shows simulated waveforms of the control signals driving the element-level switch transistors. Even without a transmitted pulse, noticeable switching glitches appear on the element, as shown in Figure 5b. The peak amplitudes of these undesired glitches at the RX to TX transition and vice versa were 2.19 V and -0.64 V, respectively. This amplitude, in the volt range, led to visible imaging artifacts, even when applying a high-voltage transmit pulse with an amplitude of tens of volts.

**Figure 5.** Simulated waveforms of the element-level circuit implemented in the first-generation ASIC (Figure 4): (a) control signals driving the element-level switch circuit and (b) the switching transients on the transducer element.

#### 2.4. Proposed Switch Controller

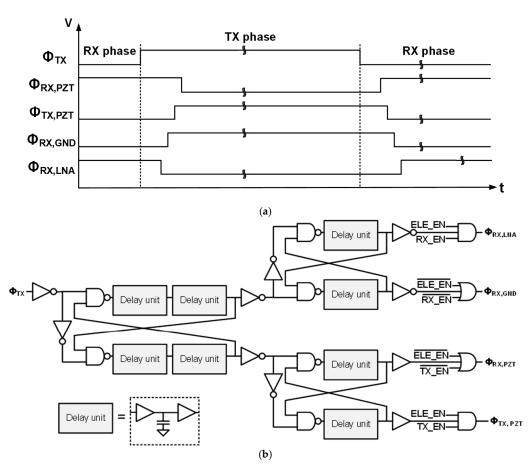

To minimize the switching transients discussed in the previous section, we proposed a new timing diagram, shown in Figure 6a, of the switch control signals. At the transition from RX to TX, the RX bus was first disconnected from the element by making  $\Phi_{RX, LNA}$  low while  $\Phi_{RX, PZT}$  remained high. Subsequently, M5 was turned on by making  $\Phi_{RX, GND}$  high; thus, a low-impedance discharging path from the element to ground was created before actuating M1 and M2 associated with the HV TX switch. Thus, when  $\Phi_{TX, PZT}$  was made high, the clock feedthrough-induced current could flow to the ground through transistor M5 instead of to the element. Finally, when  $\Phi_{RX, PZT}$  was made low, the charge injection error from M4 could be absorbed to both ground and the low-impedance output of the pulser. This switching sequence reduced the peak amplitude of the switching transients

Sensors 2021, 21, 150 7 of 13

significantly at the transition of RX to TX. Although M6, a 5 V device, was switching without a discharging path to the ground, the associated transient was not critical because M6 was much smaller than the high-voltage devices.

**Figure 6.** (a) The proposed timing diagram of the control signals to minimize the switching transients and (b) implementation of the switch controller to generate such signals.

Conversely, at the transition of TX to RX, transistor M4 was activated first to create a discharging path again from the element to the ground. At the transition of  $\Phi_{TX,\,PZT}$ , a significant error could be generated due to charge injection related to M1 and M2. However, the resulting voltage transient on the element was minimized because the associated charge could flow via M4 and M5 to the ground.

Figure 6b shows the switch controller's design with cascaded non-overlapping clock generators to generate the control signals presented in Figure 6a. Each stage employed delay unit cells in which metal–oxide–semiconductor (MOS) capacitors were used to make sufficient delay (>100 ns) between the signals.

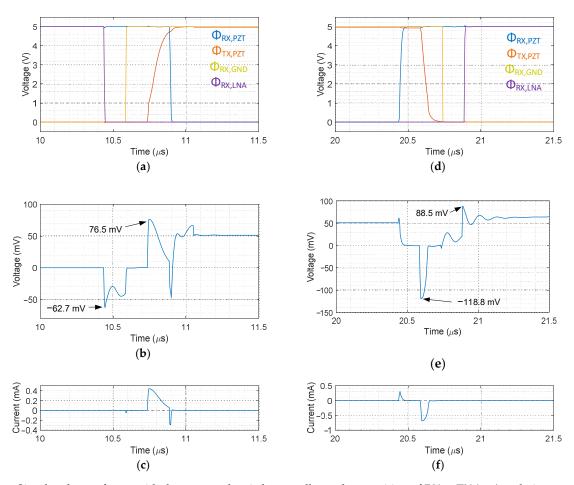

#### 2.5. Validation in Simulation

The proposed switch controller was simulated to validate the reduction of the switching transients. Figure 7 shows the simulation results of the control signals generated by the controller, the voltage on the element, and the current flowing through M5 in Figure 4 at the switching moments for the TX to RX transition and vice versa. Figure 7a shows the transition of the signals at the switching moment from RX to TX, with the peak-to-peak amplitude of switching transients being 139.2 mV, as shown in Figure 7b. Figure 7c shows that the current flows through M5 at the switching moments of high-voltage transistors M1, M2, and M4, resulting in the reduction of the switching transients. Figure 7d shows waveforms of the control signals at the transition from TX to RX, with the peak-to-peak

Sensors 2021, 21, 150 8 of 13

amplitude being 207.3 mV, as shown in Figure 7e. In particular, the largest peak value of -118.8 mV, associated with the falling edge of  $\Phi_{TX,\,PZT}$ , was caused by the charge injection effect of M1 and M2. This amplitude was significantly reduced because the charge-injection-induced current was also absorbed into the ground via M5, as is confirmed in Figure 7f. Consequently, compared to 2.19 V in the first-generation ASIC simulation, the peak-to-peak amplitude of the switching transients with the newly designed switch controller was reduced by around 20 dB.

Figure 7. Simulated waveforms with the proposed switch controller at the transition of RX to TX (a–c) and vice versa (d–f). (a,d) Control signals driving the element-level switch circuit, (b,e) the switching transients on the transducer element, and (c,f) the drain current flowing via M5.

## 3. Results and Discussion

# 3.1. Experimental Prototype

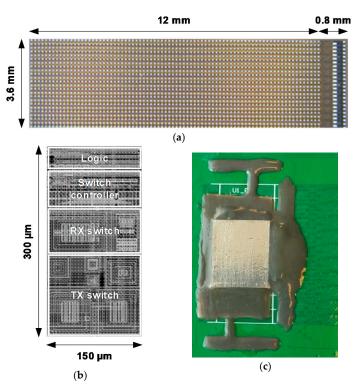

The ASIC was fabricated in a 0.18- $\mu$ m HVBCD process. Figure 8a,b shows a photograph of a bare die and a plot of the layout of the element-level TX and RX circuits, respectively. The area of the element-level circuit was matched to the 150  $\times$  300  $\mu$ m<sup>2</sup> transducer element size. In the prototype shown in Figure 8c, four ASICs were mounted on a test PCB and wire-bonded for RX and TX channels as well as for power and control signals. A piezo-electric transducer array was built on top of the ASICs using the process described in [23]. The prototype was covered by a ground foil, the common ground electrode of the transducer elements, and by a moisture protection layer.

Sensors **2021**, 21, 150 9 of 13

**Figure 8.** (a) Chip photograph of the ASIC, (b) layout of the pitch-matched element-level circuit, and (c) the test printed circuit board (PCB) with transducer array on top of the ASICs.

# 3.2. Electrical Verification

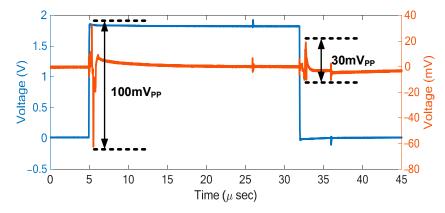

In the electrical characterization, an ASIC die without transducer array was used, on which selected transducer pads were wire-bonded to the test board to observe the switching transients. Without applying a high-voltage TX pulse, residual switching transients were visible, as shown in Figure 9. Their peak-to-peak amplitudes at the TX to RX transition and vice versa were  $100~\text{mV}_{PP}$  and  $30~\text{mV}_{PP}$ , respectively. Compared to the simulation results with the first-generation ASIC shown in Figure 5, the peak-to-peak values were reduced by factors of 6 and 70. Compared to the simulation results shown in Figure 7, the measured peak-to-peak amplitudes were a factor of 2 and 5 lower. This was likely due to the effects of the wire-bonded connection, the bondpad on the PCB, and the probe capacitance in the test setup, which resulted in a higher capacitance, and hence a smaller transient voltage than in the simulation. Taking this loading effect into account, the results were consistent with the expected reduction of 20 dB derived in Section 2.5.

**Figure 9.** Measured waveforms of the RX phase (blue) and the switching transient observed on the element X [6, 41] (orange).

Sensors **2021**, 21, 150

## 3.3. Improvement in Clock Feedthrough and Charge Injection-Induced Imaging Artifact

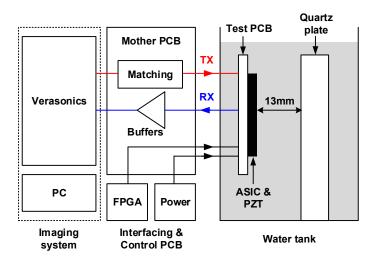

The test-bench for acoustic experiments to validate the reduced switching artifacts is shown in Figure 10. A Verasonics V1 imaging system (Verasonics, Kirkland, WA, USA) was used to generate the HV TX signals. To interface the TX and RX signals between the Verasonics and the test PCB, we designed a motherboard PCB. On the transmit paths, a matching circuit was implemented to guarantee a unipolar excitation pulse. The received signals were buffered with unity-gain operational amplifiers on the motherboard before being fed into the Verasonics. The motherboard also included low-dropout regulators (LDOs) to generate supply voltages for analog, digital, and 5 V circuitry. Moreover, the board contained digital buffers to transfer the signals from the field-programmable gate array (FPGA) board. These digital signals consisted of clock and data for programming the ASICs and their control signals.

**Figure 10.** Overview of the measurement setup used for demonstrating the effect of the switching transients for the first- and the second-generation ASICs.

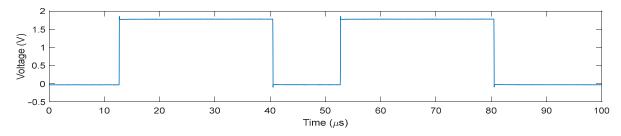

Pulse-echo measurements were performed to obtain imaging results using a quartz plate as a reflector located at a depth of 13 mm. The TX signal was a unipolar half-cycle 7.5 MHz pulse with a peak value of 1 V. All elements were enabled to send a plane wave on the full-aperture in TX, and echo signals were received in a column-by-column fashion. The reason for using a relatively small 1 V pulse was to better bring out the switching artifacts compared to the 60 V pulse used in normal operation. To record the switching glitches at the transitions of both TX to RX and vice versa, we applied two successive RX phases, as shown in Figure 11. During the first RX phase, the echo signal from the transmitted 1 V pulse and the switching transients from the first transition from TX to RX (the first rising edge) can be recorded. In the second cycle, the switching transients from the first transition from TX to RX (the second rising edge) were recorded.

**Figure 11.** The waveform of the RX phase with two cycles used in the pulse-echo measurement to record the switching glitches at both TX to RX transition and vice versa.

Sensors **2021**, 21, 150 11 of 13

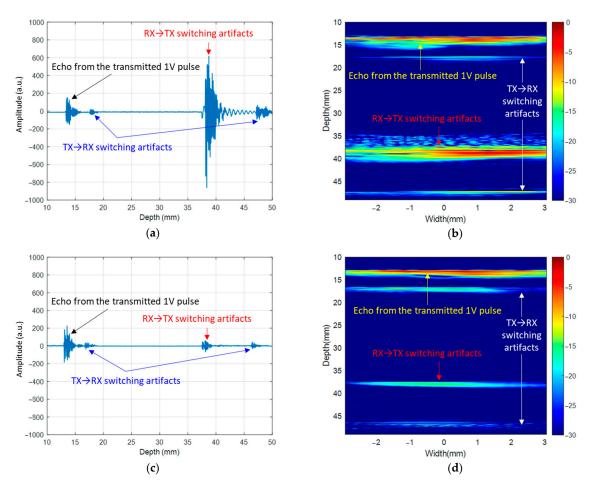

Figure 12 demonstrates how the switching transients affected the image and how much imaging artifacts were improved with the proposed switch controller circuit. Figure 12a,b show the RF signal for a single channel captured by the Verasonics and the imaging result, respectively, with the first-generation ASIC. As can be seen in Figure 12a, the peak-to-peak amplitude of the RX to TX switching transients located at a depth of 38 mm was considerably larger than the echo signal from the transmitted 1 V pulse. Even if the largest pulse amplitude supported by the ASIC of 65 V would be used, these switching transients would give significant artifacts in the image. On the other hand, the amplitude of the RX to TX switching transients was reduced by a factor of 20 dB in Figure 12c,d for the second-generation ASIC. This reduced amplitude corresponded to a parasitic transmitted pulse with an amplitude of only 0.3 V. If the maximum pulse amplitude of 65 V were to be used, the echo signals from the switching would be 46.7 dB smaller than the echoes from the intended pulse, making their impact on the image much less significant. This result demonstrated that the switching artifact reduction scheme with the proposed switch controller improved image quality significantly.

**Figure 12.** Comparison of switching transients for the first- and second-generation ASICs. (a) Time-domain plot of the received RX output data for a single channel and (b) B-Mode imaging result with the first-generation ASIC. (c) Time-domain plot for the second-generation ASIC with the same test conditions and (d) its imaging result.

## 4. Conclusions

We present an ultrasound transceiver ASIC design with a switching artifact reduction technique, designed for 3D volumetric imaging of the carotid artery. We have previously reported a first-generation ASIC design [17] that demonstrated the 3D imaging capability; however, we observed noticeable ghost echoes in the experiment. We have identified that this issue originates from clock feedthrough and charge injection of the HV MOSFETs in the

Sensors **2021**, 21, 150

element-level switch circuits, generating switching transients on the transducer elements that lead to parasitic pulse transmission. The improved switch controller proposed in this paper generates control signals of HV switches such that a discharge path to ground is created at the critical switching moments, strongly reducing the transients on the transducer element. Measured results demonstrate a 20 dB reduction in imaging artifacts compared to our previous ASIC.

**Author Contributions:** Conceptualization, T.K. and M.A.P.P.; methodology, T.K. and M.A.P.P.; validation, T.K., F.F., and D.S.d.S.; formal analysis, T.K., J.G.B., M.D.V., N.d.J., and M.A.P.P.; investigation, T.K., F.F., D.S.d.S., J.G.B., M.D.V., N.d.J., and M.A.P.P.; resources, Z.-Y.C. and E.N.; writing—original draft preparation, T.K.; writing—review and editing, F.F., D.S.d.S., H.J.V., J.G.B., M.D.V., N.d.J., and M.A.P.P.; supervision, J.G.B., M.D.V., N.d.J., and M.A.P.P.; project administration, H.J.V., J.G.B., M.D.V., N.d.J., and M.A.P.P.; funding acquisition, T.K., H.J.V., J.G.B., M.D.V., N.d.J., and M.A.P.P. All authors have read and agreed to the published version of the manuscript.

**Funding:** This research is a part of the PUMA and UltraXtreme projects (project numbers 13154 and P17-32, respectively), which are financed by the Netherlands Organization for Scientific Research (NWO). Moreover, this project has received funding from the European Union's Horizon 2020 research and innovation program under the Marie Skłodowska-Curie grant agreement no. 707404.

**Informed Consent Statement:** Not applicable.

**Data Availability Statement:** The data presented in this study are available on request from the corresponding author.

**Conflicts of Interest:** The authors declare no conflict of interest.

#### References

- 1. Couade, M.; Pernot, M.; Messas, E.; Emmerich, J.; Hagège, A.; Fink, M.; Tanter, M. Ultrafast imaging of the arterial pulse wave. *IRBM* **2011**, *32*, 106–108. [CrossRef]

- 2. Hasegawa, H.; Hongo, K.; Kanai, H. Measurement of regional pulse wave velocity using very high frame rate ultrasound. *J. Med. Ultrason.* **2012**, *40*, 91–98. [CrossRef] [PubMed]

- 3. Kruizinga, P.; Mastik, F.; Oord, S.C.V.D.; Schinkel, A.F.L.; Bosch, J.G.; De Jong, N.; Van Soest, G.; Van Der Steen, A.F. High-definition imaging of carotid artery wall dynamics. *Ultrasound Med. Biol.* **2014**, *40*, 2392–2403. [CrossRef] [PubMed]

- 4. Provost, J.; Papadacci, C.; Arango, J.E.; Imbault, M.; Fink, M.; Gennisson, J.-L.; Anter, M.; Pernot, M. 3D ultrafast ultrasound imaging in vivo. *Phys. Med. Biol.* **2014**, *59*, 1–13. [CrossRef] [PubMed]

- 5. Savord, B.; Solomon, R. Fully sampled matrix transducer for real time 3D ultrasonic imaging. In Proceedings of the IEEE Symposium on Ultrasonics, 2003, Honolulu, HI, USA, 5–8 October 2003.

- 6. Chen, C.; Vos, H.J.; Bosch, J.G.; Hay, T.A.; De Jong, N.; Pertijs, M.A.P.; Chen, Z.; Bera, D.; Raghunathan, S.B.; Shabanimotlagh, M.; et al. A front-end ASIC with receive sub-array beamforming integrated with a 32 × 32 PZT matrix transducer for 3-D transesophageal echocardiography. *IEEE J. Solid-State Circuits* **2017**, *52*, 994–1006. [CrossRef]

- 7. Kim, T.; Shin, S.; Kim, S. An 80.2 dB DR 23.25 mW/channel 8-channel ultrasound receiver with a beamforming embedded SAR ADC. *IEEE Trans. Circuits Syst. II Express Briefs* **2018**, *66*, 1487–1491. [CrossRef]

- 8. Igarashi, Y.; Kajiyama, S.; Katsube, Y.; Nishimoto, T.; Nakagawa, T.; Okuma, Y.; Nakamura, Y.; Terada, T.; Yamawaki, T.; Yazaki, T.; et al. Single-chip 3072-element-channel transceiver/128-subarray-channel 2-D array IC with analog RX and all-digital TX beamformer for echocardiography. *IEEE J. Solid-State Circuits* **2019**, *54*, 2555–2567. [CrossRef]

- 9. Wygant, I.O.; Jamal, N.S.; Lee, H.J.; Nikoozadeh, A.; Oralkan, O.; Karaman, M.; Khuri-Yakub, B.T. An integrated circuit with transmit beamforming flip-chip bonded to a 2-D CMUT array for 3-D ultrasound imaging. *IEEE Trans. Ultrason. Ferroelectr. Freq. Control.* 2009, 56, 2145–2156. [CrossRef] [PubMed]

- 10. Bhuyan, A.; Choe, J.W.; Lee, B.C.; Wygant, I.O.; Nikoozadeh, A.; Oralkan, O.; Khuri-Yakub, B.T. Integrated circuits for volumetric ultrasound imaging with 2-D CMUT arrays. *IEEE Trans. Biomed. Circuits Syst.* **2014**, *7*, 796–804. [CrossRef] [PubMed]

- 11. Chen, K.; Lee, H.-S.; Chandrakasan, A.P.; Sodini, C.G. Ultrasonic imaging transceiver design for CMUT: A three-level 30-Vpp pulse-shaping pulser with improved efficiency and a noise-optimized receiver. *IEEE J. Solid-State Circuits* **2013**, *48*, 2734–2745. [CrossRef]

- 12. Kim, B.-H.; Kim, Y.; Lee, S.; Cho, K.; Song, J. Design and test of a fully controllable 64x128 2-D cmut array integrated with reconfigurable frontend asics for volumetric ultrasound imaging. In Proceedings of the 2012 IEEE International Ultrasonics Symposium, Dresden, Germany, 7–10 October 2012.

- 13. Chen, K.; Lee, H.-S.; Sodini, C.G. A column-row-parallel ASIC architecture for 3-D portable medical ultrasonic imaging. *IEEE J. Solid-State Circuits* **2015**, *51*, 738–751. [CrossRef]

Sensors **2021**, 21, 150

14. Jung, S.-J.; Song, J.-K.; Kwon, O.-K. Three-side buttable integrated ultrasound chip with a 16 × 16 reconfigurable transceiver and capacitive micromachined ultrasonic transducer array for 3-D ultrasound imaging systems. *IEEE Trans. Electron. Devices* **2013**, 60, 3562–3569. [CrossRef]

- 15. Tamano, S.; Kobayashi, T.; Sano, S.; Hara, K.; Sakano, J.; Azuma, T. 3D ultrasound imaging system using fresnel ring array & high voltage multiplexer IC. In Proceedings of the IEEE Ultrasonics Symposium, Montreal, QC, Canada, 23–27 August 2004; Volume 1, pp. 782–785.

- 16. Fisher, R.; Thomenius, K.; Wodnicki, R.; Thomas, R.; Cogan, S.; Hazard, C.; Lee, W.; Mills, D.; Khuri-Yakub, B.; Ergun, A.; et al. Reconfigurable arrays for portable ultrasound. In Proceedings of the IEEE Ultrasonics Symposium, Rotterdam, The Netherlands, 18–21 September 2005; Volume 1, pp. 495–499.

- 17. Kang, E.; Ding, Q.; Shabanimotlagh, M.; Kruizinga, P.; Chang, Z.-Y.; Noothout, E.; Vos, H.J.; Bosch, J.G.; Hay, T.A.; De Jong, N.; et al. A reconfigurable ultrasound transceiver ASIC with 24 × 40 elements for 3-D carotid artery imaging. *IEEE J. Solid-State Circuits* **2018**, 53, 2065–2075. [CrossRef]

- 18. Enz, C.C.; Temes, G.C. Circuit techniques for reducing the effects of op-amp imperfections: Autozeroing, correlated double sampling, and chopper stabilization. *Proc. IEEE* **1996**, *84*, 1584–1614. [CrossRef]

- 19. Eichenberger, C.; Guggenbuhl, W. Dummy transistor compensation of analog MOS switches. *IEEE J. Solid-State Circuits* **1989**, 24, 1143–1146. [CrossRef]

- 20. Eichenberger, C.; Guggenbuhl, W. On charge injection in analog MOS switches and dummy switch compensation techniques. *IEEE Trans. Circuits Syst.* **1990**, *37*, 256–264. [CrossRef]

- 21. Wu, C.-Y.; Chen, C.-C.; Cho, J.-J. Precise CMOS current sample/hold circuits using differential clock feedthrough attenuation techniques. *IEEE J. Solid-State Circuits* **1995**, *30*, 76–80. [CrossRef]

- 22. Wodnicki, R.; Liu, Y.; Chiu, V.; Stephens, D.N.; Zhou, Q.; Ferrara, K.W.; Kang, H.; Li, D.; Sun, Y.; Jiang, L.; et al. Tiled large element 1.75D aperture with dual array modules by adjacent integration of PIN-PMN-PT transducers and custom high voltage switching ASICs. In Proceedings of the 2019 IEEE International Ultrasonics Symposium (IUS), Glasgow, UK, 6–9 October 2019; pp. 1955–1958.

- 23. Chen, C.; Noothout, E.; Vos, H.J.; Bosch, J.G.; Verweij, M.D.; De Jong, N.; Pertijs, M.A.P.; Raghunathan, S.B.; Yu, Z.; Shabanimotlagh, M.; et al. A prototype PZT matrix transducer with low-power integrated receive ASIC for 3-D transesophageal echocardiography. *IEEE Trans. Ultrason. Ferroelectr. Freq. Control.* 2015, 63, 47–59. [CrossRef] [PubMed]