Article

# High Frequency Dual-Buck Full-Bridge Inverter Utilizing a Dual-Core MCU and Parallel Algorithm for Renewable Energy Applications

Zhun Meng, Yi-Feng Wang \*, Liang Yang and Wei Li

School of Electrical Engineering and Automation, Tianjin University, Tianjin 300072, China; quakermaster@hotmail.com (Z.M.); zyangliang@tju.edu.cn (L.Y.); liweitju@hotmail.com (W.L.)

\* Correspondence: wayif@tju.edu.cn; Tel.: +86-22-2740-1117; Fax: +86-22-2740-1479

Academic Editor: Paul Stewart

Received: 30 December 2016; Accepted: 15 March 2017; Published: 21 March 2017

Abstract: A high frequency dual-buck full-bridge inverter for small power renewable energy applications is proposed in this paper. The implementation of the wide band gap SiC (Silicon Carbide) power device contributes to the high switching frequency of 400 kHz. This high frequency contributes to reduced converter volume as well as improved power density, which greatly strengthens its portability and application range. For the control strategy, a voltage-current dual loop controller is employed. A three-pole-three-zero (3P3Z) compensator is applied in the current loop in order to track the current reference without static error. A voltage loop two-pole two-zero (2P2Z) compensator is used to generate the current reference for stabilizing the DC bus voltage. Not only is the inner current loop analyzed in detail, which includes the modeling of the equivalent inductor-capacitor-inductor (LCL)-type inverter and the design of the 3P3Z compensator, but also the outer voltage loop is discussed, the model of which is established based on the energy balance. Furthermore, a feedback linearization method is adopted to simplify the duty cycle calculation and helps to accelerate the control speed. A second-order generalized integrator software phase lock loop (SOGI-SPLL) is employed to obtain the phase angle and to synchronize the inverter output current with the grid voltage. A parallel structure algorithm is conducted based on a dual-core microcontroller unit (MCU) for the first time to control the high frequency inverter. This approach avoids the contradiction between the high frequency operation and the limited computing capacity of the conventional single-core MCUs. The software structure, time-consuming distribution, and interactive communication method are analyzed in detailed. Finally, this paper verifies the feasibility of the theoretical analyses through simulation and experiments based on a 1 kW prototype.

**Keywords:** SiC power device; grid-connected generation; dual-buck inverter; high frequency conversion; software phase lock loop; dual-core microcontroller unit (MCU)

#### 1. Introduction

Environmental crisis is becoming a major obstacle to national economic development. Many responsible nations turn to renewable energy in order to make development more ecological and sustainable. Hence, distributed renewable energy generation has become a hot research topic for its environment protection, low cost, flexibility, and convenience. Being able to convert all kinds of distributed energy into a unified AC power, the grid-connected inverter extensively broadens the application range of renewable energies, and thus has an indispensable role in the renewable energy generation systems.

The H-type full bridge and half bridge topologies, with the advantage of a simple structure and mature technology, are widely adopted by most of the traditional grid-connected inverters [1–5].

Energies 2017, 10, 402 2 of 18

However, the main disadvantage of the H-type inverter is that in each of the two legs, two switches are arrayed in series and may suffer from shoot-through problems. As a result, dead-time control must be used to avoid this issue, which not only introduces the harmonic into the output current, but also causes conduction loss and reverse recovering loss of the freewheeling body diode. Moreover, due to the low switching speed, a large-volume output filter has to be used to smooth the output current distortions, which lowers the power density and limits the applications of the inverter.

The dual-buck inverter, as an effective solution for the aforementioned problem, has the advantage of being free from shoot-though issues, because the switches are no longer located on the same leg. By eliminating the dead-time control, the reliability is significantly improved. Regarding the topology, there are two basic types of dual-buck inverters, namely the half bridge type and the full bridge type.

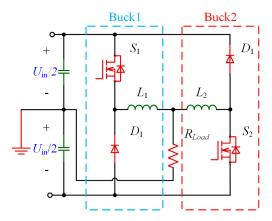

The structure of the dual-buck half-bridge inverter is shown in Figure 1. The topology is good for its simple structure and ease of control; nevertheless, it still has drawbacks including a low DC voltage utilization ratio and higher voltage stress, which impairs its extensive applications [6–8]. In contrast, the full-bridge alternative not only possesses the main advantages of the half-bridge type, but has a high DC voltage utilization ratio and diminished voltage stress [9,10].

Figure 1. Dual-buck half-bridge inverter.

A family of five-level dual-buck full-bridge inverters with the advantages of multi-level, high reliability, and high efficiency are proposed in [11]. However, these multi-level inverters often have very complicated topologies which increase the cost of the components and complicate the control method. For small renewable energy applications, cost is one of the most important criteria. A dual-buck inverter with coupled inductors as energy storage branches is described in [12]. The inverter achieves zero current switching (ZCS) and high efficiency. Moreover, different structures of coupled inductor are discussed in [13]. By employing coupled inductors, the number of inductors is successfully reduced, but the system efficiency also decreases. However, all of these full-bridge buck type inverters have a switching frequency among 10 kHz to 40 kHz and have a filter inductor volume issue which leads to the decrease of the power density.

Furthermore, the power devices of the inverters mentioned above are all traditional silicon devices, which are not suitable for high speed switching and will reduce the system efficiency. With the development of wide band-gap semiconductor technology, the SiC power devices, which are suitable for high frequency switching, are becoming mature. Contrast analyses have been done between the Si and SiC power devices in different applications [14–17]. The results show that the SiC device has lower losses in different implementations and the advantages are more obvious in high frequency applications.

A high frequency single phase dual-buck full-bridge grid-connected inverter for small power renewable energy is proposed. Based on full SiC power switching devices, the operating frequency balloons from the normal  $10–50~\rm kHz$  to the very high  $400~\rm kHz$ , which consequently reduces the

Energies 2017, 10, 402 3 of 18

filter's size and the ripple of the grid-connected current. At the same time, limited conversion loss is guaranteed. The design procedure of the proposed inverter is presented and analyzed in detail, which gives a practical design example for a similar type inverter. A three-pole three-zero (3P3Z) compensator is used in the current loop for high frequency compensation. A two-pole two-zero (2P2Z) compensator is used to generate the reference current in order to stabilize the DC bus voltage. Not only is the inner current loop analyzed in detail, which includes the modeling of the equivalent LCL-type inverter and the design of its 3P3Z compensator, but the outer voltage loop is discussed, the model of which is established by energy balance. The control strategy discussed above is actualized by a parallel algorithm on a high performance dual-core MCU. Application details of the proposed algorithm are presented in this paper, including software structure, time-consuming distribution, and the interactive communication method. As a consequence, a 400 kHz high speed control is achieved based on a 1 kW prototype to verify the theoretical analyses.

#### 2. Circuit Configuration and Operation Principles

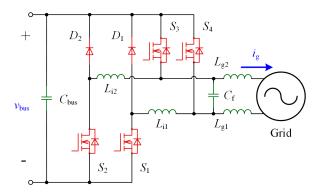

The topology of the dual-buck full-bridge inverter is presented in Figure 2. The inverter can be regarded as two individual buck converters. One consists of  $S_1$ ,  $S_3$ ,  $D_1$ , and  $L_{i1}$ , connecting to the DC bus positively. The other is  $S_2$ ,  $S_4$ ,  $D_2$ , and  $L_{i2}$ , connecting to the DC bus negatively. The output inductors of the buck converters  $L_{i1}$  and  $L_{i2}$  constitute a LCL filter with  $C_f$ ,  $L_{g1}$ , and  $L_{g2}$ . For one AC cycle, both bucks work in their own half cycles separately.

The design features of the inverter are:

- (1) The structure is simple and no extra power circuit is introduced.

- (2) Dead time, which is set up to avoid shoot-through, can be ignored because no switch is arrayed in series at the same leg. No dead time makes the implementation of high speed switching more reliable and easy.

- (3) Comparing to the full bridge topology, only two diodes are added in the dual-buck inverter. The performance of the individual diode is better than the body diode of the switch, which can lower the freewheeling conduction loss.

- (4) Wide Band Gap (WBG) semiconductor devices are adopted.  $S_1$ - $S_4$  and  $D_1$ - $D_2$  are all SiC-based components, which make high speed switching possible and lower the switching losses simultaneously.

- (5) The high switching frequency shrinks the size and value of the inductors in the converter, making high power density inversion feasible.

Figure 2. The topology of the proposed inverter.

## 2.1. Operation States

To drive the inverter, unipolar modulation has been adopted. The operation principle and modes are analyzed in this section. In order to simplify the analysis procedure, several assumptions are made:

Energies 2017, 10, 402 4 of 18

- (1) All the devices, including switches, diodes, and the grid, are ideal.

- (2) The current, which goes through  $C_f$ , can be negligible compared with the currents of  $L_{i1}$ ,  $L_{i2}$ ,  $L_{g1}$ , and  $L_{g2}$ .

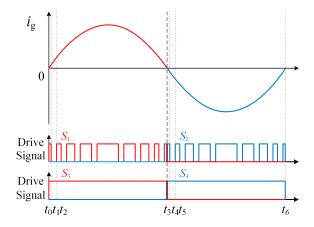

From Figure 3, a full AC cycle can be divided into two separate phases by judging the direction of the output grid current  $i_g$ . In Phase 1,  $i_g$  is positive. Buck 1, which consists of  $S_1$ ,  $S_3$ , and  $D_1$ , works with the LCL filter consisting of  $L_{i1}$ ,  $C_f$ ,  $L_{g1}$ , and  $L_{g2}$ . Similarly, in Phase 2,  $i_g$  is negative. Buck 2, which consists of  $S_2$ ,  $S_4$ , and  $D_2$  is working with the LCL filter. In each phase,  $S_1$  or  $S_2$  switches at 400 kHz and  $S_3$  or  $S_4$  switches at AC frequency.

Figure 3. Key waveforms of the system.

From  $t_0$  to  $t_3$ , assume that  $i_g$  flows positively. Buck 2 does not work and Buck 1 works alternately to form Mode I to Mode II.

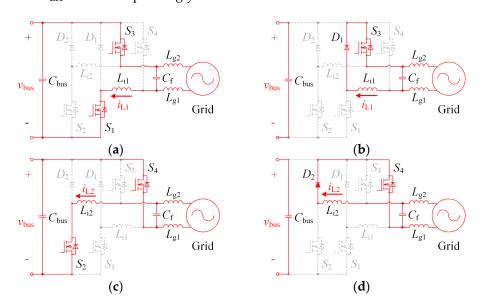

Mode I ( $t_0$ - $t_1$ ) is shown in Figure 4a.  $S_1$  and  $S_3$  turn on at  $t_0$ .  $S_2$ ,  $S_4$ ,  $D_1$ , and  $D_2$  are all off. The DC bus,  $S_1$ ,  $S_3$ ,  $L_{i1}$ ,  $L_{g1}$ , and  $L_{g2}$  are in series to form a loop. The DC Bus charges  $L_{i1}$ ,  $L_{g1}$ , and  $L_{g2}$ , and the inductor current  $i_{Li1}$  rises correspondingly.

Figure 4. Working models of the system. (a) Mode I; (b) Mode II; (c) Mode III; (d) Mode IV.

Mode II  $(t_1-t_2)$  is shown in Figure 4b.  $S_3$  stays turned on at  $t_1$ , and  $S_2$  and  $S_4$  are kept off. When  $S_1$  is closed,  $D_1$  turns on. The freewheeling current runs through  $D_1$  instead of the body diode.  $L_{i1}$ ,  $L_{g1}$ , and  $L_{g2}$  are discharged and  $i_{L1}$  decreases linearly.

Energies 2017, 10, 402 5 of 18

From  $t_3$  to  $t_6$ ,  $i_g$  is flowing negatively. Buck 1 does not work and Buck 2 alters from Mode III to Mode IV. Mode III and Mode IV are similar to Mode I and Mode II, respectively. Therefore, Mode III and Mode IV will not be discussed in this paper.

## 2.2. Parameter Design

The LCL-filter has an outstanding performance of attenuating the switching noise, which is better than the L and LC-filters. In order to make the filter function well, the parameters of the filter have to be designed properly [1,18]. Section 2.1 shows the operation principles of the inverter, and the two buck converters share  $C_f$ ,  $L_{g1}$ , and  $L_{g2}$ , which form a LCL filter. For convenience, the equivalent inductors of the LCL filter can be expressed as:  $L_i = L_{i1} = L_{i2}$ ,  $L_g = L_{g1} + L_{g2}$ .

#### 2.2.1. Inverter Side Inductor $L_i$

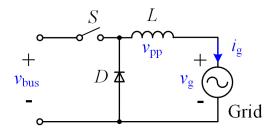

The main function of  $L_i$  is to suppress the current ripple. Neglecting the current through  $C_f$ ,  $L_g$  is in series with  $L_i$ , and the LCL filter can be simplified as a single inductor  $L = L_i + L_g$ , as shown in Figure 5 [19].

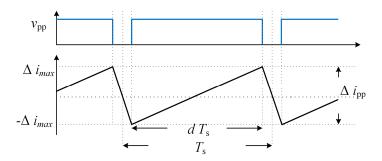

The duty cycle of the equivalent switch is d, the switching period is  $T_{\rm s}$ , and the DC bus voltage is  $v_{\rm bus}$ . The relationship between the inductor voltage  $v_{\rm pp}$  and the peak-to-peak value of the inductor current  $\Delta i_{\rm pp}$  is shown in Figure 6.

Figure 5. Equivalent circuit for current ripple analysis.

Figure 6. Relationship between the inductor voltage and current ripple peak.

In Figure 6, the inductor voltage is  $v_{\rm pp} = v_{\rm bus} - v_{\rm g}$ ,  $m_{\rm a}$  is the voltage modulation index,  $\omega_{\rm pp}$  represents the peak-to-peak frequency of inductor ripple, and  $\Delta i_{\rm pp}$  can be calculated as Equation (1).

$$\Delta i_{\rm pp} = \frac{\left(v_{\rm bus} - v_{\rm g}\right) \cdot dT_{\rm s}}{L} = \frac{v_{\rm bus}T_{\rm s} \cdot d(1-d)}{L} = \frac{v_{\rm bus}T_{\rm s}m_{\rm a}\sin(\omega_{\rm pp}t) \cdot (1-m_{\rm a}\sin(\omega_{\rm pp}t))}{L} \tag{1}$$

From (1), it is noted that the current ripple is not uniform across the sine wave cycle and has a maximum value at  $\sin(\omega t) = 1/2m_a$ . Accordingly, the maximum current ripple is (2)

$$\Delta i_{\rm pp}|_{\rm max} = \frac{v_{\rm bus}T_{\rm s}}{4L} \tag{2}$$

Energies 2017, 10, 402 6 of 18

The output current ripple should meet the institute of electrical and electronics engineers (IEEE) standard requirement, and thus 5% is chosen as the maximum current ripple. As mentioned before, L is equal to  $L_i + L_g$ , however, if  $L_i$  alone is large enough and satisfies the requirement of the ripple constraint, then L will meet this requirement as well. The switch frequency is  $f_{sw}$ , and the design equation of  $L_i$  is given as:

$$L_{\rm i} = \frac{v_{\rm bus}}{4f_{\rm sw} \cdot \Delta i_{\rm pp}|_{\rm max}} \tag{3}$$

## 2.2.2. Filter Capacitor $C_{\rm f}$

According to the IEEE-1547/IEEE-519 standard, the maximum reactive power, which is absorbed by the inverter in the rated condition, is 5% of the rated capacity. Hence, the maximum value of the filter capacitor  $C_f$  can be calculated based on the system capacity as Equation (4).  $S_n$  is the rated capacity of the inverter,  $U_n$  is the grid voltage, and  $\omega_n$  is the grid angular frequency.

$$C_{\text{fmax}} = \frac{S_{\text{n}}}{\omega_{\text{n}} U_{\text{n}}^2} \cdot 5\% \tag{4}$$

## 2.2.3. Grid Side Inductor $L_{\rm g}$

The resonant frequency  $f_{res}$  of the inverter LCL filter can be calculated as:

$$f_{\rm res} = \frac{1}{2\pi} \sqrt{\frac{L_{\rm i} + L_{\rm g}}{L_{\rm i} L_{\rm g} C_{\rm f}}} \tag{5}$$

As Figure 9 shows, the disturbances and noise may be amplified around the resonant frequency. In order to reduce the negative effect of the filter, it is important that the filter has enough attenuation ability at the switching frequency. Thus, the resonant frequency must have a distance from the grid frequency and the distance should be one half of the switching frequency at minimum. By tweaking the  $L_{\rm g}$  and  $C_{\rm f}$  values, the resonant frequency can be designed within the desirable range. The component parameters of the proposed inverter will be listed in a later section.

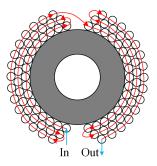

## 2.2.4. Material and Winding Method of the Inductor

Taking account of the high switching frequency, it is vital to choose the inductor material appropriately in order to reduce the inductor loss. Balancing the cost and performance, sendust is selected as the toroid material. Moreover, the Miller effect may cause oscillation during the switch operation and this problem may get even worse in high speed switching and lead to switching failure. As is shown in Figure 7, the segment winding method is employed to the halved interlayer capacitance. Hence, the two sections of winding are connected in series with each other and the parasitic capacitance is further reduced.

Figure 7. Inductor segment winding method.

Energies 2017, 10, 402 7 of 18

#### 3. Control of the Proposed Inverter

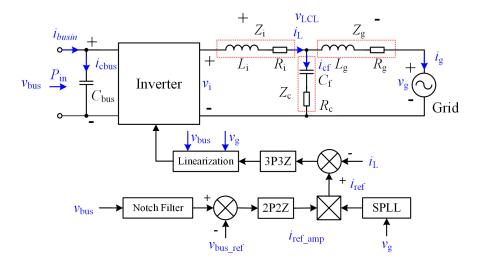

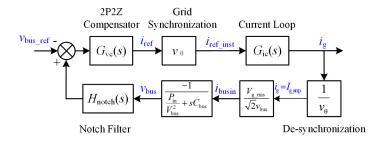

In the renewable energy distributed generation system, it usually has a two-stage structure. The front-stage DC-DC converter adopts the maximum power tracking method to capture energy, while the post-stage inverter transfers the energy into the power grid and stabilizes the DC bus voltage by balancing the input and output power. To actualize these functions, the proposed inverter adopts a current voltage dual-loop. The structure of the control system is shown in Figure 8.

Figure 8. Control structure of the inverter.

The bus voltage error is acquired by comparing the measured bus voltage  $v_{\rm bus}$  with the bus voltage reference  $v_{\rm bus\_ref}$ . By injecting the error signal into the 2P2Z compensator, the current reference amplitude  $i_{\rm ref\_amp}$  for the inner current loop is obtained. The SOGI-SPLL measures the grid voltage signal and synchronizes  $i_{\rm ref\_amp}$  with the grid voltage in order to generate the reference current  $i_{\rm ref}$ . Then,  $i_{\rm ref}$  is compensated by a 3P3Z compensator. The result goes through a feedback linearization module and becomes the duty cycle which generates the pulse-width modulation (PWM) signal to control the inverter. This method is highly simplified and optimized, which achieves a 400 kHz high speed control.

## 3.1. Current Loop Compensation

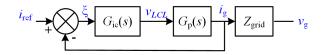

The plant transfer function of the LCL filter for the current control loop can be derived by Kirchhoff's law. The LCL filter is modeled below as (6),  $G_{ig\_vi}$  is the plant model for the grid current  $i_g$  with regards to the inverter voltage  $v_i$ .

$$G_{ig\_vi}(s) = \frac{Z_c}{\left(\left(Z_g Z_c\right) + \left(\left(Z_g + Z_c\right) \cdot Z_i\right)\right)} \tag{6}$$

The  $Z_i$ ,  $Z_g$ , and  $Z_c$  are the impedances of  $L_i$ ,  $L_g$ , and  $C_f$  respectively. For the proposed inverter, the current feedback senses the  $L_i$  current  $i_L$ , and the transfer function of  $i_L$  with regards to the inverter voltage  $v_i$  is  $G_p$  (7)

$$G_{p}(s) = \frac{v_{i}}{i_{L}} = G_{ig\_vi}(s) \cdot \frac{(Z_{g} + Z_{c})}{Z_{c}} = \frac{Z_{g} + Z_{c}}{((Z_{g} \cdot Z_{c}) + ((Z_{g} + Z_{c}) \cdot Z_{i}))}$$

(7)

In the current control mode, the goal of the compensator is to reduce the steady state error to zero. The plant transfer function  $G_p$  and current loop compensator  $G_{ic}$  can be rearranged and bring out the number of integrators.  $\alpha_p$  and  $\alpha_{ic}$  are the number of integrators in the plant transfer function

Energies 2017, 10, 402 8 of 18

and compensator, respectively.  $K_p$  and  $G_{p_r}(s)$  are the coefficient and plant transfer function after rearranging, respectively, and  $K_{ic}$  and  $G_{ic_r}(s)$  are the coefficient and compensator transfer function after rearranging, respectively.

$$G_{ic}(s) = \frac{K_{ic}}{s^{\alpha_{ic}}} G_{ic\_r}(s)$$

(8)

$$G_{\mathbf{p}}(s) = \frac{K_{\mathbf{p}}}{s^{\alpha_{\mathbf{p}}}} G_{\mathbf{p}_{-}\mathbf{r}}(s) \tag{9}$$

The grid voltage  $v_g(s)$  can be approximated to be a ramp signal as Equation (10)

$$v_{\rm g}(s) \approx \frac{1}{s^2} \tag{10}$$

The error  $\xi$  of the grid current  $i_g$ , which is caused by the grid voltage  $v_g$ , is given below as

$$\xi(s) = v_{g}(s) \frac{G_{p}(s)}{v_{\text{bus}} G_{\text{ic}}(s) G_{p}(s) + 1}$$

$$\tag{11}$$

Combining with Equations (8–10), Equation (11) can be expressed as

$$\lim_{s \to 0} s\xi(s) = \lim_{s \to 0} \frac{1}{s} \frac{s^{\alpha_{ic}} G_{p_{r}}(s)}{s^{\alpha_{ic} + \alpha_{p}} + v_{bus} K_{ic} K_{p} G_{ic r}(s) G_{p_{r}}(s)}$$

(12)

Obviously, to eliminate the state error, the compensator which has a higher number of integrators ( $\alpha_{ic} \ge 2$ ) must be used.

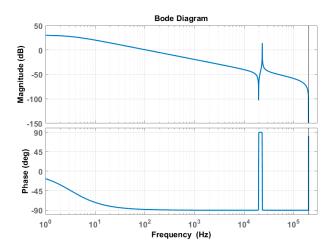

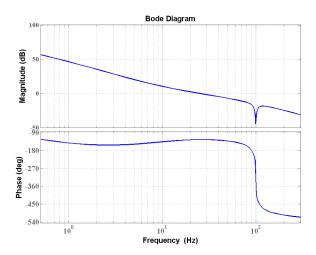

The Bode diagram of the LCL transfer function  $G_p(s)$  is shown in Figure 9.

Figure 9. Bode diagram of the inductor-capacitor-inductor (LCL) filter.

As shown in Figure 9, the LCL filter presents resonant peaks around the resonant frequency. As a result, the system will be vulnerable and highly sensitive to turbulence and noise which will bring unstable states into the system [20]. Therefore, a 3P3Z compensator is adopted in order to track the current reference without state error and damps the resonant peak simultaneously.

The compensator is designed in the Matlab SISOtool environment. Graphical tuning is used as the design method. One real pole, one complex pole pair, and one real zero, and one complex zero pair are added in the compensator. The complex zero pair and complex pole pair are placed near the resonance peak. By adjusting the damping factor, the peak can be diminished in order to achieve active damping. Appropriate phase and gain margins can be obtained by tweaking the real pole and real

Energies 2017, 10, 402 9 of 18

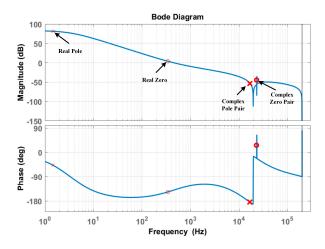

zero positions. The compensator transfer function is transferred in the *z*-domain by the Tustin method and is shown in Equation (13). The current control loop Bode diagram is shown in Figure 10.

$$G_{\rm ic}(z) = \frac{0.2886z^3 - 0.3173z^2 + 0.3338z - 0.2616}{z^3 - 1.584z^2 + 0.6978z - 0.1137}$$

(13)

Figure 10. Bode diagram of the current control loop.

After compensation, as shown in Figure 10, the resonant peak is damped effectively. A gain margin of 38.9 dB and a phase margin of 40.1 degree are achieved. The block diagram of the current control loop, which is based on Equation (11), is shown in Figure 11.

Figure 11. Block diagram of the current control loop.

Where  $G_{ic}$  is the current loop compensator, d is the duty cycle of the switch,  $Z_{grid}$  is the grid impedance,  $v_i = v_{bus} \times d$ ,  $i_g$  is the grid current, and  $i_{ref}$  is the reference current. In order to calculate the duty cycle d,  $Z_{grid}$  is needed, but  $Z_{grid}$  cannot be directly obtained. To solve this contradiction, a feedback linearization method is adopted [20].

For adopting the method, several assumptions and approximations are made.

- (1) The change in the inductor current  $i_L$  has no effect on the grid voltage  $v_g$ ; it is a stiff grid system.

- (2) The current  $i_{cf}$  that flows through the filter capacitor  $C_f$  is negligible compared to the inductor current  $i_L$ . Hence,  $i_L = i_g$ .

- (3) The current controller bandwidth is much higher than the grid frequency, and the feedback path from the grid voltage to the grid controller is broken.

- (4) The current loop controller is designed such that the current loop gain at the grid frequency is high. As a result,  $v_g$  can be treated as a DC parameter compared to the dynamics of the inverter inductor current  $i_L$ ; in another word, the current loop crossover frequency is much higher than the grid frequency.

Under these assumption the current controller loop in Figure 11 can be redrawn as Figure 12. From Figure 11,  $v_{LCL}$  can be expressed as Equation (14)

$$v_{\text{LCL}} = v_{\text{i}} - v_{\text{g}} = d \cdot v_{\text{bus}} - v_{\text{g}} = (i_{\text{ref}} - i_{\text{g}}) \cdot G_{\text{ic}}(s) = (i_{\text{ref}} - i_{\text{L}}) \cdot G_{\text{ic}}(s)$$

$$(14)$$

Energies 2017, 10, 402 10 of 18

It is clear that the voltage across the output filter  $v_{\rm LCL}$ , and not  $v_{\rm i}$ , has a direct impact on the line current. This is valid when the  $v_{\rm LCL}$  is controlled by a current loop compensator such that the loop gain at grid frequency is high. Hence the compensator must provide the  $v_{\rm LCL}$ . The model of the plant does not change because it takes into account only the small signal behavior. If the compensator provides  $v_{\rm LCL}$ , the duty cycle can be computed as:

$$d = \frac{(i_{\text{ref}} - i_{\text{L}}) \cdot G_{\text{ic}}(s) + v_{\text{g}}}{v_{\text{bus}}}$$

(15)

Figure 12. Current control loop with feedback linearization.

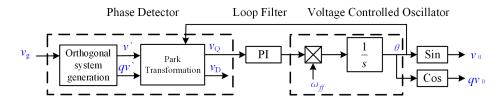

## 3.2. Second Order Generalized Integrator Software Phase Lock Loop (SOGI-SPLL)

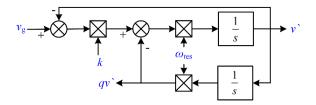

To acquire the phase angle, the SOGI-SPLL method is adopted. The main structure of the PLL is shown in Figure 13.

Figure 13. General structure of a single-phase phase lock loop (PLL).

Compared with the traditional method, the SOGI method introduces a new type of orthogonal system as shown in Figure 14.

Figure 14. Orthogonal signal generation based on the second-order generalized integration (SOGI) method.

There are several advantages of this PLL method. First, the generated orthogonal system is filtered without delay due to its resonance at the fundamental frequency. Second, the PLL structure is not affected by the frequency changes. Finally, the simple implementation and low calculation consumption are also important advantages [21], for the calculation time of the control loop is very limited when the control frequency is high.

As Figure 13 shows,  $v_{\theta}$  is the phase locked signal, which has the same phase angle as the input grid voltage  $v_{g}$ , and  $qv_{\theta}$  is the orthogonal signal of  $v_{\theta}$ . The reference current  $i_{ref}$  can be expressed as Equation (16), where  $i_{ref\_amp}$  is the active power reference amplitude and  $i_{ref\_qamp}$  is the reactive power reference amplitude. Because the inverter only outputs active power,  $i_{ref\_qamp} = 0$ , and the

Energies 2017, 10, 402 11 of 18

equation can be simplified as Equation (17). Current  $i_{ref\_amp}$  is the current reference amplitude, which is generated by the voltage loop.

$$i_{\text{ref}} = i_{\text{ref amp}} \cdot v_{\theta} + i_{\text{ref gamp}} \cdot q v_{\theta} \tag{16}$$

$$i_{\text{ref}} = i_{\text{ref amp}} \cdot v_{\theta} \tag{17}$$

## 3.3. Bus Voltage Regulation

To stabilize the bus voltage, a 2P2Z compensator is employed to control the voltage loop. According to Kirchhoffs current law (KCL) and Kirchhoffs voltage law (KVL), the relationship between the bus voltage  $v_{\rm bus}$  and bus input current  $i_{\rm busin}$  can be deduced as

$$\frac{v_{\text{bus}}(s)}{i_{\text{busin}}(s)} = \frac{-1}{\frac{P_{\text{in}}}{V_{\text{bus}}^2} + C_{\text{bus}}s}$$

$$\tag{18}$$

where  $V_{\rm bus}$  is the nominal bus voltage,  $P_{\rm in}$  is the inverter input power, and  $C_{\rm bus}$  is the inverter input capacitor. The grid side voltage  $v_{\rm g}$  and grid current  $i_{\rm g}$  can be represented as

$$v_{\rm g} = V_{\rm g\_amp} \cos(\omega_{\rm g} t) \tag{19}$$

$$i_{g} = I_{g\_amp} \cos(\omega_{g} t - \Phi) \tag{20}$$

$V_{\rm g\_amp}$ ,  $I_{\rm g\_amp}$  are the amplitudes of the current and voltage, respectively.  $\omega_{\rm g}$  is the grid angular frequency, and  $\Phi$  is the phase difference between  $v_{\rm g}$  and  $i_{\rm g}$ . The power balance equation of the inverter can be represented as

$$P_{\rm in} = P_{\rm out} + P_{\rm cbus} + P_{\rm LCL} \tag{21}$$

$P_{\rm in}$  is the input power,  $P_{\rm out}$  is the AC output power,  $P_{\rm cbus}$  is the power of the capacitor  $C_{\rm bus}$ , and  $P_{\rm LCL}$  is the power of the LCL filter. In order to simplify the power analysis of the LCL filter, an assumption is made. Considering that the value of the LCL capacitor  $C_{\rm f}$  is small, the  $C_{\rm f}$  is ignored. Hence, the inductor currents of the  $L_{\rm i}$  and  $L_{\rm g}$  are the same, and  $L_{\rm i}$  and  $L_{\rm g}$  can be considered as a single inductor. The input power, output power, and power of LCL can be expressed as Equations (22)–(24).

$$P_{\rm in} = v_{bus} \cdot i_{\rm busin} \tag{22}$$

$$P_{\rm out} = V_{\rm g\_amp} I_{\rm g\_amp} \cos(\omega_{\rm g} t) \cos(\omega_{\rm g} t - \Phi) = \frac{V_{\rm g\_amp} I_{\rm g\_amp}}{2} \cos(\Phi) + \frac{V_{\rm g\_amp} I_{\rm g\_amp}}{2} \cos(2\omega_{\rm g} t - \Phi) \quad (23)$$

$$P_{LCL} = (L_i + L_g) \cdot i_g \cdot \frac{di}{dt} = -\frac{1}{2} I_{g\_amp}^2 \omega (L_i + L_g) \sin[2(\omega t - \Phi)]$$

(24)

Combined with Equations (22)–(24), the power balance equation of the inverter can be represented as

$$v_{bus} \cdot i_{busin} = \frac{V_{g\_amp} I_{g\_amp}}{2} \cos(\Phi) + \frac{V_{g\_amp} I_{g\_amp}}{2} \cos(2\omega_g t - \Phi) - \frac{1}{2} I_{g\_amp}^2 \omega(L_i + L_g) \sin[2(\omega t - \Phi)] + P_{cbus} \tag{25}$$

As Equation (25) shows, the bus input current  $i_{\text{busin}}$  can be regarded as a composite variable of a DC component  $I_{\text{busin}}$  and an AC component  $i_{\text{busripple}}$ . They can be expressed as Equation (26) and Equation (27), respectively.

$$I_{\text{busin}} = \frac{V_{\text{g\_amp}}}{2v_{\text{bus}}} I_{\text{g\_amp}} \cos(\Phi) = \frac{V_{\text{g\_rms}}}{\sqrt{2}v_{\text{bus}}} I_{\text{g\_amp}} \cos(\Phi)$$

(26)

$$i_{\text{busripple}} = \frac{V_{\text{g\_amp}} I_{\text{g\_amp}}}{2v_{\text{bus}}} \cos(2\omega_{\text{g}} t - \Phi) - \frac{1}{2v_{\text{bus}}} I_{\text{g\_amp}}^2 \omega(L_{\text{i}} + L_{\text{g}}) \sin[2(\omega t - \Phi)] + \frac{P_{\text{cbus}}}{v_{\text{bus}}}$$

$$= \frac{V_{\text{g\_amp}} I_{\text{g\_amp}}}{2v_{\text{bus}}} \cos(2\omega_{\text{g}} t - \Phi) - \frac{1}{2v_{\text{bus}}} I_{\text{g\_amp}}^2 \omega(L_{\text{i}} + L_{\text{g}}) \sin[2(\omega t - \Phi)] + C_{\text{bus}} \frac{dv_{\text{bus}}}{dt}$$

$$(27)$$

Energies 2017, 10, 402 12 of 18

$V_{\rm g\_rms}$  and  $I_{\rm g\_rms}$  are the root meam square (RMS) values of the voltage and current, respectively. The inverter only delivers active power and does not participate in reactive power regulation. Therefore,  $\cos(\Phi)$  is almost 1. The bus voltage contains a double grid frequency ripple. In order to filter out the interference, a notch filter is added in the voltage control loop.

The notch filter can be designed by the FDA tool in the Matlab. The notch frequency is chosen to be 100 Hz and the bandwidth of the filter is 5 Hz for typical applications. The block diagram of the voltage control loop is shown in Figure 15 and the 2P2Z compensator is shown in Equation (28).

$$G_{vc}(z) = \frac{(5.136z^2 + 2.042z - 3.074) \cdot 10^{-5}}{z^2 - 1.998z + 0.9983}$$

(28)

Figure 15. Block diagram of the voltage control loop.

The bode diagram of the whole system is shown in Figure 16. The input power is 1 kW and cross over frequency is 24.4 Hz. A gain margin of 16.5 dB and a phase margin of 54.4 degrees are achieved. According to the system stability criterion, the gain margin and phase margin are sufficient and the robustness of the system is guaranteed [22,23].

Figure 16. Bode diagram of the inverter.

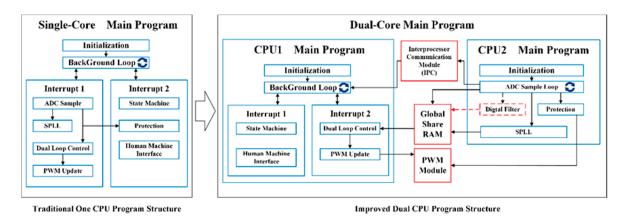

## 3.4. Dual-Core MCU Algorithm

The biggest challenge of the real-time digital control implementation is the calculation speed. Most researchers adopt the analog circuit for loop control when the switching speed is high. Although analog control features innate advantages of high bandwidth, high resolution, and low cost, its control ability is limited to classical control theories. Moreover, the hardware-based structures lack flexibility. By contrast, the digital control is able to perform multiple control loops and advanced algorithms, which make multi-task and multi-function control possible. The software-based compensator can be tuned and expanded easily. Furthermore, the insensitivity to temperature drift and electromagnetic

Energies 2017, 10, 402 13 of 18

interference (EMI) makes it suitable for high frequency switching control. When the control loop is running at 400 kHz, for a 200 MHz MCU, only 500 CPU clock cycles are available for calculation. The CPU cycle consumption of the main calculation modules are shown in Table 1 and one CPU cycle is 5 ns.

| Task Group                                  | Calculation Module      | Time Consumed (CPU Cycle) |

|---------------------------------------------|-------------------------|---------------------------|

| And the Divital Committee (ADC) Committee   | ADC Sample and Hold     | 70                        |

| Analog-to-Digital Conversion (ADC) Sampling | Read ADC results        | 40                        |

| Decal Lang Control                          | 3P3Z Compensator        | 110                       |

| Dual Loop Control                           | 2P2Z Compensator        | 90                        |

| SPLL                                        | SOGI-SPLL               | 89                        |

| PWM                                         | PWM Update              | 15                        |

|                                             | State Machine           | 30                        |

| Auxiliary Module                            | Protection              | 20                        |

|                                             | Human Machine Interface | 10                        |

| Total time consumption (CPU Cycle)          |                         | 474                       |

**Table 1.** Time consumption of the main calculation modules.

Obviously, the total time consumption for these main calculation modules almost reaches the MCU process limit of 500 CPU cycles. For this problem, one solution is to manage the calculation with great accuracy and to arrange each step and each interrupt tightly [24]. The consumption of the computing capability by each module must be measured accurately. This method will greatly increase the difficulty of programming and may cause the program to be unable to modify and expand. Even a small change may overflow the calculation and cause system failure. To overcome this problem, based on a dual-core MCU, a parallel algorithm is adopted. The control program of the inverter can be expressed in Figure 17.

Figure 17. Improvement of the control structure.

For a single-core CPU structure, even if the calculation modules are relatively independent, such as the ADC sample and State machine, the calculation has to be executed sequentially. The interrupt mechanism only affects the sequence of execution but not the total calculation time. Unlike the one-core CPU interrupt strategy, the calculation modules of the program, which are not directly combined, can be executed in parallel at the same time by dual CPU cores. Ideally, the calculation time can be reduced by half. The dual CPU structure is shown in Figure 17. In order to simplify the communication between different CPUs, the modules, which are relatively independent, are distributed in the same CPU. For example, the ADC sample, SOGI-SPLL, and Protection modules are assigned to CPU2. As a result, the main data flow is almost in one direction towards CPU1 because

Energies 2017, 10, 402 14 of 18

those function modules only need to send the data to CPU1. The only communication which is needed is the acknowledgement from CPU2 to CPU1. The acknowledgement is the signal which CPU2 completes the ADC sampling procedure and finishes writing the results to the global share RAM. CPU1 receives the signal, reads the ADC results from the global share RAM, and begins the calculation. The acknowledgement mechanism is implemented by the interprocessor communication module (IPC), which is designed to communicate between the two CPUs. The ADC results are transmitted through the global share RAM, which is suitable for data transfer.

As Figure 18 shows, the calculation modules are rearranged for both CPU cores, and the calculation quantity of CPU1 is greatly reduced. As a result, both CPUs have unused computing margins for further applications, such as digital filters. For the powerful calculation ability and flexible expansion capability, the dual-core MCU system is well suited for a high switching frequency inverter.

Figure 18. Microcontroller unit (MCU) scheme contrast diagram between single-core and dual-core.

## 4. Experimental Results

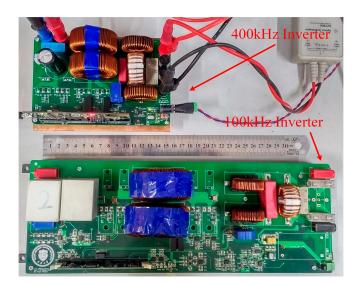

To verify the validity of the theoretical analyses, a 1 kW prototype was built in the laboratory, shown in Figure 19. The 400 kHz inverter is about half the size of the previous 100 kHz prototype. The power density and portability are significantly improved. The parameters of the components are shown in Table 2. The control platform is a TMS320F28377D from Texas Instruments. It is a high performance dual-core MCU running at 200 MHz.

Figure 19. Experimental prototype.

Energies 2017, 10, 402 15 of 18

| Component            | Manufacture | Model       | Value   |

|----------------------|-------------|-------------|---------|

| $S_1, S_2, S_3, S_4$ | Wolfspeed   | C2M0280120D |         |

| $D_1,D_2$            | Wolfspeed   | CVFD20065A  |         |

| $L_{i1}$ , $L_{i2}$  | Magnetics   | 77439A7     | 800 μΗ  |

| $L_{g1},L_{g2}$      | Magnetics   | 77548A7     | 215 μΗ  |

| $C_{f}$              | WIMA        | MKP10       | 0.15 uF |

**Table 2.** Parameters of the proposed system.

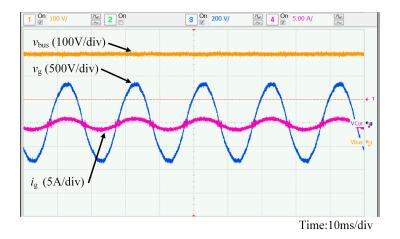

Figure 20 shows the output current  $i_g$  at 100 W. The output current  $i_g$  can track the grid voltage very well when the power output is low. The power factor is 0.99 and the total harmonic distortion THD is 4.8%. The bus voltage is stabilized at 400 V and the ripple is within  $\pm 4$  V.

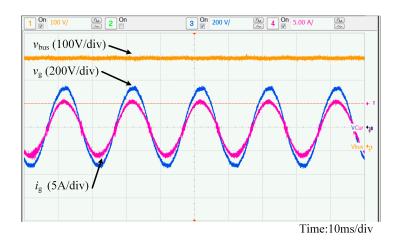

Figure 21 shows the output power at 1 kW. The RMS value of  $i_{\rm g}$  is 4.5 A. Along with the increase of the output power, the waveform of the  $i_{\rm g}$  increases significantly. The power factor is 0.99 and THD is down to 1.8%. The efficiency of the inverter is 96.1% at this moment.

Figure 20. Experimental waveforms of the inverter at low power.

Figure 21. Experimental waveforms of the inverter at rated power.

Also from Figures 20 and 21, it indicates that the proposed inverter can obtain power factors near unity for the output current, constrained THDs, and relatively high efficiencies among the full load range at 400 kHz. For the next-stage work, the efficiency can be further improved through adding resonant snubbers, which may help the inverter to achieve soft-switching characteristics.

Energies 2017, 10, 402 16 of 18

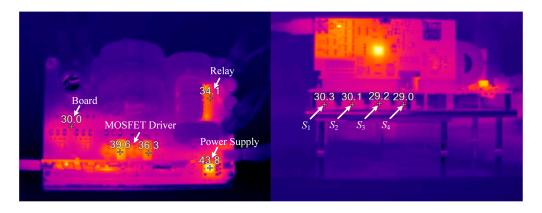

Figure 22 shows a thermal image of the inverter at 1 kW. The temperatures of the switches  $S_1$ - $S_4$  are around 30 centigrade and that of the metal-oxide-semiconductor field-effect transistor (MOSFET) driver is under 40 centigrade. The highest hotspot is the power supply at 43.8 centigrade. Due to the high efficiency and thermal design, the component temperature is in the controllable range, which leaves margins for further higher power levels.

Figure 22. Thermal image of the inverter at rated power.

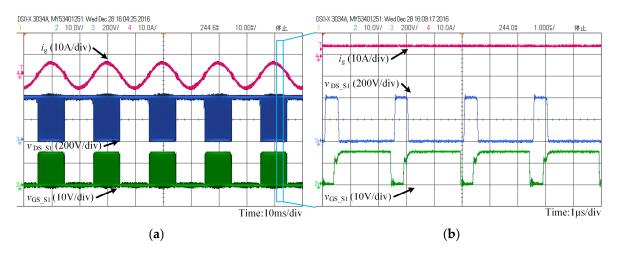

Figure 23a shows the waveforms of the switch and grid current at 1 kW. Figure 23b is the partial enlarged waveform.  $i_g$  is the grid current of the inverter.  $v_{DS}$  is the drain-to-source voltage of the switch  $S_1$ .  $v_{GS}$  is the drive signal of  $S_1$ . As the waveform shows, when  $i_g$  is above zero,  $S_1$  is switched at the high frequency of 400 kHz and thus  $i_g$  in phase with  $v_{DS\_S1}$ . The voltage stress of  $S_1$  is 400 V. Then when  $i_g$  flows negatively, both switches  $S_1$  and  $S_3$  will not function, and instead,  $S_2$  and  $S_4$  will continue to operate.

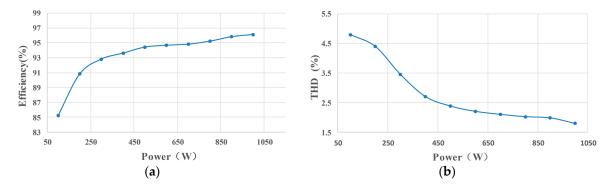

Finally, the relationships between efficiency and THD versus the output power are shown in Figure 24a,b, respectively. The efficiency increases from 85.2% to 96.1% when the output power grows from 100 W to 1000 W. The efficiency reaches the maximum efficiency of 96.1% at the rated condition. The THD is 1.8% at the rated condition. Thus, in small renewable energy applications [25–27], the proposed inverter can achieve outstanding performances, including a relatively high conversion efficiency, high power factor, and low THD.

**Figure 23.** Experimental waveforms of the switch and grid current at rated power. (a) The waveform of  $i_g$ ,  $v_{DS\_S1}$  and  $v_{GS\_S1}$ ; (b) zoom-in waveform of  $i_g$ ,  $v_{DS\_S1}$  and  $v_{GS\_S1}$ .

Energies 2017, 10, 402 17 of 18

**Figure 24.** Efficiency and grid current total harmonic distortion (THD) curves. (a) Efficiency curve; (b) THD curve.

#### 5. Conclusions

A high frequency single phase dual-buck full-bridge grid-connected inverter for small power renewable energy is proposed. Based on the full SiC power devices, the 400 kHz switching frequency is achieved, which contributes to significant reduction of the inverter volume. The design procedure of the proposed inverter is presented and analyzed in detail, which gives a practical design example for a similar type inverter. For the control aspect, the voltage-current dual loop control is employed. The inner current loop is analyzed in detail, which includes the modeling of the equivalent LCL-type inverter and the design of its 3P3Z compensator. The outer voltage loop is also discussed, the model of which is established by energy balance. Moreover, a parallel structure algorithm is conducted based on a dual-core MCU for the first time to control the high frequency inverter. The implementation of the proposed dual-core method is thoroughly discussed. Finally, a prototype is made in the laboratory to validate the appropriateness and feasibility of the theory. The inverter has a high power factor of above 0.99 and a low THD of 1.8% at rated power of 1 kW with the highest efficiency of 96.1%.

**Acknowledgments:** This research was supported by the National Natural Science Foundation of China (Grant: 2015AA050603) and supported by the Tianjin Municipal Science and Technology Commission (Grant: 14ZCZDGX00035). The authors would also like to thank the anonymous reviewers for their valuable comments and suggestions to improve the quality of the paper.

**Author Contributions:** Zhun Meng and Yi-Feng Wang designed the main parts of the study. Liang Yang and Wei Li helped in the fabrication.

**Conflicts of Interest:** The authors declare no conflict of interest.

## References

- 1. Zhang, N.; Tang, H.; Yao, C. A Systematic Method for Designing a PR Controller and Active Damping of the LCL Filter for Single-Phase Grid-Connected PV Inverters. *Energies* **2014**, 7, 3934–3954. [CrossRef]

- 2. Yu, Y.; Zhang, Q.; Liang, B.; Liu, X.; Cui, S. Analysis of a Single-Phase Z-Source Inverter for Battery Discharging in Vehicle to Grid Applications. *Energies* **2011**, *4*, 2224–2235. [CrossRef]

- 3. Jeong, H.G.; Kim, G.S.; Lee, K.B. Second-Order Harmonic Reduction Technique for Photovoltaic Power Conditioning Systems Using a Proportional-Resonant Controller. *Energies* **2013**, *6*, 79–96. [CrossRef]

- 4. Dou, X.; Yang, K.; Quan, X.; Liu, X.; Cui, S. An Optimal PR Control Strategy with Load Current Observer for a Three-Phase Voltage Source Inverter. *Energies* **2015**, *8*, 7542–7562. [CrossRef]

- 5. Lorzadeh, I.; Abyaneh, H.A.; Savaghebi, M.; Bakhshai, A.; Guerrero, J.M. Capacitor Current Feedback-Based Active Resonance Damping Strategies for Digitally-Controlled Inductive-Capacitive-Inductive-Filtered Grid-Connected Inverters. *Energies* 2016, 9, 642. [CrossRef]

- Hong, F.; Wang, C.H.; Ji, D.Y.; Yan, Y.G. Three level dual Buck half bridge inverter. In Proceedings of the International Conference on Sustainable Power Generation and Supply, Nanjing, China, 6–7 April 2009; pp. 1–5.

- 7. Yao, Z.; Xiao, L.; Yan, Y. Control Strategy for Series and Parallel Output Dual-Buck Half Bridge Inverters Based on DSP Control. *IEEE Trans. Power Electron.* **2009**, 24, 434–444.

Energies 2017, 10, 402 18 of 18

8. Liu, M.; Hong, F.; Wang, C. Three-Level Dual Buck Inverter With Coupled-Inductance. In Proceedings of the Power and Energy Engineering Conference (APPEEC), Chengdu, China, 28–31 March 2010; pp. 1–4.

- 9. Yao, Z.; Xiao, L.; Yan, Y. Dual-Buck Full-Bridge Inverter With Hysteresis Current Control. *IEEE Trans. Ind. Electron.* **2009**, *56*, 3153–3160.

- 10. Hong, F.; Liu, J.; Ji, B.; Zhou, Y. Single Inductor Dual Buck Full-Bridge Inverter. *IEEE Trans. Ind. Electron.* **2015**, 62, 4869–4877. [CrossRef]

- 11. Zhang, L.; Sun, K.; Xing, Y.; Zhao, J. A Family of Five-Level Dual-Buck Full-Bridge Inverters for Grid-tied Applications. *IEEE Trans. Power Electron.* **2016**, *31*, 7029–7042. [CrossRef]

- 12. Cho, Y.W.; Cha, W.J.; Kwon, J.M.; Kwon, B.H. Improved single-phase transformerless inverter with high power density and high efficiency for grid-connected photovoltaic systems. *IET Renew. Power Gener.* **2016**, 10, 166–174. [CrossRef]

- 13. Yao, Z.; Hu, G. Comparison of Dual-Buck Full-Bridge Inverter with Different Inductor Structures. In Proceedings of the Asia-Pacific Power & Energy Engineering Conference, Wuhan, China, 25–28 March 2011; pp. 1–3.

- 14. Swamy, M.M.; Kang, J.K.; Shirabe, K. Power Loss, System Efficiency, and Leakage Current Comparison Between Si IGBT VFD and SiC FET VFD With Various Filtering Options. *IEEE Trans. Ind. Appl.* **2015**, *51*, 3858–3866. [CrossRef]

- 15. Rąbkowski, J.; Płatek, T. Comparison of the power losses in 1700V Si IGBT and SiC MOSFET modules including reverse conduction. In Proceedings of the European Conference on Power Electronics and Applications, Geneva, Switzerland, 8–10 September 2015; pp. 1–10.

- 16. Madhusoodhanan, S.; Mainali, K.; Tripathi, A.K.; Kadavelugu, A. Power Loss Analysis of Medium-Voltage Three-Phase Converters Using 15-kV/40-A SiC N-IGBT. *IEEE J. Emerg. Sel. Top. Power Electron.* **2016**, *4*, 902–917. [CrossRef]

- 17. Jiang, H.; Wei, J.; Dai, X.; Ke, M. SiC Trench MOSFET with Shielded Fin-Shaped Gate to Reduce Oxide Field and Switching Loss. *IEEE Electron Device Lett.* **2016**, *37*, 1324–1327. [CrossRef]

- 18. Lu, M.; Wang, X.; Loh, P.; Blaabjerg, F. Resonance Interaction of Multi-Parallel Grid-Connected Inverters with LCL Filter. *IEEE Trans. Power Electron.* **2016**, *32*, 894–899. [CrossRef]

- 19. Kim, H.; Kim, K.H. Filter design for grid connected PV inverters. In Proceedings of the IEEE International Conference on Sustainable Energy Technologies, Singapore, 24–27 November 2008; pp. 1070–1075.

- Bhardwaj, M.; Choudhury, S.; Xue, V.; Akin, B. Online LCL filter compensation using embedded FRA. In Proceedings of the IEEE Applied Power Electronics Conference and Exposition, Fort Worth, TX, USA, 16–20 March 2014; pp. 3186–3191.

- 21. Ciobotaru, M.; Teodorescu, R.; Blaabjerg, F. A New Single-Phase PLL Structure Based on Second Order Generalized Integrator. In Proceedings of the 37th IEEE Power Electronics Specialists Conference, Jeju, Korea, 18–22 June 2006; pp. 1–6.

- 22. Liu, Y.; Wu, W.; He, Y.; Lin, Z. An Efficient and Robust Hybrid Damper for Based Grid-Tied Inverter with Strong Grid-Side Harmonic Voltage Effect Rejection. *IEEE Trans. Ind. Electron.* **2015**, *63*, 926–936. [CrossRef]

- 23. Bao, C.; Ruan, X.; Wang, X.; Li, W. Step-by-Step Controller Design for LCL-Type Grid-Connected Inverter with Capacitor–Current-Feedback Active-Damping. *IEEE Trans. Power Electron.* **2014**, *29*, 1239–1253.

- Xue, L.; Shen, Z.; Boroyevich, D.; Mattavelli, P. GaN-based high frequency totem-pole bridgeless PFC design with digital implementation. In Proceedings of the Applied Power Electronics Conference and Exposition, Charlotte, NC, USA, 15–19 March 2015; pp. 759–766.

- 25. Tanimoto, Y.; Saito, A.; Matsuura, K.; Kikuchihara, H. Power-Loss Prediction of High-Voltage SiC-mosfet, Circuits With Compact Model Including Carrier-Trap Influences. *IEEE Trans. Power Electron.* **2016**, 31, 4509–4516. [CrossRef]

- 26. Turzynski, M.; Kulesza, W. A simplified behavioral MOSFET model based on parameters extraction for circuit simulations. *IEEE Trans. Power Electron.* **2016**, *31*, 3096–3105. [CrossRef]

- 27. Miyake, M.; Ueno, M.; Feldmann, U.; Mattausch, H.J. Modeling of SiC IGBT Turn-Off Behavior Valid for Over 5-kV Circuit Simulation. *IEEE Trans. Electron Devices* **2013**, *60*, 622–629. [CrossRef]

© 2017 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).