Transparent Fingerprint Sensor System for Large Flat Panel Display

Abstract

:1. Introduction

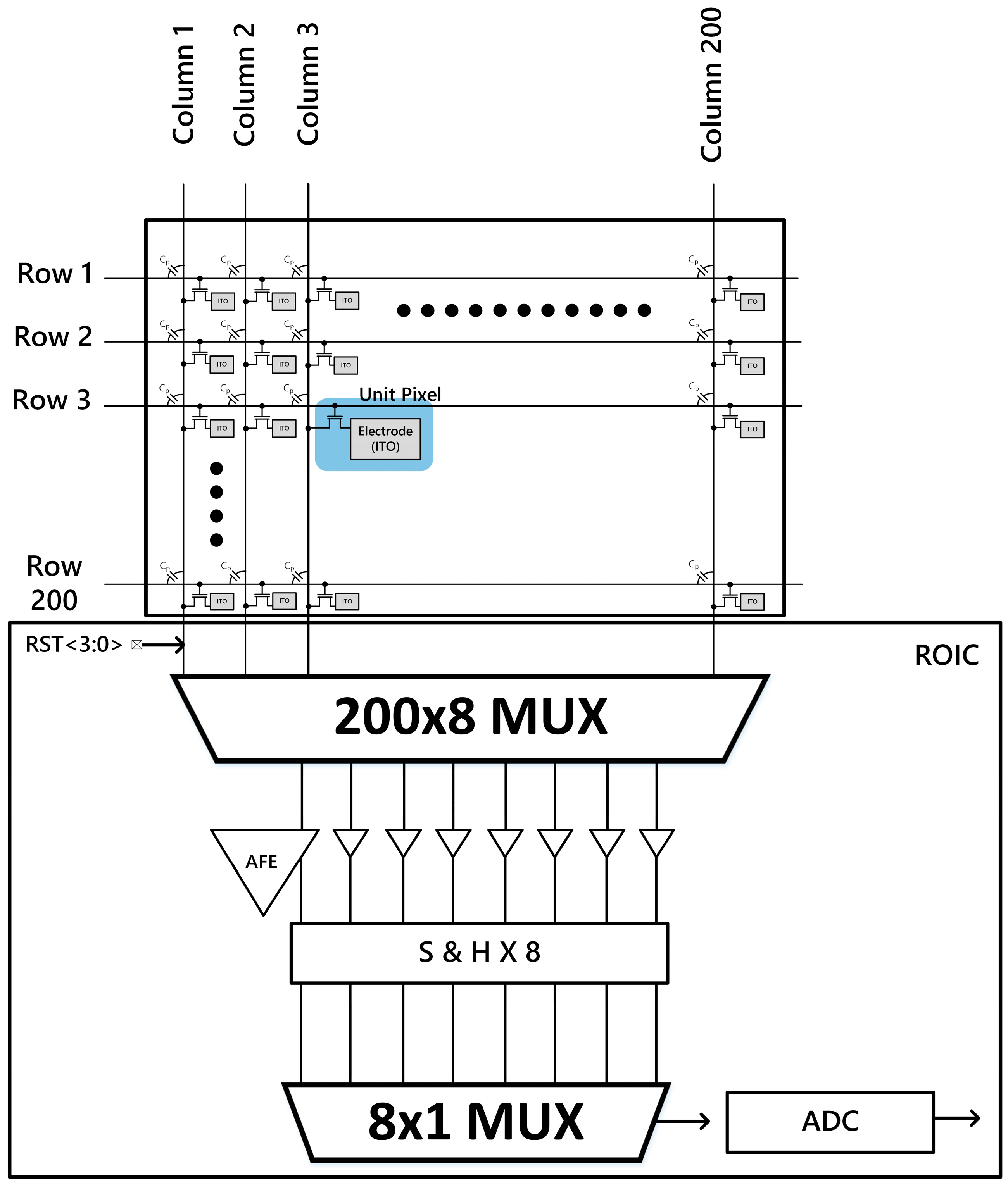

2. Structure of a Transparent Sensor Panel

2.1. Structure of a Proposed Fingerprint Sensor Pixel

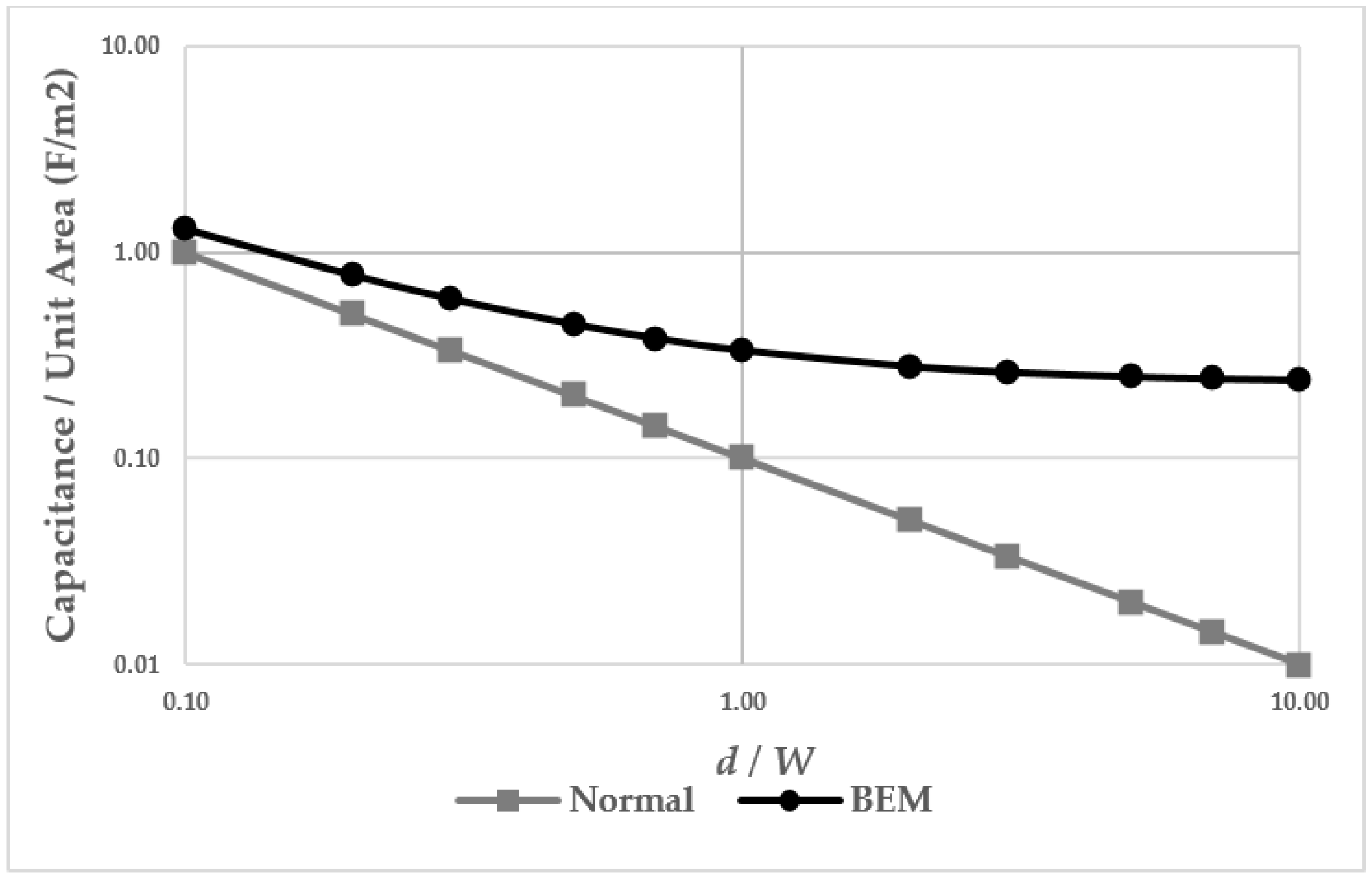

2.2. Calculating the Self-Capacitance of the Pixel Structure

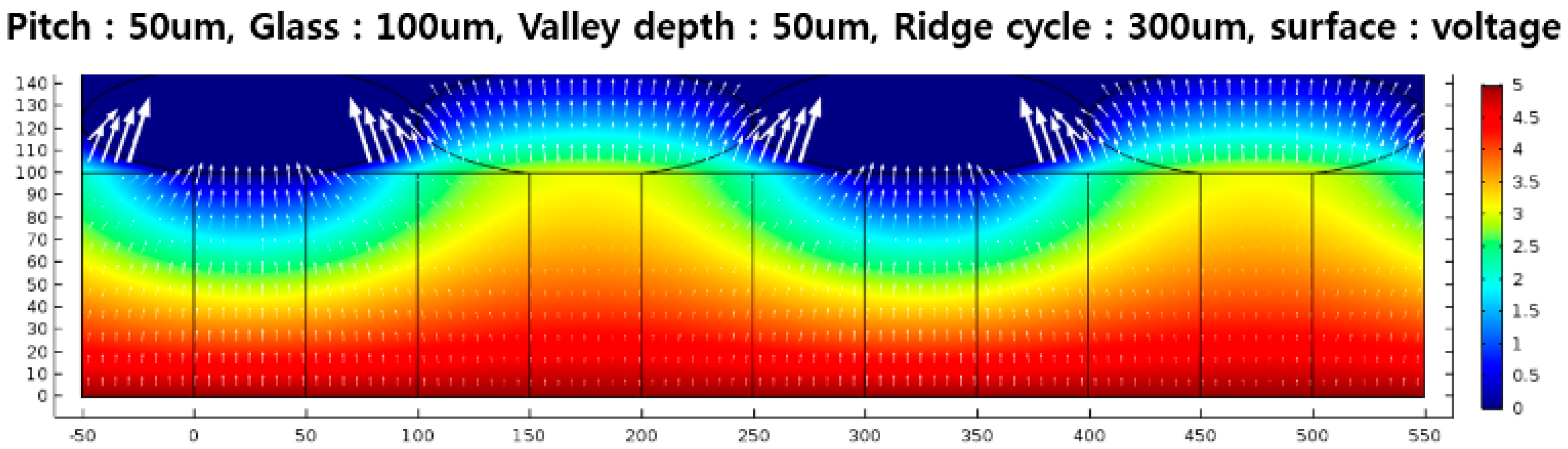

2.3. Fingerprint Capacitance Modeling

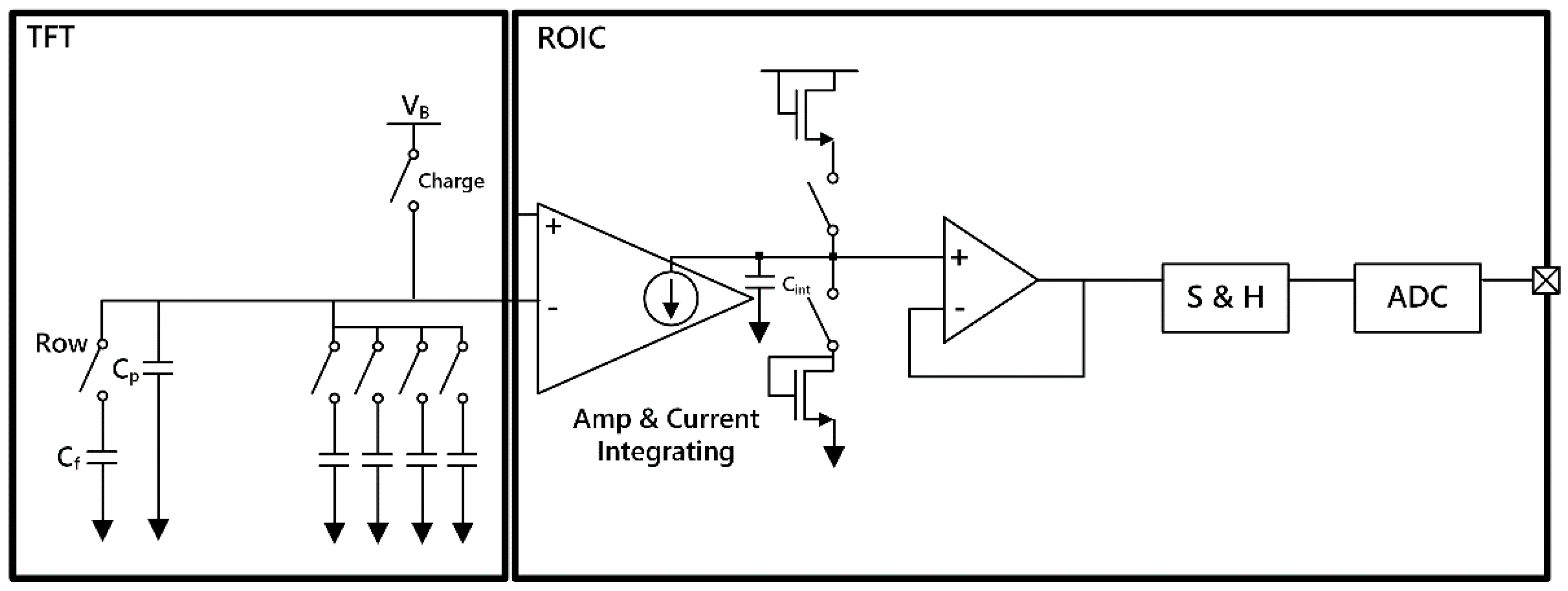

3. ROIC Structure

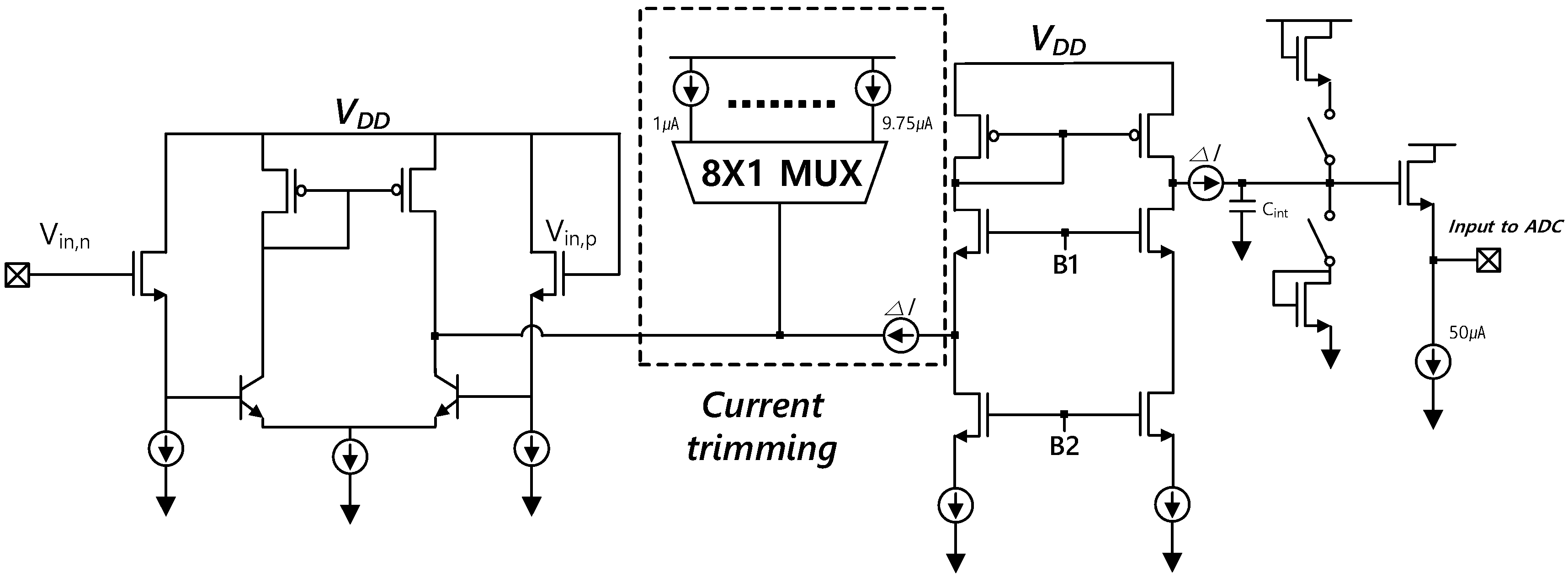

3.1. AFE Structure

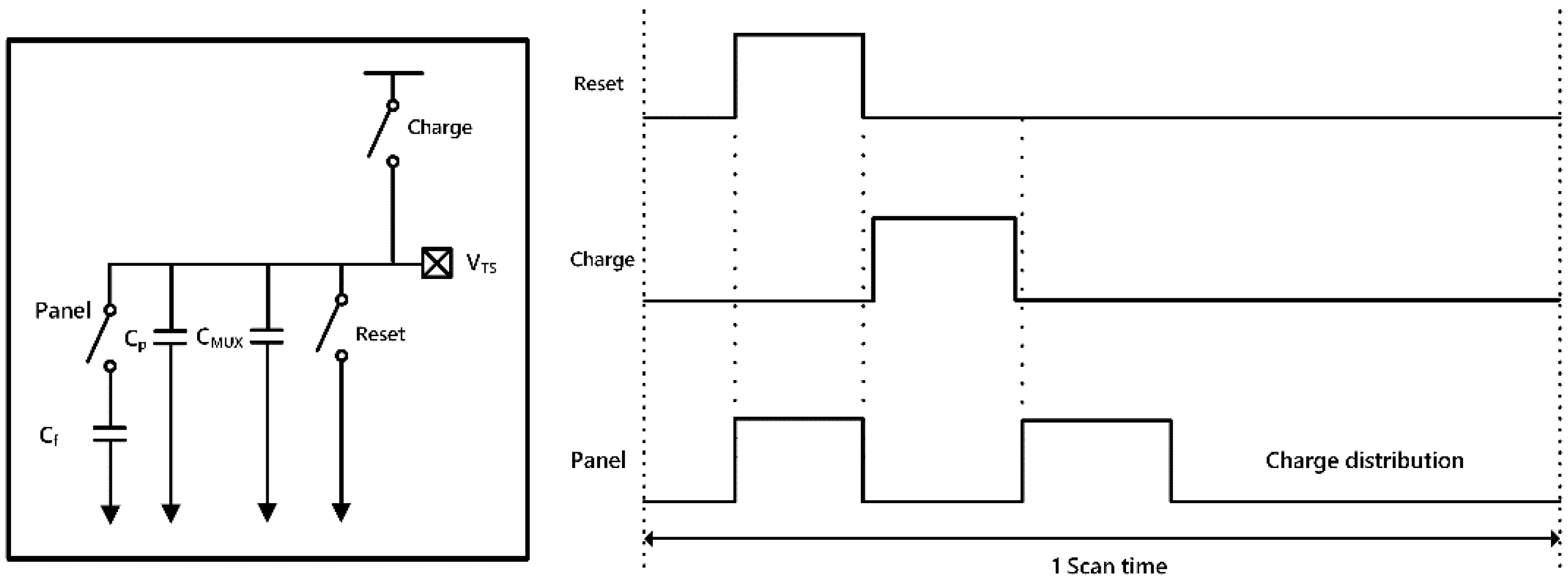

3.2. ROIC Signal Processing Sequence

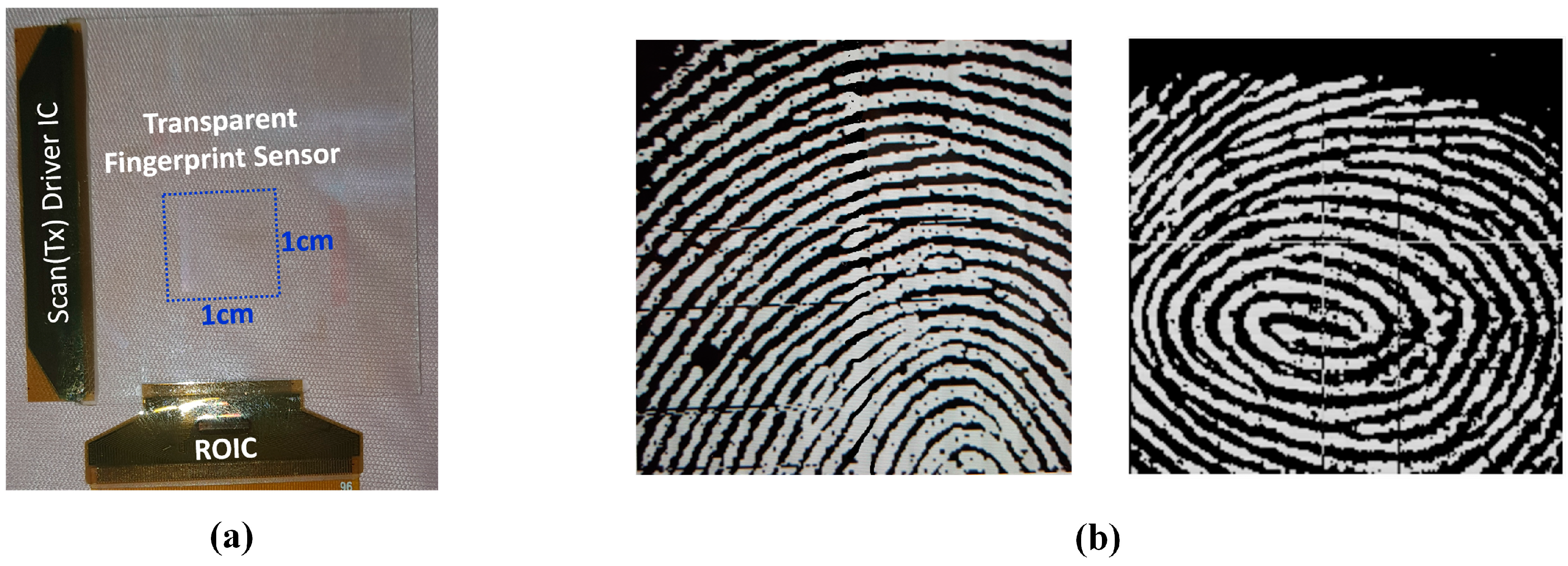

4. Measurement Results

5. Conclusions

Acknowledgments

Author Contributions

Conflicts of Interest

References

- Jain, A.; Bolle, R.; Pankanti, S. Biometrics identification. Commun. ACM 2000, 43, 90–98. [Google Scholar] [CrossRef]

- Jain, A.K.; Ross, A.; Prabhakar, S. An introduction to biometric recognition. IEEE Circuits Syst. Video Technol. 2004, 14, 4–20. [Google Scholar] [CrossRef]

- Hashido, R.; Suzuku, A. A capacitive fingerprint sensor chip using low-temperature poly-Si TFTs on a glass substrate and a novel and unique sensing method. IEEE J. Solid-State Circuits 2003, 38, 274–280. [Google Scholar] [CrossRef]

- Tartagni, M.; Guerrieri, R. A fingerprint sensor based on the feedback capacitive sensing scheme. IEEE J. Solid-State Circuits 1998, 33, 133–142. [Google Scholar] [CrossRef]

- Liao, Y.; Chang, C. Flat panel fingerprint optical sensor using TFT technology. In Proceedings of the IEEE Sensors, Busan, Korea, 1–4 November 2015. [Google Scholar]

- Tang, H.; Lu, Y. 3-D ultrasonic fingerprint sensor-on-a-chip. IEEE J. Solid-State Circuits 2016, 51, 2522–2533. [Google Scholar] [CrossRef]

- Chuang, C.-S.; Fung, T.-C.; Mullins, B.G.; Nomura, K.; Kamiya, T.; Shieh, H.P.D.; Hosono, H.; Kanicki, J. Photosensitivity of amorphous IGZO TFTs for active-matrix flat-panel displays. SID Symp. Dig. Technol. Pap. 2008, 13, 1215–1218. [Google Scholar] [CrossRef] [Green Version]

- Hayashi, R.; Sato, A.; Ofuji, M.; Abe, K.; Yabuta, H.; Sato, M.; Kumomi, H. Improved amorphous In-Ga-Zn-O TFTs. SID Symp. Dig. Technol. Pap. 2008, 42, 621–624. [Google Scholar] [CrossRef]

- Catalan, S.; Jose, M. Capacitance evaluation on parallel-plate capacitors by means of finite element analysis. In Proceedings of the International Conference on Renewable Energies and Power Quality, Valencia, Spain, 15–17 April 2009. [Google Scholar]

- Nishiyama, H.; Nakamura, M. Form and capacitance of parellel-plate capacitors. IEEE Trans. Compon. Packag. Manuf. Technol. 1994, 17, 477–484. [Google Scholar] [CrossRef]

- COMSOL Multiphysics. Available online: https://www.comsol.com/ (accessed on 16 January 2018).

- Tiao, Y.; Sheu, M. A CMOS readout circuit for LTPS-TFT capacitive fingerprint sensor. In Proceedings of the IEEE Electron Devices and Solid-State Circuits, Hong Kong, China, 19–21 December 2005. [Google Scholar]

- Ackland, B.; Comizzoll, R.; Dickinson, A.; Inglis, C.; Manchanda, L.; Mandis, S.; Martin, E.; O’Gorman, L.; Silveman, P.; Weber, G. A robust 1.8-V 250-W direct-contact 500-dpi fingerprint sensor. In Proceedings of the IEEE International Solid-State Circuits Conference (ISSCC) Digest of Technical Papers, San Francisco, CA, USA, 5–7 February 1998; pp. 284–285. [Google Scholar]

- Jung, S.; Hierold, C.; Scheiter, T.; Werner von Basse, P.; Thewes, R.; Goser, K.; Weber, W. Intelligent CMOS fingerprint sensors. In Proceedings of the 10th International Conference Solid-State Sensors and Actuators Digest Technical Papers, Sendai, Japan, 2–4 November 1999; pp. 966–969. [Google Scholar]

- Adachi, T.; Machida, K.; Morimura, H.; Shigematsu, S.; Tanabe, Y. A single-chip fingerprint sensor and identifier. IEEE J. Solid-State Circuits 1999, 34, 1852–1859. [Google Scholar]

| By Equation (1) | By BEM (d/W = 1.5) |

|---|---|

| 171 aF | 513 aF |

| Pixel Information | Sensor Array Information | |||||

|---|---|---|---|---|---|---|

| Unit Pixel Dimension | Sensing Electrode Dimension | Resolution | Sensor Array Dimension | PPI | Column Line Resistance | Column Line Capacitance |

| 50 μm × 50 μm | 44 μm × 44 μm | 200 × 200 | 1 cm × 1 cm | 508 | 66 kΩ | 0.3 pF |

| Equation (1) | BEM | Commercial Tool |

|---|---|---|

| 171 aF | 513 aF | 400 aF |

| Sequence | Vin,n | Vin,p | Vin,p − Vin,n | ∆(Vin,p − Vin,n) (Ridge-Valley) |

|---|---|---|---|---|

| Charge | 0 | Vref | 3.3 V | - |

| Reset | Vref | Vref | 0 V | - |

| Charge Sharing | Vref | 300 μV | 150 μV |

| Parameter | Specification | |

|---|---|---|

| Sensor System | Sensor Array | 200 × 200 |

| Pixel Area | 50 × 50 μm2 | |

| Electrode Plate Size | 44 × 44 μm2 | |

| Total Scan time/frame | 500 ms | |

| ROIC | Power Supply | 3.3 V |

| Power Dissipation | 9 mW | |

| Process Technology | 180 nm Magnachip | |

| Chip Area | 5560 × 720 μm2 |

© 2018 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).

Share and Cite

Seo, W.; Pi, J.-E.; Cho, S.H.; Kang, S.-Y.; Ahn, S.-D.; Hwang, C.-S.; Jeon, H.-S.; Kim, J.-U.; Lee, M. Transparent Fingerprint Sensor System for Large Flat Panel Display. Sensors 2018, 18, 293. https://doi.org/10.3390/s18010293

Seo W, Pi J-E, Cho SH, Kang S-Y, Ahn S-D, Hwang C-S, Jeon H-S, Kim J-U, Lee M. Transparent Fingerprint Sensor System for Large Flat Panel Display. Sensors. 2018; 18(1):293. https://doi.org/10.3390/s18010293

Chicago/Turabian StyleSeo, Wonkuk, Jae-Eun Pi, Sung Haeung Cho, Seung-Youl Kang, Seong-Deok Ahn, Chi-Sun Hwang, Ho-Sik Jeon, Jong-Uk Kim, and Myunghee Lee. 2018. "Transparent Fingerprint Sensor System for Large Flat Panel Display" Sensors 18, no. 1: 293. https://doi.org/10.3390/s18010293