Communication

# Improved Properties of Post-Deposition Annealed Ga<sub>2</sub>O<sub>3</sub>/SiC and Ga<sub>2</sub>O<sub>3</sub>/Al<sub>2</sub>O<sub>3</sub>/SiC Back-Gate Transistors Fabricated by Radio Frequency Sputtering

Hee-Jae Lee <sup>1</sup>, Geon-Hee Lee <sup>1</sup>, Seung-Hwan Chung <sup>1</sup>, Dong-Wook Byun <sup>1</sup>, Michael A. Schweitz <sup>1</sup>, Dae Hwan Chun <sup>2</sup>, Nack Yong Joo <sup>2</sup>, Minwho Lim <sup>3</sup>, Tobias Erlbacher <sup>3</sup> and Sang-Mo Koo <sup>1</sup>,\*

- Department of Electronic Materials Engineering, Kwangwoon University, Seoul 01897, Republic of Korea; tkrkek123@kw.ac.kr (H.-J.L.); ghlee117@kw.ac.kr (G.-H.L.); wkdrn1394@kw.ac.kr (S.-H.C.); byun1994@kw.ac.kr (D.-W.B.); michael.schweitz@schweitzlee.com (M.A.S.)

- <sup>2</sup> Electronic Devices Research Team, Hyundai Motor Group, Uiwang-si 16082, Republic of Korea; chundh@hyundai.com (D.H.C.); n.y.joo@hyundai.com (N.Y.J.)

- Fraunhofer Institute for Integrated Systems and Device Technology, Schottkystrasse 10, 91058 Erlangen, Germany; minwho.lim@iisb.fraunhofer.de (M.L.); tobias.erlbacher@iisb.fraunhofer.de (T.E.)

- \* Correspondence: smkoo@kw.ac.kr; Tel.: +82-2-940-5763

Abstract: The high breakdown electric field, n-type doping capability, availability of high-quality substrates, and high Baliga's figure of merit of Ga<sub>2</sub>O<sub>3</sub> demonstrate its potential as a next-generation power semiconductor material. However, the thermal conductivity of Ga<sub>2</sub>O<sub>3</sub> is lower than that of other wide-bandgap materials, resulting in the degradation of the electrical performance and reduced reliability of devices. The heterostructure formation on substrates with high thermal conductivity has been noted to facilitate heat dissipation in devices. In this work, Ga<sub>2</sub>O<sub>3</sub> thin films with an Al<sub>2</sub>O<sub>3</sub> interlayer were deposited on SiC substrates by radio frequency sputtering. Post-deposition annealing was performed at 900 °C for 1 h to crystallize the Ga<sub>2</sub>O<sub>3</sub> thin films. The Auger electron spectroscopy depth profiles revealed the interdiffusion of the Ga and Al atoms at the Ga<sub>2</sub>O<sub>3</sub>/Al<sub>2</sub>O<sub>3</sub> interface after annealing. The X-ray diffraction (XRD) results displayed improved crystallinity after annealing and adding the Al<sub>2</sub>O<sub>3</sub> interlayer. The crystallite size increased from 5.72 to 8.09 nm as calculated by the Scherrer equation using the full width at half maximum (FWHM). The carrier mobility was enhanced from 5.31 to 28.39 cm<sup>2</sup>  $V^{-1}$  s<sup>-1</sup> in the annealed  $Ga_2O_3$  thin films on  $Al_2O_3/SiC$ . The transfer and output characteristics of the  $Ga_2O_3/SiC$  and  $Ga_2O_3/Al_2O_3/SiC$  back-gate transistors reflect the trend of the XRD and Hall measurement results. Therefore, this work demonstrated that the physical and electrical properties of the Ga<sub>2</sub>O<sub>3</sub>/SiC back-gate transistors can be improved by post-deposition annealing and the introduction of an Al<sub>2</sub>O<sub>3</sub> interlayer.

Keywords: gallium oxide; heterostructure; wide bandgap; transistor; aluminum oxide; semiconductor

Citation: Lee, H.-J.; Lee, G.-H.; Chung, S.-H.; Byun, D.-W.; Schweitz, M.A.; Chun, D.H.; Joo, N.Y.; Lim, M.; Erlbacher, T.; Koo, S.-M. Improved Properties of Post-Deposition Annealed Ga<sub>2</sub>O<sub>3</sub>/SiC and Ga<sub>2</sub>O<sub>3</sub>/ Al<sub>2</sub>O<sub>3</sub>/SiC Back-Gate Transistors Fabricated by Radio Frequency Sputtering. *Micro* 2023, 3, 775–784. https://doi.org/10.3390/ micro3040055

Academic Editors: Ajit Roy and Hiroshi Furuta

Received: 27 July 2023 Revised: 31 August 2023 Accepted: 25 September 2023 Published: 30 September 2023

Copyright: © 2023 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

# 1. Introduction

Although Si-based semiconductors have been widely used in power electronic devices, the narrow bandgap of Si (1.1 eV) limits its applications owing to its instability in harsh environments, such as high temperatures [1,2]. Wide-bandgap semiconductors, such as GaN, 4H-SiC, and  $Ga_2O_3$ , are important materials for high-frequency, -power, and temperature devices [2-4]. Among these,  $Ga_2O_3$  has a bandgap (~4.9 eV) that is significantly higher than that of 4H-SiC (~3.3 eV) and GaN (~3.4 eV) [5-7]. Owing to its high breakdown electric field (~8 MV cm<sup>-1</sup>), n-type doping capability, availability of high-quality substrates, and high Baliga's figure of merit (~3400),  $Ga_2O_3$  is attracting extensive attention as a next-generation power semiconductor material [5,6,8-11].

Despite the advantages of  $Ga_2O_3$ , its thermal conductivity (11–27  $Wm^{-1}~K^{-1}$ ) is lower than that of other wide-bandgap materials, such as SiC (370  $Wm^{-1}~K^{-1}$ ) and GaN

(253  $\mathrm{Wm^{-1}\ K^{-1}}$ ). The heat generated in  $\mathrm{Ga_2O_3}$  may thus increase the lattice temperature, thereby affecting the carrier mobility in current devices, potentially resulting in critical degradation of electrical performance and device reliability [10,11]. For high-power and frequency applications, thermal management is an inevitable consideration for reducing device degradation [11,12]. By forming heterostructures on substrates with high thermal conductivity, such as 4H-SiC, heat dissipation in devices can be facilitated [10,13].

For  $\varepsilon$ -Ga<sub>2</sub>O<sub>3</sub> and ZnO, which have similar crystal structures, previous studies showed that an amorphous Al<sub>2</sub>O<sub>3</sub> interface buffer layer can improve the crystallinity of the thin films [14,15]. Moreover, as Ga<sub>2</sub>O<sub>3</sub> has an ultra-wide bandgap, few gate dielectric materials can achieve conduction band offsets of over 1 eV, which is favorable for metal-oxide-semiconductor structures [16]. Recently, materials, including Al<sub>2</sub>O<sub>3</sub> and its alloys, are being broadly investigated for use as a gate or buffer oxide layers in metal-oxide-semiconductor field-effect transistors [16–20].

Channel control of MOSFETs has been improved by adopting various gate structures. Multi-gate MOSFETs (MGMOS), as well as gate-all-around (GAA) transistors, are investigated to increase the gate control and the integration density [21]. The double-gate structure consisting of top and back gate also improves the gate controllability like short channel effects [22]. However, there are not many studies on  $Ga_2O_3$  transistors that investigate the effect of multi-gate including back-gate transistors. Therefore, it is necessary to study the characteristics and improve the performance of  $Ga_2O_3$  transistors using back gates.

In this work, we deposited  $Ga_2O_3$  and  $Al_2O_3$  films on n-type 4H-SiC substrates by radio frequency (RF) sputtering. Post-deposition annealing at 900 °C was performed to crystallize the  $Ga_2O_3$  thin films. The structural and electrical characteristics of the films were analyzed by Auger electron spectroscopy (AES), X-ray diffraction (XRD), Hall measurements, and current–voltage (I–V) measurements.

## 2. Experimental Details

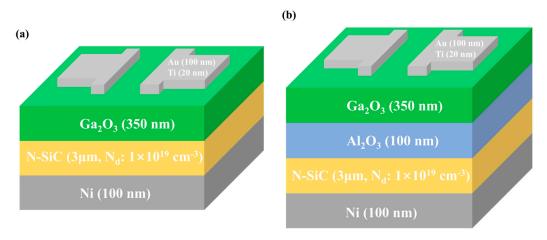

Figure 1a,b show schematics of the fabricated structures, comprising Ga<sub>2</sub>O<sub>3</sub> on SiC and Ga<sub>2</sub>O<sub>3</sub> on Al<sub>2</sub>O<sub>3</sub>/SiC, respectively. N-type 4H-SiC (0004) substrates with a doping concentration of  $1 \times 10^{19}$  cm<sup>-3</sup> were cleaned using acetone, methanol, and deionized water for 15 min each. The native oxide layer was stripped using a buffered oxide etch with a 30:1 ratio of HF:NH<sub>4</sub>F for 5 min. Substrate back-side metal in the form of a 100 nm thick Ni layer was deposited by an electron beam (E-beam) evaporator (KVE-T8065, Korea Vacuum Co., Ltd., Daegu, Republic of Korea) with a working pressure of  $5 \times 10^{-4}$  Pa. Ohmic contacts were formed at the 4H-SiC/Ni interface by rapid thermal annealing at 1000 °C for 60 s under an N<sub>2</sub> atmosphere. Ga<sub>2</sub>O<sub>3</sub>- and Al<sub>2</sub>O<sub>3</sub>-sintered ceramic targets (Toshima Manufacturing Co., Ltd., Saitama, Japan. purity of 99.99%) were used for RF sputtering. In Figure 1a, Ga<sub>2</sub>O<sub>3</sub> films were deposited to a thickness of ~350 nm on cleaned N-SiC substrates for 200 min. In Figure 1b, Al<sub>2</sub>O<sub>3</sub> (~100 nm, 200 min) and Ga<sub>2</sub>O<sub>3</sub> (~350 nm, 200 min) films were deposited on the substrates. The sputtering chamber base and working pressures were maintained at  $6 \times 10^{-4}$  and 3 Pa, respectively. Sputtering was performed at room temperature (25 °C), with no external substrate heating, 120 W sputtering power. and Ar gas flow rate of 4 sccm. Thin films were subsequently annealed at 900 °C for 60 min under an  $N_2$  atmosphere using a tube furnace at  $101.325 \times 10^3$  Pa. The top Ti (20 nm)/Au (100 nm) electrodes were deposited on the  $Ga_2O_3$  thin films using an E-beam evaporator. The distance between the source and drain was 100  $\mu$ m.

Figure 1. Schematic of the (a) Ga<sub>2</sub>O<sub>3</sub>/SiC and (b) Ga<sub>2</sub>O<sub>3</sub>/Al<sub>2</sub>O<sub>3</sub>/SiC structures.

### 3. Characterization and Instrumentation

AES depth profiling was conducted using a PHI 710 scanning Auger probe (ULVAC-PHI, Kanagawa, Japan) with electron beam energy of 5 kV, target current of 5 nA, and a SiO<sub>2</sub> sputtering rate of 29.4 nm·min<sup>-1</sup> to confirm the depth-dependent atomic concentration of the samples. The crystallinity and orientations of the Ga<sub>2</sub>O<sub>3</sub> thin films were examined using XRD (Dmax2500/PC, Rigaku, Tokyo, Japan) by 20 scanning with CuK $\alpha$  radiation ( $\lambda$  = 0.15406 nm) at 200 mA and 40 kV. Electrical properties of the Ga<sub>2</sub>O<sub>3</sub> thin films, including mobility, charge carrier concentrations, and resistivity, were analyzed by Hall effect measurements (HMS-5000, Ecopia Corporation, Anyang, Republic of Korea). I–V characteristics of the devices were measured by a Keithley 4200-SCS (Cleveland, OH, USA) parameter analyzer. Electrical measurements were carried out on the devices by sweeping the gate-to-source voltage (V<sub>GS</sub>) from -6 to +2 V and drain-to-source voltage (V<sub>DS</sub>) from 0 to +10 V.

### 4. Results and Discussion

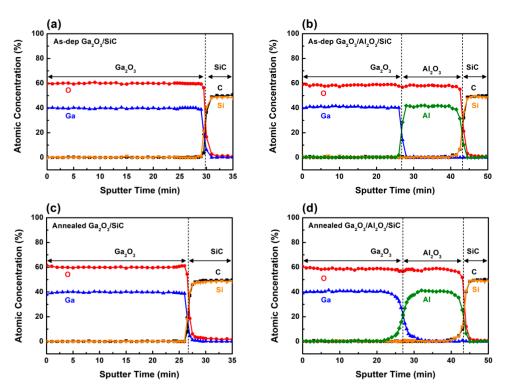

The AES measurements were carried out to obtain a depth profile of Ga, Al, O, Si, and C elements in order to understand their diffusion behaviors at the interface during annealing. Figure 2a–d show depth profiles of the as-deposited and annealed  $Ga_2O_3/SiC$  and  $Ga_2O_3/Al_2O_3/SiC$  structures. In the  $Ga_2O_3/SiC$  structures (Figure 2a,c), sharp interfaces were observed between the  $Ga_2O_3$  thin films and SiC substrates. Meanwhile, in the  $Ga_2O_3/Al_2O_3/SiC$  structures (Figure 2b,d), Al, O, Si, and C atoms had not diffused into the opposite SiC substrates or  $Al_2O_3$  films. However, gradient changes of Ga and Al atomic concentrations at the  $Ga_2O_3/Al_2O_3$  interface indicate the interdiffusion of Ga and Al atoms [23,24]. Therefore,  $(Al_xGa_{1-x})_2O_3$  ternary compounds at the  $Ga_2O_3/Al_2O_3$  interfaces were formed during the annealing of the devices.

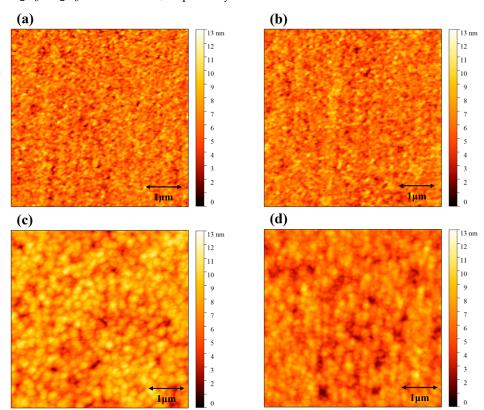

In order to investigate the surface of  $Ga_2O_3$  films, atomic force microscopy (AFM) was performed with a scanned area of  $5\times 5~\mu m^2$ . Figure 3 shows morphological AFM 2D images of as-deposited and annealed  $Ga_2O_3$  films on SiC and  $Al_2O_3$ . The root mean square (rms) roughness was (a) 0.821, (b) 0.845, (c) 1.324, and (d) 1.359 nm, respectively. The result shows that the surfaces of the annealed samples are rougher than the as deposited sample, and thus the annealing treatment may provide energy to atoms in the films and induce the recrystallization of  $Ga_2O_3$  films.

**Figure 2.** AES depth profiles of the as-deposited and annealed (900 °C) (**a**,**c**)  $Ga_2O_3/SiC$  and (**b**,**d**)  $Ga_2O_3/Al_2O_3/SiC$  structures, respectively.

**Figure 3.** AFM images of the as-deposited and annealed (a,c)  $Ga_2O_3/SiC$  and (b,d)  $Ga_2O_3/Al_2O_3/SiC$  back-gate transistors, respectively.

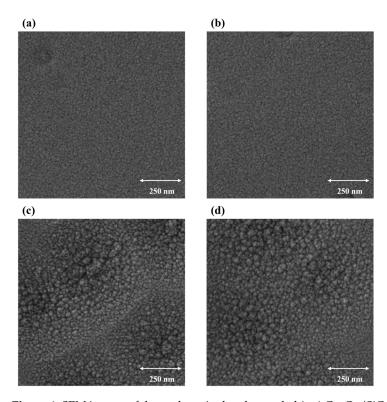

Figure 4 illustrates the scanning electron microscopy (SEM) images of as deposited and annealed  $Ga_2O_3$  films on SiC and  $Al_2O_3$ , respectively. It can be clearly seen that larger crystals were formed after the annealing process at 900 °C. Moreover, as shown in

Figure 4c,d, annealed Ga<sub>2</sub>O<sub>3</sub> thin films possess well-defined grain boundaries which may affect the Hall mobility of devices.

**Figure 4.** SEM images of the as-deposited and annealed ( $\mathbf{a}$ , $\mathbf{c}$ ) Ga<sub>2</sub>O<sub>3</sub>/SiC and ( $\mathbf{b}$ , $\mathbf{d}$ ) Ga<sub>2</sub>O<sub>3</sub>/Al<sub>2</sub>O<sub>3</sub>/SiC back-gate transistors, respectively.

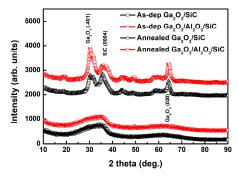

The XRD  $2\theta$ – $\theta$  patterns at  $\theta$  of 10– $90^{\circ}$  of the RF-sputtered  $Ga_2O_3$  thin films with and without an  $Al_2O_3$  interlayer are shown in Figure 5. For the as-deposited samples, only strong diffraction peaks of the 4H-SiC (0004) substrates were noted [25,26]. The absence of any  $Ga_2O_3$  peaks indicates that the as-deposited thin films are in an amorphous state [27]. After annealing at  $900~^{\circ}$ C, three main peaks were noted at  $30.36^{\circ}$ ,  $64.36^{\circ}$ , and  $35.48^{\circ}$ , corresponding to  $Ga_2O_3(-401)$  [28],  $Ga_2O_3(020)$  [9,29], and 4H-SiC(0004), respectively. Furthermore, diffraction peaks of  $Al_2O_3$  were not observed in the  $Ga_2O_3/Al_2O_3/SiC$  structure, indicating that the deposited  $Al_2O_3$  films remained amorphous, even after annealing at  $900~^{\circ}$ C. This can be attributed to the low annealing temperature in this experiment, which, according to the literature, is too low to cause a phase change from amorphous to crystalline  $Al_2O_3$  [30]. The presence of the lattice mismatch buffering  $Al_2O_3$  interlayer, along with any  $(Al_xGa_{1-x})_2O_3$  formed at the  $Ga_2O_3/Al_2O_3$  interface, resulted in enhanced diffraction peak intensities from the (–401) and (020)  $Ga_2O_3$  crystal faces [14,15,31,32], which may connect to increased crystallite size.

**Figure 5.** XRD  $2\theta$ — $\theta$  wide-scan spectra of the  $Ga_2O_3$  thin films.

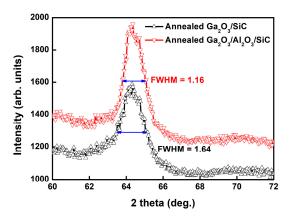

The full width at half maximum (FWHM) and crystallite sizes were extracted from the (020) peaks to compare the effects of the  $Al_2O_3$  interlayer on the crystallinity of the annealed  $Ga_2O_3$  thin films. Figure 6 shows XRD patterns of the (020) peaks and FWHM values of the annealed  $Ga_2O_3$  thin films. The Scherrer equation (Equation (1)) was used to calculate the crystallite sizes:

$FWHM = \frac{K\lambda}{L\cos\theta} \tag{1}$

where K is the shape factor (0.9), L is the crystallite sizes,  $\theta$  is the Bragg diffraction angle [2], and  $\lambda$  is the wavelength of the CuK $\alpha$  X-ray source (0.15406 nm). The crystallite size of the Ga<sub>2</sub>O<sub>3</sub> thin films tends to increase from 5.72 to 8.09 nm with the addition of the Al<sub>2</sub>O<sub>3</sub> interlayer. The crystallite size is inversely proportional to the number of grain boundaries, which are a major factor in carrier mobility degradation [33]. This suggests that the samples with the Al<sub>2</sub>O<sub>3</sub> interlayer may exhibit improved electrical characteristics.

**Figure 6.** XRD patterns of (020) peaks and the extracted FWHM values of annealed  $Ga_2O_3$  thin films, with or without an  $Al_2O_3$  interlayer.

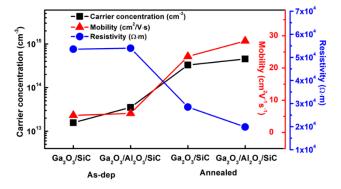

Hall measurements of the  $Ga_2O_3$  thin films were performed (at room temperature) to examine the influence of annealing and the presence or absence of an  $Al_2O_3$  interlayer on the electrical properties of the sample devices. Figure 7 shows the carrier concentration, mobility, and resistivity of the different  $Ga_2O_3$  thin films, according to whether they had been annealed after deposition or not, and relating to the device structure, with or without an  $Al_2O_3$  interlayer. After annealing of the thin films, the Hall mobility increased, indicating the effect of  $Ga_2O_3$  crystallization on the Hall mobility. The annealed  $Ga_2O_3/Al_2O_3/SiC$  devices exhibited the highest charge carrier concentration and mobility (4.52  $\times$  10<sup>14</sup> cm<sup>-3</sup> and 25.65 cm<sup>2</sup> V<sup>-1</sup> s<sup>-1</sup>, respectively) and lowest resistivity (19.86  $\times$  10<sup>3</sup>  $\Omega$ m). As previously hypothesized, the improved Hall mobility can be attributed to the larger crystallite size due to the reduction in grain boundary scattering [34–36].

**Figure 7.** Hall mobility, carrier concentration, and resistivity of the Ga<sub>2</sub>O<sub>3</sub> thin films.

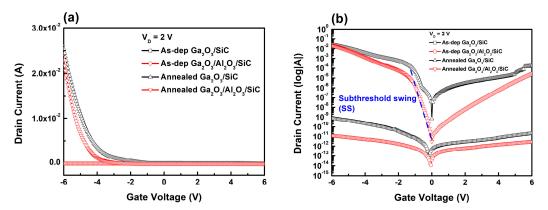

The back-gate transistors, as shown in Figure 1a,b, have a source–drain spacing of 100  $\mu$ m with highly doped SiC/Ni back gates. Figure 8a,b show the electrical transfer characteristics of the as-deposited and annealed Ga<sub>2</sub>O<sub>3</sub>/SiC and Ga<sub>2</sub>O<sub>3</sub>/Al<sub>2</sub>O<sub>3</sub>/SiC backgate transistors. The subthreshold swing (SS), defined by the  $V_{GS}$  variations required for the ten-fold increase in  $I_{DS}$ , is given by the maximum slope in the transfer curve in a logarithmic scale [37] and can be extracted by (Equation (2)):

$$SS = \frac{dV_{GS}}{d(\log I_{DS})} \tag{2}$$

**Figure 8.** Transfer characteristics of the as-deposited and annealed Ga<sub>2</sub>O<sub>3</sub>/SiC and Ga<sub>2</sub>O<sub>3</sub>/Al<sub>2</sub>O<sub>3</sub>/SiC back-gate transistors in (a) linear and (b) logarithmic scales.

The on and off currents, on/off ratio ( $V_{GS} = \pm 6$  V), and SS of the devices are shown in Table 1. The annealed  $Ga_2O_3/Al_2O_3/SiC$  transistors have the highest on/off ratio of  $8.27 \times 10^2$  and the lowest SS of 154 mV·dec<sup>-1</sup>.

Table 1. Electrical characteristics of fabricated back-gate transistors.

|                                  | As-Deposited                        |                                                                     | Annealed at 900 °C                  |                                                                     |

|----------------------------------|-------------------------------------|---------------------------------------------------------------------|-------------------------------------|---------------------------------------------------------------------|

| -                                | Ga <sub>2</sub> O <sub>3</sub> /SiC | Ga <sub>2</sub> O <sub>3</sub> /Al <sub>2</sub> O <sub>3</sub> /SiC | Ga <sub>2</sub> O <sub>3</sub> /SiC | Ga <sub>2</sub> O <sub>3</sub> /Al <sub>2</sub> O <sub>3</sub> /SiC |

| On current [A] (+6 V)            | $8.03 \times 10^{-10}$              | $1.19 \times 10^{-11}$                                              | $2.53 \times 10^{-2}$               | $2.27 \times 10^{-2}$                                               |

| Off current [A] $(-6 \text{ V})$ | $-2.14 \times 10^{-11}$             | $-2.78 \times 10^{-12}$                                             | $-1.73 	imes 10^{-4}$               | $-2.75 \times 10^{-5}$                                              |

| On/off ratio                     | $3.74 \times 10$                    | 4.29                                                                | $1.46 \times 10^{2}$                | $8.27 \times 10^{2}$                                                |

| SS (mV·dec <sup>-1</sup> )       | 233                                 | 234                                                                 | 182                                 | 154                                                                 |

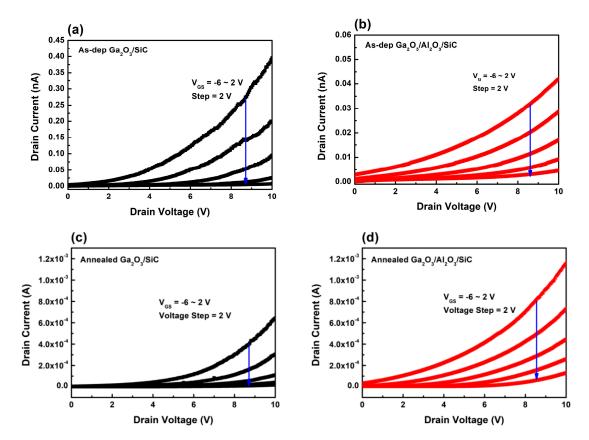

The  $I_{DS}$ - $V_{DS}$  output curves were measured by sweeping the  $V_{DS}$  from 0 to +10 V, whereas  $V_{GS}$  was biased from -6 to +2 V. Figure 9a–d show the electrical output characteristics of the back-gate transistors. The transistors with the as-deposited  $Ga_2O_3$  films exhibited a maximum  $I_{DS}$  below  $10^{-9}$  A, whereas the transistors with annealed  $Ga_2O_3$  films featured currents over  $10^{-4}$  A. Annealed samples with an  $Al_2O_3$  layer exhibited the highest carrier mobility, resulting in the highest on-current level. This result is mainly attributed to the improved crystallinity of the  $Ga_2O_3$  films by annealing [38] and the addition of the  $Al_2O_3$  interlayer [14,15,31,32]. The larger crystallite grains, and thus enhanced crystallinity, apparently mitigate the parasitic resistance [39] and grain boundary scattering of thin films [33,36] of the  $Ga_2O_3$  thin films, resulting in improved device performance.

**Figure 9.** Output characteristics of the as-deposited and annealed ( $\mathbf{a}$ , $\mathbf{c}$ ) Ga<sub>2</sub>O<sub>3</sub>/SiC and ( $\mathbf{b}$ , $\mathbf{d}$ ) Ga<sub>2</sub>O<sub>3</sub>/Al<sub>2</sub>O<sub>3</sub>/SiC back-gate transistors, respectively.

### 5. Conclusions

In this study,  $Ga_2O_3$  and  $Al_2O_3$  thin films were deposited on 4H-SiC substrates using RF sputtering to compare the effects of an  $Al_2O_3$  interlayer on the morphological and electrical properties of the manufactured thin films and resulting devices. Through AES depth profiling, we confirmed that Al and Ga atoms interdiffusion at the  $Ga_2O_3/Al_2O_3$  interface during annealing at 900 °C. XRD results brought to light an improved crystallinity of the  $Ga_2O_3$  thin films after annealing and adding the  $Al_2O_3$  layer. Annealed  $Ga_2O_3$  film on  $Al_2O_3/SiC$  displayed the highest carrier concentration and mobility of  $4.52 \times 10^{14}$  cm<sup>-3</sup> and 25.65 cm<sup>2</sup> V<sup>-1</sup> s<sup>-1</sup>, respectively, as well as the lowest resistivity of  $19.86 \times 10^3$   $\Omega$ ·m. These enhanced electrical properties of the annealed  $Ga_2O_3$  on  $Al_2O_3/SiC$  affected the transfer and output characteristics, resulting in the highest on/off ratio  $(8.27 \times 10^2)$  and lowest SS (154 mV·dec<sup>-1</sup>). Thus, introducing an  $Al_2O_3$  interlayer in RF-sputtered  $Ga_2O_3/SiC$  back-gate transistors improved the electrical characteristics of the devices.

**Author Contributions:** Conceptualization, H.-J.L. and S.-M.K.; Data curation, H.-J.L. and D.H.C.; Formal analysis, H.-J.L. and D.-W.B.; Funding acquisition, S.-M.K.; Investigation, H.-J.L., M.L., and S.-M.K.; Methodology, H.-J.L. and S.-H.C.; Project administration, S.-M.K.; Software, H.-J.L., G.-H.L. and N.Y.J.; Supervision, S.-M.K.; Validation, H.-J.L., T.E., and S.-M.K.; Writing—original draft, H.-J.L.; Writing—review and editing, M.A.S. and S.-M.K. All authors have read and agreed to the published version of the manuscript.

**Funding:** This work was supported by the Kwangwoon University in 2023, the Korea Institute of Energy Technology Evaluation and Planning (KETEP) (20214000000700) and the Korea Evaluation Institute of Industrial Technology (KEIT) (20016102) grant funded by the MOTIE of Korea.

**Data Availability Statement:** Data supporting the published results can be obtained from the authors upon reasonable request.

**Acknowledgments:** Hee-Jae Lee and Sang-Mo Koo thank Tobias Erlbacher, Minwho Lim, and the Fraunhofer Institute for Integrated Systems and Devices Technology (IISB) for allowing the research-visit collaboration of the graduate students.

Conflicts of Interest: The authors declare no conflict of interest.

### References

- 1. Oh, S.; Yang, G.; Kim, J. Electrical characteristics of vertical Ni/β-Ga<sub>2</sub>O<sub>3</sub> Schottky barrier diodes at high temperatures. *ECS J. Solid State Sci. Technol.* **2016**, *6*, Q3022. [CrossRef]

- Byun, D.W.; Lee, Y.J.; Oh, J.M.; Schweitz, M.A.; Koo, S.M. Morphological and electrical properties of β-Ga<sub>2</sub>O<sub>3</sub>/4H-SiC heterojunction diodes. *Electron. Mater. Lett.* 2021, 17, 479–484. [CrossRef]

- 3. Pérez-Tomás, A.; Jennings, M.R.; Davis, M.; Shah, V.; Grasby, T.; Covington, J.A.; Mawby, P.A. High doped MBE Si p–n and n–n heterojunction diodes on 4H-SiC. *Microelectron. J.* **2007**, *38*, 1233–1237. [CrossRef]

- 4. Oshima, T.; Kaminaga, K.; Mukai, A.; Sasaki, K.; Masui, T.; Kuramata, A.; Yamakoshi, S.; Fujita, S.; Ohtomo, A. Formation of semi-insulating layers on semiconducting β-Ga<sub>2</sub>O<sub>3</sub> single crystals by thermal oxidation. *Jpn. J. Appl. Phys.* **2013**, *52*, 051101. [CrossRef]

- Lee, H.J.; Shin, M.C.; Moon, S.Y.; Byun, D.W.; Kim, M.Y.; Lee, H.J.; Lee, G.H.; Jung, S.W.; Schweitz, M.A.; Park, J.; et al. Bandgap modulation and electrical characteristics of (Al<sub>x</sub>Ga<sub>1-x</sub>)<sub>2</sub>O<sub>3</sub>/4H-SiC thin film heterostructures. *Thin Solid Film.* 2022, 754, 139276. [CrossRef]

- 6. Wang, Y.; Xu, W.; You, T.; Mu, F.; Hu, H.; Liu, Y.; Huang, H.; Suga, T.; Han, G.; Ou, X.; et al. β-Ga<sub>2</sub>O<sub>3</sub> MOSFETs on the Si substrate fabricated by the ion-cutting process. *Sci. China Phys. Mech. Astron.* **2020**, *63*, 277311. [CrossRef]

- Zhang, J.; Shi, J.; Qi, D.C.; Chen, L.; Zhang, K.H. Recent progress on the electronic structure, defect, and doping properties of Ga<sub>2</sub>O<sub>3</sub>. APL Mater. 2020, 8, 020906. [CrossRef]

- Lee, Y.J.; Schweitz, M.A.; Oh, J.M.; Koo, S.M. Influence of annealing atmosphere on the characteristics of Ga<sub>2</sub>O<sub>3</sub>/4H-SiC n-n heterojunction diodes. *Materials* 2020, 13, 434. [CrossRef]

- 9. Bhuiyan, A.F.M.; Feng, Z.; Johnson, J.M.; Huang, H.L.; Sarker, J.; Zhu, M.; Karim, M.R.; Mazumder, B.; Hwang, J.; Zhao, H. Phase transformation in MOCVD growth of (Al<sub>x</sub>Ga<sub>1-x</sub>)<sub>2</sub>O<sub>3</sub> thin films. *APL Mater.* **2020**, *8*, 031104. [CrossRef]

- 10. Vaca, D.; Yates, L.; Nepal, N.; Katzer, D.S.; Downey, B.P.; Wheeler, V.; Meyer, D.J.; Graham, S.; Kumar, S. Thermal conductivity of β-Ga<sub>2</sub>O<sub>3</sub> thin films grown by molecular beam epitaxy. In Proceedings of the 2020 19th IEEE Intersociety Conference on Thermal and Thermomechanical Phenomena in Electronic Systems (ITherm), Orlando, FL, USA, 21–23 July 2020; pp. 1011–1016.

- 11. Santia, M.D.; Tandon, N.; Albrecht, J.D. Lattice thermal conductivity in β-Ga<sub>2</sub>O<sub>3</sub> from first principles. *Appl. Phys. Lett.* **2015**, 107, 041907. [CrossRef]

- 12. Cheng, Z.; Yates, L.; Shi, J.; Tadjer, M.J.; Hobart, K.D.; Graham, S. Thermal conductance across β-Ga<sub>2</sub>O<sub>3</sub>-diamond van der Waals heterogeneous interfaces. *APL Mater.* **2019**, *7*, 031118. [CrossRef]

- 13. Bar-Cohen, A.; Albrecht, J.D.; Maurer, J.J. Near-junction thermal management for wide bandgap devices. In Proceedings of the 2011 IEEE Compound Semiconductor Integrated Circuit Symposium (CSICS), Waikoloa, HI, USA, 16–19 October 2011; pp. 1–5.

- 14. Wang, T.; Wu, H.; Chen, C.; Liu, C. Growth, optical, and electrical properties of nonpolar m-plane ZnO on p-Si substrates with Al<sub>2</sub>O<sub>3</sub> buffer layers. *Appl. Phys. Lett.* **2012**, *100*, 011901. [CrossRef]

- 15. Qian, H.; Zhang, X.; Ma, Y.; Zhang, L.; Chen, T.; Wei, X.; Tang, W.; Zhou, X.; Feng, B.; Fan, Y.; et al. Quasi-vertical ε-Ga<sub>2</sub>O<sub>3</sub> solar-blind photodetectors grown on p-Si substrates with Al<sub>2</sub>O<sub>3</sub> buffer layer by metalorganic chemical vapor deposition. *Vacuum* **2022**, 200, 111019. [CrossRef]

- 16. Jian, Z.; Sayed, I.; Liu, W.; Mohanty, S.; Ahmadi, E. Characterization of MOCVD-grown AlSiO gate dielectric on β-Ga<sub>2</sub>O<sub>3</sub> (001). *Appl. Phys. Lett.* **2021**, *118*, 172102. [CrossRef]

- 17. Wang, T.; Li, W.; Ni, C.; Janotti, A. Band gap and band offset of Ga<sub>2</sub>O<sub>3</sub> and (Al<sub>x</sub>Ga<sub>1-x</sub>)<sub>2</sub>O<sub>3</sub> alloys. *Phys. Rev. Appl.* **2018**, 10, 011003. [CrossRef]

- 18. Feng, Z.; Feng, Q.; Zhang, J.; Zhang, C.; Zhou, H.; Li, X.; Huang, L.; Xu, L.; Hu, Y.; Zhao, S.; et al. Band alignments of  $SiO_2$  and  $HfO_2$  dielectrics with  $(Al_xGa_{1-x})_2O_3$  film  $(0 \le x \le 0.53)$  grown on  $Ga_2O_3$  buffer layer on sapphire. *J. Alloys Compd.* **2018**, 745, 292–298. [CrossRef]

- 19. Bhuiyan, A.F.M.; Feng, Z.; Johnson, J.M.; Huang, H.L.; Hwang, J.; Zhao, H. Band offsets of (100)  $\beta$ -(Al<sub>x</sub>Ga<sub>1-x</sub>)<sub>2</sub>O<sub>3</sub>/ $\beta$ -Ga<sub>2</sub>O<sub>3</sub> heterointerfaces grown via MOCVD. *Appl. Phys. Lett.* **2020**, *117*, 252105. [CrossRef]

- 20. Singh, P.; Jha, R.K.; Singh, R.K.; Singh, B.R. Preparation and characterization of Al<sub>2</sub>O<sub>3</sub> film deposited by RF sputtering and plasma enhanced atomic layer deposition. *J. Vac. Sci. Technol. B Nanotechnol. Microelectron. Mater. Process. Meas. Phenom.* **2018**, *36*, 04G101. [CrossRef]

- 21. Herrera, F.Á.; Hirano, Y.; Miura-Mattausch, M.; Iizuka, T.; Kikuchihara, H.; Mattausch, H.J.; Ito, A. Advanced short-channel-effect modeling with applicability to device optimization—Potentials and scaling. *IEEE Trans. Electron Devices* **2019**, *66*, 3726–3733. [CrossRef]

- 22. Madadi, D.; Orouji, A.A. β-Ga<sub>2</sub>O<sub>3</sub> double gate junctionless FET with an efficient volume depletion region. *Phys. Lett. A* **2021**, 412, 127575. [CrossRef]

23. Li, Z.; Wu, Y.; Feng, B.; Li, Y.; Liu, T.; Feng, J.; Chen, X.; Huang, R.; Xu, L.; Li, Z.; et al. Bandgap Tailoring of Monoclinic Single-Phase  $\beta$ -(Al<sub>x</sub>Ga<sub>1-x</sub>)<sub>2</sub>O<sub>3</sub> ( $0 \le x \le 0.65$ ) Thin Film by Annealing  $\beta$ -Ga<sub>2</sub>O<sub>3</sub>/Al<sub>2</sub>O<sub>3</sub> Heterojunction at High Temperatures. *Phys. Status Solidi A* **2021**, 218, 2000785. [CrossRef]

- Liao, C.H.; Li, K.H.; Torres-Castanedo, C.G.; Zhang, G.; Li, X. Wide range tunable bandgap and composition β-phase (AlGa)<sub>2</sub>O<sub>3</sub> thin film by thermal annealing. Appl. Phys. Lett. 2021, 118, 032103. [CrossRef]

- 25. Nakagomi, S.; Sakai, T.; Kikuchi, K.; Kokubun, Y. β-Ga<sub>2</sub>O<sub>3</sub>/p-type 4H-SiC heterojunction diodes and applications to deep-UV photodiodes. *Phys. Status Solidi A* **2019**, 216, 1700796. [CrossRef]

- Nepal, N.; Katzer, D.S.; Downey, B.P.; Wheeler, V.D.; Nyakiti, L.O.; Storm, D.F.; Hardy, M.T.; Freitas, J.A.; Jin, E.N.; Vaca, D.; et al. Heteroepitaxial growth of β-Ga<sub>2</sub>O<sub>3</sub> films on SiC via molecular beam epitaxy. *J. Vac. Sci. Technol. A Vac. Surf. Film.* 2020, 38, 063406. [CrossRef]

- 27. Singh, A.K.; Gupta, M.; Sathe, V.; Katharria, Y.S. Effect of annealing temperature on β-Ga<sub>2</sub>O<sub>3</sub> thin films deposited by RF sputtering method. *Superlattices Microstruct.* **2021**, 156, 106976. [CrossRef]

- 28. Yu, J.; Nie, Z.; Dong, L.; Yuan, L.; Li, D.; Huang, Y.; Zhang, L.; Zhang, Y.; Jia, R. Influence of annealing temperature on structure and photoelectrical performance of β-Ga<sub>2</sub>O<sub>3</sub>/4H-SiC heterojunction photodetectors. *J. Alloys Compd.* **2019**, 798, 458–466. [CrossRef]

- 29. Anhar Uddin Bhuiyan, A.F.M.; Feng, Z.; Johnson, J.M.; Chen, Z.; Huang, H.L.; Hwang, J.; Zhao, H. MOCVD epitaxy of β-(Al<sub>x</sub>Ga<sub>1-x</sub>)<sub>2</sub>O<sub>3</sub> thin films on (010) Ga<sub>2</sub>O<sub>3</sub> substrates and N-type doping. *Appl. Phys. Lett.* **2019**, *115*, 120602. [CrossRef]

- 30. Zhang, L.; Jiang, H.C.; Liu, C.; Dong, J.W.; Chow, P. Annealing of Al<sub>2</sub>O<sub>3</sub> thin films prepared by atomic layer deposition. *J. Phys. D Appl. Phys.* **2007**, *40*, 3707. [CrossRef]

- 31. Kim, B.; Yang, D.; Sohn, W.; Lee, S.; Jang, T.; Yoon, E.; Park, Y.; Jang, H.W. Strain relaxation and dislocation annihilation in compositionally graded  $\alpha$ -(Al<sub>x</sub>Ga<sub>1-x</sub>)<sub>2</sub>O<sub>3</sub> layer for high voltage  $\alpha$ -Ga<sub>2</sub>O<sub>3</sub> power devices. *Acta Mater.* **2021**, 221, 117423. [CrossRef]

- 32. Cheng, Y.; Zhang, C.; Xu, Y.; Li, Z.; Chen, D.; Zhu, W.; Feng, Q.; Xu, S.; Zhang, J.; Hao, Y. Heteroepitaxial growth of  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> thin films on c-plane sapphire substrates with  $\beta$ -(Al<sub>x</sub>Ga<sub>1-x</sub>)<sub>2</sub>O<sub>3</sub> intermediate buffer layer by mist-CVD method. *Mater. Today Commun.* **2021**, 29, 102766. [CrossRef]

- 33. Bhuvana, K.P.; Elanchezhiyan, J.; Gopalakrishnan, N.; Balasubramanian, T. Influence of grain size on the properties of AIN doped ZnO thin film. *Mater. Sci. Semicond. Process.* **2011**, *14*, 84–88. [CrossRef]

- 34. Assunção, V.; Fortunato, E.; Marques, A.; Gonçalves, A.; Ferreira, I.; Águas, H.; Martins, R. New challenges on gallium-doped zinc oxide films prepared by rf magnetron sputtering. *Thin Solid Film*. **2003**, 442, 102–106. [CrossRef]

- 35. Wang, D.; Ma, X.; Xiao, H.; Le, Y.; Ma, J. Ta-doped epitaxial β-Ga<sub>2</sub>O<sub>3</sub> films deposited on SrTiO<sub>3</sub> (100) substrates by MOCVD. *Mater. Sci. Semicond. Process.* **2021**, 128, 105749. [CrossRef]

- 36. Wang, S.; Hui, S.; Peng, K.; Bailey, T.P.; Zhou, X.; Tang, X.; Uher, C. Grain boundary scattering effects on mobilities in p-type polycrystalline SnSe. *J. Mater. Chem. C* **2017**, *5*, 10191–10200. [CrossRef]

- 37. Oh, B.Y.; Jeong, M.C.; Ham, M.H.; Myoung, J.M. Effects of the channel thickness on the structural and electrical characteristics of room-temperature fabricated ZnO thin-film transistors. *Semicond. Sci. Technol.* **2007**, 22, 608. [CrossRef]

- 38. Makeswaran, N.; Battu, A.K.; Deemer, E.; Ramana, C.V. Crystal growth and structure–property optimization of thermally annealed nanocrystalline Ga<sub>2</sub>O<sub>3</sub> films. *Cryst. Growth Des.* **2020**, *20*, 2893–2903. [CrossRef]

- 39. Patel, S.L.; Chander, S.; Purohit, A.; Kannan, M.D.; Dhaka, M.S. Influence of NH<sub>4</sub>Cl treatment on physical properties of CdTe thin films for absorber layer applications. *J. Phys. Chem. Solids* **2018**, *123*, 216–222. [CrossRef]

**Disclaimer/Publisher's Note:** The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content.