A Compact 5 GHz Power Amplifier Using a Spiral Transformer for Enhanced Power Supply Rejection in 180-nm CMOS Technology

Abstract

:1. Introduction

2. Circuit Design

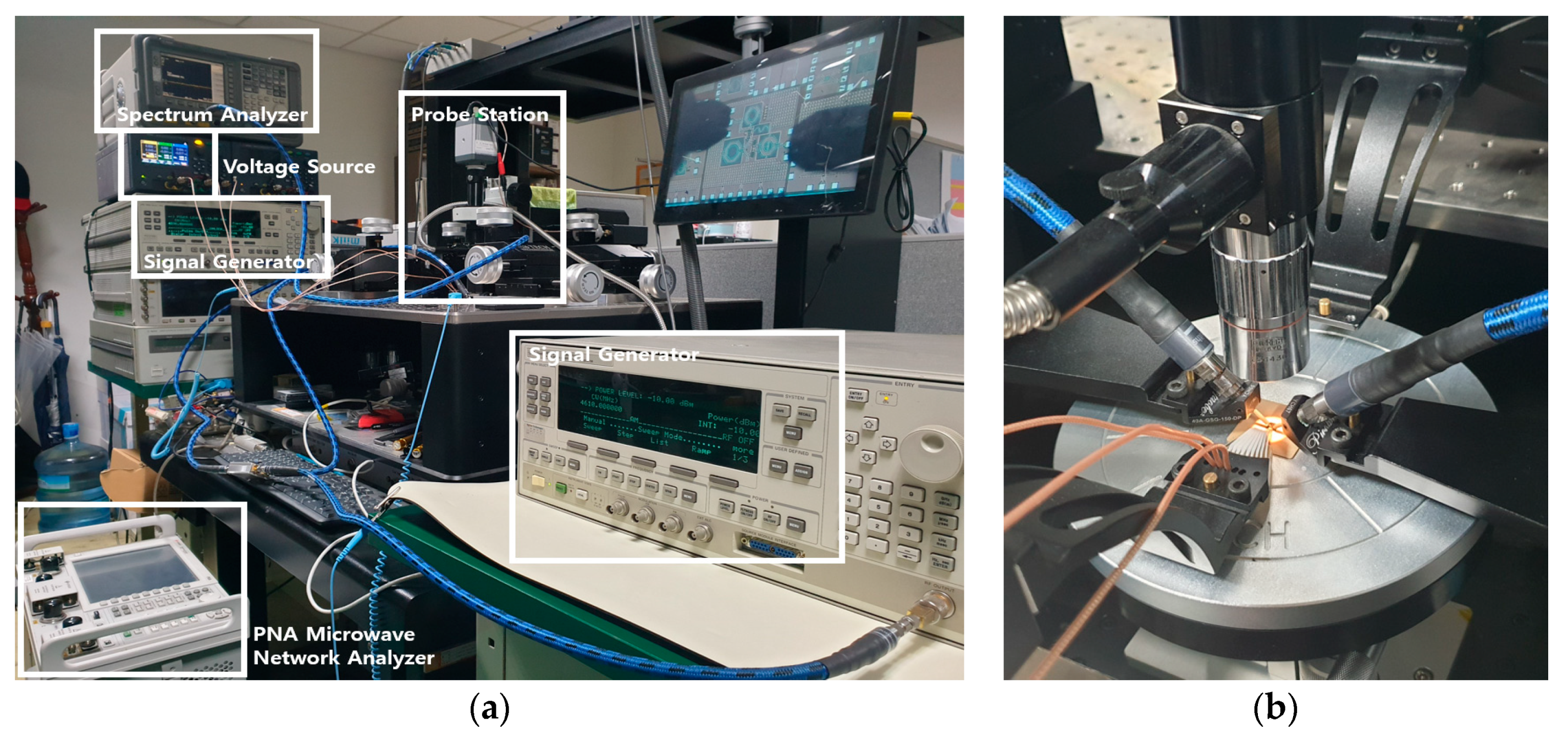

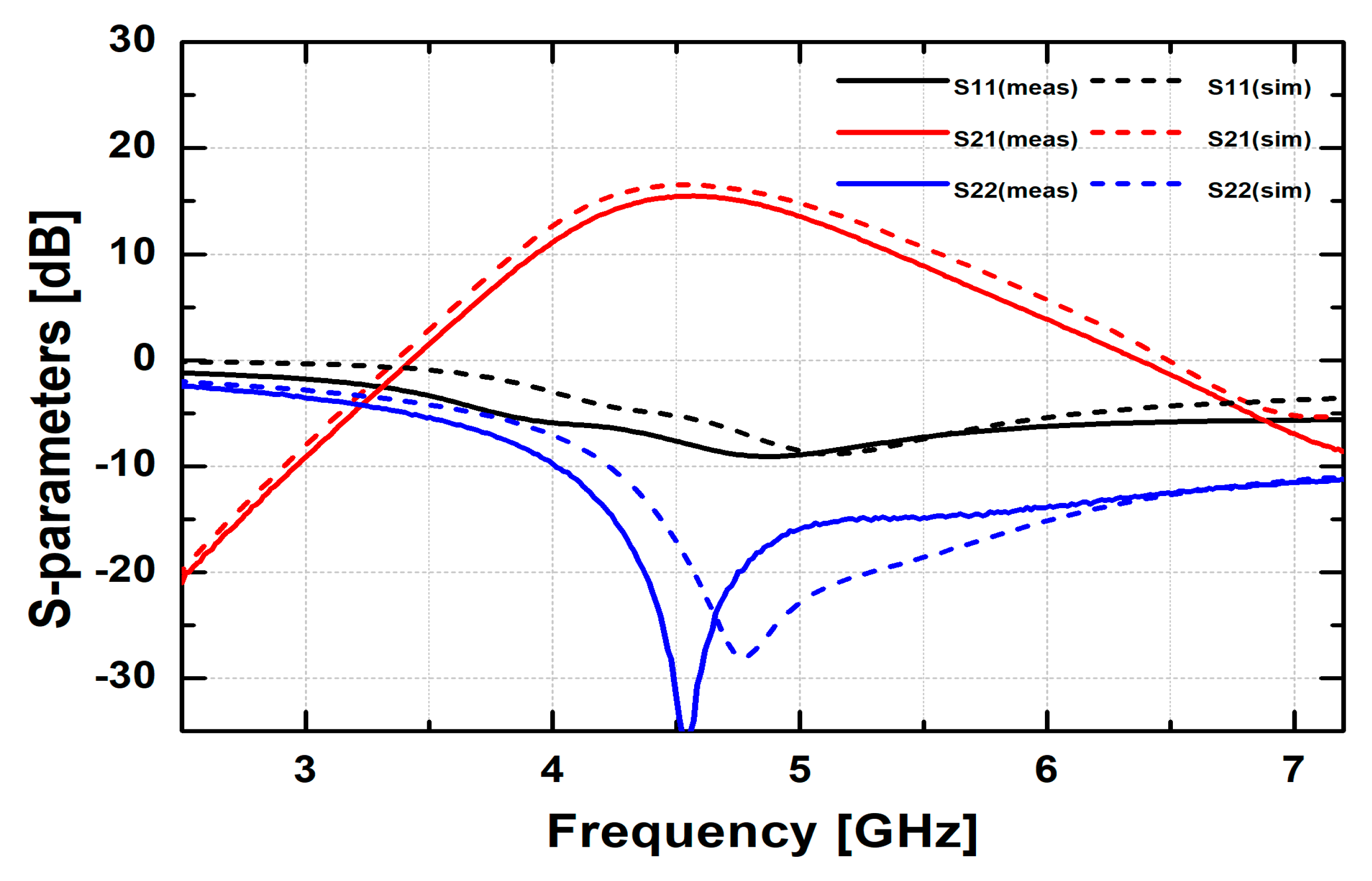

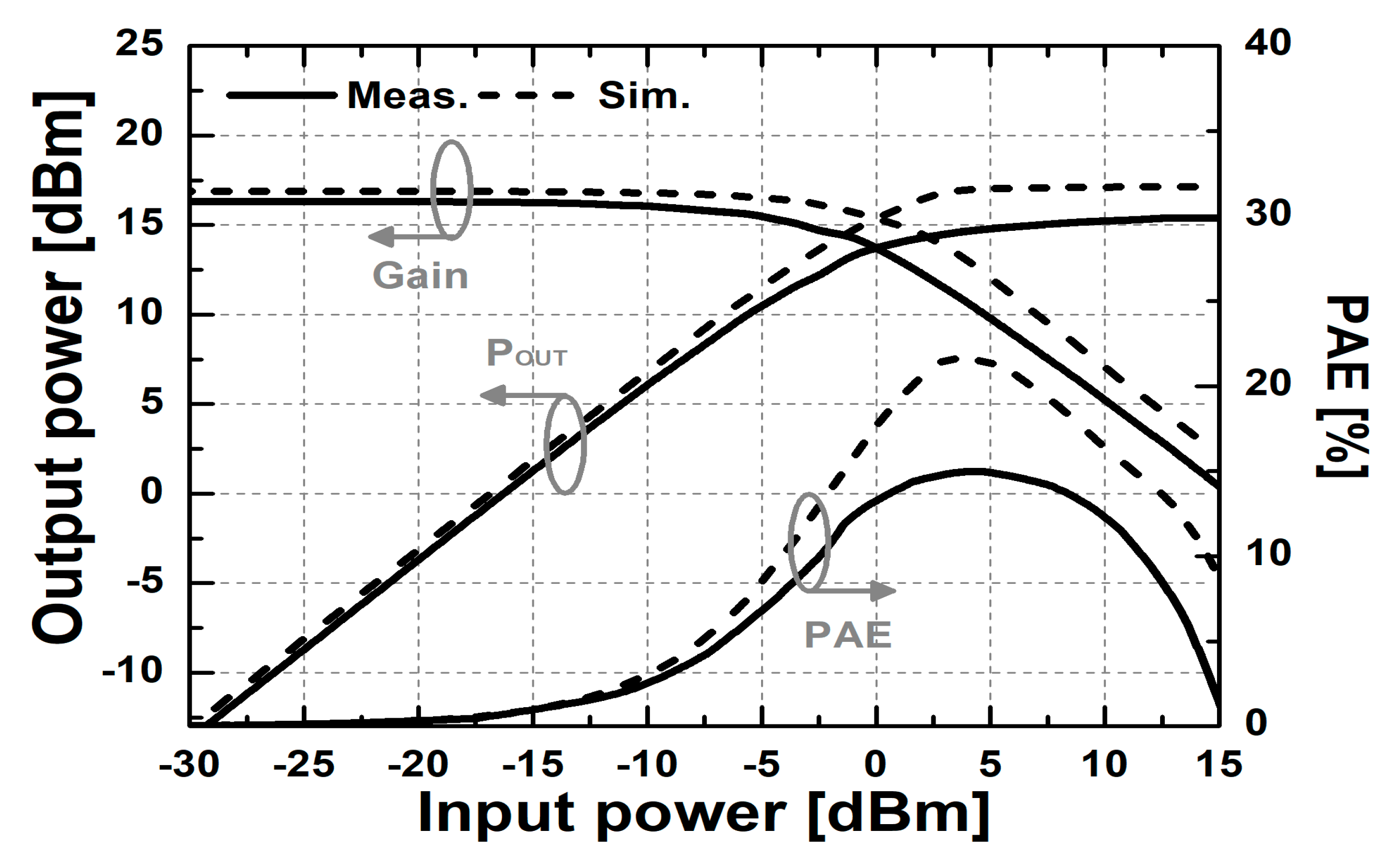

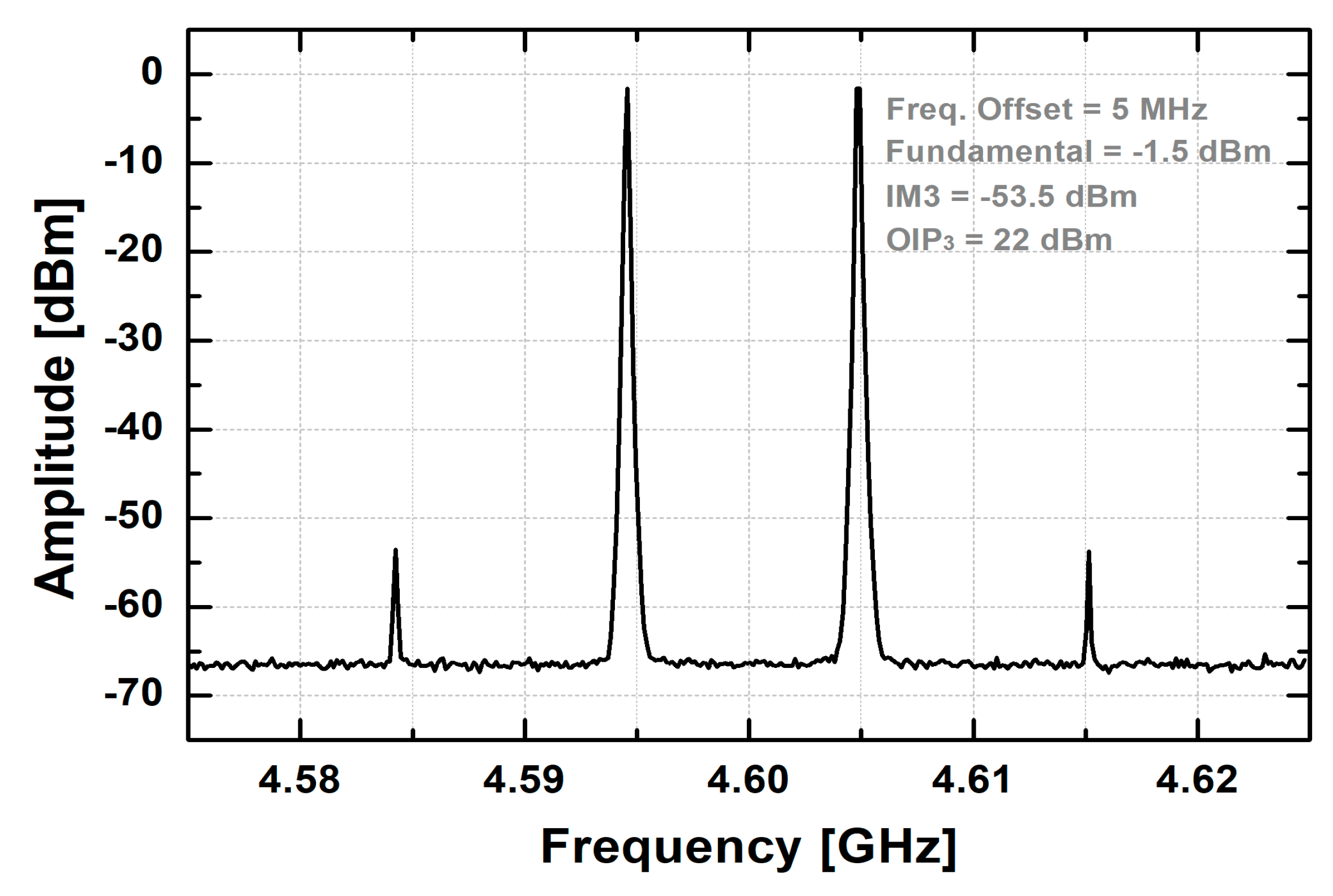

3. Measurement Results

4. Conclusions

Author Contributions

Funding

Acknowledgments

Conflicts of Interest

References

- Reynaert, P.; François, B.; Kaymaksüt, E. CMOS RF PA Design: Using Complexity to Solve the Linearity and Efficiency Trade-off. In Proceedings of the 2009 IEEE International Symposium on Radio-Frequency Integration Technology (RFIT 2009), Singapore, 9–11 December 2009; pp. 207–212. [Google Scholar]

- Srirattana, N.; Raghavan, A.; Heo, D.; Allen, P.E.; Laskar, J. Analysis and Design of a High-efficiency Multistage Doherty Power Amplifier for Wireless Communications. IEEE Trans. Microw. Theory Tech. 2005, 53, 852–860. [Google Scholar] [CrossRef]

- Winoto, R.; He, M.; Lu, Y.; Signoff, D.; Chan, E.; Lin, C.-H.; Loeb, W.; Park, J.; Lin, L. A WLAN and Bluetooth Combo Transceiver with Integrated WLAN Power Amplifier, Transmit-receive Switch and WLAN/Bluetooth Shared Low Noise Amplifier. In Proceedings of the 2012 IEEE Radio Frequency Integrated Circuits Symposium, Montreal, QC, Canada, 17–19 June 2012; pp. 395–398. [Google Scholar]

- Singh, A.; Kaur, H. Non Linearity Analysis of High Power Amplifier in OFDM System. Int. J. Comput. Appl. 2012, 37, 37–41. [Google Scholar] [CrossRef]

- Su, D.; Zagari, M.; Yue, P.; Rabii, S.; Weber, D.; Kaczynski, B.; Mehta, B.; Singh, K.; Mendis, S.; Wooley, B. A 5 GHz CMOS Transceiver for IEEE 802.11a Wireless LAN. In Proceedings of the 2002 IEEE International Solid-State Circuits Conference. Digest of Technical Papers, San Francisco, CA, USA, 7 February 2002; pp. 92–449. [Google Scholar]

- Stauth, J.T.; Sanders, S.R. Power Supply Rejection for RF Amplifiers: Theory and Measurements. IEEE Trans. Microw. Theory Tech. 2007, 55, 2043–2052. [Google Scholar] [CrossRef] [Green Version]

- Aoki, I.; Kee, S.D.; Rutledge, D.B.; Hajimiri, A. Distributed active transformer-a new power-combining and impedance-transformation technique. IEEE Trans. Microw. Theory Tech. 2002, 50, 316–331. [Google Scholar] [CrossRef] [Green Version]

- Wei, P.; Tsai, M.; Hsu, S.; Shen, C.; Wu, T. An Electromagnetic Bandgap Structure Integrated With RF LNA Using Integrated Fan-Out Wafer-Level Package for Gigahertz Noise Suppression. IEEE Trans. Microw. Theory Tech. 2018, 66, 5482–5490. [Google Scholar] [CrossRef]

- Razavi, B. RF Microelectronics, 2nd ed.; Prentice-Hall: Upper Saddle River, NJ, USA, 2012. [Google Scholar]

- Loikkanen, M.; Kostamovaara, J. High PSRR Class AB Power Amplifier. In Proceedings of the 2006 NORCHIP, Linkoping, Sweden, 20–21 November 2006; pp. 71–74. [Google Scholar]

- Pedro, J.C.; Nunes, L.C.; Cabral, P.M. A Simple Method to Estimate the Output Power and Efficiency Load-Pull Contours of Class-B Power Amplifiers. IEEE Trans. Microw. Theory Tech. 2015, 63, 1239–1249. [Google Scholar] [CrossRef]

- Pengelly, R.; Saffian, M. Load Pull Simulation Speeds Design of Wideband High-Efficiency PAs [Application Notes]. IEEE Microw. Mag. 2016, 17, 42–53. [Google Scholar] [CrossRef]

- El-Nozahi, M.; Amer, A.; Torres, J.; Entesari, K.; Sanchez-Sinencio, E. High PSR Low Drop-Out Regulator With Feed-Forward Ripple Cancellation Technique. IEEE J. Solid-State Circuits 2010, 45, 565–577. [Google Scholar] [CrossRef]

- Le, V.-H.; Han, S.-K.; Lee, S.-G. A Low Power Driver Amplifier for Unlicensed 2.4 GHz Band. IEICE Trans. Electron. 2011, 94, 120–123. [Google Scholar] [CrossRef]

- Lin, K.-C.; Chiou, H.-K.; Wu, P.-C.; Ko, C.-L.; Tsai, H.-H.; Juang, Z.-L. A 28-dBm Pout 5-GHz CMOS Power Amplifier using Integrated Passive Device Power Combining Transformer. In Proceedings of the Asia-Pacific Microwave Conference Proceedings (APMC), Seoul, Korea, 5–8 November 2013; pp. 766–768. [Google Scholar]

- Zhang, W.; Khoo, E.-Z.; Tear, T. A Low Voltage Fully-integrated 0.18 um CMOS Power Amplifier for 5 GHz WLAN. In Proceedings of the 28th European Solid-State Circuits Conference, Florence, Italy, 22–26 September 2002; pp. 215–218. [Google Scholar]

- Eo, Y.-S.; Lee, K.D. A Fully Integrated 24-dBm CMOS Power Amplifier for 802.11a WLAN Applications. IEEE Microw. Wirel. Compon. Lett. 2004, 14, 504–506. [Google Scholar] [CrossRef]

- Kurniawan, T.A.; Yoshimasu, T. A 2.5-GHz 1-V High Efficiency CMOS Power Amplifier IC with a Dual-Switching Transistor and Third Harmonic Tuning Technique. Electronics 2019, 8, 69. [Google Scholar] [CrossRef]

| PA | This Work | [3] | [6] | [10] | [14] | [15] | [16] | [17] | [18] |

|---|---|---|---|---|---|---|---|---|---|

| Technology [nm] | 180 | 55 | 180 | 350 | 180 | 180 | 180 | 180 | 180 |

| Frequency [GHz] | 4.1–5.1 | 2.4 | 2.4 | 10.6 MHz | 2.4 | 5.8 | 5 | 5 | 2.5 |

| Supply Voltage [V] | 1.8 | 3.3 | 1.8 | 3 | 1.8 | 1.8 | 1.8 | 1.8 | 1 |

| PSAT [dBm] | 15.4 | 29 | 15 | - | 5 | 26.7 | 17.4 | 24.1 | 10.1 |

| PAE(1) [%] | 15 | - | - | - | 20 | 19 | 27.1 | 13 | 34.5 |

| OP1dB [dBm] | 13 | 27.5 | - | - | 4 | 24.2 | 15.4 | 21.8 | 8 |

| OIP3(2) [dBm] | 22 | -15 | - | - | 15 | - | 25 | - | - |

| PSRR [dB at 10 MHz] | 82.5 | - | 25 | 30 | - | - | - | - | - |

| Area [mm2] | 0.65 | 6.6 | 1.96 | - | 0.8 | 1.92 | .84 | 1.8 | - |

| FoM* [(dBm∙GHz2)/mm2] | 45 | - | - | - | 21.6 | - | 51.5 | - | - |

© 2019 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).

Share and Cite

Choe, Y.-J.; Nam, H.; Park, J.-D. A Compact 5 GHz Power Amplifier Using a Spiral Transformer for Enhanced Power Supply Rejection in 180-nm CMOS Technology. Electronics 2019, 8, 1043. https://doi.org/10.3390/electronics8091043

Choe Y-J, Nam H, Park J-D. A Compact 5 GHz Power Amplifier Using a Spiral Transformer for Enhanced Power Supply Rejection in 180-nm CMOS Technology. Electronics. 2019; 8(9):1043. https://doi.org/10.3390/electronics8091043

Chicago/Turabian StyleChoe, Young-Joe, Hyohyun Nam, and Jung-Dong Park. 2019. "A Compact 5 GHz Power Amplifier Using a Spiral Transformer for Enhanced Power Supply Rejection in 180-nm CMOS Technology" Electronics 8, no. 9: 1043. https://doi.org/10.3390/electronics8091043