X-Band GaN Power Amplifier MMIC with a Third Harmonic-Tuned Circuit

Abstract

:1. Introduction

2. Device Technology

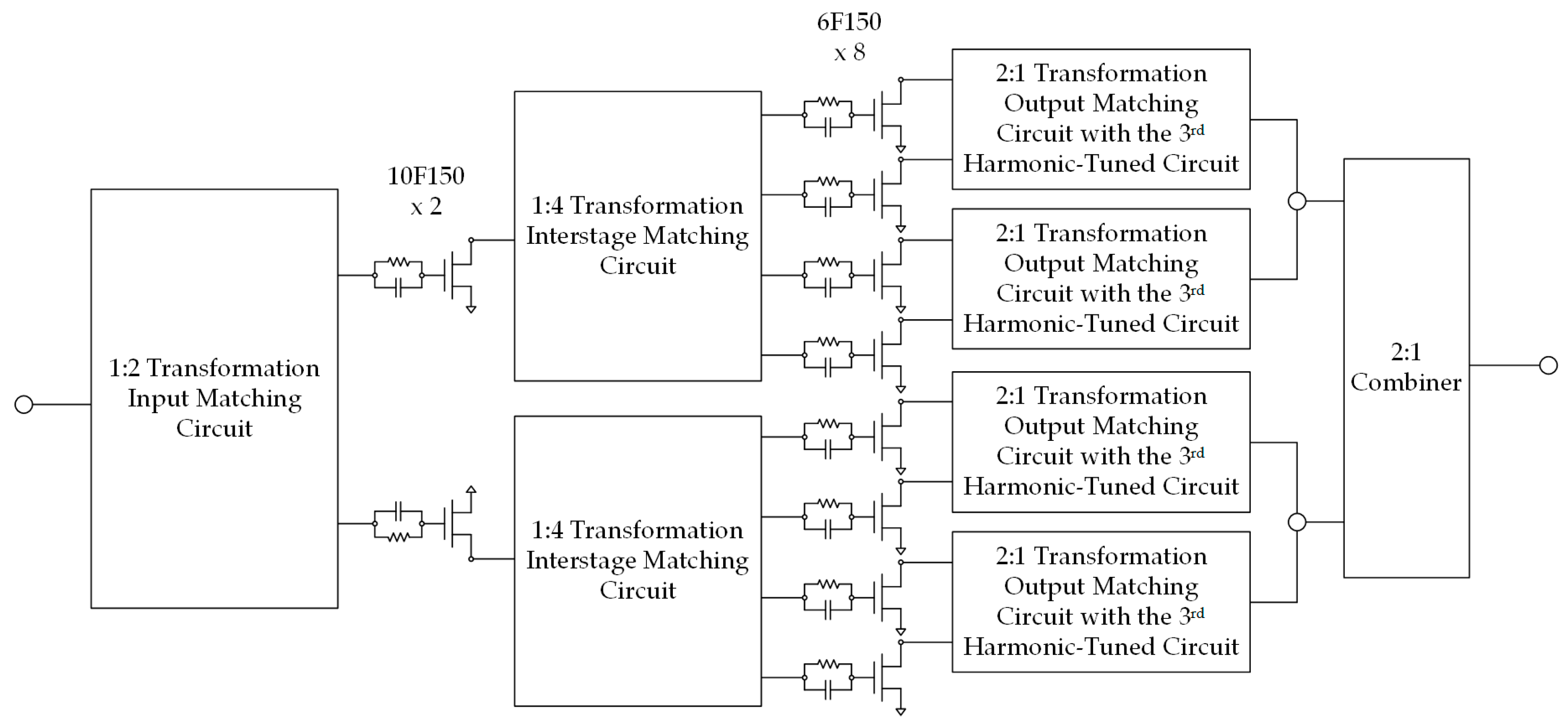

3. Circuit Design

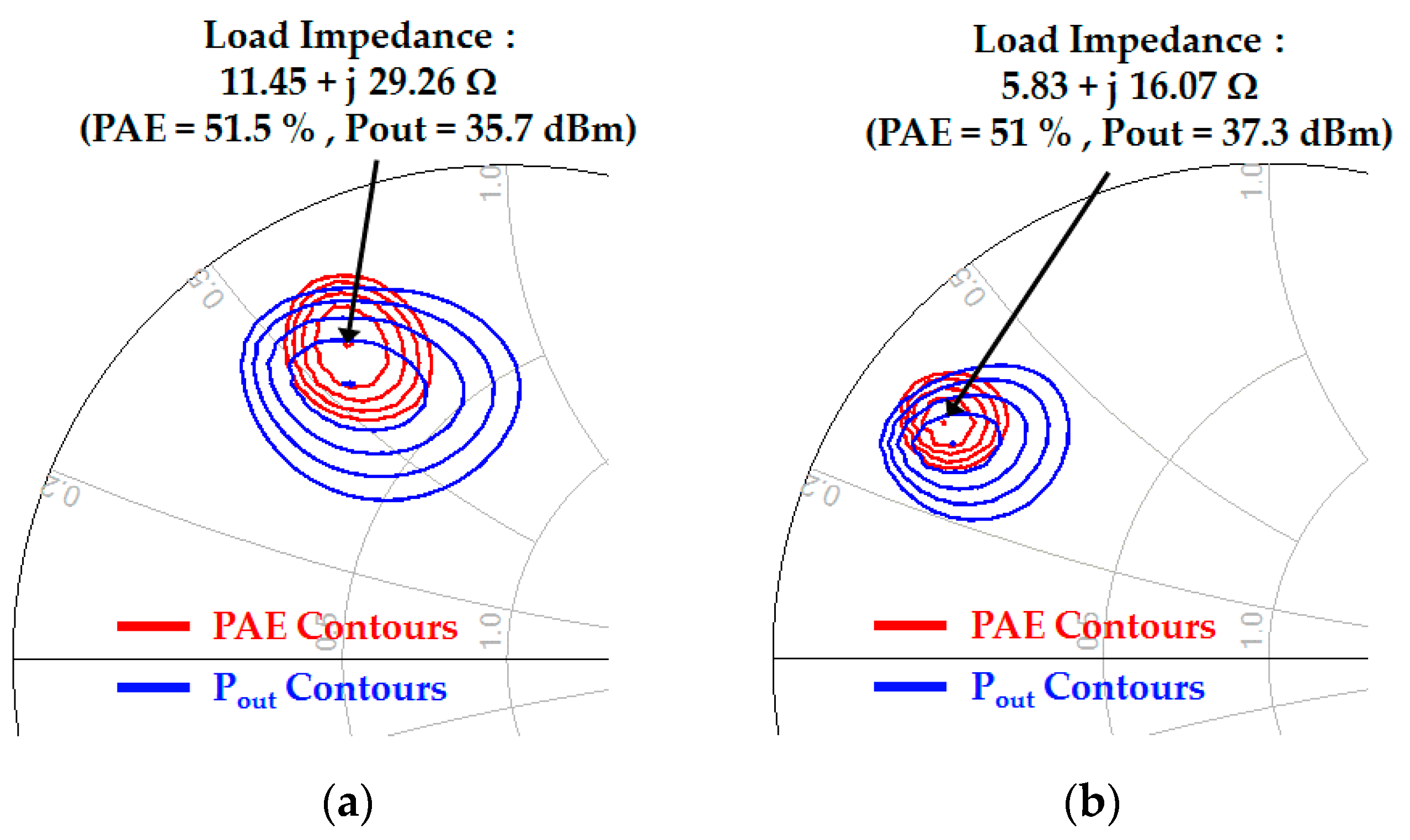

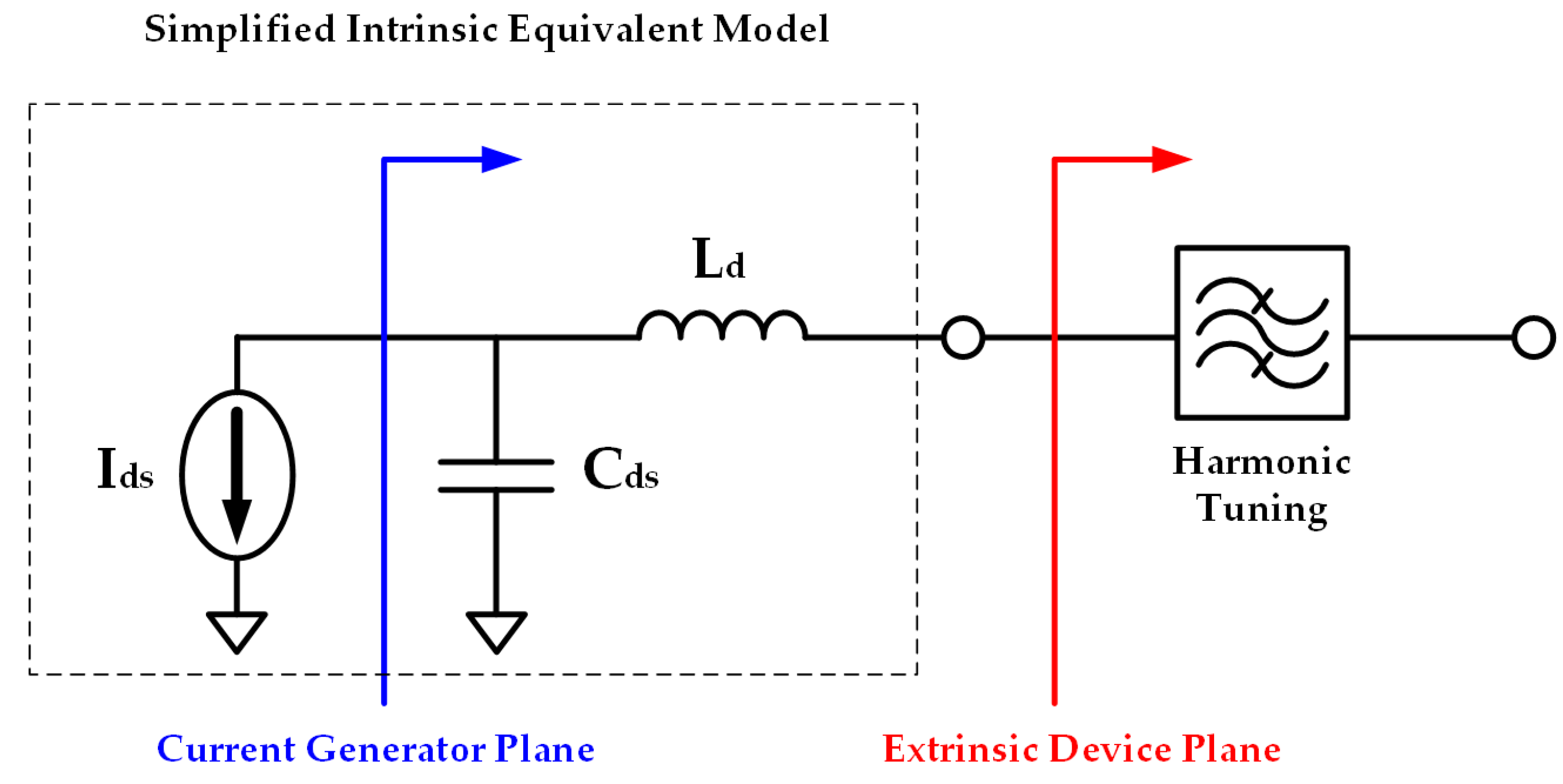

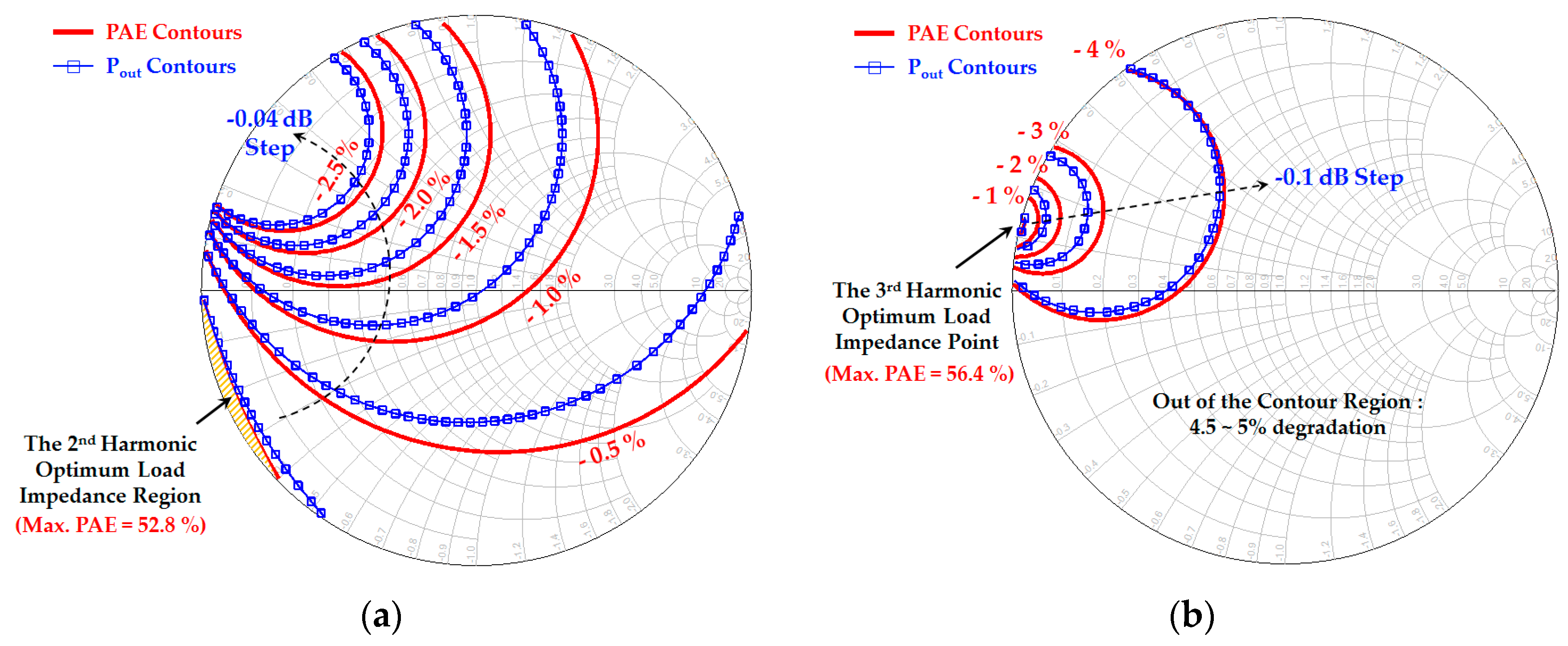

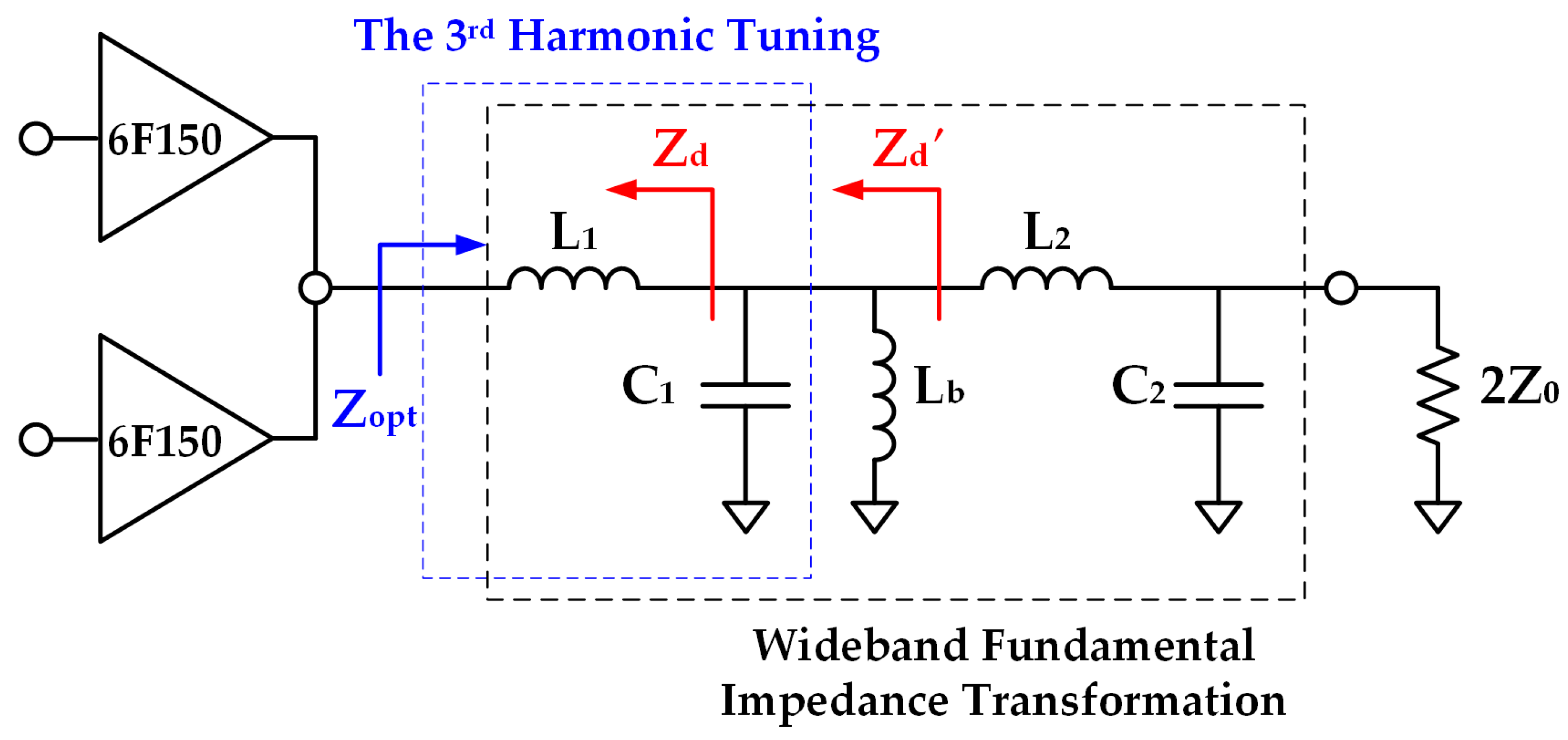

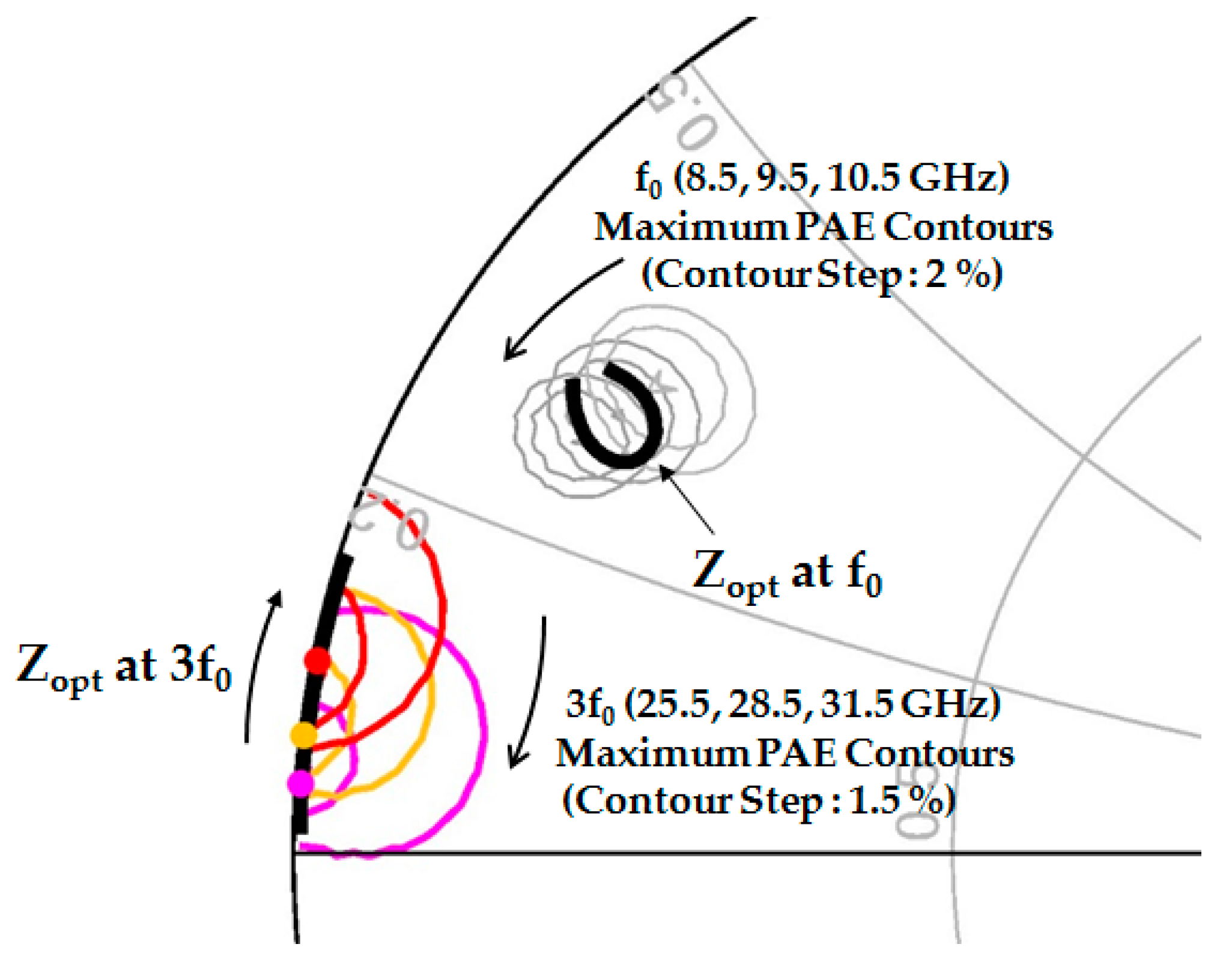

3.1. Output Matching Circuit Design with the Third Harmonic-Tuned Circuit

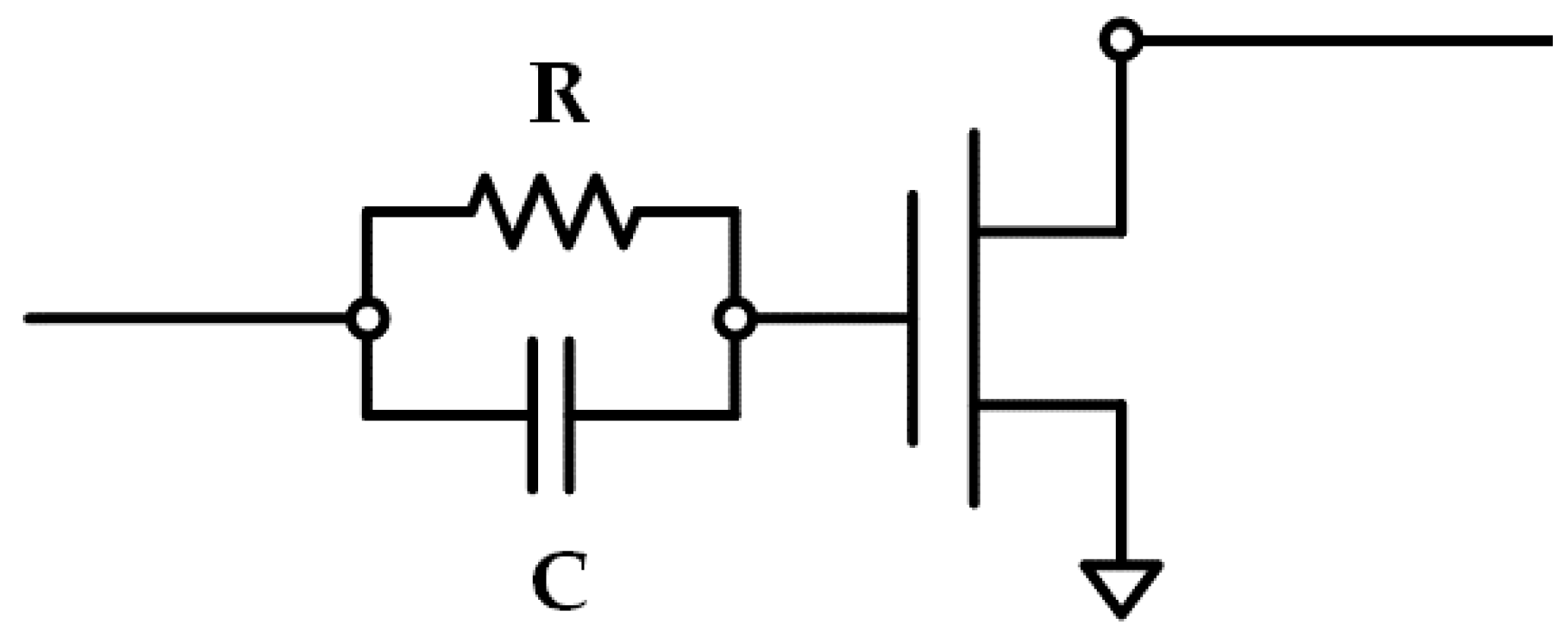

3.2. Design of Input Matching Circuit Using Lossy Matching

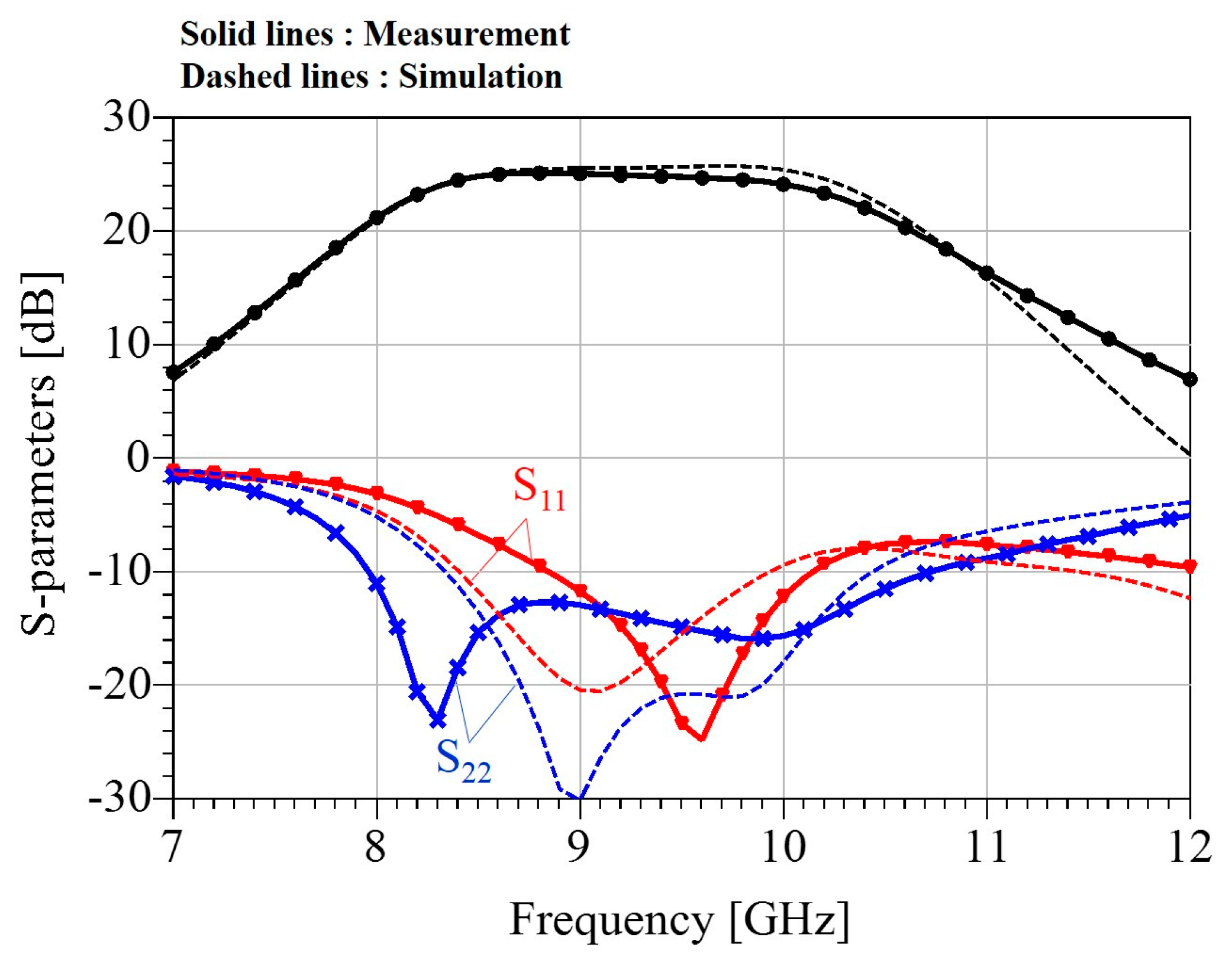

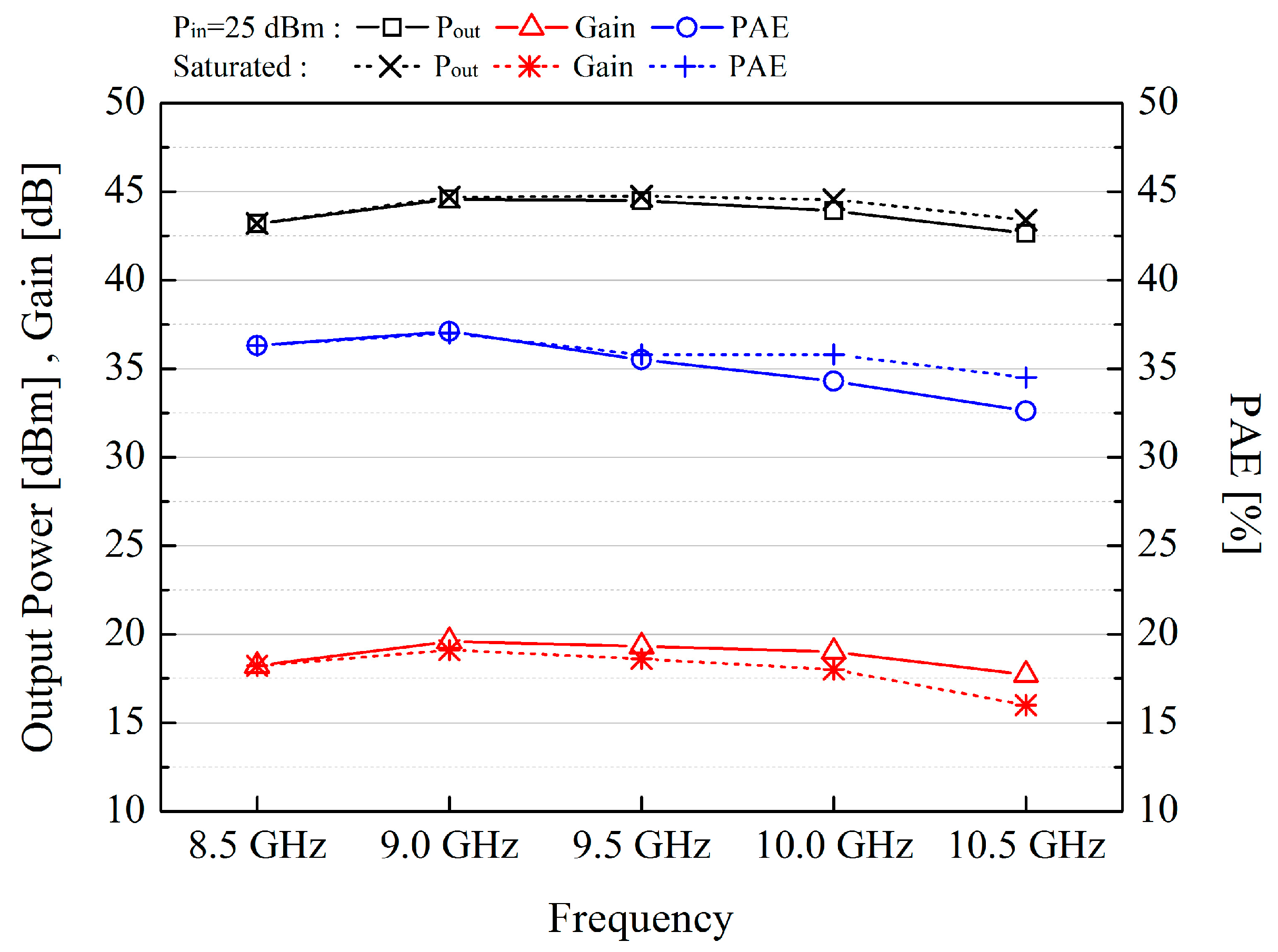

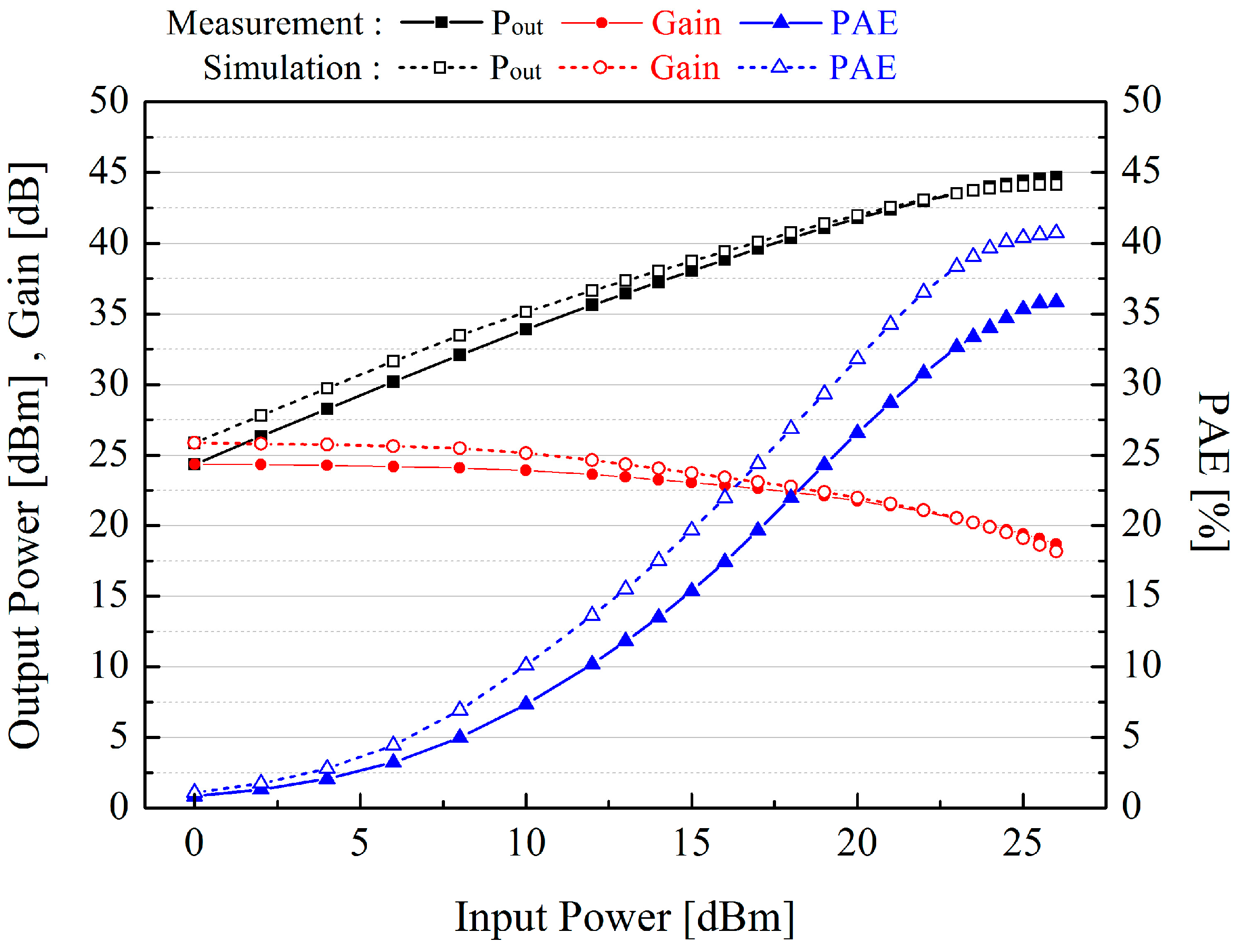

4. Fabrication and Measurement

5. Discussion

6. Conclusions

Author Contributions

Conflicts of Interest

References

- Brookner, E. Phased Array Radars-Past, Present and Future. In Proceedings of the 2002 RADAR, Edinburgh, UK, 15–17 October 2002; pp. 104–113. [Google Scholar]

- Ludwig, M.; Feldle, H.-P.; Ott, H. A Miniaturised X-Band T/R-Module for SAR-Systems Based on Active Phased Array Techniques. In Proceedings of the 1995 International Geoscience and Remote Sensing Symposium, Firenze, Italy, 10–14 July 1995; pp. 2063–2065. [Google Scholar]

- Lacomme, P. New Trends in Airborne Phased Array Radars. In Proceedings of the 2003 IEEE International Symposium on Phased Array Systems and Technology, Boston, MA, USA, 14–17 October 2003; pp. 17–22. [Google Scholar]

- Terry, E. Semiconductor Technology Trends for Phased Array Antenna Power Amplifiers. In Proceedings of the 2006 3rd European Radar Conference, Manchester, UK, 13–15 September 2006; pp. 269–272. [Google Scholar]

- Bettidi, A.; Cetronio, A.; Cicolani, M.; Costrini, C.; Lanzieri, C.; Maccaroni, S.; Marescialli, L.; Peroni, M.; Romanini, P. X-Band T/R Module in State-of-the-Art GaN Technology. In Proceedings of the 2009 European Radar Conference, Rome, Italy, 30 September–2 October 2009; pp. 258–261. [Google Scholar]

- Ortega-Gonzalez, F.-J.; Tena-Ramos, D.; Patiño-Gomez, M.; Pardo-Martin, J.M.; Madueño-Pulido, D. High-Power Wideband L-Band Suboptimum Class-E Power Amplifier. IEEE Trans. Microw. Theory Tech. 2013, 61, 3712–3720. [Google Scholar] [CrossRef]

- Liu, S.; Schreurs, D. Intrinsic Class-F RF GaN Power Amplifier with a Commercial Transistor Based on a Modified Hybrid Approach. In Proceedings of the 2012 Workshop on Integrated Nonlinear Microwave and Millimetre-wave Circuits, Dublin, Ireland, 3–4 September 2012. [Google Scholar]

- Rezaei, S.; Belostotski, L.; Ghannouchi, F.-M.; Aflaki, P. Integrated Design of a Class-J Power Amplifier. IEEE Trans. Microw. Theory Tech. 2013, 61, 1639–1648. [Google Scholar] [CrossRef]

- Piotrowicz, S.; Ouarch, Z.; Chartier, E.; Aubry, R.; Callet, G.; Floriot, D.; Jacquet, J.-C.; Jardel, O.; Morvan, E.; Reveyrand, T.; et al. 43W, 52% PAE X-Band AlGaN/GaN HEMTs MMIC Amplifiers. In Proceedings of the 2010 IEEE MTT-S International Microwave Symposium Digest, Anaheim, CA, USA, 23–28 May 2010; pp. 505–508. [Google Scholar]

- Kühn, J.; van Raay, F.; Quay, R.; Kiefer, R.; Maier, T.; Stibal, R.; Mikulla, M.; Seelmann-Eggebert, M.; Bronner, W.; Schlechtweg, M.; et al. Design of Highly-Efficient GaN X-Band Power Amplifier MMICs. In Proceedings of the 2009 IEEE MTT-S International Microwave Symposium Digest, Boston, MA, USA, 7–12 June 2009; pp. 661–664. [Google Scholar]

- Sardin, D.; Reveyrand, T.; Popović, Z. X-band 10 W MMIC High-Gain Power Amplifier with up to 60% PAE. In Proceedings of the 2014 9th European Microwave Integrated Circuit Conference, Rome, Italy, 6–7 October 2014; pp. 393–396. [Google Scholar]

- Resca, D.; Raffo, A.; Falco, S.-D.; Scappaviva, F.; Vadalà, V. X-Band GaN Power Amplifier for Future Generation SAR Systems. IEEE Microw. Wirel. Compon. Lett. 2014, 24, 266–268. [Google Scholar] [CrossRef]

- WIN Semiconductors Corp. Process Roadmap. Available online: http://www.winsemiconductorscorp.com (accessed on 1 July 2016).

- Lee, S.-K.; Bae, K.-T.; Kim, D.-W. 2–6 GHz GaN HEMT Power Amplifier MMIC with Bridged-T All-Pass Filters and Output-Reactance-Compensation Shorted Stubs. J. Semicond. Technol. Sci. 2016, 16, 312–318. [Google Scholar] [CrossRef]

- Costrini, C.; Cetronio, A.; Romanini, P.; Breglio, G.; Irace, A.; Riccio, M. 50W X-band GaN MMIC HPA: Effective Power Capability and Transient Thermal Analysis. In Proceedings of the 2010 40th European Microwave Conference, Paris, France, 28–30 September 2010; pp. 1650–1653. [Google Scholar]

- D’Angelo, S.; Biondi, A.; Scappaviva, F.; Resca, D.; Monaco, V.-A. A GaN MMIC Chipset Suitable for Integration in Future X-band Spaceborne Radar T/R Module Frontends. In Proceedings of the 2016 21st International Conference on Microwave, Radar and Wireless Communications (MIKON), Krakow, Poland, 9–11 May 2016. [Google Scholar]

- Shin, D.-H.; Yom, I.-B.; Kim, D.-W. X-Band GaN MMIC Power Amplifier for the SSPA of a SAR System. In Proceedings of the 2017 IEEE International Symposium on Radio-Frequency Integration Technology, Seoul, Korea, 30 August–1 September 2017; pp. 93–95. [Google Scholar]

- Wolfspeed, MMIC Bare Die, CMPA801B025D Data Sheet. Available online: http://www.wolfspeed.com (accessed on 1 October 2017).

- Qorvo, High Frequency Amplifiers, TGA2624 Data Sheet. Available online: http://www.qorvo.com (accessed on 1 October 2017).

| Reference | Technology | Frequency (GHz) | Pulse Width/Duty (μs/%) | Vds (V) | Pout (W) | PAE (%) | Area (mm2) | Power Density (W/mm2) |

|---|---|---|---|---|---|---|---|---|

| [9] | 0.25 μm GaN | 8.5–11.0 | 20/10 | 25 | 25–43 | 33–52 | 18 | 2.89 |

| [10] | 0.25 μm GaN | 8.5–10.5 | 100/10 | 30 | 17–19 | 32–35 | 13.5 | 1.41 |

| [11] | 0.25 μm GaN | 10.0–10.5 | CW | 25 | 10–14 | 45–61 | 9.2 | 1.52 |

| [12] | 0.25 μm GaN | 8.6–10.6 | 50/15 | 26 | 12–15 | 38–43 | 18 | 0.83 |

| [15] | 0.5 μm GaN | 8.0–10.5 | 10/1 | 35 | 50–57 | 27–32 | 16 | 3.56 |

| [16] | 0.25 μm GaN | 8.8–10.2 | 100/30 | 30 | 28–32 | 36–37 | 22 | 1.45 |

| [17] | 0.25 μm GaN | 8.8–10.8 | 100/10 | 28 | 30–40 | 38–44 | 20.7 | 1.93 |

| [18] | 0.25 μm GaN | 8.0–11.0 | 100/10 | 28 | 32–47 | 37–44 | 17.28 | 2.72 |

| [19] | 0.25 μm GaN | 9.0–10.5 | 100/10 | 28 | 18–20 | 40–43 | 13 | 1.54 |

| This Work | 0.25 μm GaN | 8.5–10.5 | 100/10 | 28 | 21–29 | 35–37 | 13.26 | 2.19 |

© 2017 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).

Share and Cite

Bae, K.-T.; Lee, I.-J.; Kang, B.; Sim, S.; Jeon, L.; Kim, D.-W. X-Band GaN Power Amplifier MMIC with a Third Harmonic-Tuned Circuit. Electronics 2017, 6, 103. https://doi.org/10.3390/electronics6040103

Bae K-T, Lee I-J, Kang B, Sim S, Jeon L, Kim D-W. X-Band GaN Power Amplifier MMIC with a Third Harmonic-Tuned Circuit. Electronics. 2017; 6(4):103. https://doi.org/10.3390/electronics6040103

Chicago/Turabian StyleBae, Kyung-Tae, Ik-Joon Lee, Byungjoo Kang, Sanghoon Sim, Laurence Jeon, and Dong-Wook Kim. 2017. "X-Band GaN Power Amplifier MMIC with a Third Harmonic-Tuned Circuit" Electronics 6, no. 4: 103. https://doi.org/10.3390/electronics6040103