Reduced-Area Constant-Coefficient and Multiple-Constant Multipliers for Xilinx FPGAs with 6-Input LUTs

Abstract

:1. Introduction

- Embedded multiplier operands are fixed in size and type, such as two’s complement, while LUT-based KCM operands can be any size or type;

- The number and location of embedded multipliers are fixed, while LUT-based KCMs can be placed anywhere and the number is limited only by the size of the reconfigurable fabric;

2. Background

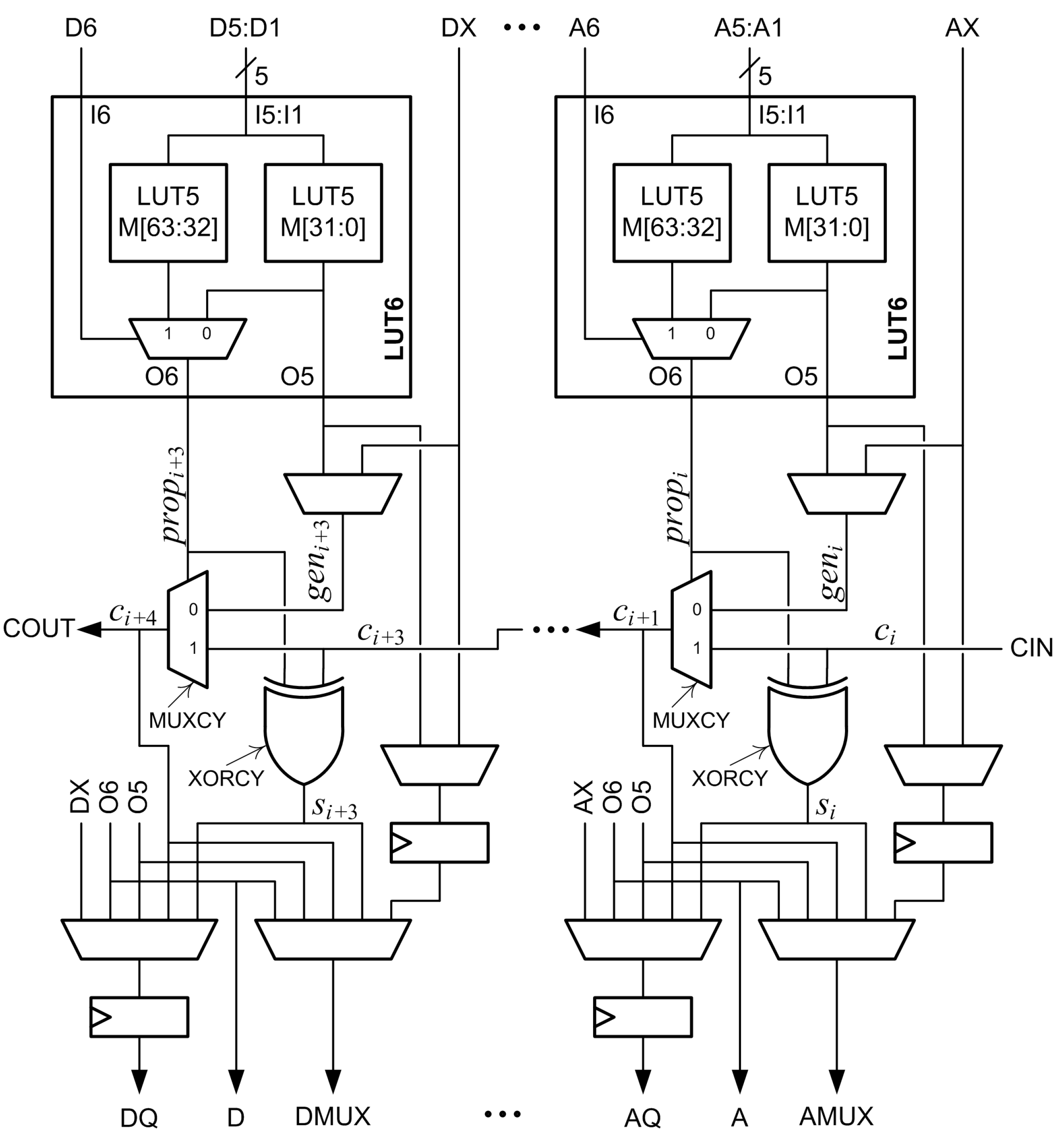

2.1. FPGA Logic Fabric

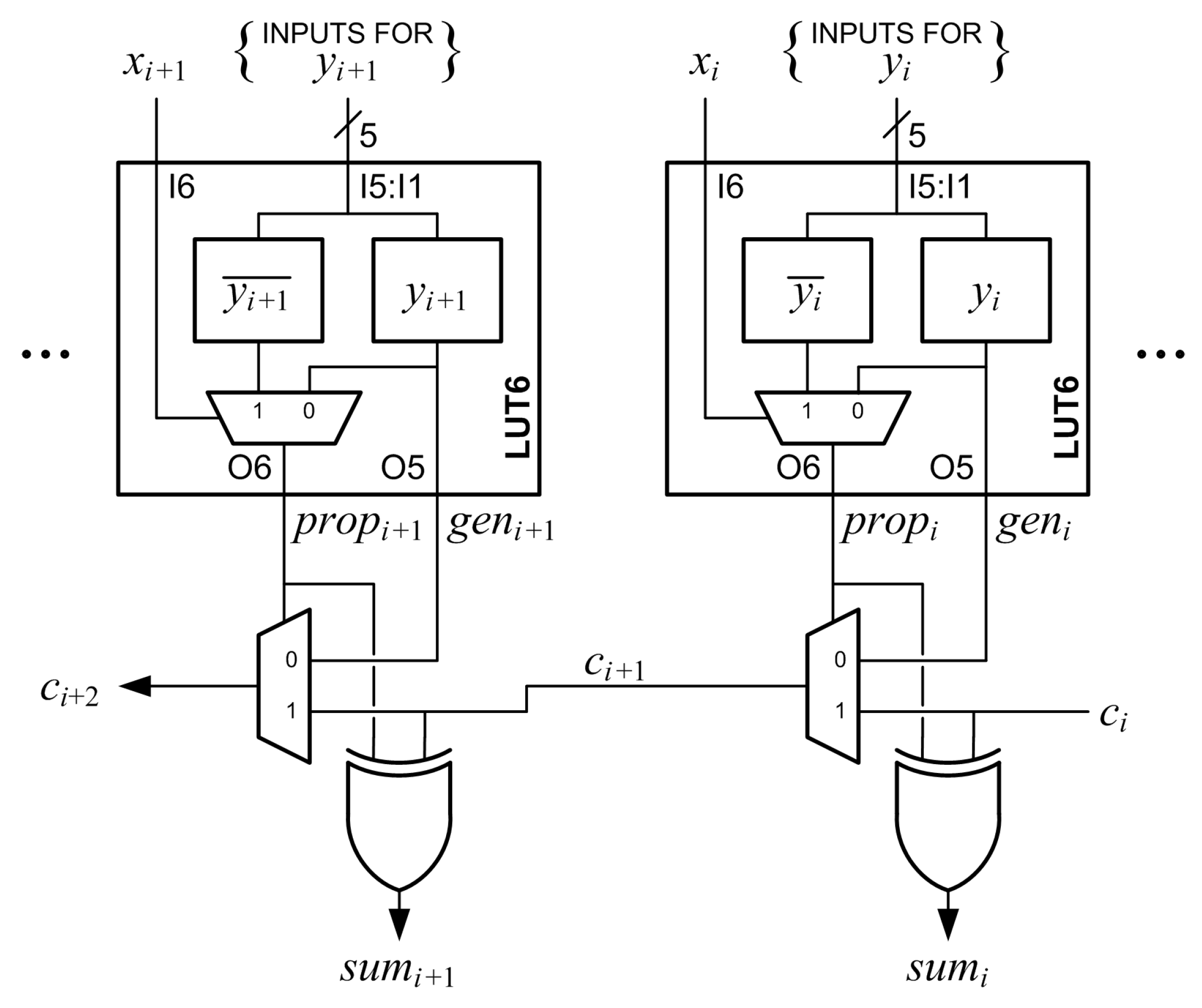

2.2. Proposed Two-Operand Adder

3. Proposed Constant-Coefficient Multipliers

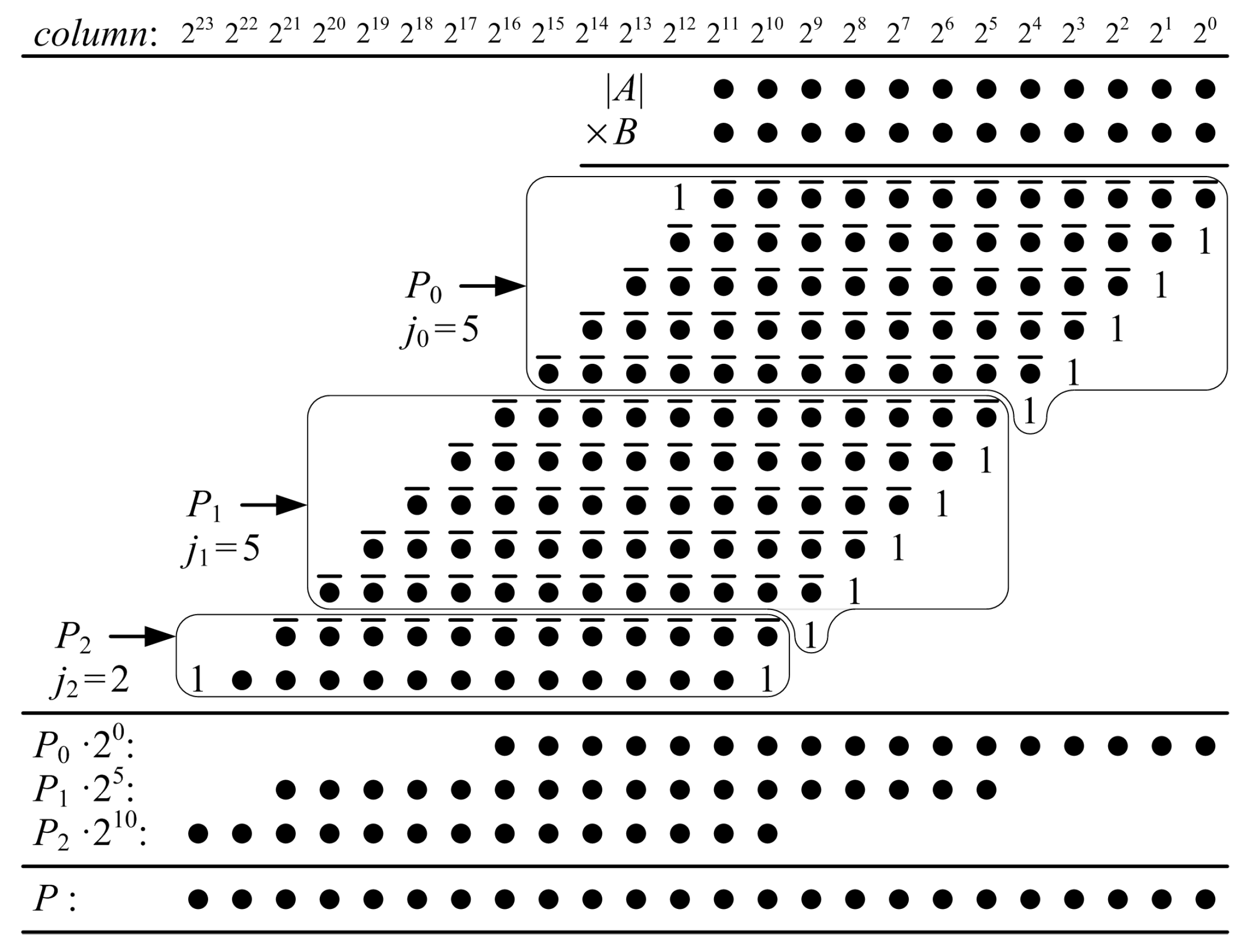

3.1. Radix-2 Multiplication by a Constant

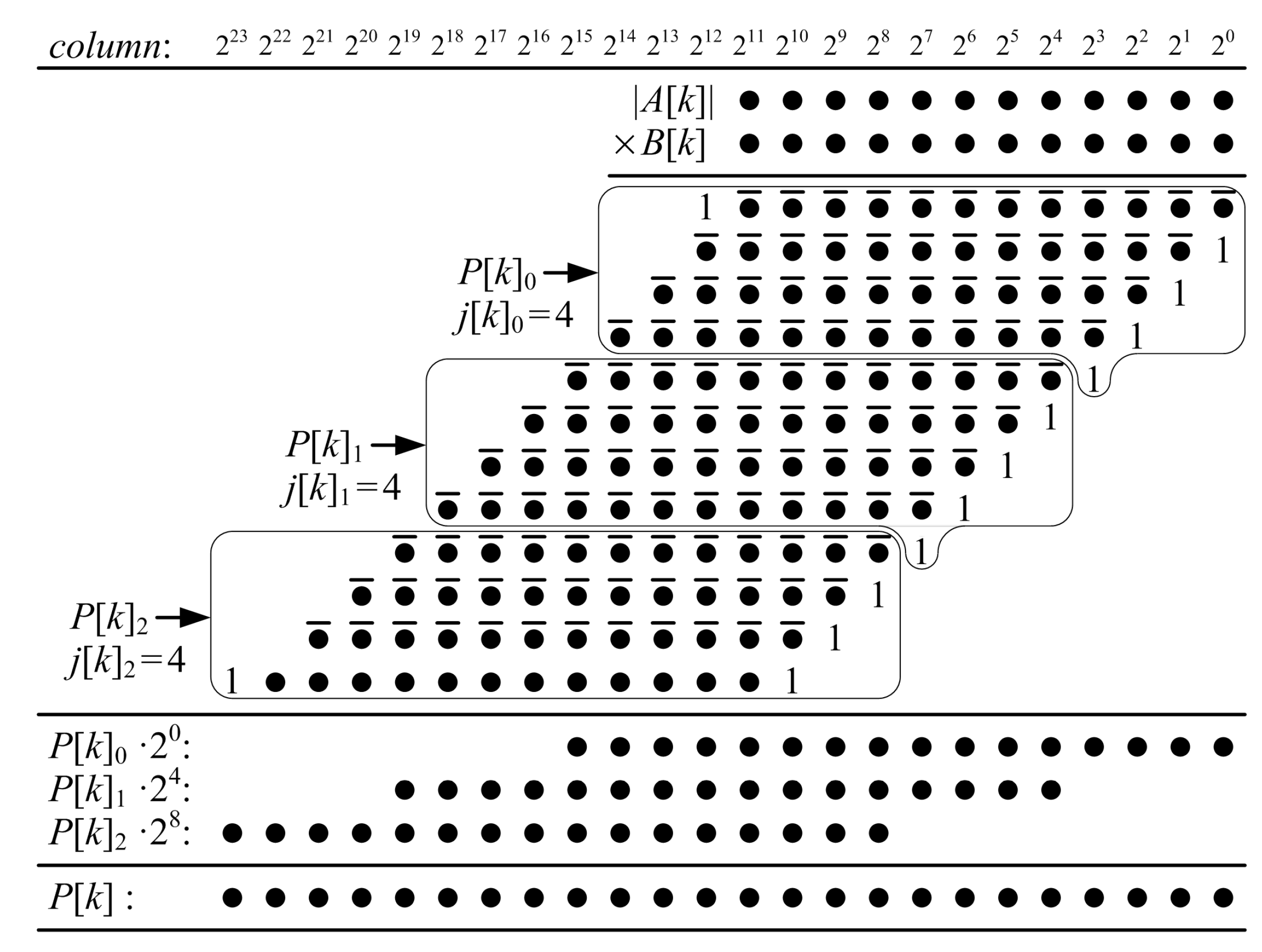

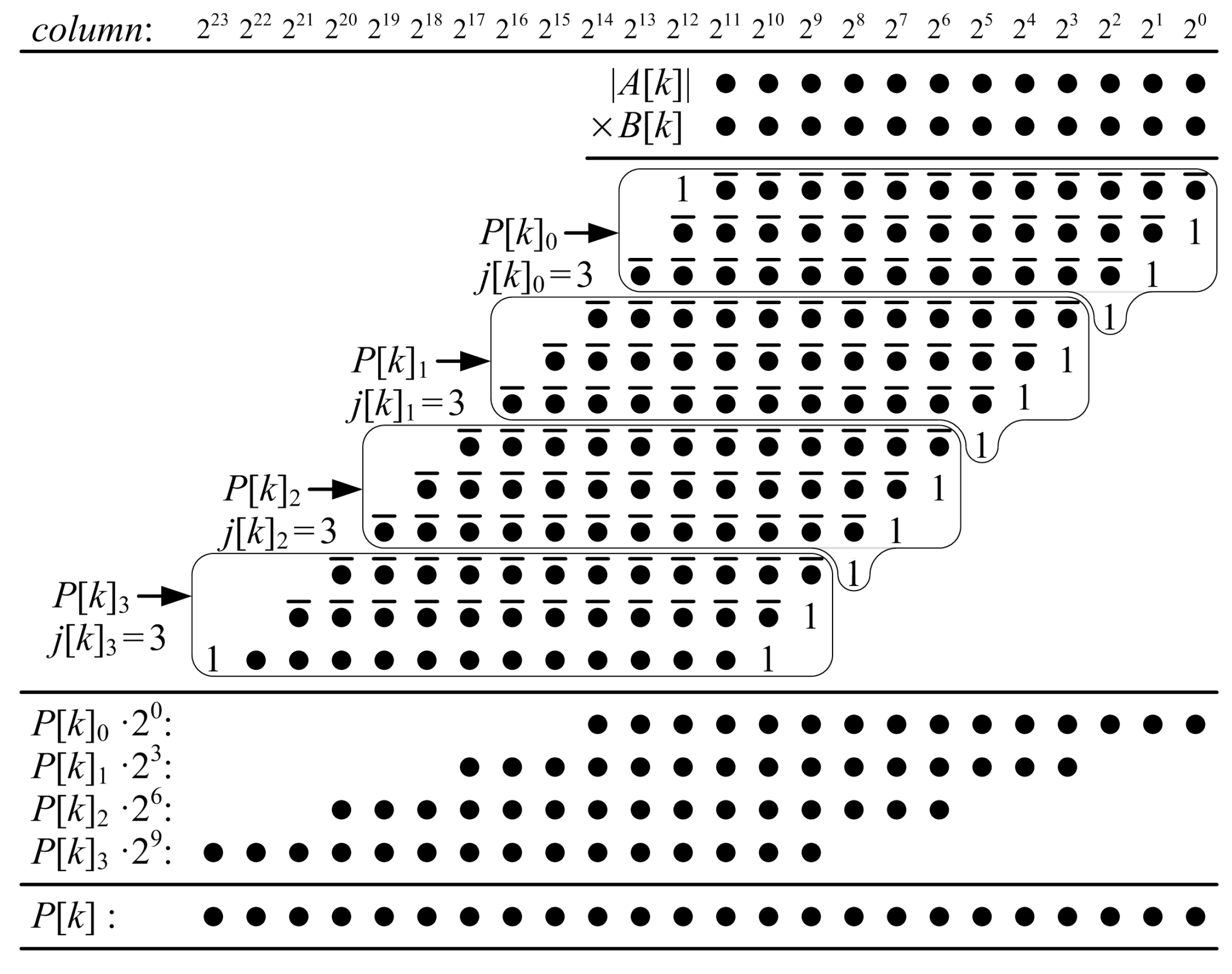

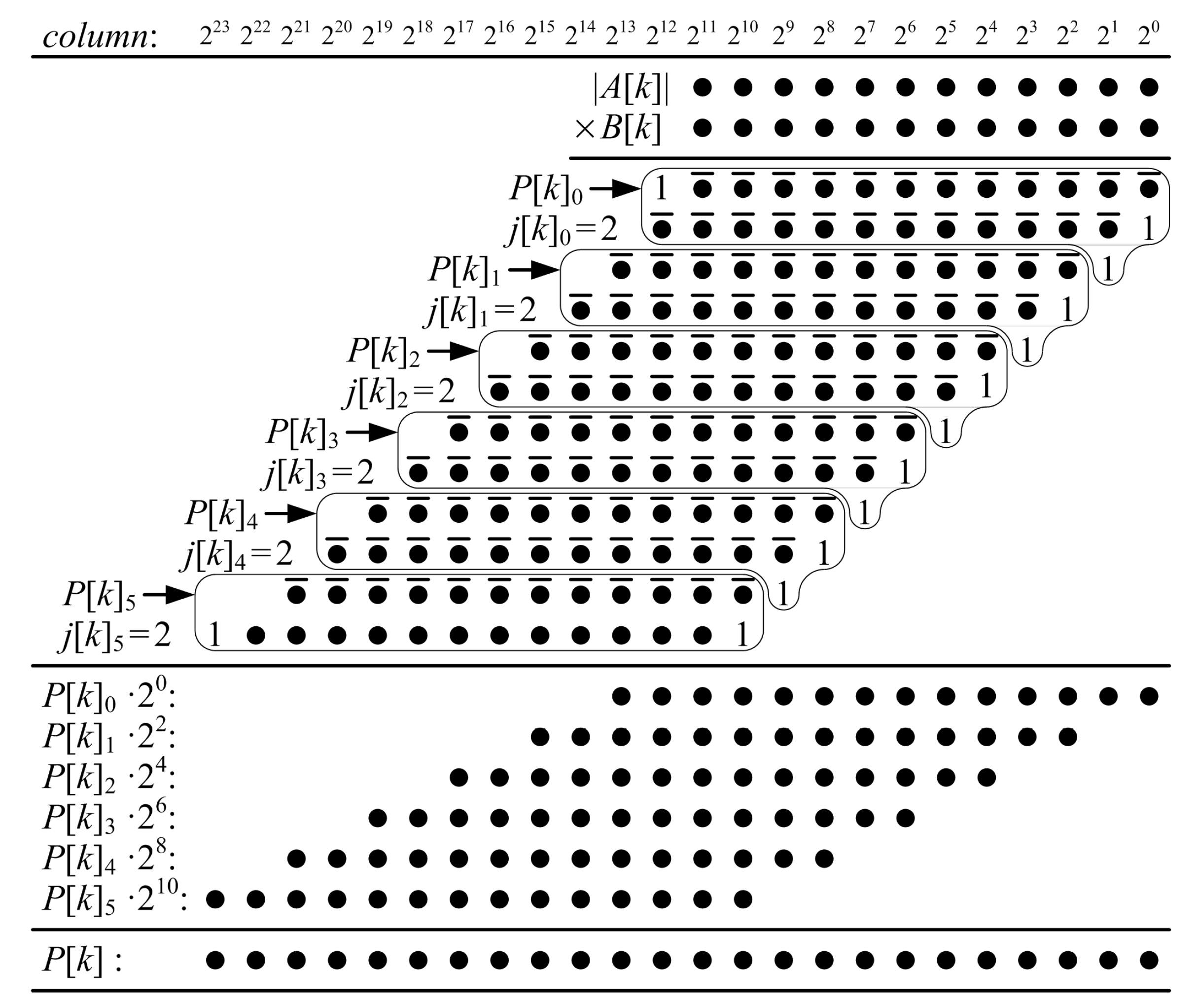

3.2. Design of Proposed Constant-Coefficient Multiplier

3.3. Array Structure and Pipelining

3.4. Discussion

4. Proposed KCMs with Selectable Coefficients

4.1. Proposed KCMs with Two Selectable Coefficients

4.2. Proposed KCMs with Four Selectable Coefficients

4.3. Proposed KCMs with Eight Selectable Coefficients

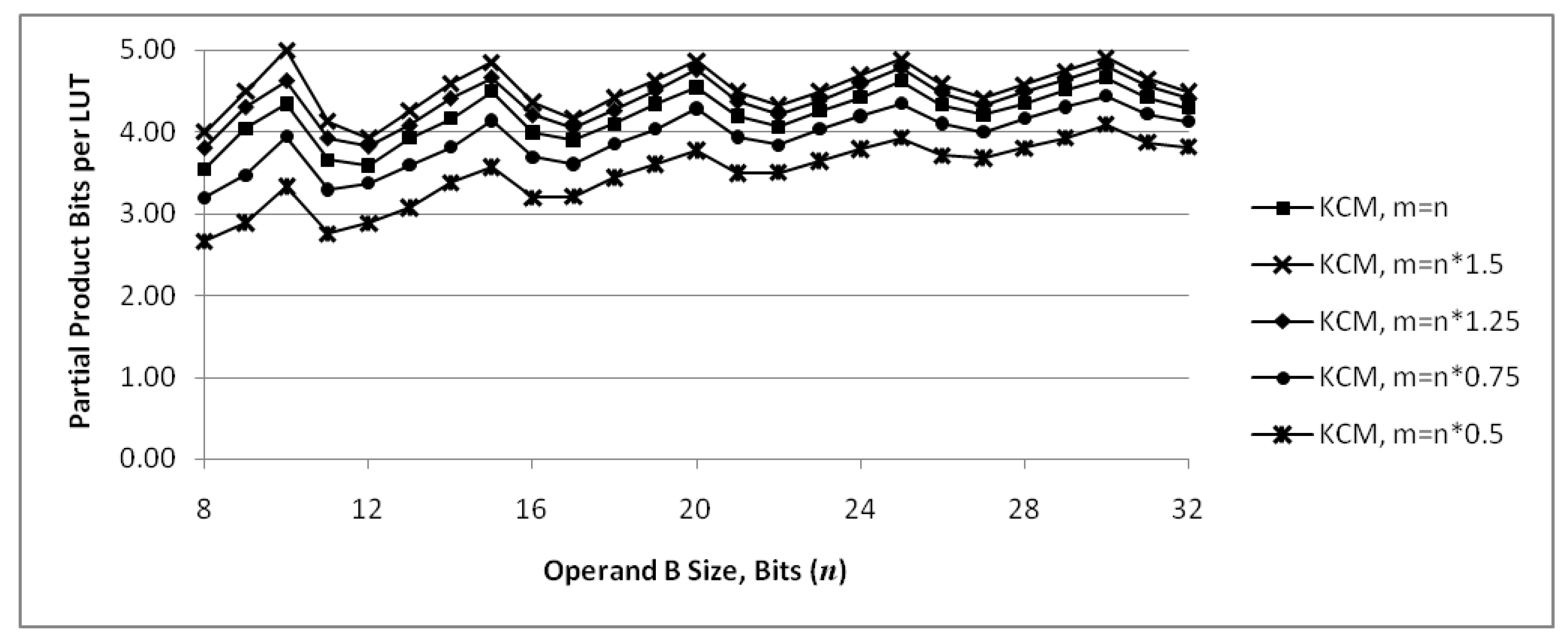

4.4. Discussion

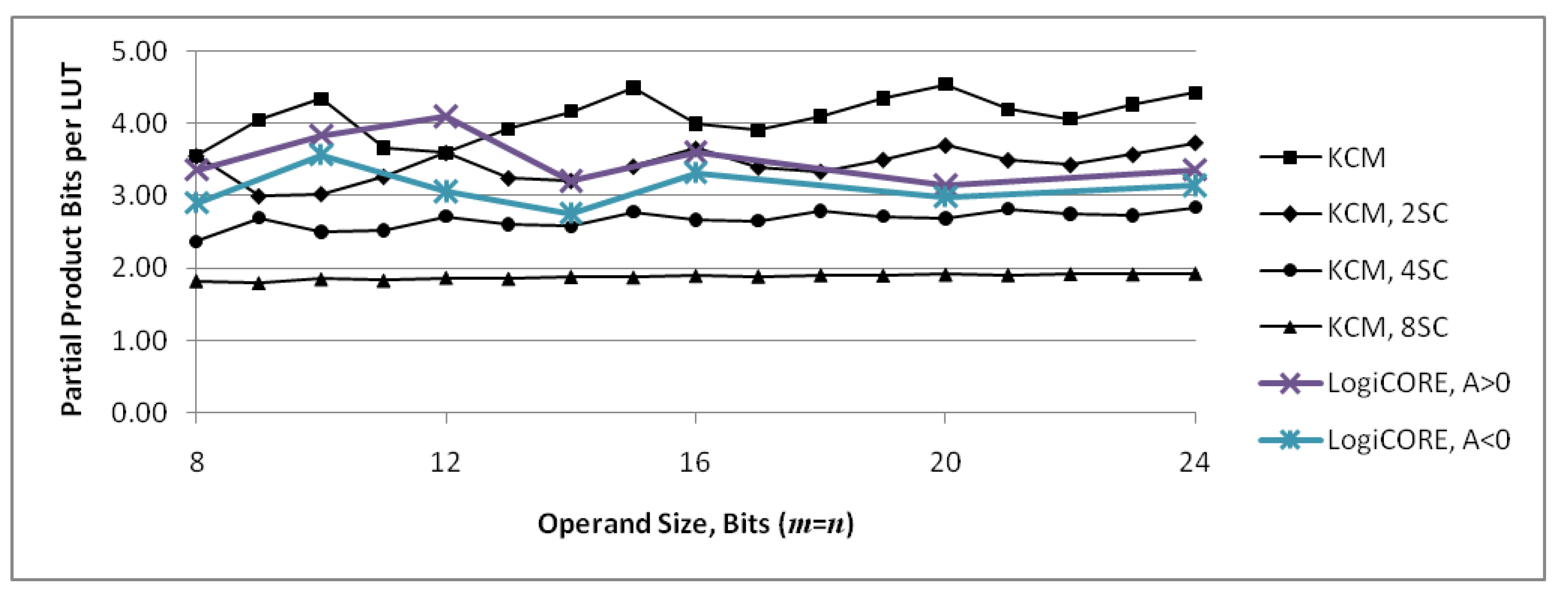

5. Results

5.1. Methodology

5.2. SynthesisResults

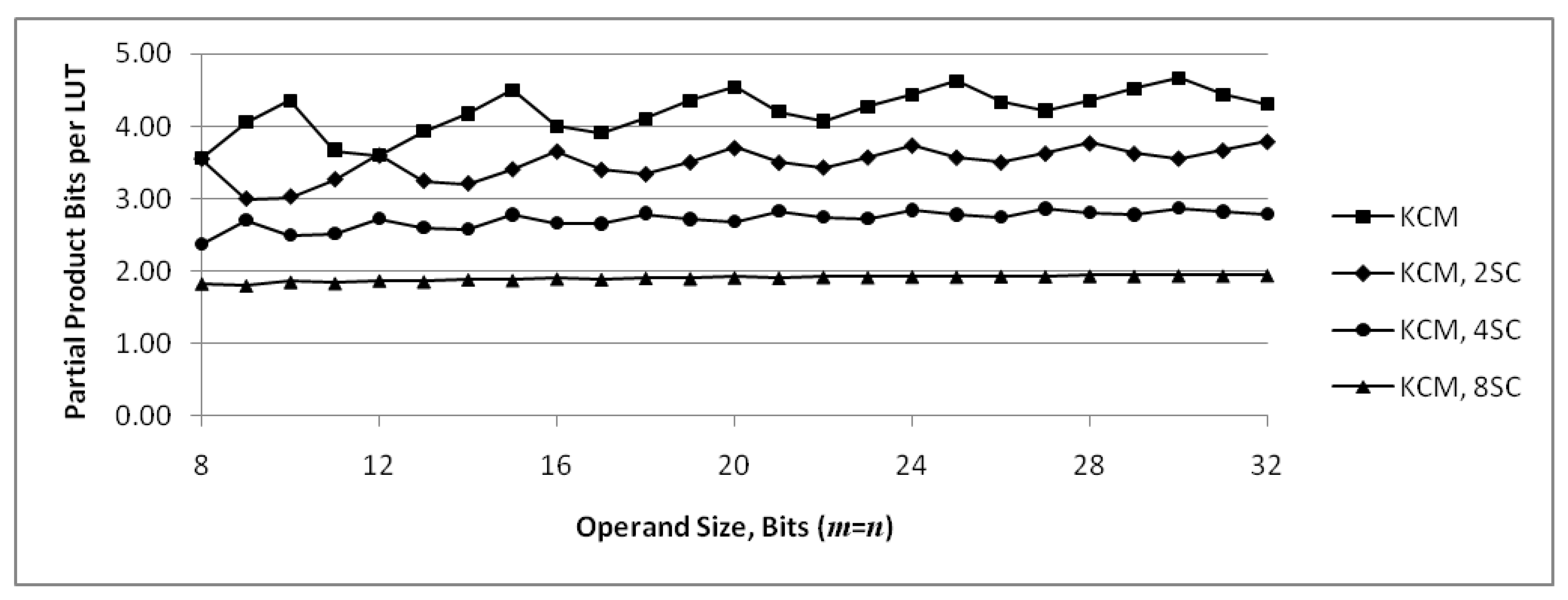

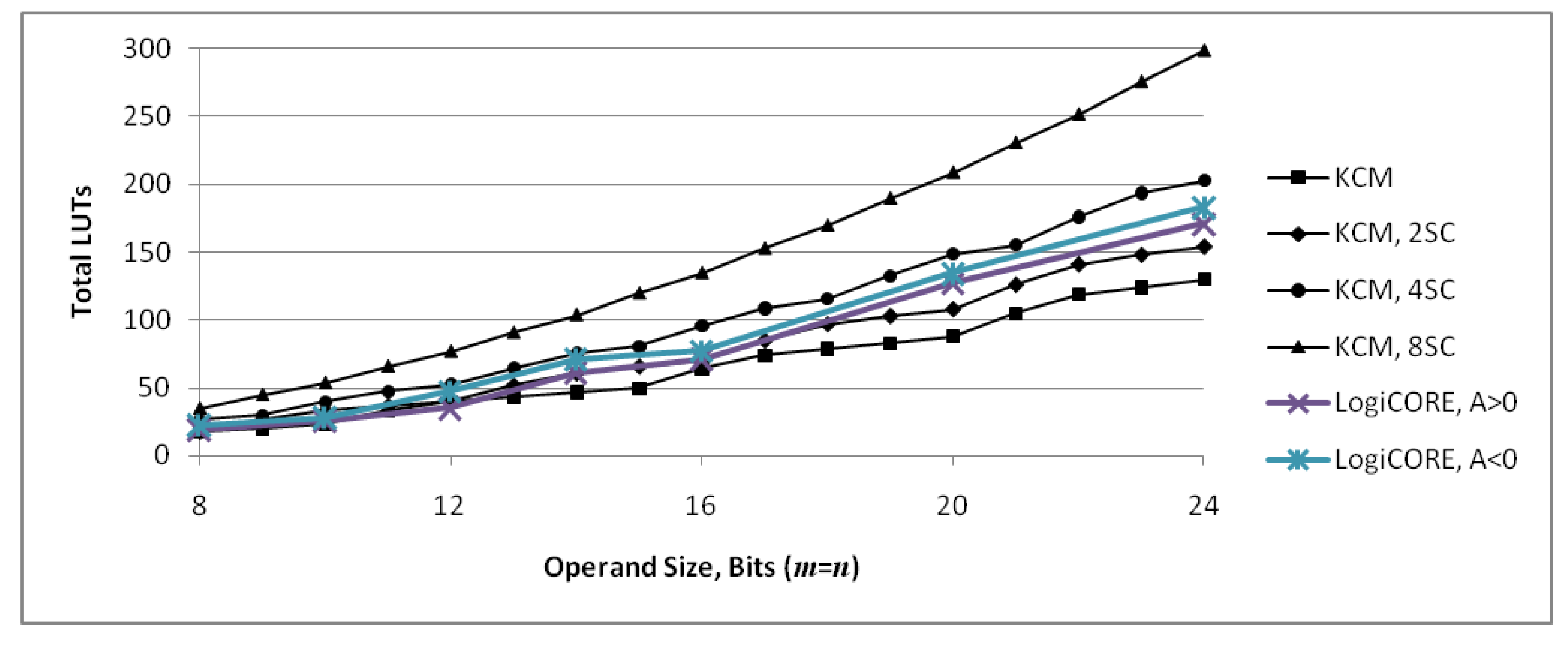

5.2.1. Proposed Constant-Coefficient Multipliers

5.2.2. Proposed KCMs with Two Selectable Coefficients

5.2.3. Proposed KCMs with Four Selectable Coefficients

5.2.4. Proposed KCMs with Eight Selectable Coefficients

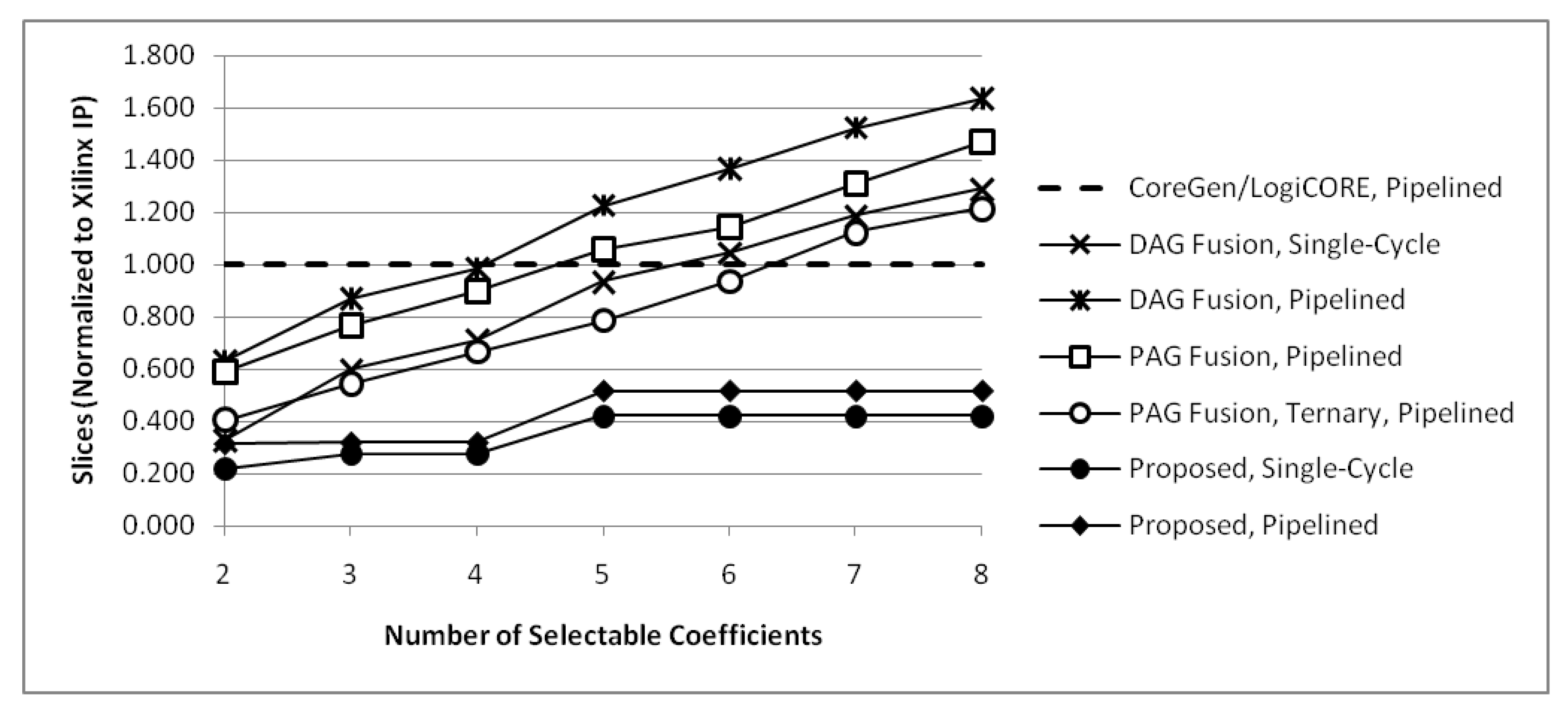

5.3. Comparison to Möller Et Al.

6. Conclusions

Acknowledgments

Author Contributions

Conflicts of Interest

Abbreviations

| BRAM | Block RAM (Random-Access Memory) |

| CLB | Configurable Logic Block |

| CSD | Canonical Signed Digit |

| DAG | Directed Acyclic Graph |

| DSP | Digital-Signal Processing |

| FPGA | Field-Programmable Gate Array |

| KCM | Constant-Coefficient Multiplier |

| LDP | LUT-Delay Product |

| LSB | Least-Significant Bit |

| LUT | Lookup Table |

| LUT5 | 5-Input Lookup Table |

| LUT6 | 6-Input Lookup Table |

| MSB | Most-Significant Bit |

| PAG | Pipelined Adder Graph |

| RCM | Reduced Coefficient Multiplier |

| PAG | Reduced Pipelined Adder Graph |

References

- Swartzlander, E.E., Jr. Merged Arithmetic. IEEE Trans. Comput. 1980, C-29, 946–950. [Google Scholar] [CrossRef]

- Ercegovac, M. On Approximate Arithmetic. In Proceedings of the 47th Asilomar Conference on Signals, Systems, and Computers, Pacific Grove, CA, USA, 3–6 November 2013; pp. 126–130. [Google Scholar]

- Chapman, K.D. Fast Integer Multipliers Fit in FPGAs; EDN Magazine: AspenCore Media, San Francisco, CA, USA, 1994. [Google Scholar]

- Chapman, K. Constant Coefficient Multipliers for the XC4000E; Version 1.1; Application Note XAPP 054; Xilinx: San Jose, CA, USA, 1996. [Google Scholar]

- Wirthlin, M.J. Constant Coefficient Multiplication Using Look-Up Tables. J. VLSI Signal Process. Syst. Signal Image Video Technol. 2004, 36, 7–15. [Google Scholar] [CrossRef]

- Hormigo, J.; Caffarena, G.; Oliver, J.P.; Boemo, E. Self-Reconfigurable Constant Multiplier for FPGA. ACM Trans. Reconfig. Technol. Syst. 2013, 6, 14:1–14:17. [Google Scholar] [CrossRef]

- Ercegovac, M.; Lang, T. Digital Arithmetic; Morgan Kaufmann: San Francisco, CA, USA, 2004. [Google Scholar]

- Brisebarre, N.; de Dinechin, F.; Muller, J.M. Integer and Floating-Point Constant Multipliers for FPGAs. In Proceedings of the International Conference on Application-Specific Systems, Architectures and Processors (ASAP), Leuven, Belgium, 2–4 July 2008; pp. 239–244. [Google Scholar]

- Gustafsson, O.; Dempster, A.G.; Johansson, K.; Macleod, M.D.; Wanhammar, L. Simplified Design of Constant Coefficient Multipliers. Circuits Syst. Signal Process. 2006, 25, 225–251. [Google Scholar] [CrossRef]

- Turner, R.H.; Woods, R.F. Highly Efficient, Limited Range Multipliers for LUT-Based FPGA Architectures. IEEE Trans. VLSI Syst. 2004, 12, 1113–1117. [Google Scholar] [CrossRef]

- Tummeltshammer, P.; Hoe, J.C.; Püschel, M. Time-Multiplexed Multiple-Constant Multiplication. IEEE Trans. Comput.-Aided Des. Integr. Circuits Syst. 2007, 26, 1551–1563. [Google Scholar] [CrossRef]

- Kumm, M.; Zipf, P.; Faust, M.; Chang, C.H. Pipelined Adder Graph Optimization for high speed multiple constant multiplication. In Proceedings of the 2012 IEEE International Symposium on Circuits and Systems (ISCAS), Seoul, Korea, 20–23 May 2012; pp. 49–52. [Google Scholar]

- Möller, K.; Kumm, M.; Kleinlein, M.; Zipf, P. Reconfigurable Constant Multiplication for FPGAs. IEEE Trans. Comput.-Aided Des. Integr. Circuits Syst. 2017, 36, 927–937. [Google Scholar] [CrossRef]

- Walters, E.G., III. Partial-Product Generation and Addition for Multiplication in FPGAs With 6-Input LUTs. In Proceedings of the 48th Asilomar Conference on Signals, Systems, and Computers, Pacific Grove, CA, USA, 2–5 November 2014; pp. 1247–1251. [Google Scholar]

- Walters, E.G., III. Techniques and Devices for Performing Arithmetic. US Patent Application 15/025,770, 29 March 2016. [Google Scholar]

- Walters, E.G., III. Array Multipliers for FPGAs With 6-Input LUTs. Computers 2016, 5, 20:1–20:25. [Google Scholar] [CrossRef]

- Young, S.P.; Bauer, T.J. Programmable Integrated Circuit Providing Efficient Implementations of Arithmetic Functions. US Patent 7 218 139, 15 May 2007. [Google Scholar]

- Xilinx. 7 Series FPGAs Configurable Logic Block User Guide; UG474 (v1.4); Xilinx: San Jose, CA, USA, 2012. [Google Scholar]

- Baugh, C.R.; Wooley, B.A. A Two’s Complement Parallel Array Multiplication Algorithm. IEEE Trans. Comput. 1973, C-22, 1045–1047. [Google Scholar] [CrossRef]

- Xilinx. Multiplier v12.0 LogiCORE IP Product Guide; PG108; Xilinx: San Jose, CA, USA, 2015. [Google Scholar]

- Xilinx. LogiCORE IP Multiplier v11.2 Product Specification; DS255; Xilinx: San Jose, CA, USA, 2011. [Google Scholar]

| One Coefficient | Two Coefficient | Four Coefficient | Eight Coefficient | ||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|

| n | PPs | LUTs | PPs | LUTs | Increase | PPs | LUTs | Increase | PPs | LUTs | Increase |

| 8 | 2 | 18 | 2 | 18 | 0% | 3 | 27 | 50% | 4 | 35 | 94% |

| 10 | 2 | 23 | 3 | 33 | 43% | 3 | 40 | 74% | 5 | 54 | 135% |

| 12 | 3 | 40 | 3 | 40 | 0% | 4 | 53 | 33% | 6 | 77 | 93% |

| 14 | 3 | 47 | 4 | 61 | 30% | 5 | 76 | 62% | 7 | 104 | 121% |

| 16 | 3 | 64 | 4 | 70 | 9% | 5 | 96 | 50% | 8 | 135 | 111% |

| 18 | 4 | 79 | 5 | 97 | 23% | 6 | 116 | 47% | 9 | 170 | 115% |

| 20 | 4 | 88 | 5 | 108 | 23% | 7 | 149 | 69% | 10 | 209 | 138% |

| 22 | 5 | 119 | 6 | 141 | 18% | 7 | 176 | 48% | 11 | 252 | 112% |

| 24 | 5 | 130 | 6 | 154 | 18% | 8 | 203 | 56% | 12 | 299 | 130% |

| Magnitude of A, | Magnitude of A, | |||

|---|---|---|---|---|

| n | Integer | Binary | Integer | Binary |

| 8 | 201 | 11001001 | 151 | 10010111 |

| 10 | 805 | 1100100101 | 603 | 1001011011 |

| 12 | 3,217 | 110010010001 | 2,413 | 100101101101 |

| 14 | 12,867 | 11001001000011 | 9,651 | 10010110110011 |

| 16 | 51,471 | 1100100100001111 | 38,603 | 1001011011001011 |

| 20 | 823,549 | 11001001000011111101 | 617,663 | 10010110110010111111 |

| 24 | 13,176,795 | 110010010000111111011011 | 9,882,595 | 100101101100101111100011 |

| Magnitude of A, | Magnitude of A, | |||

| n | Integer | Binary | Integer | Binary |

| 8 | 251 | 11111011 | 175 | 10101111 |

| 10 | 1,005 | 1111101101 | 703 | 1010111111 |

| 12 | 4,021 | 111110110101 | 2,815 | 101011111111 |

| 14 | 16,085 | 11111011010101 | 11,259 | 10101111111011 |

| 16 | 64,339 | 1111111101111011 | 45,037 | 1010111111101101 |

| 20 | 1,029,437 | 11111011010100111101 | 720,605 | 10101111111011011101 |

| 24 | 16,470,993 | 111110110101001111010001 | 11,529,695 | 101011111110110111011111 |

| Type | Total | Delay | Normalized | ||||

|---|---|---|---|---|---|---|---|

| n | LUTs | (ns) | LDP | LUTs | Delay | LDP | |

| LogiCORE IP B is signed | 8 | 19 | 0.972 | 18.5 | 1.000 | 1.000 | 1.000 |

| 10 | 26 | 1.083 | 28.2 | 1.000 | 1.000 | 1.000 | |

| 12 | 35 | 1.112 | 38.9 | 1.000 | 1.000 | 1.000 | |

| 14 | 61 | 1.786 | 108.9 | 1.000 | 1.000 | 1.000 | |

| 16 | 71 | 1.869 | 132.7 | 1.000 | 1.000 | 1.000 | |

| 20 | 127 | 2.033 | 258.2 | 1.000 | 1.000 | 1.000 | |

| 24 | 171 | 2.044 | 349.5 | 1.000 | 1.000 | 1.000 | |

| Proposed KCM B is signed | 8 | 17 | 1.463 | 24.9 | 0.895 | 1.505 | 1.347 |

| 10 | 22 | 1.475 | 32.5 | 0.846 | 1.362 | 1.152 | |

| 12 | 40 | 2.308 | 92.3 | 1.143 | 2.076 | 2.372 | |

| 14 | 47 | 2.454 | 115.3 | 0.770 | 1.374 | 1.059 | |

| 16 | 63 | 2.306 | 145.3 | 0.887 | 1.234 | 1.095 | |

| 20 | 87 | 3.149 | 274.0 | 0.685 | 1.549 | 1.061 | |

| 24 | 129 | 4.025 | 519.2 | 0.754 | 1.969 | 1.486 | |

| Type | Total | Delay | Normalized | ||||

|---|---|---|---|---|---|---|---|

| n | LUTs | (ns) | LDP | LUTs | Delay | LDP | |

| LogiCORE IP B is signed | 8 | 22 | 0.958 | 21.1 | 1.000 | 1.000 | 1.000 |

| 10 | 28 | 1.117 | 31.3 | 1.000 | 1.000 | 1.000 | |

| 12 | 47 | 1.115 | 52.4 | 1.000 | 1.000 | 1.000 | |

| 14 | 71 | 1.821 | 129.3 | 1.000 | 1.000 | 1.000 | |

| 16 | 77 | 1.860 | 143.2 | 1.000 | 1.000 | 1.000 | |

| 20 | 134 | 1.980 | 265.3 | 1.000 | 1.000 | 1.000 | |

| 24 | 183 | 2.092 | 382.8 | 1.000 | 1.000 | 1.000 | |

| Proposed KCM B is signed | 8 | 17 | 1.500 | 25.5 | 0.773 | 1.566 | 1.210 |

| 10 | 22 | 1.595 | 35.1 | 0.786 | 1.428 | 1.122 | |

| 12 | 39 | 2.366 | 92.3 | 0.830 | 2.122 | 1.761 | |

| 14 | 46 | 2.405 | 110.6 | 0.648 | 1.321 | 0.856 | |

| 16 | 60 | 2.272 | 136.3 | 0.779 | 1.222 | 0.952 | |

| 20 | 87 | 3.190 | 277.5 | 0.649 | 1.611 | 1.046 | |

| 24 | 129 | 3.969 | 512.0 | 0.705 | 1.897 | 1.337 | |

| Type | Pipeline | Total | Delay | Normalized | ||||

|---|---|---|---|---|---|---|---|---|

| n | Stages | LUTs | (ns) | LDP | LUTs | Delay | LDP | |

| LogiCORE IP B is signed | 8 | 2 | 20 | 0.914 | 18.3 | 1.000 | 1.000 | 1.000 |

| 10 | 2 | 28 | 1.000 | 28.0 | 1.000 | 1.000 | 1.000 | |

| 12 | 2 | 37 | 1.066 | 39.4 | 1.000 | 1.000 | 1.000 | |

| 14 | 3 | 71 | 1.143 | 81.2 | 1.000 | 1.000 | 1.000 | |

| 16 | 3 | 84 | 1.186 | 99.6 | 1.000 | 1.000 | 1.000 | |

| 20 | 3 | 135 | 1.270 | 171.5 | 1.000 | 1.000 | 1.000 | |

| 24 | 3 | 184 | 1.334 | 245.5 | 1.000 | 1.000 | 1.000 | |

| Proposed KCM B is signed | 8 | 2 | 17 | 1.122 | 19.1 | 0.850 | 1.228 | 1.043 |

| 10 | 2 | 22 | 1.284 | 28.2 | 0.786 | 1.284 | 1.009 | |

| 12 | 3 | 39 | 1.478 | 57.6 | 1.054 | 1.386 | 1.461 | |

| 14 | 3 | 46 | 1.500 | 69.0 | 0.648 | 1.312 | 0.850 | |

| 16 | 3 | 63 | 1.538 | 96.9 | 0.750 | 1.297 | 0.973 | |

| 20 | 4 | 87 | 1.628 | 141.6 | 0.644 | 1.282 | 0.826 | |

| 24 | 5 | 138 | 1.802 | 248.7 | 0.750 | 1.351 | 1.013 | |

| Type | Pipeline | Total | Delay | Normalized | ||||

|---|---|---|---|---|---|---|---|---|

| n | Stages | LUTs | (ns) | LDP | LUTs | Delay | LDP | |

| LogiCORE IP B is signed | 8 | 2 | 24 | 0.962 | 23.1 | 1.000 | 1.000 | 1.000 |

| 10 | 2 | 34 | 0.963 | 32.7 | 1.000 | 1.000 | 1.000 | |

| 12 | 2 | 49 | 1.071 | 52.5 | 1.000 | 1.000 | 1.000 | |

| 14 | 3 | 80 | 1.174 | 93.9 | 1.000 | 1.000 | 1.000 | |

| 16 | 3 | 90 | 1.188 | 106.9 | 1.000 | 1.000 | 1.000 | |

| 20 | 3 | 146 | 1.279 | 186.7 | 1.000 | 1.000 | 1.000 | |

| 24 | 3 | 198 | 1.360 | 269.3 | 1.000 | 1.000 | 1.000 | |

| Proposed KCM B is signed | 8 | 2 | 17 | 1.184 | 20.1 | 0.708 | 1.231 | 0.872 |

| 10 | 2 | 22 | 1.227 | 27.0 | 0.647 | 1.274 | 0.824 | |

| 12 | 3 | 39 | 1.450 | 56.6 | 0.796 | 1.354 | 1.078 | |

| 14 | 3 | 46 | 1.480 | 68.1 | 0.575 | 1.261 | 0.725 | |

| 16 | 3 | 60 | 1.505 | 90.3 | 0.667 | 1.267 | 0.845 | |

| 20 | 4 | 87 | 1.615 | 140.5 | 0.596 | 1.263 | 0.752 | |

| 24 | 5 | 138 | 1.739 | 240.0 | 0.697 | 1.279 | 0.891 | |

| Type | Total | Delay | Normalized | ||||

|---|---|---|---|---|---|---|---|

| n | LUTs | (ns) | LDP | LUTs | Delay | LDP | |

| LogiCORE IP Lookup + Multiplier B[k] is signed | 8 | 67 | 2.861 | 191.7 | 1.136 | 2.199 | 2.497 |

| 10 | 104 | 3.676 | 382.3 | 1.368 | 2.749 | 3.762 | |

| 12 | 151 | 3.935 | 594.2 | 1.438 | 2.752 | 3.957 | |

| 14 | 205 | 4.088 | 838.0 | 1.289 | 1.829 | 2.358 | |

| 16 | 270 | 3.980 | 1074.6 | 1.508 | 1.446 | 2.181 | |

| 20 | 420 | 5.013 | 2105.5 | 1.405 | 1.843 | 2.589 | |

| 24 | 603 | 4.982 | 3004.1 | 1.508 | 1.727 | 2.603 | |

| LogiCORE IP KCMs + MUX B[k] is signed | 8 | 59 | 1.301 | 76.8 | 1.000 | 1.000 | 1.000 |

| 10 | 76 | 1.337 | 101.6 | 1.000 | 1.000 | 1.000 | |

| 12 | 105 | 1.430 | 150.2 | 1.000 | 1.000 | 1.000 | |

| 14 | 159 | 2.235 | 355.4 | 1.000 | 1.000 | 1.000 | |

| 16 | 179 | 2.753 | 492.8 | 1.000 | 1.000 | 1.000 | |

| 20 | 299 | 2.720 | 813.3 | 1.000 | 1.000 | 1.000 | |

| 24 | 400 | 2.885 | 1154.0 | 1.000 | 1.000 | 1.000 | |

| Proposed KCM B[k] is signed | 8 | 18 | 1.468 | 26.4 | 0.305 | 1.128 | 0.344 |

| 10 | 33 | 2.211 | 73.0 | 0.434 | 1.654 | 0.718 | |

| 12 | 40 | 2.305 | 92.2 | 0.381 | 1.612 | 0.614 | |

| 14 | 61 | 3.146 | 191.9 | 0.384 | 1.408 | 0.540 | |

| 16 | 70 | 3.210 | 224.7 | 0.391 | 1.166 | 0.456 | |

| 20 | 108 | 4.012 | 433.3 | 0.361 | 1.475 | 0.533 | |

| 24 | 154 | 5.009 | 771.4 | 0.385 | 1.736 | 0.668 | |

| Type | Pipeline | Total | Delay | Normalized | ||||

|---|---|---|---|---|---|---|---|---|

| n | Stages | LUTs | (ns) | LDP | LUTs | Delay | LDP | |

| LogiCORE IP Lookup + Multiplier is signed | 8 | 4 | 67 | 1.510 | 101.2 | 1.117 | 1.593 | 1.779 |

| 10 | 5 | 106 | 1.476 | 156.5 | 1.268 | 1.440 | 1.861 | |

| 12 | 5 | 153 | 1.604 | 245.4 | 1.385 | 1.489 | 2.091 | |

| 14 | 5 | 207 | 1.590 | 329.1 | 1.152 | 1.355 | 1.576 | |

| 16 | 5 | 272 | 1.825 | 496.4 | 1.364 | 1.451 | 1.916 | |

| 20 | 6 | 426 | 1.917 | 816.6 | 1.350 | 1.425 | 1.903 | |

| 24 | 6 | 609 | 1.932 | 1176.6 | 1.436 | 1.442 | 2.052 | |

| LogiCORE IP KCMs + MUX is signed | 8 | 3 | 60 | 0.948 | 56.9 | 1.000 | 1.000 | 1.000 |

| 10 | 3 | 82 | 1.025 | 84.1 | 1.000 | 1.000 | 1.000 | |

| 12 | 3 | 109 | 1.077 | 117.4 | 1.000 | 1.000 | 1.000 | |

| 14 | 4 | 178 | 1.173 | 208.8 | 1.000 | 1.000 | 1.000 | |

| 16 | 4 | 206 | 1.258 | 259.1 | 1.000 | 1.000 | 1.000 | |

| 20 | 4 | 319 | 1.345 | 429.1 | 1.000 | 1.000 | 1.000 | |

| 24 | 4 | 428 | 1.340 | 573.5 | 1.000 | 1.000 | 1.000 | |

| Proposed KCM is signed | 8 | 2 | 18 | 1.211 | 21.8 | 0.300 | 1.277 | 0.383 |

| 10 | 3 | 33 | 1.404 | 46.3 | 0.402 | 1.370 | 0.551 | |

| 12 | 3 | 40 | 1.256 | 50.2 | 0.367 | 1.166 | 0.428 | |

| 14 | 4 | 61 | 1.429 | 87.2 | 0.343 | 1.218 | 0.417 | |

| 16 | 4 | 70 | 1.407 | 98.5 | 0.340 | 1.118 | 0.380 | |

| 20 | 5 | 116 | 1.379 | 160.0 | 0.364 | 1.025 | 0.373 | |

| 24 | 6 | 170 | 1.451 | 246.7 | 0.397 | 1.083 | 0.430 | |

| Type | Total | Delay | Normalized | ||||

|---|---|---|---|---|---|---|---|

| n | LUTs | (ns) | LDP | LUTs | Delay | LDP | |

| LogiCORE IP | 8 | 67 | 2.903 | 194.5 | 1.000 | 1.000 | 1.000 |

| Lookup + Multiplier | 10 | 106 | 3.740 | 396.4 | 1.000 | 1.000 | 1.000 |

| 12 | 153 | 3.922 | 600.1 | 1.000 | 1.000 | 1.000 | |

| 14 | 207 | 3.811 | 788.9 | 1.000 | 1.000 | 1.000 | |

| 16 | 272 | 4.068 | 1106.5 | 1.000 | 1.000 | 1.000 | |

| 20 | 422 | 4.885 | 2061.5 | 1.000 | 1.000 | 1.000 | |

| is signed | 24 | 605 | 5.128 | 3102.4 | 1.000 | 1.000 | 1.000 |

| LogiCORE IP | 8 | 97 | 1.500 | 145.5 | 1.448 | 0.517 | 0.748 |

| KCMs + MUX | 10 | 127 | 1.528 | 194.1 | 1.198 | 0.409 | 0.489 |

| 12 | 191 | 1.591 | 303.9 | 1.248 | 0.406 | 0.506 | |

| 14 | 291 | 2.633 | 766.2 | 1.406 | 0.691 | 0.971 | |

| 16 | 331 | 3.102 | 1026.8 | 1.217 | 0.763 | 0.928 | |

| 20 | 554 | 2.872 | 1591.1 | 1.313 | 0.588 | 0.772 | |

| is signed | 24 | 774 | 3.019 | 2336.7 | 1.279 | 0.589 | 0.753 |

| Proposed KCM | 8 | 26 | 2.190 | 56.9 | 0.388 | 0.754 | 0.293 |

| 10 | 39 | 1.894 | 73.9 | 0.368 | 0.506 | 0.186 | |

| 12 | 52 | 3.178 | 165.3 | 0.340 | 0.810 | 0.275 | |

| 14 | 75 | 3.855 | 289.1 | 0.362 | 1.012 | 0.367 | |

| 16 | 95 | 3.604 | 342.4 | 0.349 | 0.886 | 0.309 | |

| is signed | 20 | 148 | 5.464 | 808.7 | 0.351 | 1.119 | 0.392 |

| 24 | 202 | 6.453 | 1303.5 | 0.334 | 1.258 | 0.420 | |

| Type | Pipeline | Total | Delay | Normalized | ||||

|---|---|---|---|---|---|---|---|---|

| n | Stages | LUTs | (ns) | LDP | LUTs | Delay | LDP | |

| LogiCORE IP | 8 | 4 | 69 | 1.635 | 112.8 | 1.000 | 1.000 | 1.000 |

| Lookup + Multiplier | 10 | 5 | 108 | 1.466 | 158.3 | 1.000 | 1.000 | 1.000 |

| 12 | 5 | 155 | 1.671 | 259.0 | 1.000 | 1.000 | 1.000 | |

| 14 | 5 | 209 | 1.640 | 342.8 | 1.000 | 1.000 | 1.000 | |

| 16 | 5 | 274 | 1.731 | 474.3 | 1.000 | 1.000 | 1.000 | |

| 20 | 6 | 428 | 1.817 | 777.7 | 1.000 | 1.000 | 1.000 | |

| is signed | 24 | 6 | 611 | 1.820 | 1112.0 | 1.000 | 1.000 | 1.000 |

| LogiCORE IP | 8 | 3 | 103 | 1.030 | 106.1 | 1.493 | 0.630 | 0.940 |

| KCMs + MUX | 10 | 3 | 145 | 1.066 | 154.6 | 1.343 | 0.727 | 0.976 |

| 12 | 3 | 200 | 1.137 | 227.4 | 1.290 | 0.680 | 0.878 | |

| 14 | 4 | 327 | 1.624 | 531.0 | 1.565 | 0.990 | 1.549 | |

| 16 | 4 | 385 | 1.403 | 540.2 | 1.405 | 0.811 | 1.139 | |

| 20 | 4 | 593 | 1.515 | 898.4 | 1.386 | 0.834 | 1.155 | |

| is signed | 24 | 4 | 823 | 1.532 | 1260.8 | 1.347 | 0.842 | 1.134 |

| Proposed KCM | 8 | 3 | 26 | 1.365 | 35.5 | 0.377 | 0.835 | 0.315 |

| 10 | 3 | 39 | 1.482 | 57.8 | 0.361 | 1.011 | 0.365 | |

| 12 | 4 | 52 | 1.404 | 73.0 | 0.335 | 0.840 | 0.282 | |

| 14 | 5 | 80 | 1.561 | 124.9 | 0.383 | 0.952 | 0.364 | |

| 16 | 5 | 102 | 1.520 | 155.0 | 0.372 | 0.878 | 0.327 | |

| is signed | 20 | 7 | 165 | 1.628 | 268.6 | 0.386 | 0.896 | 0.345 |

| 24 | 8 | 226 | 1.712 | 386.9 | 0.370 | 0.941 | 0.348 | |

| Type | Total | Delay | Normalized | ||||

|---|---|---|---|---|---|---|---|

| n | LUTs | (ns) | LDP | LUTs | Delay | LDP | |

| LogiCORE IP | 8 | 73 | 2.830 | 206.6 | 1.000 | 1.000 | 1.000 |

| Lookup + Multiplier | 10 | 110 | 3.838 | 422.2 | 1.000 | 1.000 | 1.000 |

| 12 | 157 | 3.892 | 611.0 | 1.000 | 1.000 | 1.000 | |

| 14 | 212 | 3.892 | 825.1 | 1.000 | 1.000 | 1.000 | |

| 16 | 278 | 4.188 | 1164.3 | 1.000 | 1.000 | 1.000 | |

| 20 | 428 | 4.968 | 2126.3 | 1.000 | 1.000 | 1.000 | |

| is signed | 24 | 611 | 5.113 | 3124.0 | 1.000 | 1.000 | 1.000 |

| Proposed KCM | 8 | 35 | 3.018 | 105.6 | 0.479 | 1.066 | 0.511 |

| 10 | 54 | 3.642 | 196.7 | 0.491 | 0.949 | 0.466 | |

| 12 | 77 | 4.428 | 341.0 | 0.490 | 1.138 | 0.558 | |

| 14 | 104 | 5.209 | 541.7 | 0.491 | 1.338 | 0.657 | |

| 16 | 135 | 6.014 | 811.9 | 0.486 | 1.436 | 0.697 | |

| is signed | 20 | 209 | 7.749 | 1619.5 | 0.488 | 1.560 | 0.762 |

| 24 | 299 | 9.067 | 2711.0 | 0.489 | 1.773 | 0.868 | |

| Type | Pipeline | Total | Delay | Normalized | ||||

|---|---|---|---|---|---|---|---|---|

| n | Stages | LUTs | (ns) | LDP | LUTs | Delay | LDP | |

| LogiCORE IP | 8 | 4 | 73 | 1.626 | 118.7 | 1.000 | 1.000 | 1.000 |

| Lookup + Multiplier | 10 | 5 | 112 | 1.460 | 163.5 | 1.000 | 1.000 | 1.000 |

| 12 | 5 | 159 | 1.690 | 268.7 | 1.000 | 1.000 | 1.000 | |

| 14 | 5 | 214 | 1.648 | 352.7 | 1.000 | 1.000 | 1.000 | |

| 16 | 5 | 280 | 1.721 | 481.9 | 1.000 | 1.000 | 1.000 | |

| 20 | 6 | 434 | 1.894 | 822.0 | 1.000 | 1.000 | 1.000 | |

| is signed | 24 | 6 | 617 | 1.988 | 1226.6 | 1.000 | 1.000 | 1.000 |

| Proposed KCM | 8 | 4 | 35 | 1.404 | 49.1 | 0.479 | 0.863 | 0.414 |

| 10 | 5 | 58 | 1.234 | 71.6 | 0.518 | 0.845 | 0.438 | |

| 12 | 6 | 85 | 1.433 | 121.8 | 0.535 | 0.848 | 0.453 | |

| 14 | 7 | 116 | 1.364 | 158.2 | 0.542 | 0.828 | 0.449 | |

| 16 | 8 | 151 | 1.549 | 233.9 | 0.539 | 0.900 | 0.485 | |

| is signed | 20 | 10 | 233 | 1.583 | 368.8 | 0.537 | 0.836 | 0.449 |

| 24 | 12 | 331 | 1.669 | 552.4 | 0.536 | 0.840 | 0.450 | |

| Type | Number of Selectable Coefficients | |||||||

|---|---|---|---|---|---|---|---|---|

| 2 | 3 | 4 | 5 | 6 | 7 | 8 | ||

| CoreGen, | Slices | 107 | 107 | 107 | 107 | 107 | 107 | 107 |

| pipelined [13] | Normalized | 1.000 | 1.000 | 1.000 | 1.000 | 1.000 | 1.000 | 1.000 |

| DAG Fusion, | Slices | 35 | 64 | 76 | 100 | 112 | 127 | 138 |

| single-cycle [11,13] | Normalized | 0.327 | 0.598 | 0.710 | 0.935 | 1.047 | 1.187 | 1.290 |

| DAG Fusion, | Slices | 67 | 93 | 105 | 131 | 146 | 163 | 175 |

| pipelined [11,13] | Normalized | 0.626 | 0.869 | 0.981 | 1.224 | 1.364 | 1.523 | 1.636 |

| PAG Fusion, | Slices | 63 | 82 | 96 | 113 | 122 | 140 | 157 |

| pipelined [13] | Normalized | 0.589 | 0.766 | 0.897 | 1.056 | 1.140 | 1.308 | 1.467 |

| PAG Fusion Ternary, | Slices | 43 | 58 | 71 | 84 | 100 | 120 | 130 |

| pipelined [13] | Normalized | 0.402 | 0.542 | 0.664 | 0.785 | 0.935 | 1.121 | 1.215 |

| LogiCORE IP, | Slices | 96 | 101 | 95 | ||||

| pipelined | Normalized | 1.000 | 1.000 | 1.000 | ||||

| Proposed, | Slices | 21 | 28 | 40 | ||||

| single-cycle | Normalized | 0.219 | 0.277 | 0.421 | ||||

| Proposed, | Slices | 30 | 32 | 49 | ||||

| pipelined | Normalized | 0.313 | 0.317 | 0.516 | ||||

| Type | Number of Selectable Coefficients | |||||||

|---|---|---|---|---|---|---|---|---|

| 2 | 3 | 4 | 5 | 6 | 7 | 8 | ||

| CoreGen, | Freq (MHz) | 443 | 443 | 443 | 443 | 443 | 443 | 443 |

| pipelined [13] | Normalized | 1.000 | 1.000 | 1.000 | 1.000 | 1.000 | 1.000 | 1.000 |

| DAG Fusion, | Freq (MHz) | 206 | 177 | 160 | 135 | 126 | 116 | 109 |

| single-cycle [11,13] | Normalized | 0.465 | 0.399 | 0.362 | 0.304 | 0.284 | 0.261 | 0.247 |

| DAG Fusion, | Freq (MHz) | 474 | 478 | 475 | 462 | 450 | 450 | 454 |

| pipelined [11,13] | Normalized | 1.072 | 1.080 | 1.074 | 1.043 | 1.018 | 1.018 | 1.026 |

| PAG Fusion, | Freq (MHz) | 442 | 417 | 437 | 451 | 460 | 453 | 460 |

| pipelined [13] | Normalized | 0.998 | 0.942 | 0.987 | 1.019 | 1.038 | 1.024 | 1.040 |

| PAG Fusion Ternary, | Freq (MHz) | 346 | 324 | 322 | 315 | 312 | 306 | 304 |

| pipelined [13] | Normalized | 0.782 | 0.732 | 0.728 | 0.712 | 0.705 | 0.692 | 0.686 |

| LogiCORE IP, | Freq (MHz) | 548 | 577 | 581 | ||||

| pipelined | Normalized | 1.000 | 1.000 | 1.000 | ||||

| Proposed, | Freq (MHz) | 312 | 277 | 166 | ||||

| single-cycle | Normalized | 0.569 | 0.480 | 0.280 | ||||

| Proposed, | Freq (MHz) | 711 | 658 | 646 | ||||

| pipelined | Normalized | 1.297 | 1.138 | 1.111 | ||||

| Type | Number of Selectable Coefficients | |||||||

|---|---|---|---|---|---|---|---|---|

| 2 | 3 | 4 | 5 | 6 | 7 | 8 | ||

| (a) PAG Fusion, | Normalized Slices | 0.589 | 0.766 | 0.897 | 1.056 | 1.140 | 1.308 | 1.467 |

| pipelined [13] | Normalized to (a) | 1.000 | 1.000 | 1.000 | 1.000 | 1.000 | 1.000 | 1.000 |

| Normalized to (b) | 1.465 | 1.414 | 1.352 | 1.345 | 1.220 | 1.167 | 1.208 | |

| (b) PAG Fusion Ternary, | Normalized Slices | 0.402 | 0.542 | 0.664 | 0.785 | 0.935 | 1.121 | 1.215 |

| pipelined [13] | Normalized to (a) | 0.683 | 0.707 | 0.740 | 0.743 | 0.820 | 0.857 | 0.828 |

| Normalized to (b) | 1.000 | 1.000 | 1.000 | 1.000 | 1.000 | 1.000 | 1.000 | |

| Proposed, | Normalized Slices | 0.313 | 0.317 | 0.317 | 0.516 | 0.516 | 0.516 | 0.516 |

| pipelined | Normalized to (a) | 0.531 | 0.413 | 0.353 | 0.488 | 0.452 | 0.394 | 0.352 |

| Normalized to (b) | 0.778 | 0.584 | 0.477 | 0.657 | 0.552 | 0.460 | 0.425 | |

| Type | Number of Selectable Coefficients | |||||||

|---|---|---|---|---|---|---|---|---|

| 2 | 3 | 4 | 5 | 6 | 7 | 8 | ||

| (a) PAG Fusion, | Normalized Freq (MHz) | 0.998 | 0.942 | 0.987 | 1.019 | 1.038 | 1.024 | 1.040 |

| pipelined [13] | Normalized to (a) | 1.000 | 1.000 | 1.000 | 1.000 | 1.000 | 1.000 | 1.000 |

| Normalized to (b) | 1.277 | 1.287 | 1.357 | 1.432 | 1.473 | 1.479 | 1.516 | |

| (b) PAG Fusion Ternary, | Normalized Freq (MHz) | 0.782 | 0.732 | 0.728 | 0.712 | 0.705 | 0.692 | 0.686 |

| pipelined [13] | Normalized to (a) | 0.783 | 0.777 | 0.737 | 0.698 | 0.679 | 0.676 | 0.659 |

| Normalized to (b) | 1.000 | 1.000 | 1.000 | 1.000 | 1.000 | 1.000 | 1.000 | |

| Proposed, | Normalized Freq (MHz) | 1.297 | 1.138 | 1.138 | 1.111 | 1.111 | 1.111 | 1.111 |

| pipelined | Normalized to (a) | 1.299 | 1.209 | 1.154 | 1.090 | 1.070 | 1.085 | 1.068 |

| Normalized to (b) | 1.277 | 1.287 | 1.357 | 1.432 | 1.473 | 1.479 | 1.516 | |

© 2017 by the author. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).

Share and Cite

Walters, E.G., III. Reduced-Area Constant-Coefficient and Multiple-Constant Multipliers for Xilinx FPGAs with 6-Input LUTs. Electronics 2017, 6, 101. https://doi.org/10.3390/electronics6040101

Walters EG III. Reduced-Area Constant-Coefficient and Multiple-Constant Multipliers for Xilinx FPGAs with 6-Input LUTs. Electronics. 2017; 6(4):101. https://doi.org/10.3390/electronics6040101

Chicago/Turabian StyleWalters, E. George, III. 2017. "Reduced-Area Constant-Coefficient and Multiple-Constant Multipliers for Xilinx FPGAs with 6-Input LUTs" Electronics 6, no. 4: 101. https://doi.org/10.3390/electronics6040101